# ATF697FF

# Atmel

# Rad- hard 32 bit SPARC V8 Reconfigurable Processor

# DATASHEET

# **Features**

- SPARC V8 High Performance Low-power 32-bit processor core

- AT697F Sparc v8 processor

- LEON2-FT 1.0.9.16.1 compliant

- 8 Register Windows

- Advanced Architecture

- 5 Stage Pipeline

- 32 kbyte 4-way associative instruction cache

- 16 kbyte 2-way associative data cache

- Integrated 32/64-bit IEEE 754 Floating-point Unit

- Reconfigurable Unit

- ATF280F SRAM FPGA

- 280K equivalent ASIC gates

- 14400 cells

- Unlimited reprogrammability

- SEE hardened cells

- No need for Triple Modular Redundancy (TMR)

- FreeRAM<sup>™</sup>

- 115200 Bits of Distributed RAM

- 32x4 RAM blocks organization

- Independent of logic cells

- Single/Dual Port capability

- Flexible Configuration modes

- Master/Slave Capability

- Serial/Parallel Capability

- Flexible clock management 8 Global Clocks

1 Fast Clock

- Configuration Security Management

- Check of the data during FPGA configuration

- Self Integrity Check (SIC) of the configuration during FPGA operation

- Flexible Memory Interface

- PROM Controller

- SRAM Controller

- SDRAM Controller

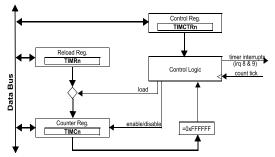

- Timers

- Two 32-bit Timers

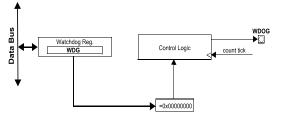

- Watchdog Timer

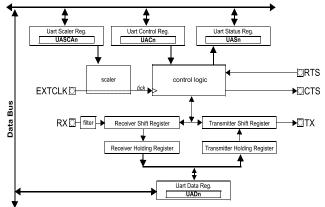

- Two 8-bit UARTs

- Interrupt Controller with 8 External Programmable Inputs

- General Purpose Interface

- 32 Parallel I/O Interface

- 140 Configurable Cold Sparing and PCI Compliant I/Os

- 4 LVDS transceivers and 4 LVDS receivers

- Debug and Test Facilities

- Debug Support Unit (DSU) for Trace and Debug

- Four Hardware Watchpoints

- Operating range

- Voltages

- 3.3V +/- 0.30V for I/O

- 1.8V +/- 0.15V for Core

- Temperature

- -55°C to 125°C

- Clocks:

- Processor : 0MHz up to 100MHz<sup>1</sup>

- Reconfigurable Unit : 0MHz up to 50MHz

- Performance:

- 86MIPS (Dhrystone 2.1)

- 23MFLOPS (Whetstone)

- Package MQFPT 352

- Mass: 30g

- Evaluation kit including

- ATF697FF evaluation board

- ATF697FF sample

<sup>&</sup>lt;sup>1</sup> The 100 MHz should be confirmed by experimental test.

# Description

ATF697FF is a multichip module integrating a 32 bit RISC processor together with a reconfigurable unit. The processor implementation is the European Space Agency (ESA) SPARC V8 LEON2 fault tolerant model also known as AT697F for the Atmel standalone chip. The reconfigurable unit is based on the Atmel 280kgates radiation hardened SRAM-based reprogrammable FPGA also known as ATF280F.

Both the processor unit and the reconfigurable units are manufactured using the Atmel 0.18µm rad-hard AT58KRHA CMOS technology.

The two dies have been especially designed for space application by implementing hardened cells, on-chip concurrent transient and permanent error detection and correction and permanent self integrity check mechanism.

By executing powerful instructions in a single clock cycle, the processor unit achieves throughputs around 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

The configurable unit offers a patented distributed 10 ns SEU hardened SRAM capability where the RAM can be used without losing logic resources. Multiple independent, synchronous or asynchronous, dual port or single port RAM functions (FIFO, scratch pad, etc.) can be created using Atmel's macro generator tool. They are organized by blocks of 32x4 bits.

ATF697FF contains an on-chip Integer Unit (IU), a Floating Point Unit (FPU), separate instruction and data caches, hardware multiplier and divider, interrupt controller, debug support unit with trace buffer, two 32-bit timers, Parallel and Serial interfaces, a Watchdog, a reconfigurable unit, a flexible Memory Controller and a 280 Kgates of reconfigurable unit. The configurable unit embeds 8 global clocks, 2 high speed clocks, 4 LVDS interface and 150 cold sparing and PCI compliant programmable I/Os dedicated to the application needs. The communication between the processor and the reconfigurable unit is performed by three different means: the internal PCI interface, GPIO and the EBI interface. ATF697FF only requires memory to be added to form a complete on-board computer.

# **Table of Contents**

# Features 1

| 1. | Pin  | description                                                    | 8  |

|----|------|----------------------------------------------------------------|----|

|    | 1.1  | System Interface                                               |    |

|    | 1.2  | Clock Interface                                                |    |

|    | 1.3  | Memory Interface                                               |    |

|    |      | 1.3.1 PROM 11                                                  |    |

|    |      | 1.3.2 SRAM12                                                   |    |

|    |      | 1.3.3 I/O 12                                                   |    |

|    |      | 1.3.4 SDRAM 12                                                 |    |

|    | 1.4  | Input / Output                                                 |    |

|    | 1.5  | LVDS Input Output                                              |    |

|    | 1.6  | DSU Interface                                                  |    |

|    | 1.7  | Power Supply                                                   |    |

| 2. | Arch | hitecture                                                      |    |

|    | 2.1  | Architecture of the processor                                  |    |

|    |      | 2.1.1 Integer Unit                                             |    |

|    |      | 2.1.2 Floating-Point Unit                                      |    |

|    |      | 2.1.3 Fault Tolerance                                          |    |

|    |      | 2.1.4 Operating Modes                                          |    |

|    | 2.2  | Architecture of the reconfigurable unit                        |    |

|    |      | 2.2.1 FPGA Core                                                |    |

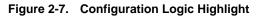

|    |      | 2.2.2 Configuration Logic                                      |    |

|    |      | 2.2.3 POR 25                                                   |    |

|    |      | 2.2.4 Configuration Control                                    |    |

|    |      | 2.2.5 Configuration SRAM                                       |    |

|    |      | 2.2.6 Configuration Load Checker                               |    |

|    |      | 2.2.7 Configuration Self Internal Checker<br>2.2.8 User I/O 26 |    |

|    |      | 2.2.8 User I/O 26<br>2.2.9 LVDS I/O                            | 26 |

|    |      | 2.2.10 Clock 26                                                |    |

| 3. | Flex | xible memory interface                                         | 27 |

|    | 3.1  | Memory interface                                               | 27 |

|    | 0    | 3.1.1 Overview                                                 |    |

|    |      | 3.1.2 PROM Interface                                           |    |

|    |      | 3.1.3 Memory-Mapped I/O                                        |    |

|    |      | 3.1.4 RAM Interface                                            |    |

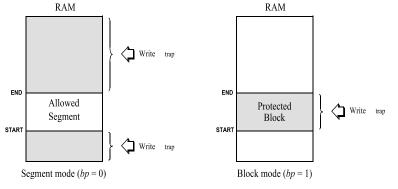

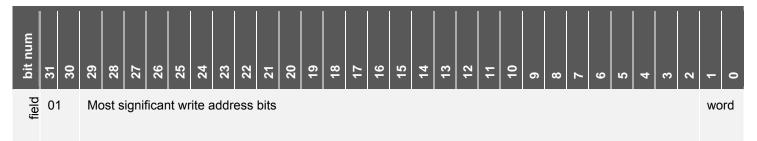

|    |      | 3.1.5 Write Protection                                         |    |

|    |      | 3.1.6 BRDY* -Controlled Access                                 |    |

|    |      | 3.1.7 Bus exception                                            |    |

|    | 3.2  | Memory Mapped Reconfigurable Unit                              |    |

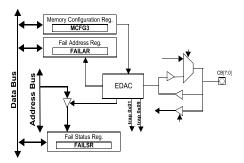

| 4. | EDA  | AC management                                                  |    |

|    | 4.1  | Overview                                                       |    |

|    | 4.2  | EDAC Capability Mapping                                        |    |

|    |      | 4.2.2 PROM Protection                                          |    |

|    |      | 4.2.3 RAM Protection                                           |    |

|    | 4.3  | Operation                                                      |    |

|    |      | 4.3.1 Hamming Code                                             |    |

|    |      | 4.3.2 Write Access                                             |    |

|    |      | 4.3.3 Read Access                                              |    |

|    |      | 4.3.4 Correctable Error                                        |    |

|    | ć    | 4.3.5 Uncorrectable Error                                      |    |

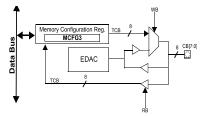

|    | 4.4  | EDAC on 8-bit Memories                                         |    |

|    | 4.5  | EDAC Testing                                                   |    |

|          |                                                       | 4.5.1                                                                                                                                                                                                                                  | EDAC testing overview                                                                                                                                                             |                                                                                                                                  |  |

|----------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

|          |                                                       | 4.5.2                                                                                                                                                                                                                                  | Write Test                                                                                                                                                                        | 45                                                                                                                               |  |

|          |                                                       | 4.5.3                                                                                                                                                                                                                                  | Read Test                                                                                                                                                                         | 45                                                                                                                               |  |

| 5        | Cool                                                  | che Memories46                                                                                                                                                                                                                         |                                                                                                                                                                                   |                                                                                                                                  |  |

| 5.       |                                                       |                                                                                                                                                                                                                                        |                                                                                                                                                                                   |                                                                                                                                  |  |

|          | 5.1                                                   |                                                                                                                                                                                                                                        | W                                                                                                                                                                                 |                                                                                                                                  |  |

|          | 5.2                                                   | Operation                                                                                                                                                                                                                              | on                                                                                                                                                                                |                                                                                                                                  |  |

|          |                                                       | 5.2.1                                                                                                                                                                                                                                  | Disabled Mode                                                                                                                                                                     |                                                                                                                                  |  |

|          |                                                       | 5.2.2                                                                                                                                                                                                                                  | Enabled Mode                                                                                                                                                                      |                                                                                                                                  |  |

|          |                                                       | 5.2.3                                                                                                                                                                                                                                  | Frozen Mode                                                                                                                                                                       |                                                                                                                                  |  |

|          |                                                       | 5.2.4                                                                                                                                                                                                                                  | Parity Protection                                                                                                                                                                 |                                                                                                                                  |  |

|          | 5.3                                                   |                                                                                                                                                                                                                                        | ion Cache                                                                                                                                                                         |                                                                                                                                  |  |

|          |                                                       | 5.3.1                                                                                                                                                                                                                                  | Overview                                                                                                                                                                          | 47                                                                                                                               |  |

|          |                                                       | 5.3.2                                                                                                                                                                                                                                  | Cache Control                                                                                                                                                                     |                                                                                                                                  |  |

|          |                                                       | 5.3.3                                                                                                                                                                                                                                  | Operation                                                                                                                                                                         |                                                                                                                                  |  |

|          | 5.4                                                   | Data Ca                                                                                                                                                                                                                                | ache                                                                                                                                                                              | 48                                                                                                                               |  |

|          |                                                       | 5.4.1                                                                                                                                                                                                                                  | Overview                                                                                                                                                                          | 48                                                                                                                               |  |

|          |                                                       | 5.4.2                                                                                                                                                                                                                                  | Cache Control                                                                                                                                                                     |                                                                                                                                  |  |

|          |                                                       | 5.4.3                                                                                                                                                                                                                                  | Operation                                                                                                                                                                         |                                                                                                                                  |  |

|          |                                                       | 5.4.4                                                                                                                                                                                                                                  | Error Reporting                                                                                                                                                                   |                                                                                                                                  |  |

|          | 5.5                                                   | Diagnos                                                                                                                                                                                                                                | stic Cache Access                                                                                                                                                                 | 49                                                                                                                               |  |

| ~        | <b>T</b>                                              |                                                                                                                                                                                                                                        |                                                                                                                                                                                   | - 4                                                                                                                              |  |

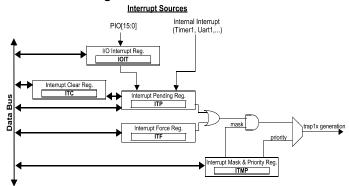

| 6.       | •                                                     | is and ir                                                                                                                                                                                                                              | nterrupts                                                                                                                                                                         | 51                                                                                                                               |  |

|          | 6.1                                                   | Overvie                                                                                                                                                                                                                                | ۰                                                                                                                                                                                 | 51                                                                                                                               |  |

|          | 6.2                                                   | Synchro                                                                                                                                                                                                                                | onous Traps                                                                                                                                                                       | 51                                                                                                                               |  |

|          | 6.3                                                   | Traps D                                                                                                                                                                                                                                | Description                                                                                                                                                                       | 52                                                                                                                               |  |

|          | 6.4                                                   |                                                                                                                                                                                                                                        | ronous Traps / Interrupts                                                                                                                                                         |                                                                                                                                  |  |

|          |                                                       | 6.4.2                                                                                                                                                                                                                                  | Operation                                                                                                                                                                         |                                                                                                                                  |  |

|          |                                                       | 6.4.3                                                                                                                                                                                                                                  | Interrupts List                                                                                                                                                                   |                                                                                                                                  |  |

|          |                                                       | 6.4.4                                                                                                                                                                                                                                  | I/O Interrupts                                                                                                                                                                    | 54                                                                                                                               |  |

| 7        | тімі                                                  | -R 56                                                                                                                                                                                                                                  |                                                                                                                                                                                   |                                                                                                                                  |  |

| 7.       | <b>TIM</b><br>7.1<br>7.2<br>7.3                       | Timer 1                                                                                                                                                                                                                                | er<br>& Timer 2<br>og                                                                                                                                                             | 56                                                                                                                               |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd                                                                                                                                                                                                           | & Timer 2                                                                                                                                                                         | 56                                                                                                                               |  |

| 7.<br>8. | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd                                                                                                                                                                                                           | & Timer 2<br>og                                                                                                                                                                   | 56<br>57                                                                                                                         |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd<br>CT 58<br>Overvie                                                                                                                                                                                       | & Timer 2<br>og                                                                                                                                                                   | 56<br>57<br>58                                                                                                                   |  |

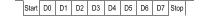

|          | 7.1<br>7.2<br>7.3                                     | Prescale<br>Timer 1<br>Watchd<br><b>RT 58</b><br>Overvie<br>8.1.2                                                                                                                                                                      | & Timer 2<br>og<br>w<br>Data Frame                                                                                                                                                |                                                                                                                                  |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd<br>RT 58<br>Overvie<br>8.1.2<br>8.1.3                                                                                                                                                                     | & Timer 2<br>og<br>w<br>Data Frame<br>Baud-Rate                                                                                                                                   | 56<br>57<br>58<br>58<br>58                                                                                                       |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd<br><b>RT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4                                                                                                                                                     | & Timer 2<br>og<br>W<br>Data Frame<br>Baud-Rate<br>External Clock                                                                                                                 | 56<br>57<br>58<br>58<br>58<br>59                                                                                                 |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5                                                                                                                                            | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering                                                                                                  | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59                                                                                     |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6                                                                                                                                   | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering<br>Hardware Flow-Control                                                                         | 56<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>59<br>59                                                                         |  |

|          | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7                                                                                                                          | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering<br>Hardware Flow-Control<br>Noise Filtering                                                      | 56<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>59                                                             |  |

|          | 7.1<br>7.2<br>7.3                                     | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio                                                                                                              | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering<br>Hardware Flow-Control<br>Noise Filtering<br>on                                                | 56<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>59<br>60                                                       |  |

|          | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1                                                                                                     | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering<br>Hardware Flow-Control<br>Noise Filtering<br>on<br>Transmitter Operation                       | 56<br>57<br>58<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60                                                       |  |

|          | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2                                                                                            | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering<br>Hardware Flow-Control<br>Noise Filtering<br>on<br>Transmitter Operation<br>Receiver Operation | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60                                                 |  |

|          | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>XT 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1                                                                                                     | & Timer 2<br>og<br>Data Frame                                                                                                                                                     | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>60                                           |  |

|          | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                                                                          | & Timer 2<br>og<br>Data Frame<br>Baud-Rate<br>External Clock<br>Double Buffering<br>Hardware Flow-Control<br>Noise Filtering<br>on<br>Transmitter Operation<br>Receiver Operation | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>60                                           |  |

|          | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                                                                          | & Timer 2<br>og<br>Data Frame                                                                                                                                                     | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>60                                           |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1                       | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>0 62</b>                                                           | & Timer 2<br>og<br>Data Frame                                                                                                                                                     | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61                                           |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2                | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>0 62</b>                                                           | & Timer 2                                                                                                                                                                         | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61                                           |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2                | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>D 62</b><br>Process                                                | & Timer 2                                                                                                                                                                         | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61                                           |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2                | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>O 62</b><br>Process<br>9.1.1<br>9.1.2                              | & Timer 2<br>og<br>Data Frame                                                                                                                                                     | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61<br>61                               |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2<br>GPIC<br>9.1 | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>O 62</b><br>Process<br>9.1.1<br>9.1.2                              | & Timer 2                                                                                                                                                                         | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>63<br>64 |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2<br>GPIC<br>9.1 | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>D 62</b><br>Process<br>9.1.1<br>9.1.2<br>Reconfi                   | & Timer 2<br>og                                                                                                                                                                   | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>63<br>64 |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2<br>GPIC<br>9.1 | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>D 62</b><br>Process<br>9.1.1<br>9.1.2<br>Reconfi<br>9.2.1          | & Timer 2<br>og                                                                                                                                                                   | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>63<br>64 |  |

| 8.       | 7.1<br>7.2<br>7.3<br>UAR<br>8.1<br>8.2<br>GPIC<br>9.1 | Prescal<br>Timer 1<br>Watchd<br><b>2T 58</b><br>Overvie<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>Operatio<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br><b>D 62</b><br>Process<br>9.1.1<br>9.1.2<br>Reconfi<br>9.2.1<br>9.2.2 | & Timer 2                                                                                                                                                                         | 56<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>59<br>59<br>60<br>60<br>60<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>63<br>64 |  |

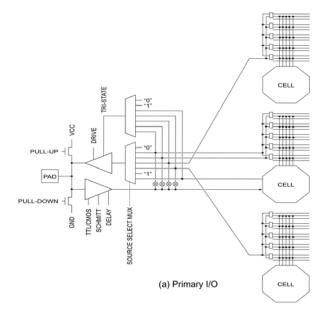

|           | 9.2.6 Tri-State 65                                                                                                   |         |

|-----------|----------------------------------------------------------------------------------------------------------------------|---------|

|           | 9.2.7 Dual-use I/O                                                                                                   |         |

| 9.3       | LVDS Interfaces                                                                                                      |         |

| 10. Inter | nal communication                                                                                                    | 67      |

| 10.1      | Introduction                                                                                                         | 67      |

| 10.2      | EBI sharing                                                                                                          |         |

| 10.3      | GPIO sharing                                                                                                         | 67      |

| 10.4      | PCI sharing                                                                                                          |         |

|           | 10.4.1 Internal PCI interface: pin description                                                                       |         |

|           | 10.4.2 Internal PCI arbiter                                                                                          |         |

|           | 10.4.3 PCI pheripheral (ATF697FF processor's side)                                                                   |         |

|           | <ul> <li>10.4.4 PCI Interface</li> <li>10.4.5 To launch an internal PCI transaction between the processor</li> </ul> | and the |

|           | reconfigurable unit                                                                                                  |         |

| 11. Cloc  | k system                                                                                                             |         |

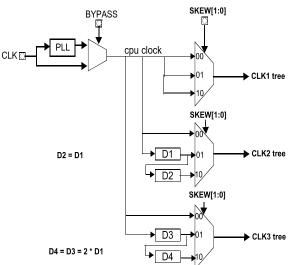

| 11.1      | Clock: processor part                                                                                                |         |

| 11.2      | Overview                                                                                                             |         |

| 11.3      | PCI Clock                                                                                                            |         |

|           | 11.3.1 External Clock                                                                                                |         |

| 11.4      | CPU Clock                                                                                                            |         |

|           | 11.4.1 External Clock                                                                                                |         |

|           | 11.4.2 PLL 81                                                                                                        | 0.0     |

| 11.5      | Fault-Tolerance & Clock                                                                                              |         |

| 11.0      | 11.5.2 Skew82                                                                                                        | 0.0     |

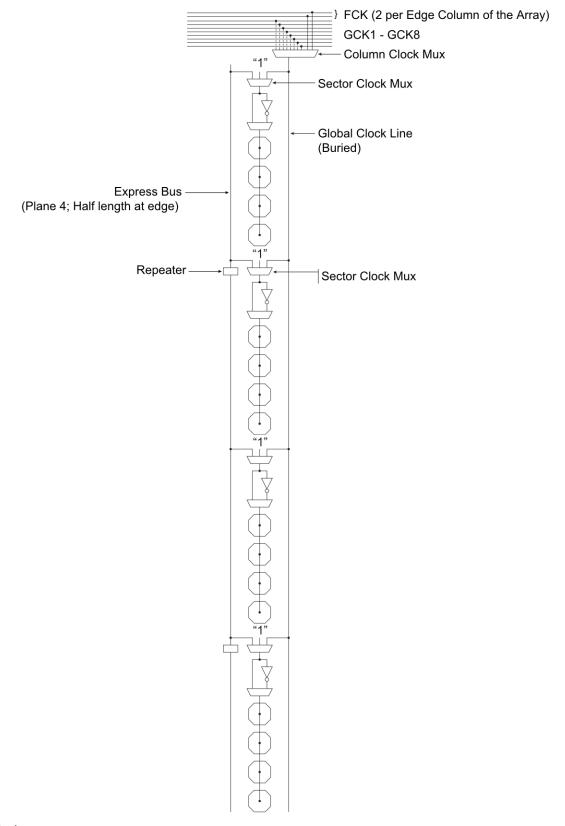

| 11.6      | Clock: reconfigurable unit part                                                                                      |         |

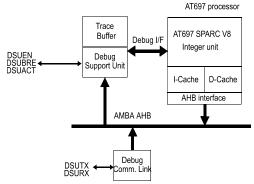

| 12.1      | <b>Ig interface: DSU</b><br>Overview<br>Debug Support Unit                                                           |         |

| 12.2      | 12.2.1 DSU Breakpoint                                                                                                |         |

|           | 12.2.2 Time Tag                                                                                                      |         |

|           | 12.2.3 Trace Buffer                                                                                                  |         |

|           | 12.2.4 DSU Memory Map                                                                                                |         |

|           | 12.2.5 Debug Operations                                                                                              |         |

|           | 12.2.6 DSU Trap                                                                                                      |         |

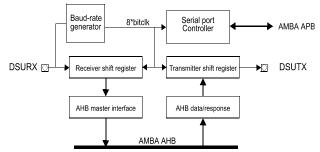

| 12.3      | DSU Communication Link                                                                                               |         |

|           | 12.3.2 Data Frame                                                                                                    |         |

|           | 12.3.3 Commands                                                                                                      |         |

| 12.4      | 12.3.4 Clock Generation<br>Booting from DSU                                                                          |         |

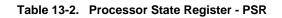

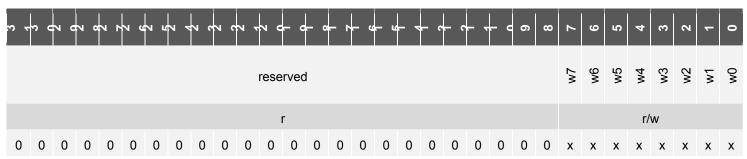

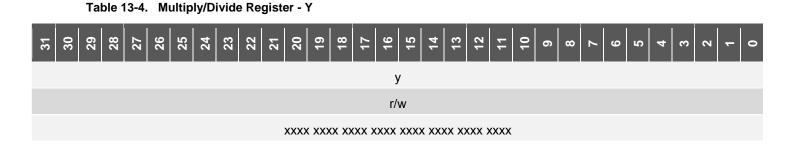

| 13 Proc   | essor registers description                                                                                          |         |

| 13.1      | Description registers                                                                                                |         |

| 13.2      | Integer Unit Registers                                                                                               |         |

|           | Floating-Point Unit Registers                                                                                        |         |

| 13.4      | Memory Interface Registers                                                                                           |         |

| 13.5      | System Registers                                                                                                     |         |

|           | Caches Register                                                                                                      |         |

| 13.0      | Idle Register                                                                                                        |         |

| 13.7      | Timer Registers                                                                                                      |         |

| 13.0      | -                                                                                                                    |         |

|           | UART Registers                                                                                                       |         |

|           | Interrupt Registers                                                                                                  |         |

|           | General Purpose Interface Registers                                                                                  |         |

|           | PCI Registers<br>DSU Registers                                                                                       |         |

|           | -                                                                                                                    |         |

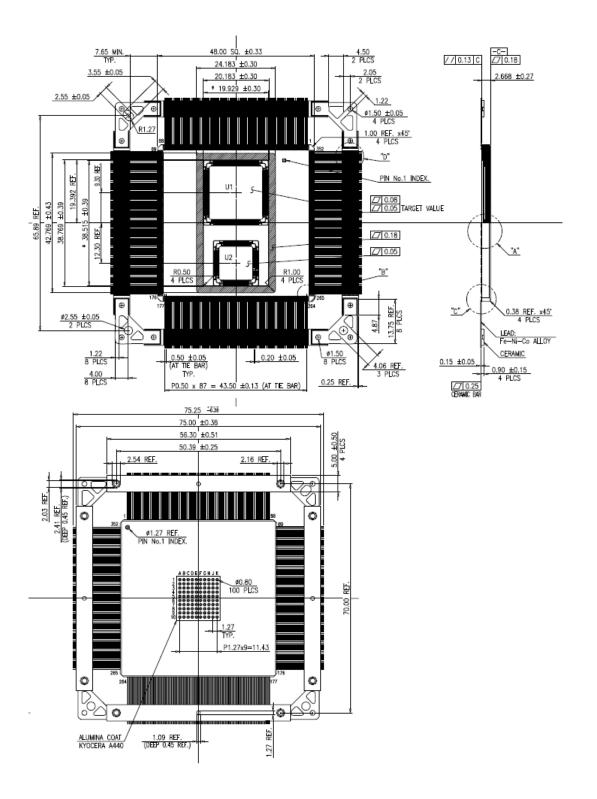

| 14. Pack  | aging information                                                                                                    | 103     |

|     | 14.1<br>14.2 |           | ng drawing: MQFPT352<br>ping: MQFPT352    |     |

|-----|--------------|-----------|-------------------------------------------|-----|

| 15. |              |           | aracteristics                             |     |

|     | 15.1         |           | e maximum ratings – advanced information  |     |

|     | 15.2         |           | acteristics – Advanced Information        |     |

|     | 15.3         |           | aring                                     |     |

|     | 15.4         |           | equencing                                 |     |

|     | 15.5         |           | onsumption: ATF697FF processor part       |     |

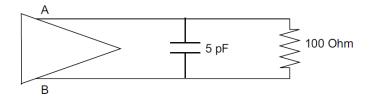

|     | 15.6         | Decoupl   | ing capacitance                           |     |

|     | 15.7         | AC char   | acteristics: ATF697FF processor           |     |

|     |              | 15.7.1    | Natural Skew                              |     |

|     |              | 15.7.2    | Maximum Skew                              |     |

|     |              | 15.7.3    | Timing Derating                           |     |

|     | 15.8         | AC char   | acteristics: ATF697FF reconfigurable unit |     |

|     |              | 15.8.1    | AC characteristics                        |     |

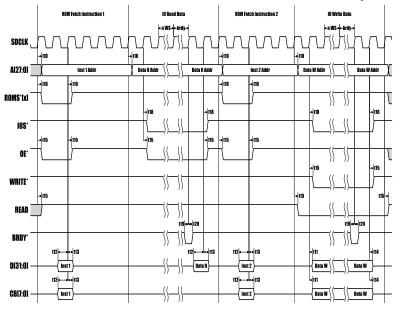

|     | 15.9         | Timing c  | liagram                                   |     |

|     |              | 15.9.1    | Diagram List                              |     |

|     |              | 15.9.2    | Reset 187                                 |     |

|     |              | 15.9.3    | Clock 188                                 |     |

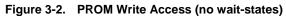

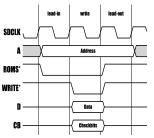

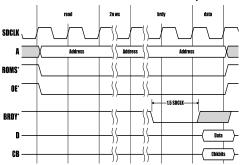

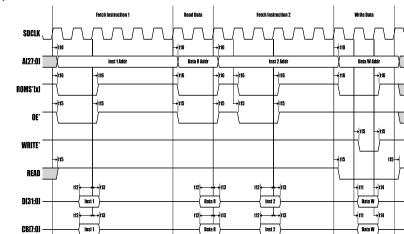

|     |              | 15.9.4    | PROM 188                                  |     |

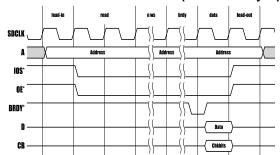

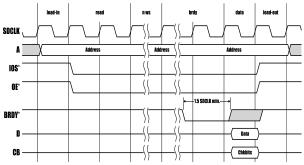

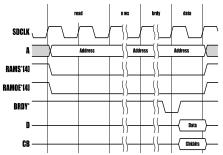

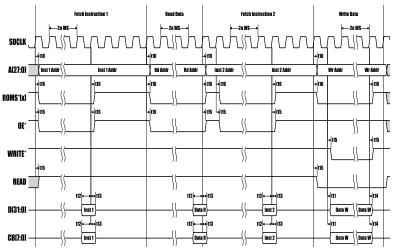

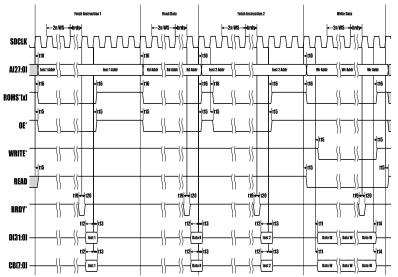

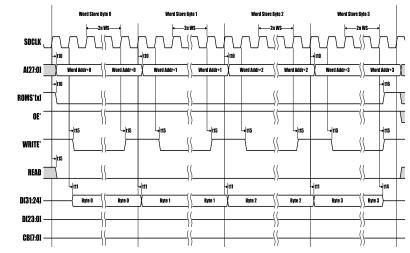

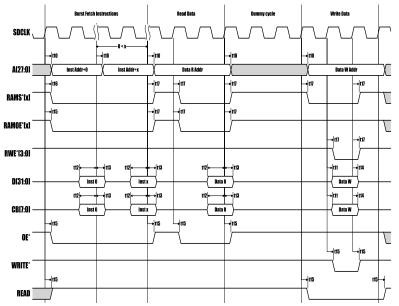

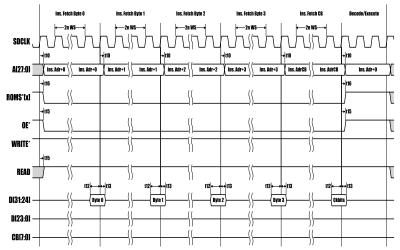

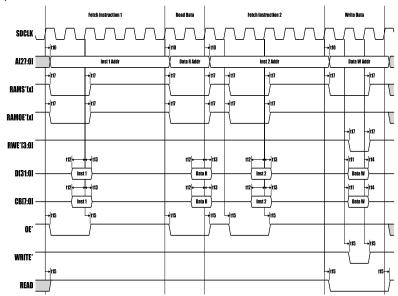

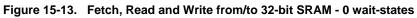

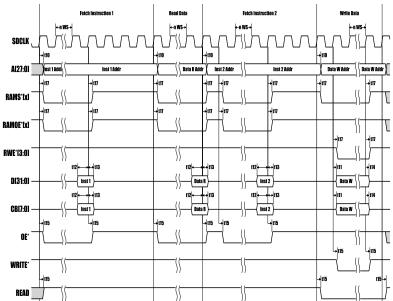

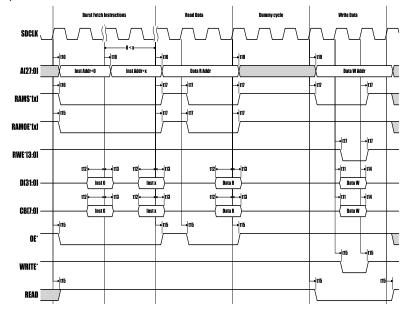

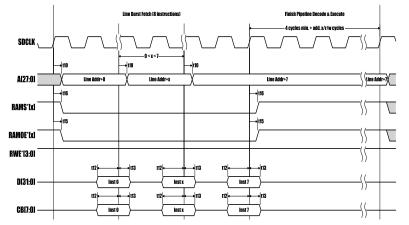

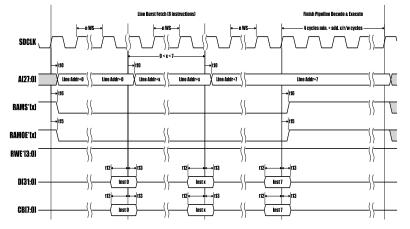

|     |              | 15.9.5    | SRAM 191                                  |     |

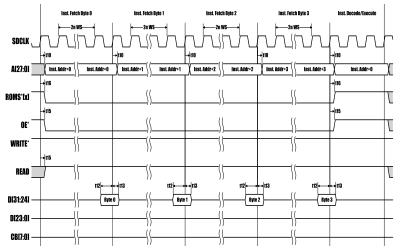

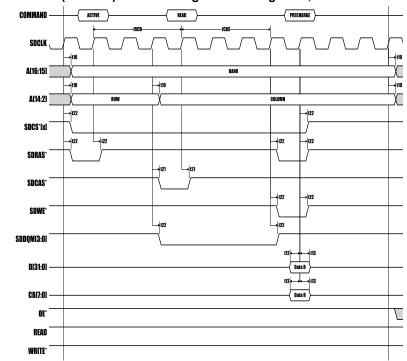

|     |              | 15.9.6    | SDRAM 194                                 |     |

|     |              | 15.9.7    | I/O 195                                   |     |

| 16. | Orde         | ring Info | ormation                                  | 197 |

| 17. | Revi         | sion His  | tory                                      | 197 |

# 1. Pin description

# 1.1 System Interface

PROC\_RESET\* - Processor reset (input)

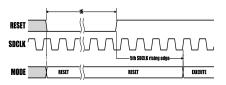

When asserted, this asynchronous active low input immediately halts and resets the processor and all on-chip peripherals. The processor restarts execution after the 5th rising edge of the clock after PROC\_RESET\* was de-asserted.

FPGA\_RESET\* - reconfigurable unit reset (input)

FPGA\_RESET\* is the reconfigurable unit configuration manual reset pin. It is available during all configuration states. It initiates a configuration clear cycle and, if operating in Mode 0, an autoconfiguration. It is a dedicated Schmitt trigger input with approximately 1V of hysteresis for noise immunity. It is pulled to VCC with a nominal 50K internal resistor.

ERROR\* - Processor error (open-drain output with pull-up)

This active low output is asserted when the processor is halted in error mode.

WDOG\* - Watchdog timeout (open-drain output with pull-up)

This active low output is asserted when the watchdog timer has expired and remains asserted until the watchdog timer is reloaded with a non-null value.

BEXC\* - Bus exception (input)

This active low input is sampled simultaneously with the data during an access to the external memory. If asserted, a memory error is generated.

M0, M1, M2 (Input)

The mode pins are dedicated TTL threshold inputs that determine the configuration mode to be used. The mode pins should not be changed during power-on-reset, manual reset, or configuration download. The user may change the mode pins during configuration idle. These pins have no pullup resistors to VCC, so they need to be driven by the user or tied off.

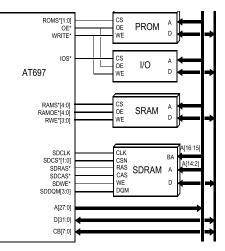

CCLK - Reconfigurable unit configuration clock (bi-directional)

CCLK is the configuration clock pin of the configurable unit. It is an input or output depending on the mode of operation. During power-on-reset or manual reset, it is a tri-stated output. During configuration download and in Mode 0, it is an output with a typical frequency of 1 MHz. During configuration download and in all other modes, it is a Schmitt trigger input with approximately 1V of hysteresis for noise immunity. It is an input during configuration idle, but is ignored. It is pulled to VCC with a nominal 50K internal resistor.

D0 - Configuration Data Bus - LSB (Input/Output)

D0 is the lsb of the ATF697FF reconfigurable unit configuration data bus used to download configuration data to the device. During power-on-reset or manual reset, D0 is controlled by the configuration SRAM. The D0 pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. D0 becomes an input during configuration download.

INIT - (Input/Output)

INIT is a multi-function pin. During power-on-reset and manual reset, the pin functions as an open drain bi-directional IO which releases High when the configuration clear cycle is complete, but can be held Low to hold the configuration in a reset state. Once released, the FPGA will proceed to either configuration download or idle, as appropriate. During configuration download, the INIT pin is again an open drain bi-directional pin which signals if an error is encountered during the download of a configuration bitstream. In addition, during the Check Function, the INIT pin drives Low for any configuration SRAM mismatch (see the description of the Check Function on page 16 for more details). While in open drain mode, the pin is pulled to VDD with a nominal 20K internal resistor. When not configuring, the INIT pin becomes a fully functional user IO.

# CON- Configuration Status (Input/Output)

CON is the FPGA configuration start and status pin. It is a dedicated open drain bi-directional pin. During power-onreset or manual reset, CON is driven Low by the ATF697FF reconfigurable unit.

- In Mode 7, when the FPGA has finished the configuration clear cycle, CON is released to indicate the device is

ready for the user to initiate configuration download. The user may then drive CON Low to initiate a

configuration download. After three clock cycles, CON is then driven Low by the FPGA until it finishes the

download, and it is then released.

- In Mode 0, CON is not released by the FPGA at the end of power-on-reset or manual reset. Instead, CON is controlled by the FPGA until the end of the auto-configuration process. CON is released at the end of configuration download in Mode 0, and the user may then initiate a manual configuration download by driving CON Low. While in open drain mode, the pin is pulled to VDD with a nominal 10K internal resistor.

### HDC - High During Configuration (output)

HDC (1) is driven High by the FPGA during power-on-reset, manual reset, and configuration download. During normal operation, the pin is a fully functional user IO.

All user IO default to inputs with pull-ups "on". The HDC pin transitions from driving a strong "1" to a pull-up "1" after reset. The HDC pin will transition from driving a strong "1" to the user programmed state at the end of configuration download. If not programmed, the default state is input with pull-up.

# LDC - Low During Configuration (output)

LDC is driven Low by the FPGA during power-on-reset, manual reset, and configuration download. During normal operation, the pin is a fully functional user IO

All user IO default to inputs with pull-ups "on". The HDC pin transitions from driving a strong "1" to a pull-up "1" after reset. The HDC pin will transition from driving a strong "1" to the user programmed state at the end of configuration download. If not programmed, the default state is input with pull-up.

# CS0\* - Configuration Chip Select (Input/Output)

CS0\* is an ATF697FF reconfigurable unitconfiguration chip select. It is active Low. During power-on-reset or manual reset, CS0\* is controlled by the configuration SRAM. The CS0\* pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. In Mode 1, it is used as a chip select to enable configuration to begin. It is most often used as the chip select of the downstream device in a cascade chain, and is usually driven by CSOUT of the upstream device. Releasing CS0\* during configuration causes the Mode 1 ATF697FF reconfigurable unit to abort the download and release CON. CS0\* is used only in Mode 1.

CSOUT - Configuration Cascade Output (Output)

CSOUT is the configuration pin used to enable the downstream device in a cascade chain. During power-on-reset or manual reset, CSOUT is controlled by the configuration SRAM. The CSOUT pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. During configuration download, CSOUT becomes an optional output. It is enabled by default after reset, and may be enabled or disabled via the configuration control register. If the user has disabled the cascade function, the pin remains a user IO. If the cascade function is enabled, the CSOUT pin is driven High at the start of configuration download. At the end of the device's portion of the cascade bitstream, the CSOUT pin is driven Low (and into the CS0\* of the downstream device) to enable the downstream device. CSOUT is released by the device at the end of the cascade bitstream and becomes a fully functional user IO.

### CHECK\* - Configuration Check (Input/Output)

CHECK\* is a configuration control pin used to control the Check Function. The Check function takes a bitstream and compares it to the contents of a previously loaded bitstream and notifies the user of any differences. Any differences cause the INIT pin to go Low. During power-on-reset or manual reset, CHECK\* is controlled by the configuration SRAM. The CHECK\* pin will transition from the user programmed state to a CMOS input with a nominal 20K internal pull-up resistor as the SRAM at that location is cleared by the configuration clear cycle. During configuration download, CHECK\* becomes an optional input. It is enabled by default after reset, and may be enabled or disabled via the configuration control register. If the user has disabled the Check Function, the pin remains a user IO.

### OTS - Dual Use Tri State (Input)

OTS is an input pin used to immediately tri-state all user IO. It is enabled by a bit in the configuration control register. Once activated, it is always an input. The OTS tri-state control of Dual-use pins is superseded by the configuration logic's claim on those pins. If the user has disabled the OTS function, the pin remains as User IO.

# 1.2 Clock Interface

CLK- Processor reference clock (input)

This input provides a reference to generate the internal clock used by the processor and the internal peripherals.

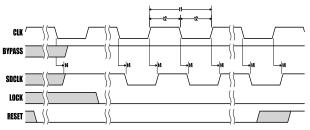

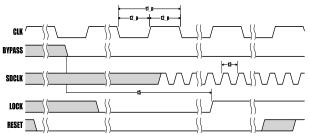

BYPASS- Processor PLL bypass (input with pull-down)

This active high input is used to bypass the internal PLL. When asserted, the processor is directly clocked from the external reference clock. When de-asserted, the processor receives its clock from the internal PLL.

This signal shall be kept static and free from glitches while the processor is operating, as it is not sampled internally. Changing the signal shall only be performed while the processor is under reset otherwise the processor's behavior is not predictable.

### LOCK- PLL lock (output)

When asserted, this active high output indicates the PLL of the processor is locked at a frequency corresponding to four times the frequency of the external processor reference clock.

Caution: this signal is de-asserted as soon as the PLL unlocks.

SKEW[1:0] - Clock tree skew (input with pull-down)

These input signals are used to programme the skew on the internal triplicated clock trees.

These signals shall be kept static and free from glitches while the processor is operating, as they are not sampled internally. Changing these signals shall only be performed while the processor is under reset otherwise the processor's behavior is not predictable.

GCK1 -GCK8: Global clock (input)

8 differential global clocks are available on the reconfigurable unit.

FCK3 - FCK4: Fast clock (input)

1 fast clock is available on the reconfigurable unit part. The 2 pins are multiplexed all together.

# 1.3 Memory Interface

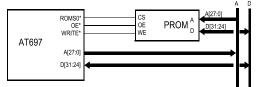

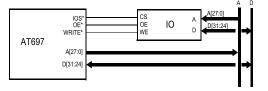

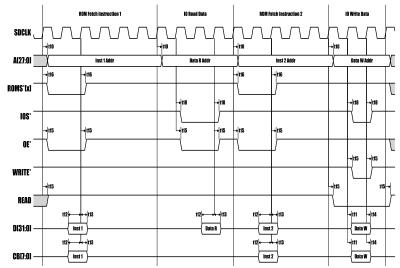

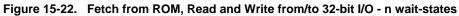

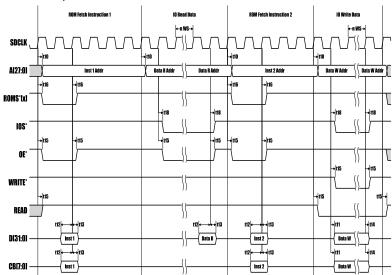

### A[27:0] - Address bus (output)

The lower 28 bits of the 32 bit address bus carry instruction or data addresses during a fetch or a load/store operation to the external memory. The address of the last external memory access remains on the address bus whenever the current access can be made out of the internal cache.

### D[31:0] - Data bus (bi-directional)

The 32-bit bi-directional data bus serves as the interface between the processor and the external memory. The data bus is only driven by the processor during the execution of integer & floating-point store instructions and the store cycle of atomic-load-store instructions. It is kept in high impedance otherwise. However: only D[31:24] are used during an access to an 8-bit area

D[15:0] are used as part of the general-purpose I/O interface whenever all the memory areas (ROM, SRAM & I/O) are 8-bit wide and the SDRAM interface is not enabled

CB[7:0] - Check bits (bi-directional)

These signals carry the EDAC checkbits(1) during a write access to the external memory and are kept in high impedance otherwise. This applies whatever the EDAC activation or not.

While only 7 bits are useful for EDAC protection, CB[7] is implemented to enable programming of FLASH memories and takes the value of MCFG3.tcb[7].

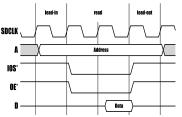

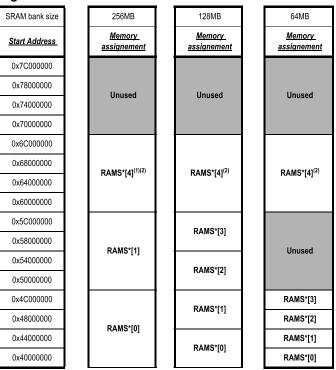

### OE\* - Output enable (output)

This active low output is asserted during a read access to the external memory. It can be used as an output enable signal when accessing PROM & I/O devices.

### READ - Read enable (output)

This active high output is asserted during a read access to the external memory. It can be used as a read enable signal when accessing PROM & I/O devices.

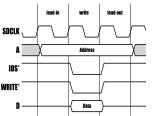

### WRITE\* - Write enable (output)

This active low output is asserted during a write-access to the external memory. It can be used as a write enable signal when accessing PROM & I/O devices.

RWE\*[3:0] - PROM & SRAM byte write-enable (output)

These active low outputs provide individual write strobes for each byte-lane on the data bus: RWE\*[0] controls D[31:24], RWE\*[1] controls D[23:16], RWE\*[2] controls D[15:8] and RWE\*[3] controls D[7:0], and they are set according to the transaction width (word/half-word/byte) and the bus width set for the respective area.

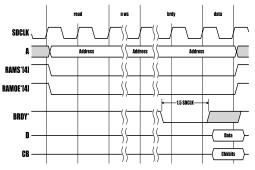

BRDY\* - Bus ready (input)

When driven low, this input indicates to the processor that the current memory access can be terminated on the next rising clock edge. When driven high, this input indicates to the processor that it must wait and not end the current access.

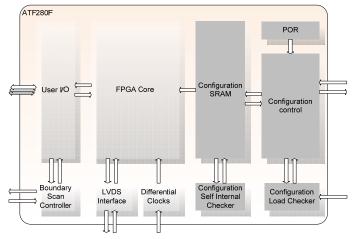

# 1.3.1 PROM

ROMS\*[1:0] - PROM chip-select (output)

These active low outputs provide the chip-select signals for decoding the PROM area. HDC[0] is asserted when the lower half of the PROM area is accessed (0x00000000 - 0x0FFFFFF), while ROMS\* [1] is asserted when the upper half is accessed (0x10000000 - 0x1FFFFFF).

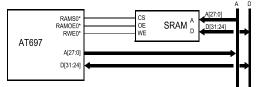

# 1.3.2 SRAM

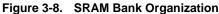

RAMS\*[4:0] - SRAM chip-select (output)

These active low outputs provide the chip-select signals for decoding five SRAM banks.

RAMOE\*[4:0] - SRAM output enable (output)

These active low signals provide an output enable signal for each SRAM bank.

# 1.3.3 I/O

IOS\* - I/O select (output)

This active low output provides the chip-select signal for decoding the memory mapped I/O area.

# 1.3.4 SDRAM

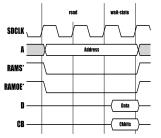

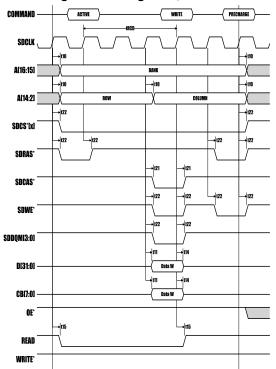

SDCLK - SDRAM clock (output)

This signal provides a reference clock for SDRAM memories. It is a copy of the processor internal clock.

SDCS\*[1:0] - SDRAM chip select (output)

These active low outputs provide the chip select signals for decoding two SDRAM banks.

SDRAS\*- SDRAM row address strobe (output)

This active low output provides the RAS signal (Row Access Strobe) for SDRAM devices.

SDCAS\* - SDRAM column address strobe (output)

This active low output provides the CAS signal (Column Access Strobe) for SDRAM devices.

SDWE\* - SDRAM write strobe (output)

This active low output provides the write strobe for SDRAM devices.

SDDQM[3:0] - SDRAM data mask (output)

These active high outputs provide the DQM strobe (Data Mask) for SDRAM devices.

# 1.4 Input / Output

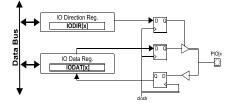

GPIO[15:0] - General Purpose Input Output (bi-directional)

These bi-directional signals can be used as general-purpose inputs or outputs to control external devices. Some of these signals have an alternate function and also serve as inputs or outputs for internal peripherals. Half of them are used as an internal mean of communication.

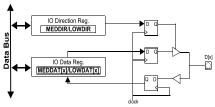

IOx - Programmable I/O (Input/Output)

The programmable IOs are dedicated to user's application. Each programmable IO can independently be configured as input, output or bidirectional IO.

# 1.5 LVDS Input Output

OLVDSx - LVDS Driver (Output) OLVDSx where 'x' is the LVDS channel: A1, A2, B1 or B2 OLVDSxN - Complementary LVDS Driver (Output) OLVDSxN where 'x' is the LVDS channel A1, A2, B1 or B2 ILVDSx - LVDS Receiver (Input) ILVDSx where 'x' is the LVDS channel A1, A2, B1 or B2 ILVDSxN - Complementary LVDS Receiver(Input) ILVDSxN where 'x' is the LVDS channel A1, A2, B1 or B2 LVDS\_REF\_A - reference voltage for LVDSA1 and LVDSA2 LVDS\_REF\_B - reference voltage for LVDSB1 and LVDSB2

# 1.6 DSU Interface

# DSUEN - DSU enable (input)

When asserted, this synchronous active high input enables the DSU unit. If de-asserted, the DSU trace buffer will continue to operate but the processor will not enter debug mode.

This signal is meant for debug purpose and shall be driven low in the final application.

DSURX - DSU receiver (input)

This input provides the serial data stream to the DSU communication link receiver.

This signal is meant for debug purpose and shall be driven low in the final application.

DSUTX - DSU transmitter (output)

This output provides the serial data stream from the DSU communication link transmitter.

DSUACT - DSU active (output)

This active high output is asserted when the processor is in debug mode and controlled by the DSU.

DSUBRE - DSU break enable (input)

A low-to-high transition on this synchronous input signals a break condition and is used to set the processor into debug mode (see "Debug Support Unit" later in this document for specific use).

This signal is meant for debug purpose and shall be driven low in the final application.

# 1.7 Power Supply

PROC\_VCC33–SPARC I/O power (supply) Power supply for the I/O pins of the processor. FPGA\_VCC33– IO power (supply) Power supply for the I/O pins of the reconfigurable unit. PROC\_VDD18– SPARC Core power (supply) Power supply for the core of processor. FPGA\_VDD18– FPGA Core power (supply) Power supply for the core of reconfigurable unit. VSS - I/O ground (supply) Ground supply.

PROC\_VDD\_PLL – processor PLL power supply

Power supply for the PLL. PROC\_VSS\_PLL – processor PLL ground supply Ground supply for the PLL.

# 2. Architecture

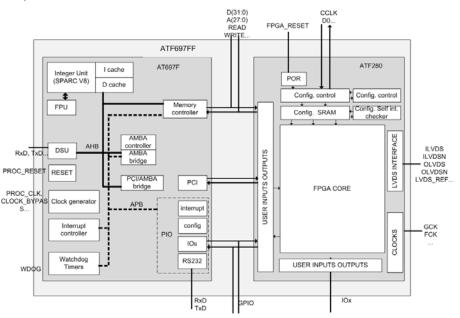

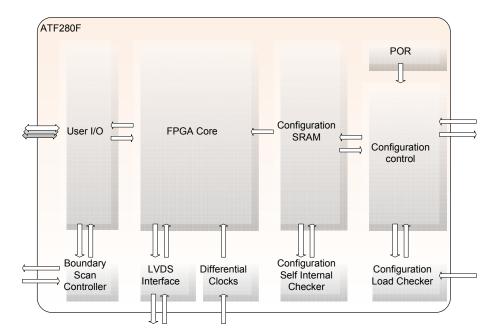

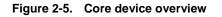

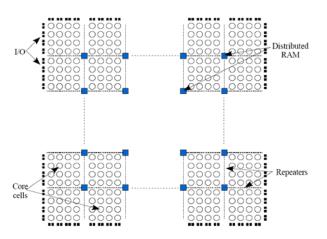

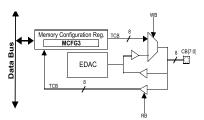

ATF697FF is made of two separate units mounted on the same chip. The ATF697FF processor embeds an IU, and FPU and several pheripherals including 2 32-bits timers, 1 watchdog, 16 GPIO, 2 UART interfaces, 1 PCI interface, an interrupt controller, a debug support unit controller and a flexible memory controller. The reconfigurable unit chip is made of a symmetrical array of identical cells, which are totally reconfigurable.

Figure 1: ATF697FF architecture overview

# 2.1 Architecture of the processor

### 2.1.1 Integer Unit

The ATF697FF processor integer unit is based on the LEON2-FT architecture; it implements the SPARC integer instruction-set defined in the SPARC Architecture Manual version 8.

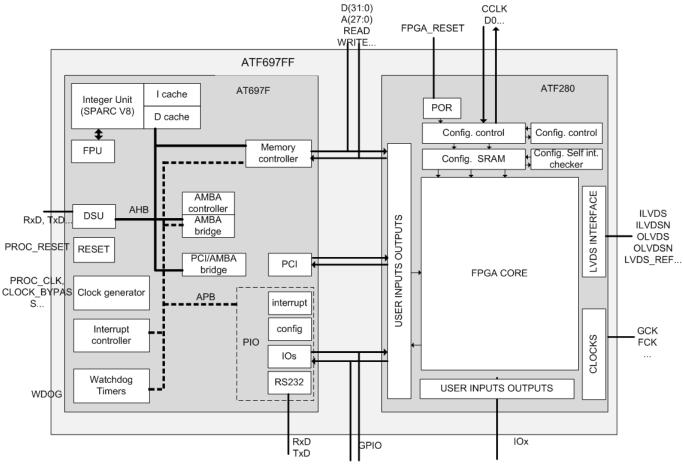

### Figure 2-1. Integer Unit Architecture

To execute instructions at a rate approaching one instruction per clock cycle, the IU employs a five-stage instruction pipeline that permits parallel execution of multiple instructions.

Fetch

The instruction is fetched from the instruction cache is enabled and available or the fetch is forwarded to the memory controller.

Decode

The instruction is placed in the instruction register and decoded. The operands are read from the register file and/or from immediate data and the next instruction computed CALL/Bicc target address are generated.

Execute

Arithmetic, logical and shift operations are performed and the result saved in temporary registers. Memory and JMPL/RETT target address are generated. Pending traps are prioritized and internal traps are taken, if any.

Memory

On a memory load instruction, data is read from the data cache if enabled and available or the read is forwarded to the memory controller. On a memory store instruction, store data is always forwarded to the memory controller and any matching data cache entry is invalidated if enabled.

• Write

The result of any arithmetic, logical, shift or memory/cache read operation is written back to the register file.

All five stages operate in parallel, working on up to five different instructions at a time.

A basic "single-cycle" instruction enters the pipeline and completes in five cycles. By the time it reaches the write stage, four more instructions have entered and are moving through the pipeline behind it. So, after the first five cycles, a single-cycle instruction exits the pipeline and a single-cycle instruction enters the pipeline on every cycle.

Of course, a "single-cycle" instruction actually takes five cycles to complete, but they are called single cycle because with this type of instruction the processor can complete one instruction per cycle after the initial five-cycle delay.

| Instruction                                | Cycles |

|--------------------------------------------|--------|

| Jump and Link (JMPL)                       | 2      |

| Load Double-Word (LDD)                     | 2      |

| Store Single-Word (ST)                     | 2      |

| Store Double-Word (STD)                    | 3      |

| Integer Multiply (SMUL/UMUL/SMULcc/UMULcc) | 5      |

| Integer Divide (SDIV/UDIV/SDIVcc/UDIVcc)   | 35     |

| Taken Trap (Ticc)                          | 4      |

| Atomic Load/Store (LDSTUB)                 | 3      |

| All other IU instructions                  | 1      |

| Single-Precision Multiply (FMULS)          | 16(1)  |

| Double-Precision Multiply (FMULD)          | 21(1)  |

| Single-Precision Divide (FDIVS)            | 20(1)  |

| Double-Precision Divide (FDIVD)            | 36(1)  |

| Single-Precision Square-Root (FSQRTS)      | 37(1)  |

| Double-Precision Square-Root (FSQRTD)      | 65(1)  |

| Single-Precision Absolute Value (FABS)     | 2(1)   |

| Single-Precision Move (FMOVS)              | 2(1)   |

| Single-Precision Negate (FNEGS)            | 2(1)   |

| Convert Single to Double-Precision (FSTOD) | 2(1)   |

| All other arithmetic FPU instructions      | 7(1)   |

### Table 2-1. Cycles per instruction (assuming cache hit and no load interlock)

This value is to be considered "typical". As the execution of FPU operations is operand-dependent, the true execution time can be lower or higher than mentioned.

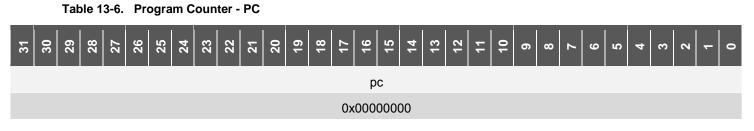

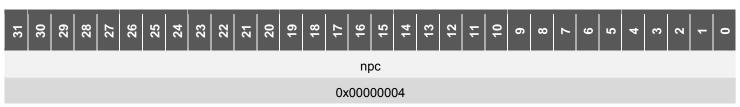

### 2.1.1.1 Program Counters

The Program Counter (PC) contains the address of the instruction currently being executed by the Integer Unit, and the next Program Counter (nPC) holds the address (PC + 4) of the next instruction to be executed (assuming there is no control transfer and a trap does not occur). The nPC is necessary to implement delayed control transfers, wherein the instruction that immediately follows a control transfer may be executed before control is transferred to the target address.

Having both the PC and nPC available to the trap handler allows a trap handler to choose between retrying the instruction causing the trap (after the trap condition has been eliminated) or resuming program execution after the trap causing instruction.

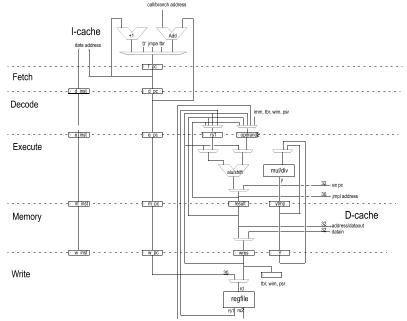

### 2.1.1.2 Windowed Register File

The ATF697FF processor contains a 136×32 register file divided into 8 overlapping windows, each window providing a working registers set at a time. Working registers are used for normal operations and are called r registers.

The 136 registers are 32-bits wide and are divided into a set of 8 global registers and a set of 128 window registers grouped into 8 sets of 24 r registers called windows. At any given time, a program can access 32 active r registers (r0 to r31): 8 (common) global registers (r0 to r7) and 24 window registers (r8 to r31) that are divided by software convention into 8 ins, 8 locals and 8 outs:

- The first 8 globals (r0 to r7) are also called g registers (g0 to g7), they usually hold common data to all functions (as a special case, r0/g0 always returns the value 0 when read and discards the value written to it)

- The next 8 ins (r8 to r15) are also called i registers (i0 to i7), they usually are the input parameters of a function

- The next 8 locals (r16 to r23) are also called I registers (I0 to I7), they usually are scratch registers that can be used for anything within a function

- The last 8 outs (r24 to r31) are also called o registers (o0 to o7), they usually are the return parameters of a function

The register file can be viewed as a circular stack, with the highest window joined to the lowest. Note that each window shares its ins and outs with adjacent windows: outs from a previous window are the ins of the current window and the outs of the current window are the ins of the next window.

### Figure 2-2. Circular Stack of Overlapping Windows

The register file implementation is based on two dual-port RAMs. The first dual-port RAM provides the first operand of a SPARC instruction while the second dual-port RAM provides the second operand unless an immediate value is needed. When applicable, the result of the instruction is written back into the register file, so the two dual-port RAMs always have equal contents.

When one function calls another, the calling function can choose to execute a SAVE instruction. This instruction decrements an internal counter, the current window pointer (CWP), shifting the register window downward. The caller's out registers then become the calling function's in registers and the calling function gets a new set of local and out registers for its own use. Only the pointer changes because the registers and return address do not need to be stored on a stack. The RESTORE/RETT instructions acts in the opposite way

The Window Invalid Mask register (WIM) is controlled by supervisor software and is used by the hardware to determine whether a window overflow or underflow trap is to be generated by a SAVE, RESTORE or RETT instruction.

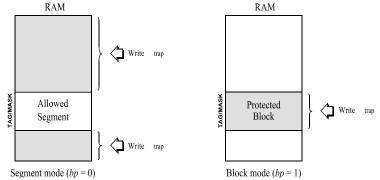

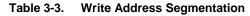

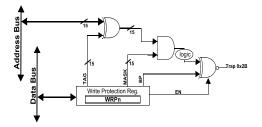

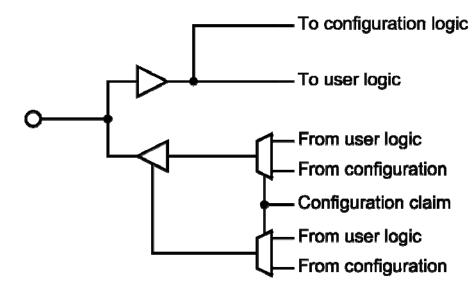

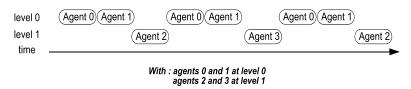

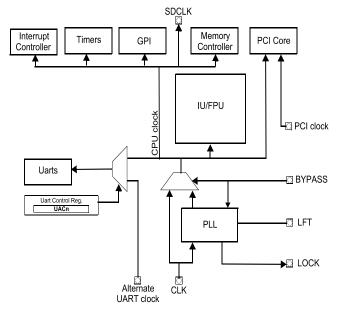

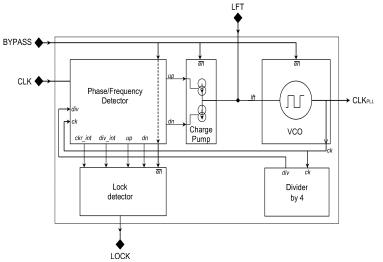

When a SAVE, RESTORE or RETT instruction is executed, the current value of the CWP is compared against the WIM register. If the SAVE, RESTORE, or RETT instruction would cause the CWP to point to an "invalid" register set, a window\_overflow or window\_underflow trap is caused.