## Rad-Hard Reprogrammable FPGA

#### **DATASHEET**

### **Features**

- SRAM-based FPGA designed for Space use

- 280K equivalent ASIC gates

- 14,400 cells (two 3-input LUT or one 4-input LUT, one DFF)

- Unlimited reprogrammability

- SEE-hardened (Configuration RAM, FreeRAM<sup>TM</sup>, DFF, JTAG, I/O buffers)

- · RHBD need for mitigation techniques during design

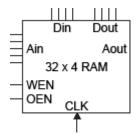

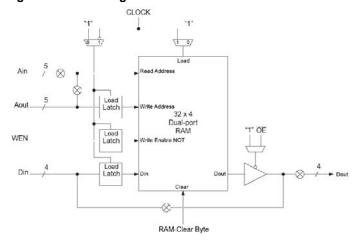

- FreeRAM™

- 115,200 bits of distributed RAM

- Organized in 32x4 blocks of RAM

- Independent of Logic Cells

- Single/Dual port capability

- Global reset option

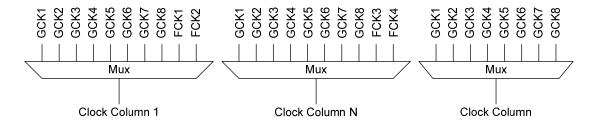

- 8 global clocks and 4 fast clocks

- 8 LVDS transceivers and 8 LVDS receivers

- Cold-sparing and PCI-compliant I/Os

- · Flexible configuration modes

- Master/Slave capability

- Serial/Parallel capability

- Check of the data during FPGA configuration

- Self Integrity Check (SIC) of the configuration during FPGA operation

- Performance

- 50MHz system performance

- 10ns 32X4 FreeRAM™ access time

- Operating range

- Voltages

- 1.65V to 1.95V (Core)

- 3V to 3.6V (Clustered I/Os)

- Temperature

- 55°C to +125°C

- Radiation performance

- Total dose tested up to 300 krads (Si)

- No single event latch-up below a LET of 80 MeV/mg/cm2

- ESD better than 2000V for I/O and better than 1000V for LVDS

- Quality grades

- QML-Q or V

- ESCC

- Ceramic packages

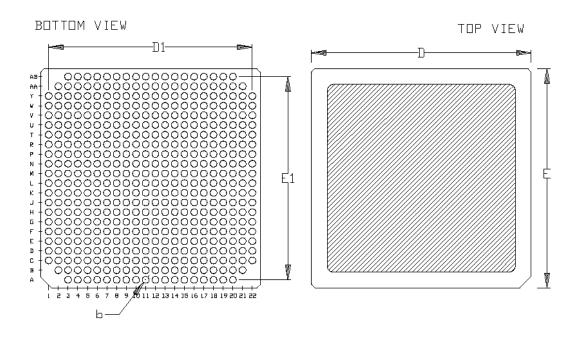

- 256-pin MQFPF (148 I/Os, 8 LVDS Tx and 8 LVDS Rx)

- 352-pin MQFPF (249 I/Os, 8 LVDS Tx and 8 LVDS Rx)

- 472-pin MCGA (308 I/Os, 8 LVDS Tx and 8 LVDS Rx)

- Weight: 14.9g (MCGA Package)

- Design Kit including

- Evaluation board

- Software design tools

- ISP probe

## **Description**

The ATF280F is a radiation-hardened reprogrammable FPGA, especially designed for space applications. For low-power consumption applications, the ATF280F is a new device offering many advantages.

The ATF280F supports an innovative built-in SEU protection, which eliminates the need for Triple-Module-Redundancy (TMR). Its re-programmability makes multiple design iterations possible. Moreover, post-programming burn-in is not necessary.

The Development Kit enables you to evaluate the ATF280F quickly and economically, running simple demonstrations as well as your complete applications. Throughout your development, from concept to final integration, Atmel provides the tools and support to help you successfully integrate your application into the ATF280F.

The ATF280F is available in MCGA/LGA 472 packages and features up to 308 standard I/Os and 16 LVDS I/Os for the user application. The MQFP256 and MQFP352 packages are also available for applications requiring fewer I/O's.

Table 1. ATF280F Summary

| Function                                 | ATF280F |

|------------------------------------------|---------|

| Available ASIC Gates (50% typ. routable) | 280K    |

| Rows x Columns                           | 120x120 |

| Core Cells                               | 14 400  |

| RAM Bits                                 | 115 200 |

| I/O max                                  | 308     |

Figure 2. ATF280F Overview

## **Table of Contents**

| 1. | Glos       | ssary                                                      | 6   |

|----|------------|------------------------------------------------------------|-----|

| 2. | Pin        | Description                                                | 7   |

|    | 2.1        | General Purpose IOs                                        | 7   |

|    | 2.2        | Configuration Interface                                    |     |

|    | 2.3        | LVDS Interface                                             |     |

|    | 2.4        | Clocks Interface                                           | 9   |

|    | 2.5        | JTAG 9                                                     |     |

|    | 2.6        | Power Supply                                               | 10  |

| 3. | Arch       | nitecture                                                  | 11  |

|    | 3.1        | FPGA Core                                                  | 11  |

|    | 3.2        | Configuration Logic                                        | 13  |

|    |            | 3.2.1 POR 13                                               |     |

|    |            | 3.2.2 Configuration Control                                |     |

|    |            | 3.2.3 Configuration SRAM                                   |     |

|    |            | 3.2.4 Configuration Load Checker                           |     |

|    | 3.3        | 3.2.5 Configuration Self Internal Checker                  |     |

|    |            | User I/OLVDS I/O                                           |     |

|    | 3.4<br>3.5 | Clock 14                                                   | 14  |

|    | 3.6        | JTAG 14                                                    |     |

| 4. | Оре        | rating Modes / Lifephases                                  | 15  |

|    | 4.1        | Power-On Reset                                             |     |

|    |            | 4.1.1 Description                                          |     |

|    |            | 4.1.2 Pin Function Availability                            |     |

|    | 4.2        | Manual Reset                                               | 17  |

|    |            | 4.2.1 Description                                          | 17  |

|    |            | 4.2.2 Pin Function Availability                            |     |

|    | 4.3        | Mode Sampling                                              |     |

|    |            | 4.3.1 Description                                          |     |

|    |            | 4.3.2 Pin Function Availability                            | 18  |

|    | 4.4        | Idle 19                                                    | 4.0 |

|    |            | 4.4.1 Description                                          |     |

|    | 4.5        | 4.4.2 Pin Function Availability  Configuration Download    |     |

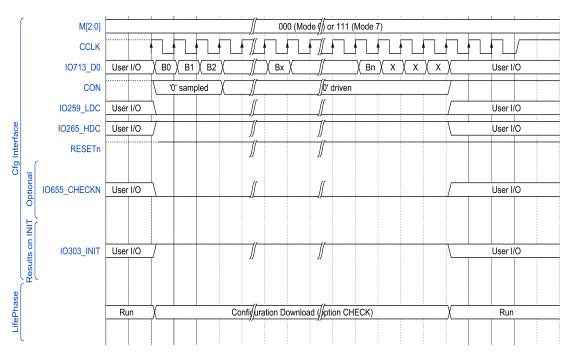

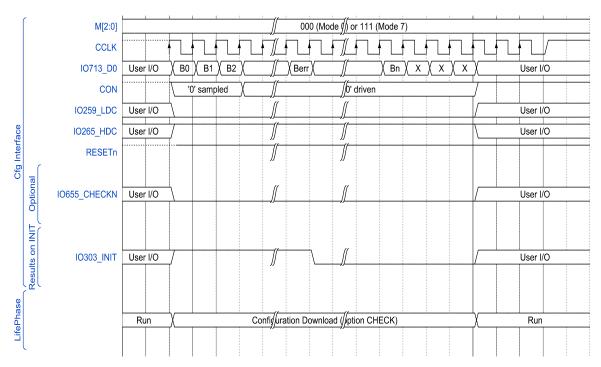

|    | 4.5        | 4.5.1 Description                                          |     |

|    |            | 4.5.1 Description 4.5.2 Pin Function Availability          |     |

|    | 4.6        | Run 21                                                     | 20  |

|    |            | 4.6.1 Description                                          |     |

|    |            | 4.6.2 Pin Function Availability                            | 21  |

| 5. | Con        | figuration Download                                        | 22  |

|    | 5.1        | Serial Configuration                                       | 23  |

|    |            | 5.1.1 Bitstream Structure                                  |     |

|    |            | 5.1.1.1 Null Byte                                          |     |

|    |            | 5.1.1.2 Preamble                                           |     |

|    |            | 5.1.1.3 Configuration Register                             |     |

|    |            | 5.1.1.4 Number of Windows<br>5.1.1.5 Data Window           |     |

|    |            | 5.1.1.6 Checksum Window                                    |     |

|    |            | 5.1.1.7 Recurrent Checksum                                 |     |

|    |            | 5.1.1.8 Postamble                                          |     |

|    | 5.2        | Master Mode – Mode 0                                       |     |

|    |            | 5.2.1 Configuration Download from Power-On Reset in mode 0 |     |

|     |                                         | 5.2.2                              |                                   | ion Download from Manual Reset in mode 0 |                |

|-----|-----------------------------------------|------------------------------------|-----------------------------------|------------------------------------------|----------------|

|     | 5.3                                     | 5.2.3<br>Slave N                   |                                   | Configuration Download in mode 0         |                |

|     | 5.5                                     | 5.3.1                              | Mode 133                          |                                          |                |

|     |                                         | 5.5.1                              | 5.3.1.1                           | Power-On Reset in mode 1                 | 33             |

|     |                                         |                                    | 5.3.1.2                           | Manual Reset in mode 1                   |                |

|     |                                         |                                    | 5.3.1.3                           | Configuration Download in mode 1         |                |

|     |                                         | 5.3.2                              | Mode 740                          | S .                                      |                |

|     |                                         |                                    | 5.3.2.1                           | Power-On Reset in mode 7                 | 40             |

|     |                                         |                                    | 5.3.2.2                           | Manual Reset in mode 7                   | 43             |

|     |                                         |                                    | 5.3.2.3                           | Configuration Download in mode 7         |                |

|     |                                         | 5.3.3                              |                                   | Protection                               |                |

|     |                                         |                                    | 5.3.3.1                           | Low level Errors management              |                |

|     | - 4                                     | D II .                             | 5.3.3.2                           | Checksum Errors management               |                |

|     | 5.4                                     |                                    |                                   | on                                       |                |

|     |                                         | 5.4.1                              |                                   | Structure                                |                |

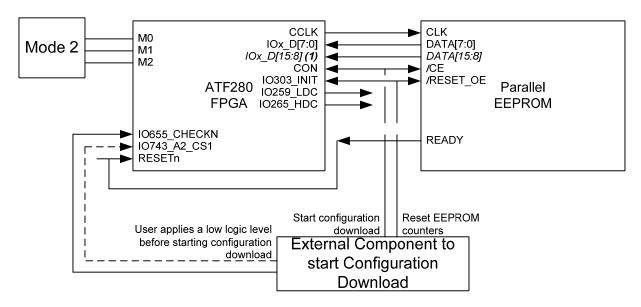

|     |                                         | 5.4.2                              | 5.4.2.1                           | les<br>Mode 2                            |                |

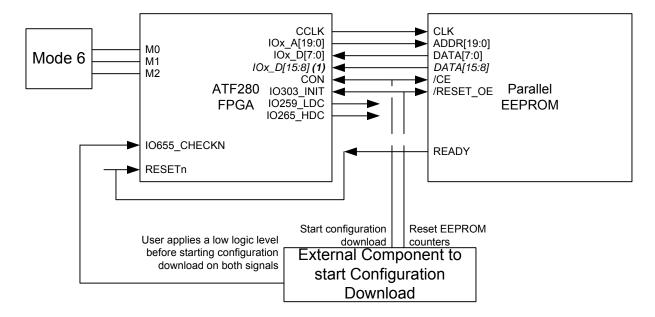

|     |                                         |                                    | 5.4.2.1                           | Mode 6                                   |                |

|     |                                         | 5.4.3                              |                                   | Protection                               |                |

|     |                                         | 0.4.0                              | 5.4.3.1                           | Low level Errors management              |                |

|     |                                         |                                    | 5.4.3.2                           | Checksum Errors management               |                |

|     |                                         |                                    |                                   | -                                        |                |

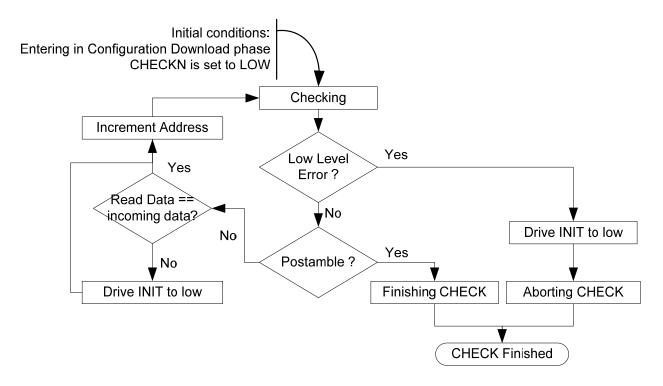

| 6.  | Con                                     | figuration                         | on Integrity                      | y Management                             | 56             |

|     | 6.1                                     | Check                              | function                          |                                          | 56             |

|     | • • •                                   | 6.1.1                              |                                   | n                                        |                |

|     |                                         | 6.1.2                              |                                   | les                                      |                |

|     |                                         | 6.1.3                              | Parallel Me                       | odes                                     | 58             |

|     |                                         | 6.1.4                              | Behavior5                         |                                          |                |

|     | 6.2                                     | Self Int                           |                                   | er function                              |                |

|     |                                         | 6.2.1                              | Description                       | n                                        | 61             |

|     |                                         | 6.2.2                              | Behavior6                         | 2                                        |                |

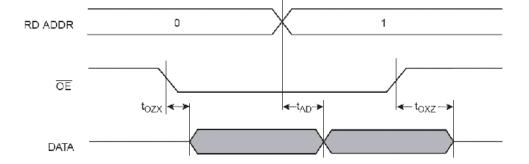

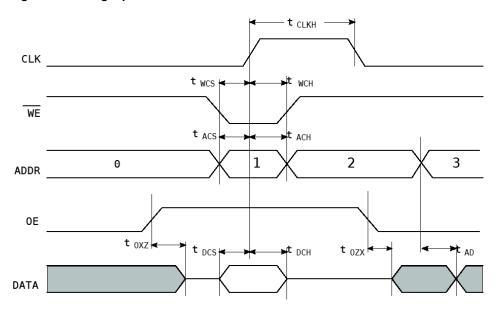

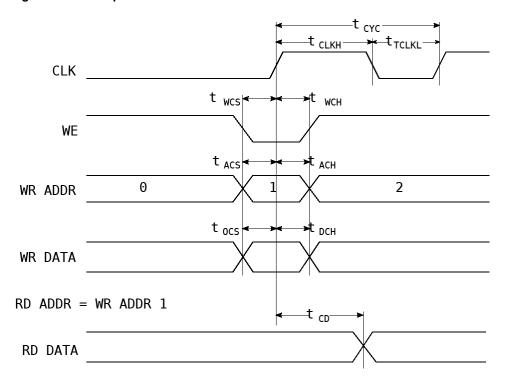

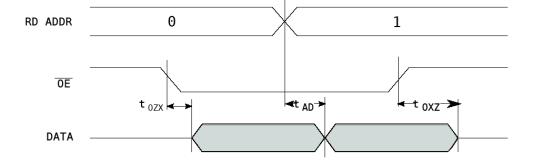

| 7   | Eroo                                    | Dom <sup>TM</sup>                  | 1                                 |                                          | 62             |

| 1.  | riee                                    | Raili                              |                                   |                                          | 03             |

| 8.  | Can                                     | aral Du                            | irnosa Inta                       | rface                                    | 65             |

| Ο.  |                                         |                                    | •                                 |                                          |                |

|     | 8.1                                     |                                    |                                   | tion                                     |                |

|     | 8.2                                     |                                    |                                   |                                          |                |

|     | 8.3                                     |                                    | •                                 | n                                        |                |

|     |                                         | 8.3.1                              |                                   | Configuration                            |                |

|     |                                         | 8.3.2                              |                                   | rce                                      |                |

|     |                                         | 8.3.3                              | •                                 | n                                        |                |

|     | 8.4                                     | 8.3.4                              |                                   | /e                                       |                |

|     | U. <del>T</del>                         | 8.4.1                              | Schmitt 67                        |                                          | 07             |

|     |                                         | 8.4.2                              |                                   |                                          |                |

|     |                                         | 8.4.3                              |                                   | ipliance                                 | 68             |

|     |                                         |                                    |                                   | •                                        |                |

| 9.  | LVD                                     | S Inter                            | face                              |                                          | 69             |

|     | ۵.                                      |                                    |                                   |                                          |                |

| 10. | . Cloc                                  | k Syste                            | em                                |                                          | 70             |

|     |                                         |                                    |                                   |                                          |                |

|     | 10.1                                    | Global                             | Clock                             |                                          | 71             |

|     |                                         |                                    |                                   |                                          |                |

|     | 10.1<br>10.2                            | Fast C                             | lock                              |                                          | 71             |

| 11. | 10.1<br>10.2                            | Fast C                             | lock                              |                                          | 71             |

|     | 10.1<br>10.2<br>. <b>Res</b> e          | Fast Clet System                   | em                                |                                          | 71<br>72       |

|     | 10.1<br>10.2<br>. <b>Res</b> e          | Fast Clet System                   | em                                |                                          | 71<br>72       |

|     | 10.1<br>10.2<br>. <b>Res</b> e          | Fast Clet Systemer Sup             | lockem<br>emply Manag             |                                          | 71<br>72<br>73 |

|     | 10.1<br>10.2<br>Rese                    | Fast Clet Systemer Sup Cold sp     | lock<br>em<br>ply Manag<br>paring | ement                                    | 717273         |

|     | 10.1<br>10.2<br>Research<br>Pow<br>12.1 | Fast Clet System Sup Cold sp Power | emply Manag parings sequencing.   | ement                                    | 71727373       |

| 13. | . JTA | G 75             |             |                              |     |

|-----|-------|------------------|-------------|------------------------------|-----|

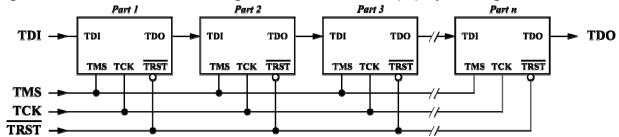

|     | 13.1  | Overvie          | ew          |                              | 75  |

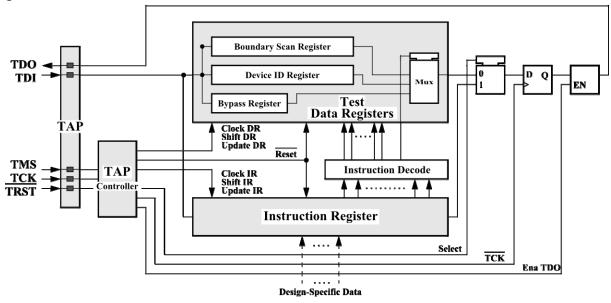

|     | 13.2  | TAP Ar           | chitecture  |                              | 76  |

|     |       | 13.2.1           | TAP Instr   | ructions                     | 76  |

|     |       |                  | 13.2.1.1    | BYPASS                       | 76  |

|     |       |                  | 13.2.1.2    | EXTEST                       |     |

|     |       |                  | 13.2.1.3    | SAMPLE/PRELOAD               |     |

|     |       | 40.00            | 13.2.1.4    | IDCODE                       |     |

|     |       | 13.2.2<br>13.2.3 |             | troller                      |     |

|     |       | 13.2.3           | 13.2.3.1    | Registers<br>Bypass Register |     |

|     |       |                  | 13.2.3.1    |                              |     |

|     |       |                  | 10.2.0.2    | Device in register           |     |

| 14. | Reg   | ister De         | escription. |                              | 80  |

|     | 14.1  | Descrip          | tion        |                              | 80  |

|     |       |                  |             |                              |     |

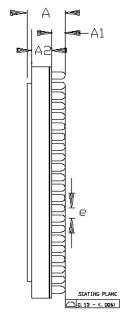

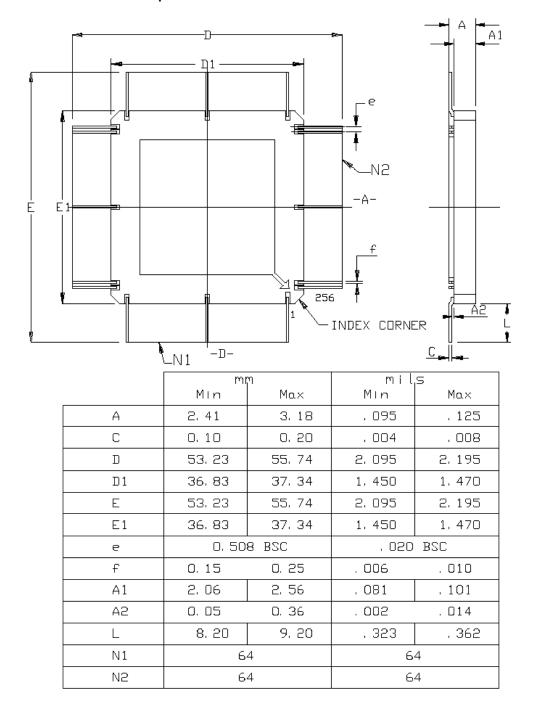

| 15. | Pack  | kage Inf         | formation   |                              | 83  |

|     | 15.1  | Packag           | es Outline. |                              | 83  |

|     |       | 15.1.1           | MCGA 47     | 72 outline                   | 83  |

|     |       | 15.1.2           | QFP 352     | outline                      | 84  |

|     |       | 15.1.3           |             | outline                      |     |

|     | 15.2  |                  |             |                              |     |

|     |       | 15.2.1           |             | ver and Ground Cluster       |     |

|     |       | 15.2.2           |             | S                            |     |

|     |       | 15.2.3           | LVDS clus   | sters                        | 95  |

| 16. | Elec  | trical C         | haracteris  | stics                        | 96  |

|     | 16.1  | Absolut          | e Maximum   | n Ratings                    | 96  |

|     | 16.2  |                  |             |                              |     |

|     | 16.3  |                  |             |                              |     |

|     | 16.4  |                  |             | acteristics                  |     |

|     | 16.5  |                  |             |                              |     |

| 17  | Orda  | arina Int        | formation   |                              | 105 |

| 17. |       | •                |             |                              |     |

|     | 17.1  |                  | _           | Codes                        |     |

|     | 17.2  | AIFZ8U           | Jr ⊑vaiuati | ion Kit Ordering Codes       | 105 |

| 18. | Revi  | sion Hi          | story       |                              | 106 |

# 1. Glossary

**FPGA** Field Programmable Gate Array

**POR** Power On Reset

SRAM Static Random Access Memory

**SEU** Single Event Unit

**CSIC** Configuration Self Internal Checker

## 2. Pin Description

The ATF280F is a built over a standard Atmel AT40K FPGAs architecture in which most of the pins support multiplexed functions. The various functions families available for the ATF280F FPGA are presented here after:

• [GPIO] : General Purpose Input/Output functions,

[CFG] : Configuration management functions,

· [CLOCK] : Clock management functions,

• [LVDS] : LVDS I/O functions,

• [JTAG] : JTAG functions,

[PWR] : Power Supply functions.

In the following section, a complete description of the functions available for each pin is given. The family to which each function belongs to is precised.

## 2.1 General Purpose IOs

### IOx - General Purpose IO

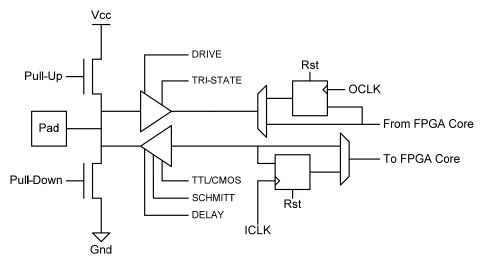

[GPIO] The general purpose IOs are used to communicate with the peripherals interconnected together with the FPGA. The general purpose IOs are highly configurable. A versatile direction management is proposed, allowing configuration of the IO in any of the following directions: input, output or bidirectional. It is also possible to configure Schmitt trigger on inputs, PCI compatibility for output, pull-up/down for input/output...The general purpose IOs provides also the possibility to configure the output buffer current drive.

## 2.2 Configuration Interface

#### **RESETN - FPGA Reset**

[CFG] RESETN is the manual reset of the FPGA. This function reset the configuration download logic. RESETN is internally pulled up to VCC and is active at a low level. Each time RESETN is activated, the FPGA enters Manual Reset lifephase.

## M0, M1, M2 - Configuration Mode

[CFG] The configuration mode pins are used to define the configuration settings of the FPGA. ATF280F samples the configuration mode pins each time a configuration clear cycle is ended.

Caution: The mode pins should not be changed during power-on-reset or manual reset.

#### IO303\_INIT - Multiplexed General Purpose IO / Configuration Error Indicator

[CFG] INIT is used as an error indicator regarding configuration logic. INIT is a bidirectional open drain I/O pulled up to VCC with an internal resistor.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## **CON – Configuration Status Indicator**

[CFG] CON is the FPGA configuration start and status pin. It is a bidirectional open drain I/O pulled up to VCC with an internal resistor.

#### **CCLK – Configuration Clock**

[CFG] CCLK function provides the clock signal used by the configuration logic. Depending on the mode used for configuration download procedure, CCLK function is configured as input or output. For slave mode, the CCLK is configured as an input whereas for master mode, it is configured as an output. When configured in input mode, CCLK is pulled up to VCC with an internal resistor.

## IO713\_D0 - Multiplexed General Purpose IO / Configuration Data

[CFG] D0 is used to transfer configuration data from or to the FPGA configuration SRAM. D0 is used for serial mode configuration and can be used together with D1 to D15 for parallel mode configuration.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

### IOx\_Dy - Multiplexed General Purpose IO / Configuration Data

[CFG] D1:D15 are the upper bits of the 8/16-bit parallel data bus used to download configuration data to the FPGA.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

### IO259\_LDC - Multiplexed General Purpose IO / Configuration Status Indicator

[CFG] LDC indicates that the configuration download is on-going. LDC is an output and is polarized to a low logic level during the configuration.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

### IO265\_HDC - Multiplexed General Purpose IO / Configuration Status Indicator

[CFG] HDC indicates that the configuration download is on-going. HDC is an output and is polarized to a high logic level during the configuration.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## IO547\_CS0 - Multiplexed General Purpose IO / Serial Configuration Chip Select

[CFG] CS0 is an active low chip select used during configuration. It is only available configuration download slave serial mode 1.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

#### IO743\_A2\_CS1 - Multiplexed General Purpose IO / Parallel Configuration Chip Select / Configuration Address

[CFG] CS1 is an active low chip select used during configuration. It is only available configuration download slave parallel mode 2.

[CFG] A0:A19 are used to control external addressing of the memories during downloads.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

### IO720\_GCK6\_CSOUT - Multiplexed General Purpose IO / Clock / Configuration Select Output

[CFG] CSOUT is the configuration pin used to enable the downstream device in an FPGA cascade chain.

[CLOCK] GCK6 function is used to provide clock signals over the entire surface of the FPGA.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

#### IOx\_Az - Multiplexed General Purpose IO / Configuration Address

[CFG] A0:A23 are used to control external addressing of the memories during downloads.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## IOx\_GCKy\_Az - Multiplexed General Purpose IO / Clock / Configuration Address

[CFG] A0:A23 are used to control external addressing of the memories during downloads.

[CLOCK] GCK function is used to provide clock signals over the entire surface of the FPGA.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

### IO655\_CHECKN - Multiplexed General Purpose IO / Configuration Check

[CFG] CHECKN pin is used to enable the CHECK function when combined with a configuration download start.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## IO225\_OTSN - Multiplexed General Purpose IO / Tri-State Command

[CFG] OTSN pin is used to tri-state all the FPGA pins configured as user I/Os.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

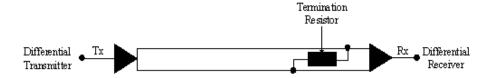

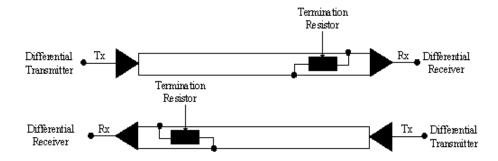

#### 2.3 LVDS Interface

### ILVDSx / ILVDSNx - LVDS Receiver Differential Pair (Input)

[LVDS] ILDVSx/ILVDSNx receiver is a pair of differential signals that comply with the LVDS standard.

## OLVDSx / OLVDSNx - LVDS Driver Differential Pair (Output)

[LVDS] OLDVSx/OLVDSNx transmitter is a pair of differential signals that comply with the LVDS standard.

## **VREF - LVDS reference voltage**

[LVDS] VREF is the reference voltage for LVDS transmission operations. Each LVDS cluster has dedicated VREF source. It shall be accurately power supplied to 1.25V to comply with the LVDS standard.

#### 2.4 Clocks Interface

#### IOx\_FCKy - Multiplexed General Purpose IO / Fast Clock

[CLOCK] FCK function is used to provide high frequency clock to part of the design.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## IOx\_GCKy - Multiplexed General Purpose IO / Clock

[CLOCK] GCK function is used to provide clock signals over the entire surface of the FPGA.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

### IOx\_GCKy\_Az - Multiplexed General Purpose IO / Clock / Configuration Address

[CFG] A0:A23 are used to control external addressing of the memories during downloads.

[CLOCK] GCK function is used to provide clock signals over the entire surface of the FPGA.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## IO720\_GCK6\_CSOUT - Multiplexed General Purpose IO / Clock / Configuration Select Output

[CFG] CSOUT is the configuration pin used to enable the downstream device in an FPGA cascade chain.

[CLOCK] GCK6 function is used to provide clock signals over the entire surface of the FPGA.

[GPIO] General Purpose IO functionalities apply to this signal when used in IO mode.

## 2.5 JTAG

### TRST - Test Reset (pull-down input)

[JTAG] This asynchronous active low input resets the TAP when asserted.

This signal is meant for board testing purpose and shall be driven low in the final application.

## TCK - Test Clock (pull-up input with Schmitt trigger)

[JTAG] This input is used to clock state information and test data into and out of the device during operation of the TAP.

## TMS - Test Mode select (pull-up input)

[JTAG] This synchronous input is used to control the state of the TAP controller in the device.

### TDI - Test data input (pull-up input)

[JTAG] This input is used to serially shift test data and test instructions into the device during TAP operation.

## TDO - Test data output (tri-statable output)

[JTAG] This input is used to serially shift test data and test instructions out of the device during TAP operation.

## 2.6 Power Supply

## **VDD - Core Power Supply**

[PWR] VDD is the power supply input for the ATF280F core.

#### **VCC - I/O Power Supply**

[PWR] VCC is the power supply input for the programmable I/Os. Each I/O cluster has dedicated VCCy sources where 'y' is the cluster number (1 < y < 8).

## VCCB - LVDS I/O Power Supply

[PWR] VCCB is the power supply input for the LVDS I/Os. Each pair of LVDS channels has a dedicated VCCB sources.

#### **VSS - Ground**

## 3. Architecture

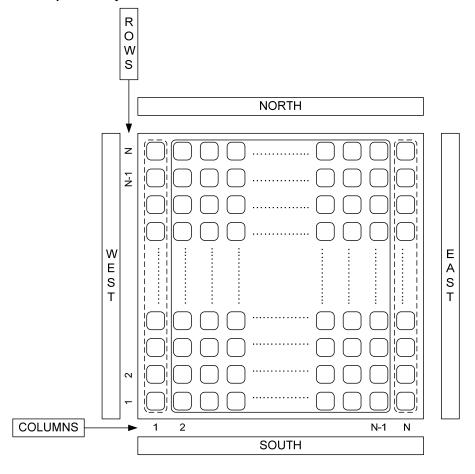

The ATF280F architecture is developed to provide the highest levels of performance, functional density and design flexibility in an FPGA. The cells in the Atmel array are small, efficient and can implement any pair of Boolean functions of (the same) three inputs or any single Boolean function of four inputs. The cell's small size leads to arrays with large numbers of cells, greatly multiplying the functionality in each cell. A simple, high-speed busing network provides fast, efficient communication over medium and long distances.

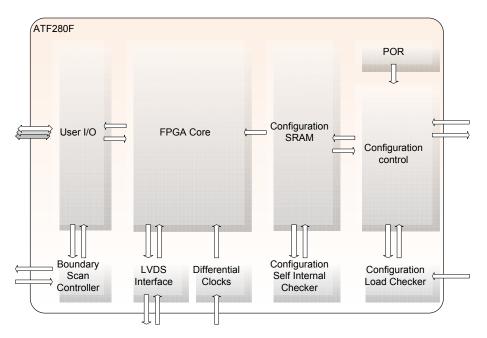

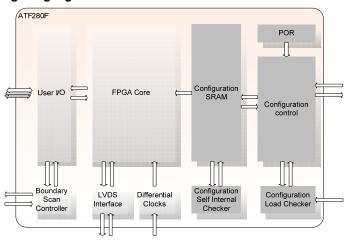

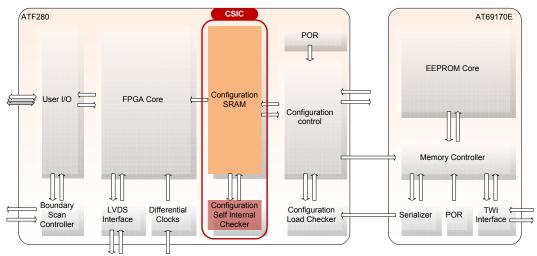

Here is an overview of the internal architecture of the ATF280F:

Figure 3-1. ATF280F Architecture Overview

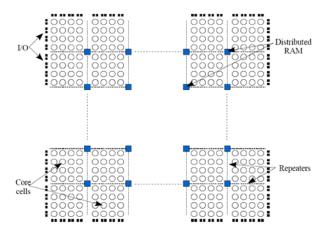

## 3.1 FPGA Core

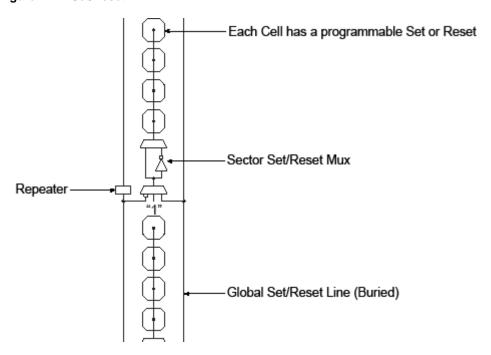

At the heart of the Atmel ATF280F architecture is a symmetrical array of identical cells. The array is continuous from one edge to the other, except for bus repeaters spaced every four cells. At the intersection of each repeater row and column is a 32 x 4 RAM block accessible by adjacent buses.

Figure 3-2. Core device overview

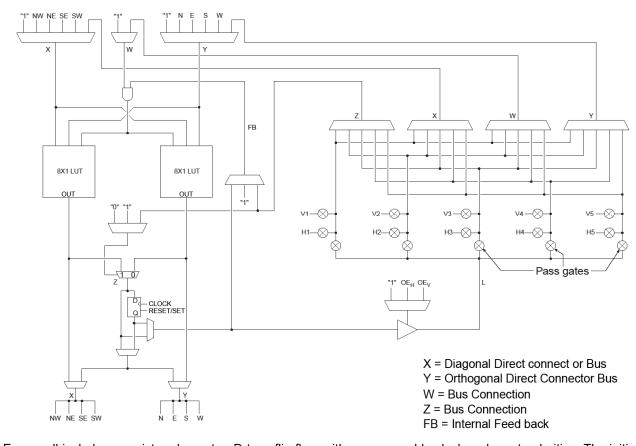

The following figure depicts the ATF280F cell which is a highly configurable logic block based around two 3-input LUTs (8 x 1 ROM), and which can be combined to produce one 4-input LUT. This means that any cell can implement two functions of 3 inputs or one function of 4 inputs.

Figure 3-3. ATF280F Core Cell

Every cell includes a register element, a D-type flip-flop, with programmable clock and reset polarities. The initialization of the register is also programmable. It can be either SET or RESET. The flip-flop can be used to register the output of one of the LUT. It can also be exploited in conjunction with the feedback path element to implement a complete ripple counter stage in a single cell. The registered or unregistered output of each LUT can be feedback within the cell and treated as another input. This allows, for example, a single counter stage to be implemented within one cell without using external routing resources for the feedback connection.

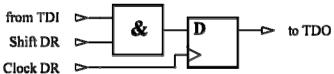

There is also a 2-to-1 multiplexer in every cell, and an upstream AND gate in the "front end" of the cell. This AND gate is an important feature in the implementation of efficient array multipliers as the product and carry terms can both be generated within a single logic cell.

The cell flexibility makes the ATF280F architecture well suited for most of the digital design application areas.

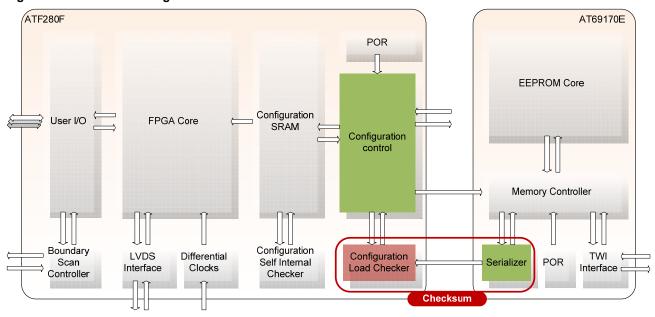

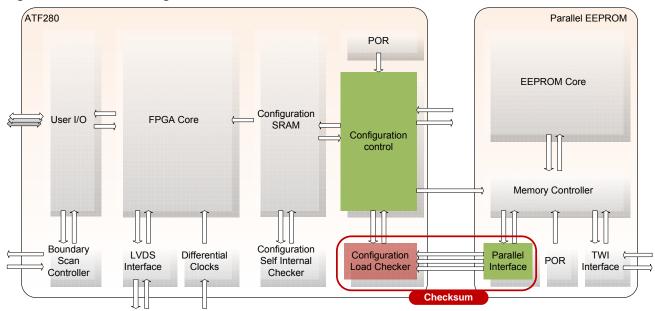

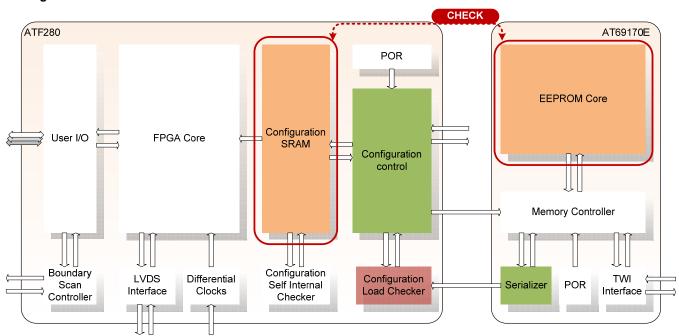

## 3.2 Configuration Logic

The ATF280F FPGA embeds the configuration logic function which is responsible of the configuration download. The configuration download is the operation by which the FPGA configuration SRAM is written in order to load the FPGA application. The configuration download operation is fully detailed in **Configuration Download** section of this document.

The configuration logic is based on the 5 modules highlighted in the following figure.

Figure 3-4. Configuration Logic Highlight

#### 3.2.1 POR

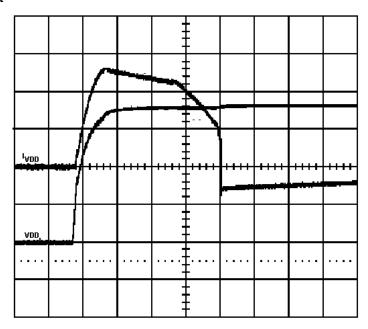

The POR module is an analogic structure which senses the rise of the VDD Power Supply. While VDD is under the POR threshold, all the FPGA logic is maintained in a reset state. Once, the Vdd rises above the POR threshold, all the FPGA logic is activated (leaves reset state) and the FPGA enters in **Power-On Reset** lifephase.

## 3.2.2 Configuration Control

The Configuration Control module is the main module of the configuration logic. It interfaces directly the POR module in order to manage the *Power-On Reset* lifephase. It also manages the configuration SRAM module and is capable to access SRAM cells in read or write mode. It drives the external configuration interface signals used to manage the configuration download. To finish, the configuration control is interconnected with the Configuration Load Checker module to ensure the integrity of the communication protocol.

#### 3.2.3 Configuration SRAM

The configuration SRAM module is made of a large set of SRAM memory points distributed through the whole FPGA. The configuration SRAM is fully cleared during the **Power-On Reset** and **Manual Reset** lifephases. It is written during **Configuration Download** lifephase with the bitstream data in order to configure the FPGA matrix. The configuration SRAM can also be read for integrity verification when using special function such as CHECK function or CSIC function. Refer to **Configuration Integrity Management** section for detailed description of those functions.

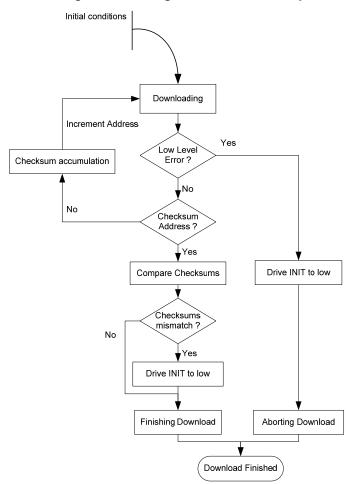

#### 3.2.4 Configuration Load Checker

The Configuration Load Checker module is responsible of the protection of the configuration download link. During the **Configuration Download** lifephase it manages the errors which are protocol relevant and informs the configuration control module of any error in such a way that the configuration control module can drive the appropriate error status signals to inform the system that an error occurred during the configuration.

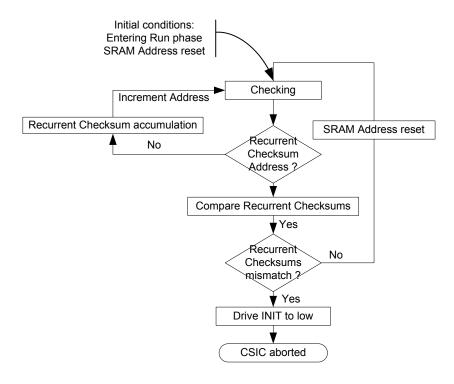

## 3.2.5 Configuration Self Internal Checker

The Configuration Self Internal Checker module is responsible of the integrity of the data during the *Run* lifephase. Once the configuration SRAM is written with the appropriate data, the ATF280F FPGA is capable to check all its effective configuration data and to notify the user in case of errors inside the configuration SRAM. This mechanism is useful to detect SEU that occur on the configuration SRAM.

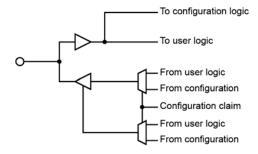

## 3.3 User I/O

Depending on the package selected, the ATF280F features up to 308 general purpose IO for end user application. Each IO can be individually adjusted to the application needs thanks to its extensive configurability. All the IOs are cold sparing, have PCI compliance capability...

Please refer to the General Purpose Interface section for detailed information on the User IOs.

## 3.4 LVDS I/O

The ATF280F provides a 200MHz LVDS interface with cold sparing feature. This interface can be used for high speed communication between the FPGA and its peripherals in order to exchange large amount of data.

Please refer to the LVDS Interface section for detailed information on the LVDS IOs

#### 3.5 Clock

Please refer to the Clock section for detailed information on clock system implemented on the ATF280F.

## **3.6 JTAG**

The ATF280F implements a standard interface compliant with the IEEE 1149.1 JTAG specification. This interface can be used for PCB testing using the JTAG boundary-scan capability.

## 4. Operating Modes / Lifephases

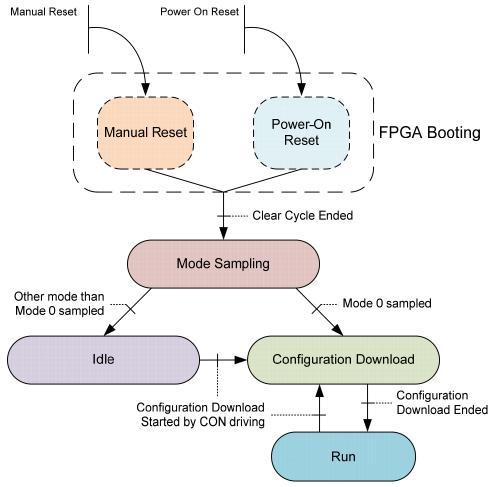

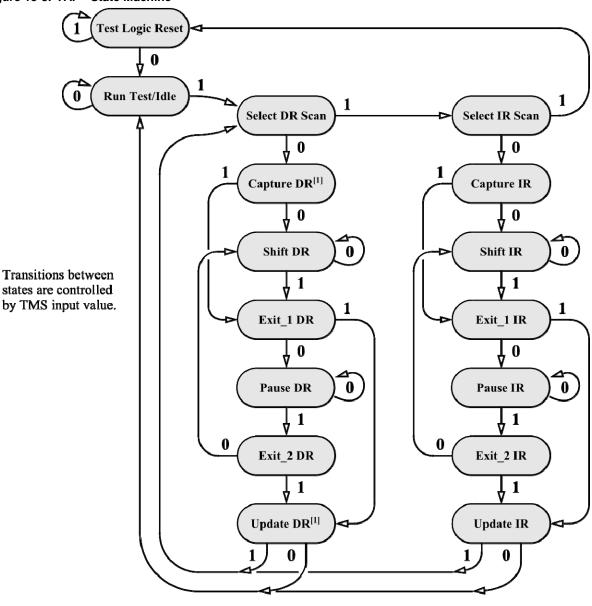

The ATF280F FPGA behaves following a deterministic life cycle. The complete life cycle of the FPGA refers to an optimized number of lifephases that are summarized in the following life cycle.

Figure 4-1. ATF280 FPGA: Life Cycle diagram

For some of the FPGA IOs, the general purpose function of the IO is multiplexed with other functions such as configuration function, clock function... as mentioned in the Pin Description section. For the multiplexed IOs, the function that is activated at a given time is directly dependent from the lifephase currently executed.

In each of the lifephase description here after, the multiplexed IO function availability is presented.

## 4.1 Power-On Reset

## 4.1.1 Description

This **Power-On Reset** lifephase occurs when power is first applied to the part. The FPGA initiates a complete clearing of its internal configuration SRAM (configuration clear cycle) prior entering in Mode Sampling lifephase. Before performing the configuration clear cycle, the power supply is sensed until the threshold voltage is reached then the internal logic activates.

In order to ensure the power supply stability to erase properly each configuration SRAM point, the ATF280F loops and perform configuration clear cycle during hardcoded silicon timing.

## 4.1.2 Pin Function Availability

Table 4-1. Pin Function during Power-On Reset

| ATF280 Pin names | Lifephase = Power-On Reset |

|------------------|----------------------------|

|                  |                            |

| RESET*           | [CFG]                      |

| M0, M1, M2       | [CFG]                      |

| IO303_INIT       | [CFG]                      |

| CON              | [CFG]                      |

| CCLK             | [CFG]                      |

| IO713_D0         | [CFG]                      |

| IOx_Dy           | [GPIO] <sup>1</sup>        |

| IO259_LDC        | [CFG]                      |

| IO265_HDC        | [CFG]                      |

| IO547_CS0        | [GPIO] <sup>1</sup>        |

| IO743_A2_CS1     | [GPIO] <sup>1</sup>        |

| IO720_GCK6_CSOUT | [GPIO] <sup>1</sup>        |

| IOx_Az           | [GPIO] <sup>1</sup>        |

| IOx_GCKy_Az      | [GPIO] <sup>1</sup>        |

| IO655_CHECKN     | [GPIO] <sup>1</sup>        |

| IO225_OTSN       | [GPIO] <sup>1</sup>        |

| IOx              | [GPIO] <sup>1</sup>        |

| IOx_GCKy         | [GPIO] <sup>1</sup>        |

| IOx_FCKy         | [GPIO] <sup>1</sup>        |

Notes: 1. During Power-On Reset lifephase, the ATF280F FPGA configuration SRAM is not configured, all GPIO functions remain in input with pull-up (by default).

## 4.2 Manual Reset

## 4.2.1 Description

This *Manual Reset* lifephase occurs when the RESET function is activated by the user. The FPGA initiates a configuration clear cycle prior entering Mode Sampling lifephase when RESET function is released. As power supplies are already stable, the configuration clear cycle is done once and takes a time which depends of the silicon intrinsic speed and the size of the FPGA matrix.

## 4.2.2 Pin Function Availability

Table 4-2. Pin Function during Manual Reset

| ATF280 Pin names | Lifephase = Manual Reset |

|------------------|--------------------------|

|                  |                          |

| RESET*           | [CFG]                    |

| M0, M1, M2       | [CFG]                    |

| IO303_INIT       | [CFG]                    |

| CON              | [CFG]                    |

| CCLK             | [CFG]                    |

| IO713_D0         | [CFG]                    |

| IOx_Dy           | [GPIO] <sup>1</sup>      |

| IO259_LDC        | [CFG]                    |

| IO265_HDC        | [CFG]                    |

| IO547_CS0        | [GPIO] <sup>1</sup>      |

| IO743_A2_CS1     | [GPIO] <sup>1</sup>      |

| IO720_GCK6_CSOUT | [GPIO] <sup>1</sup>      |

| IOx_Az           | [GPIO] <sup>1</sup>      |

| IOx_GCKy_Az      | [GPIO] <sup>1</sup>      |

| IO655_CHECKN     | [GPIO] <sup>1</sup>      |

| IO225_OTSN       | [GPIO] <sup>1</sup>      |

| IOx              | [GPIO] <sup>1</sup>      |

| IOx_GCKy         | [GPIO] <sup>1</sup>      |

| IOx_FCKy         | [GPIO] <sup>1</sup>      |

Notes: 1. During Manual Reset lifephase, the ATF280F FPGA configuration SRAM is not configured, all GPIO functions remain in input with pull-up (by default).

## 4.3 Mode Sampling

## 4.3.1 Description

This *Mode Sampling* lifephase is entered each time the FPGA has performed either Power-On-Reset or Manual Reset lifephases. In this state, the FPGA starts to drive the configuration logic interface approprietaly and samples the mode pins. Depending on the values sampled through the mode pins, the ATF280F FPGA can be configured in the following modes:

- Mode 0: Master Serial Mode

- Mode 1: Slave Serial Mode with the use of a chip select input

- Mode 7: Slave Serial Mode

- Mode 2: Parallel Serial Mode with the use of a chip select input

- Mode 6: Parallel Serial Mode with the use of an address bus output

These modes directly affect the *Configuration Download* lifephase and lead to five different contexts for these these lifephase.

## 4.3.2 Pin Function Availability

Table 4-3. Pin Function Mode Sampling

| ATF280 Pin names | Lifephase = Mode Sampling |

|------------------|---------------------------|

|                  |                           |

| RESET*           | [CFG]                     |

| M0, M1, M2       | [CFG]                     |

| IO303_INIT       | [CFG]                     |

| CON              | [CFG]                     |

| CCLK             | [CFG]                     |

| IO713_D0         | [CFG]                     |

| IOx_Dy           | [GPIO] <sup>1</sup>       |

| IO259_LDC        | [CFG]                     |

| IO265_HDC        | [CFG]                     |

| IO547_CS0        | [GPIO] <sup>1</sup>       |

| IO743_A2_CS1     | [GPIO] <sup>1</sup>       |

| IO720_GCK6_CSOUT | [GPIO] <sup>1</sup>       |

| IOx_Az           | [GPIO] <sup>1</sup>       |

| IOx_GCKy_Az      | [GPIO] <sup>1</sup>       |

| IO655_CHECKN     | [GPIO] <sup>1</sup>       |

| IO225_OTSN       | [GPIO] <sup>1</sup>       |

| IOx              | [GPIO] <sup>1</sup>       |

| IOx_GCKy         | [GPIO] <sup>1</sup>       |

| IOx_FCKy         | [GPIO] <sup>1</sup>       |

Notes: 1. During Manual Reset lifephase, the ATF280F FPGA configuration SRAM is not configured, all GPIO functions remained in input with pull-up (by default).

## 4.4 Idle

## 4.4.1 Description

This *Idle* lifephase is entered when the FPGA does no activitie. The FPGA enters in this state after Mode Sampling state when configured in slave mode. In Idle state, the configuration logic interface is released.

## 4.4.2 Pin Function Availability

Table 4-4. Pin Function during Idle

| ATF280 Pin names | Lifephase = Idle    |

|------------------|---------------------|

|                  |                     |

| RESET*           | [CFG]               |

| M0, M1, M2       | [CFG]               |

| IO303_INIT       | [GPIO] <sup>1</sup> |

| CON              | [CFG]               |

| CCLK             | [CFG]               |

| IO713_D0         | [GPIO] <sup>1</sup> |

| IOx_Dy           | [GPIO] <sup>1</sup> |

| IO259_LDC        | [GPIO] <sup>1</sup> |

| IO265_HDC        | [GPIO] <sup>1</sup> |

| IO547_CS0        | [GPIO] <sup>1</sup> |

| IO743_A2_CS1     | [GPIO] <sup>1</sup> |

| IO720_GCK6_CSOUT | [GPIO] <sup>1</sup> |

| IOx_Az           | [GPIO] <sup>1</sup> |

| IOx_GCKy_Az      | [GPIO] <sup>1</sup> |

| IO655_CHECKN     | [GPIO] <sup>1</sup> |

| IO225_OTSN       | [GPIO] <sup>1</sup> |

| IOx              | [GPIO] <sup>1</sup> |

| IOx_GCKy         | [GPIO] <sup>1</sup> |

| IOx_FCKy         | [GPIO] <sup>1</sup> |

Notes: 1. During Idle lifephase, the ATF280F FPGA configuration SRAM is not configured, all GPIO functions remained in input with pull-up (by default).

## 4.5 Configuration Download

### 4.5.1 Description

This **Configuration Download** lifephase from a system point of view is a sequence of event managed by the FPGA in order to ensure the configuration of its internal SRAM. This lifephase is entered after Mode Samping state when configured in master mode. Else the FPGA enters this lifephase after Idle state when an external master triggers the start of configuration download (could be either in slave or master mode).

Five different contexts are defined for this lifephase regarding the mode sampled in Mode Sampling.

## 4.5.2 Pin Function Availability

Table 4-5. Pin Function during Configuration Download

|                  | Lifephase = Configuration Download |                              |                              |                              |                              |  |  |

|------------------|------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|--|--|

| ATF280 Pin names | Mode 0                             | Mode 1                       | Mode 7                       | Mode 2                       | Mode 6                       |  |  |

|                  |                                    |                              |                              |                              |                              |  |  |

| RESET*           | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| M0, M1, M2       | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| IO303_INIT       | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| CON              | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| CCLK             | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| IO713_D0         | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| IOx_Dy           | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [CFG]⁴                       | [CFG] <sup>4</sup>           |  |  |

| IO259_LDC        | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| IO265_HDC        | [CFG]                              | [CFG]                        | [CFG]                        | [CFG]                        | [CFG]                        |  |  |

| IO547_CS0        | [GPIO] <sup>1</sup>                | [CFG]                        | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          |  |  |

| IO743_A2_CS1     | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [CFG] <sup>2</sup>           | [CFG] <sup>2</sup>           |  |  |

| IO720_GCK6_CSOUT | [CFG] or [GPIO] <sup>3</sup>       | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> |  |  |

| IOx_Az           | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          |  |  |

| IOx_GCKy_Az      | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          |  |  |

| IO655_CHECKN     | [CFG] or [GPIO] <sup>3</sup>       | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> |  |  |

| IO225_OTSN       | [CFG] or [GPIO] <sup>3</sup>       | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> | [CFG] or [GPIO] <sup>3</sup> |  |  |

| IOx              | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          |  |  |

| IOx_GCKy         | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          |  |  |

| IOx_FCKy         | [GPIO] <sup>1</sup>                | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          | [GPIO] <sup>1</sup>          |  |  |

Notes:

- If entering Configuration lifephase from Idle then the ATF280F FPGA configuration SRAM is not configured: all GPIO functions remained in input with pull-up (by default). Else if entering Configuration lifephase from Run then the ATF280 FPGA configuration SRAM is already configured: all GPIO functions remained in their configured state.

- 2. IO743\_A2\_CS1 has two possibilities regarding [CFG] function. When slave parallel mode 2 is set, CS1 is used as chip select of the FPGA. When slave parallel mode 6 is set, A2 is used to address an external parallel EEPROM.

- 3. IO720\_GCK6\_CSOUT, IO655\_CHECKN and IO225\_OTSN are configured in [CFG] function during configuration download if the appropriate function is activated (respectively cascading mode, CHECK function, Output Tri-State) (Refer to bitstream configuration for more details)

- 4. IOx\_Dy pins ensure the data wide access in 8 or 16 bits. When parallel mode is set (mode 2 or 6), I0x\_D[1:7] are always configured as [CFG] function. By the way, IOx\_D[8:15] are configured as [CFG] function only if 16 bits access is configured (refer to Bitstream configuration for more details) else they remain as [GPIO] function.

## 4.6 Run

## 4.6.1 Description

The *Run* lifephase is the operating state of the FPGA and is design dependent. It means that in this lifephase, the loaded design runs and its own lifephases are taken into account.

## 4.6.2 Pin Function Availability

Table 4-6. Pin Function during Run

| ATF280 Pin names     | Lifephase = Run     |                 |                 |                     |  |  |

|----------------------|---------------------|-----------------|-----------------|---------------------|--|--|

| ATT 200 FIII Hailles | Nominal             | OTS             | CSIC            | Free Run oscillator |  |  |

|                      |                     |                 |                 |                     |  |  |

| RESET*               | [CFG]               | [CFG]           | [CFG]           | [CFG]               |  |  |

| M0, M1, M2           | [CFG]               | [CFG]           | [CFG]           | [CFG]               |  |  |

| IO303_INIT           | [GPIO]              | [GPIO]          | [CFG]           | [GPIO]              |  |  |

| CON                  | [CFG]               | [CFG]           | [CFG]           | [CFG]               |  |  |

| CCLK                 | [CFG]               | [CFG]           | [CFG]           | [CFG] <sup>1</sup>  |  |  |

| IO713_D0             | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IOx_Dy               | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IO259_LDC            | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IO265_HDC            | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IO547_CS0            | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IO743_A2_CS1         | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IO720_GCK6_CSOUT     | [GPIO]or[CLOC<br>K] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK]     |  |  |

| IOx_Az               | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IOx_GCKy_Az          | [GPIO]or[CLOC<br>K] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK]     |  |  |

| IO655_CHECKN         | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IO225_OTSN           | [GPIO]              | [CFG]           | [GPIO]          | [GPIO]              |  |  |

| IOx                  | [GPIO]              | [GPIO]          | [GPIO]          | [GPIO]              |  |  |

| IOx_GCKy             | [GPIO]or[CLOC<br>K] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK]     |  |  |

| IOx_FCKy             | [GPIO]or[CLOC<br>K] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK] | [GPIO]or[CLOCK]     |  |  |

Notes: 1. When using the Free Run Oscillator in mode 0 only (refer to **Register** section about CR13), the CCLK pin is output as clock signal. The user shall take care of this at system level.

## 5. Configuration Download

Configuration is the process by which a design is loaded into an ATF280F FPGA. The ATF280F device is a SRAM based FPGA, this leads to an unlimited reprogrammability capability.

It is possible to configure either the entire device or only a portion of the device. Sections can be configured while others continue to operate undisturbed. The architecture of the ATF280F leads to a maximum bitstream size of 2.5M bits. It is possible to store configuration bit-streams of the ATF280F in one single 4Mbit EEPROM.

Full configuration takes only milliseconds. Partial configuration takes even less time and is a function of design density.

Configuration data is transferred to the device in one of the five modes supported by the ATF280F. Three dedicated input pins M0, M1 and M2 are used to determine the configuration mode.

The ATF280F supports an auto-configuring Master serial mode, two Slave serial modes and two Slave parallel modes. The following table summarizes the ATF280F configuration modes:

Table 5-1. Configuration Mode Overview

| Configuration Download Mode |                |    |    |    |        |                |

|-----------------------------|----------------|----|----|----|--------|----------------|

| Mode                        | Description    | M2 | M1 | МО | CCLK   | Data           |

| 0                           | Master serial  | 0  | 0  | 0  | Output | Serial         |

| 1                           | Slave serial   | 0  | 0  | 1  | Input  | Serial         |

| 7                           | Slave serial   | 1  | 1  | 1  | Input  | Serial         |

| 2                           | Slave parallel | 0  | 1  | 0  | Input  | 8/16 bits Word |

| 6                           | Slave parallel | 1  | 1  | 0  | Input  | 8/16 bits Word |

## 5.1 Serial Configuration

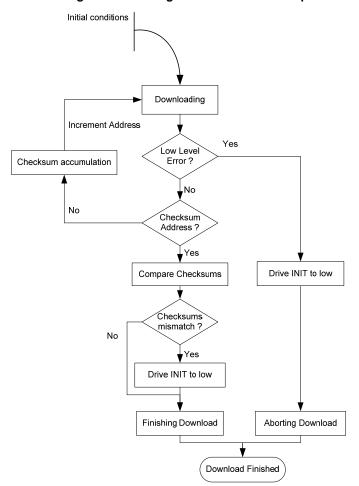

## 5.1.1 Bitstream Structure

The configuration bitstream for the ATF280F FPGA consists in a flexible structured set of data that allows configuration of the FPGA structure but also protection of the configuration data link.

The following table shows the global structure of a bitstream for ATF280F FPGA.

Table 5-2. ATF280F Bitstream structure

| Bitstream decomposition         |               |                  |  |  |  |

|---------------------------------|---------------|------------------|--|--|--|

| Description                     | Sub Zone      | Zone Size (byte) |  |  |  |

| Null byte                       |               | 1                |  |  |  |

| Preamble                        |               | 1                |  |  |  |

| Configuration                   | CR3           | 4                |  |  |  |

| Registers                       | CR2           |                  |  |  |  |

|                                 | CR1           |                  |  |  |  |

|                                 | CR0           |                  |  |  |  |

| Number of Windows               |               | 2                |  |  |  |

| Data Window1                    | Start Address | 3                |  |  |  |

|                                 | Stop Address  | 3                |  |  |  |

|                                 | Data          | Data Size        |  |  |  |

| Data Window2                    | Start Address | 3                |  |  |  |

|                                 | Stop Address  | 3                |  |  |  |

|                                 | Data          | Data Size        |  |  |  |

| Data WindowN 1                  | Start Address | 3                |  |  |  |

|                                 | Stop Address  | 3                |  |  |  |

|                                 | Data          | Data Size        |  |  |  |

| Checksum                        | Start Address | 3                |  |  |  |

|                                 | Stop Address  | 3                |  |  |  |

|                                 | Data          | 1                |  |  |  |

| Recurrent Checksum <sup>2</sup> | Start Address | 3                |  |  |  |

|                                 | Stop Address  | 3                |  |  |  |

|                                 | Data          | 1                |  |  |  |

| Postamble                       |               | 1                |  |  |  |

Notes: 1. N could be at least 1, at maximum 65535.

#### 5.1.1.1 Null Byte

The "null byte" is always present in the ATF280F bitstreams. It is used by the configuration download state machine as a download protocol start indicator.

Its value is always "00000000".

## **5.1.1.2** Preamble

The "preamble" is always present in the ATF280F bitstreams. It is used by the configuration download state machine for verifying that the bitstream proposed on the configuration link is well suited for ATF280F FPGA type.

Its value is always set to "10110111"

### 5.1.1.3 Configuration Register

The configuration register is made of four eight-bit wide registers used to configure the FPGA embedded functions. These register allows configuration of FPGA functions such as clock configuration, IO configuration... options. For the details on the configuration register options content, please refer to the *Registers* section.

The configuration registers are always present in the ATF280F bitstreams.

#### 5.1.1.4 Number of Windows

The number of windows section provides the exact number of windows used in the bitstream to be downloaded. Its value is computed by the FPGA Integrated Design System development tool and is fully dependent from the content of the FPGA application.

The number of windows is always present in an ATF280F bitstream.

#### 5.1.1.5 Data Window

The windows are the zones used to configure the different internal applicative structures of the FPGA. Each window is e made of the following elements:

- A "Start Address" which is a 24 bits word (3 bytes). It is used to identify the starting point of the FPGA

configuration SRAM mapping to be written

- A "Stop Address" which is a 24 bits word (3 bytes). It is used to delimit the end of the window, thus defining the number of data to be written in the configuration SRAM

- The "Data" section which contains the configuration data for the configuration memory itself. It is fully dependent upon the application being downloaded.

The ATF280F bitstream always embeds a minimum of one data windows.

#### 5.1.1.6 Checksum Window

The FPGA Integrated Design System development tool calculates a checksum for each generated bitstream in order to provide the capability to secure the transfer of the data during configuration download. The checksum generated is one byte computed by data accumulation over the configuration registers data and the data of all the windows that precede the checksum window.

The checksum window is used to store this checksum into the FPGA at a defined location. That is why the checksum window is made of:

- A "Start Address" which is a 24 bits word (3 bytes). This address defines the location where the checksum will be written in the FPGA.

- A "Stop Address" which is a 24 bits word (3 bytes) to delimit the end of the window,

- The "Checksum Data"

The checksum window is always present in an ATF280F bitstream.

## 5.1.1.7 Recurrent Checksum

The FPGA Integrated Design System development tool is capable to calculate a recurrent checksum for each generated bitstream. The recurrent checksum is different from the simple checksum. It is used for self integrity checking. The recurrent checksum is computed by data accumulation over the configuration registers data and the data of all the windows that precede the recurrent checksum window.

The "Recurrent Checksum" window is made of the following elements:

- The "Start Address" which is a 24 bits word (3 bytes) to access the Recurrent Checksum location in the FPGA

- The "Stop Address" which is a 24 bits word (3 bytes) to delimit the end of the window

- The "Recurrent Checksum Data"

The recurrent checksum window is optional. It is only available when the recurrent checksum function is activated in the bitstream. For details on the recurrent checksum function usage, please refer to the **Self Integrity Checker function** section.

#### 5.1.1.8 Postamble

The "postamble" is always present in the ATF280F bitstreams. It is used by the configuration download state machine as a download protocol stop indicator indicating the end of the transfer.

Its value is always "10110111".

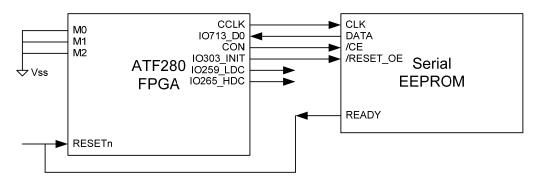

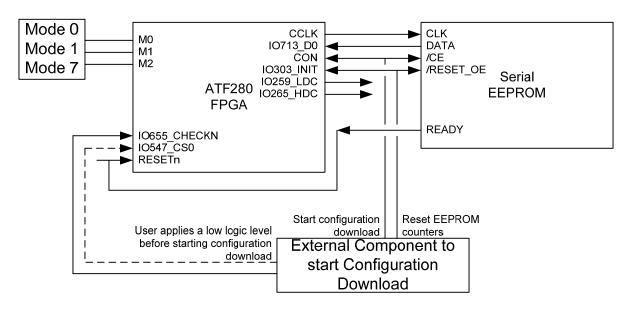

## 5.2 Master Mode – Mode 0

Mode 0 is a master mode. The Master Mode is auto-configuring; that is, after power-on-reset (POR) and the clearing of configuration memory, it self-initiates configuration. The Master Mode uses an internal oscillator to provide CCLK for clocking the external EEPROMs (configurators) which contain the configuration data. CCLK also drives the downstream devices (Slaves) in the configuration cascade chain. Master Serial Mode clocks and receives data from an EEPROM Serial Configuration Memory. After auto-configuration is complete, re-configuration can be initiated manually by the user.

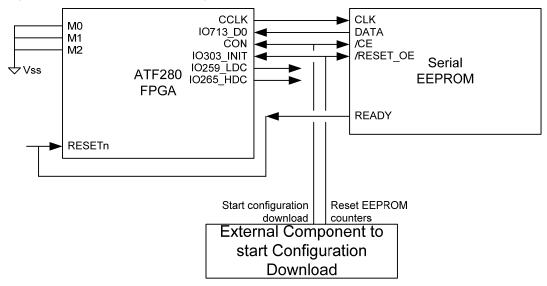

In this mode, the ATF280F is coupled to a serial EEPROM and managed automatically the whole configuration download phase. The automatic configuration download always starts after a Power-On reset or a Manual Reset (Refer to Chapter 3). The following synoptic shows the required interface to be used for automatic configuration download purpose in mode 0.

Figure 5-2. ATF280F automatic configuration download in mode 0

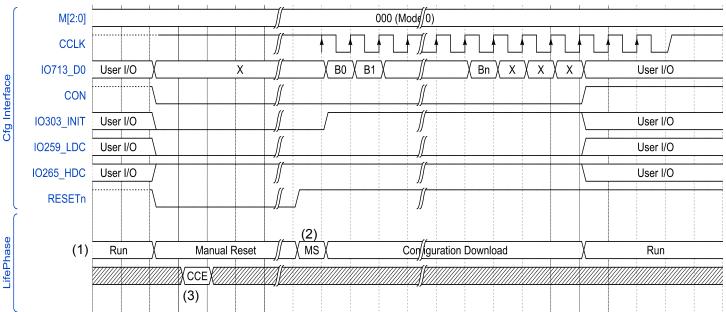

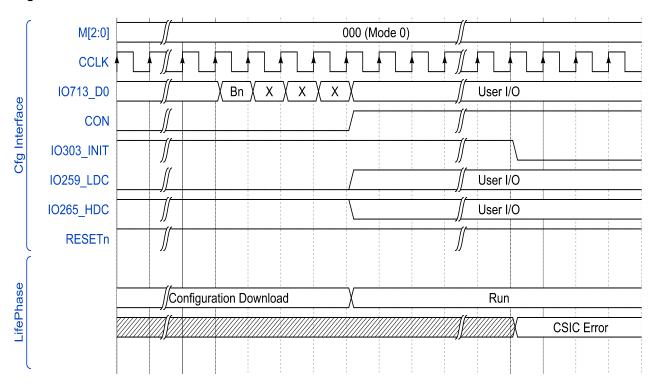

## 5.2.1 Configuration Download from Power-On Reset in mode 0

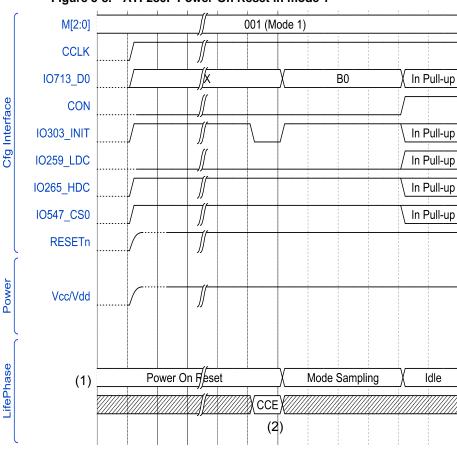

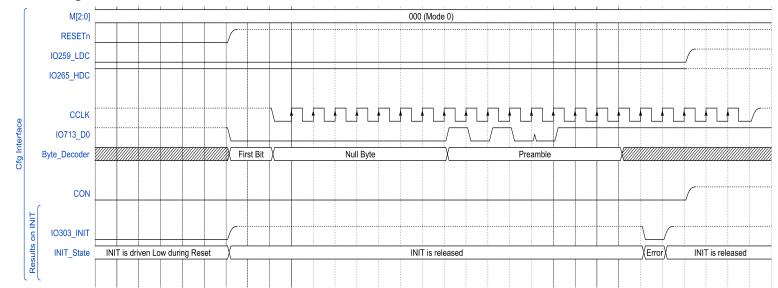

The chronogram described here after presents the sequence of ATF280F from a **Power-On Reset** until **Run**. This is the global overview of ATF280F automatic configuration download after a Power-On Reset.

M[2:0] 000 (Mode 0) **CCLK** B0 B2 Bn Χ Χ User I/O IO713 D0 /k Cfg Interface CON IO303\_INIT User I/O User I/O 10259 LDC User I/O IO265 HDC **RESETn** Power Vcc/Vdd LifePhase Power On Feset Mode Sampling Configuration Download Run (1) Rising CCE (2) (3)

Figure 5-3. ATF280F Configuration Download from Power-On Reset

Notes:

- 1. This line shows the different lifephase viewable in life cycle diagram described in **OperatingModes / Lifephases** section,

- 2. "Rising" means here the rising of power supplies line,

- 3. "CCE" means Clear Cycle End.

[Power-On-Reset]: During the Power-On Reset lifephase, the ATF280F starts to drive the signal regarding the configuration download interfaces as defined below. The end of this lifephase is marked by the rising edge of IO303 INIT pin:

- M0, M1, M2: these signals are inputs and not used,

- · CCLK: this signal is internally pulled-up,

- IO713\_D0: this signal is internally pulled-up,

- CON: this signal is driven to a low logic level,

- IO303\_INIT: this signal is internally pulled-up until the end of the Clear Cycle operation (CCE). At this time, IO303\_INIT is driven to a low logic level during approximatively 1 us,

- IO259\_LDC: the Low During Configuration is driven to a low logic level,

- IO265\_HDC: the High During Configuration is driven to a high logic level,

- RESETN: this signal is an input which has no effect during the Power-On Reset lifephase.

[Mode Sampling]: During the Mode Sampling lifephase, the ATF280F continues to drive the signal regarding configuration download interfaces. In addition, Mode Pins (M0, M1, M2) are sensed:

- M0, M1, M2: these signals are inputs and sensed to determine the used mode. If mode 0 is sampled (as shown in the figure above), the automatic configuration download starts.

- CCLK: this signal is internally pulled-up,

- IO713 D0: this signal takes the value ouput by the EEPROM (first bit of the EEPROM),

- CON: this signal is driven to a low logic level,

- IO303 INIT: this signal is internally pulled-up,

- IO259\_LDC: the Low During Configuration is driven to a low logic level,

- IO265 HDC: the High During Configuration is driven to a high logic level,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

[Configuration Download]: During the Configuration Download lifephase, the ATF280F continues to drive the signal regarding configuration download interfaces, this lifephase starts when CCLK pin is outure:

- M0, M1, M2: these signals remain inputs and are not used anymore,

- CCLK: this signal is output as clock source for the serial EEPROM memory. At each rising edge of CCLK, the EEPROM memory outputs a new bit while the ATF280F senses the previous bit. By default, the CCLK frequency toggles at a frequency of approximatively 900 KHz.

- IO713\_D0: this signal is sampled by the FPGA at each rising edge of CCLK. It is the DATA outure of the EEPROM memory,

- CON: this signal is driven to a low logic level,

- IO303\_INIT: this signal is internally pulled-up and is used as an error monitoring pin. Refer to **Data Link Protection** section for serial configuration,

- IO259\_LDC: the Low During Configuration is driven to a low logic level,

- IO265\_HDC: the High During Configuration is driven to a high logic level,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

[Run]: Once configured, the ATF280F enters in Run lifephase. In this lifephase, the loaded application runs and its own lifephases are taken into account. This lifephase is entered few CCLK cycles after the ATF280F has sensed the postamble, it then releases the configuration interface signals and all multiplexed signals are set to their GPIO function:

- M0, M1, M2: these signals remain inputs and are not used anymore,

- CCLK: this signal is an input with pull-up and is not used anymore.

- IO713 D0: this signal becomes a User I/O and takes its application configuration,

- CON: this signal is released to a high logic level,

- IO303 INIT: this signal becomes a User I/O and takes its application configuration,

- IO259 LDC: this signal becomes a User I/O and takes its application configuration,

- IO265\_HDC: this signal becomes a User I/O and takes its application configuration,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

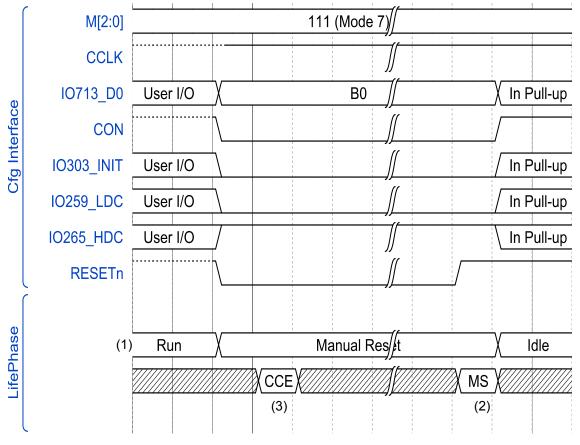

### 5.2.2 Configuration Download from Manual Reset in mode 0

The chronogram described here after presents the sequence of ATF280F from a **Manual Reset** until **Run**. This is the global overview of ATF280F automatic configuration download after a Manual Reset.

Figure 5-4. ATF280F: Configuration Download from Manual Reset

Notes:

- This line shows the different lifephase viewable in life cycle diagram described in OperatingModes / Lifephases section,

- 2. "MS" means **Mode Sampling** lifephase,

- 3. "CCE" means Clear Cycle End.

[Manual Reset]: During the Manual Reset lifephase, the ATF280F starts to drive the signal regarding the configuration download interfaces as defined below. This phase is entered when the RESETN pin is activated. The end of this lifephase is marked by the rising edge of IO303\_INIT pin. During Manual Reset lifephase, the Clear Cycle operation (ended by CCE in the figure above) starts immediately and is performed in approximatively 2 ms. If the RESETN pin is activated during less than the 2 ms required for the Clear Cycle operation, the ATF280F remains in Manual Reset until CCE time:

- M0, M1, M2: these signals are inputs and not used,

- CCLK: this signal is internally pulled-up,

- IO713\_D0: this signal is internally pulled-up,

- CON: this signal is driven to a low logic level,

- IO303 INIT: this signal is driven low until the RESETN pin is released,

- IO259 LDC: the Low During Configuration is driven to a low logic level,

- IO265\_HDC: the High During Configuration is driven to a high logic level,

- RESETN: this signal is an input which is active during Manual Reset lifephase.

[Mode Sampling]: During the Mode Sampling lifephase, the ATF280F continues to drive the signal regarding configuration download interfaces. In addition, Mode Pins (M0, M1, M2) are sensed:

- M0, M1, M2: these signals are inputs and sensed to determine the used mode. If mode 0 is sampled (as shown in the figure above), the automatic configuration download starts.

- CCLK: this signal is internally pulled-up,

- IO713\_D0: this signal takes the value ouput by the EEPROM (first bit of the EEPROM),

- CON: this signal is driven to a low logic level,

- IO303 INIT: this signal is internally pulled-up,

- IO259\_LDC: the Low During Configuration is driven to a low logic level,

- IO265\_HDC: the High During Configuration is driven to a high logic level,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

[Configuration Download]: During the Configuration Download lifephase, the ATF280F continues to drive the signal regarding configuration download interfaces, this lifephase starts when CCLK pin is outut:

- M0, M1, M2: these signals remain inputs and are not used anymore,

- CCLK: this signal is output as clock source for the serial EEPROM memory. At each rising edge of CCLK, the EEPROM memory outputs a new bit while the ATF280F senses the previous bit. By default, the CCLK frequency toggles at a frequency of approximatively 900 KHz.

- IO713\_D0: this signal is sampled by the FPGA at each rising edge of CCLK. It is the DATA outut of the EEPROM memory,

- CON: this signal is driven to a low logic level,

- IO303\_INIT: this signal is internally pulled-up and is used as an error monitoring pin Refer to **Data Link Protection** section for serial configuration,

- IO259 LDC: the Low During Configuration is driven to a low logic level,

- IO265\_HDC: the High During Configuration is driven to a high logic level,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

[Run]: Once configured, the ATF280F enters in Run lifephase. In this lifephase, the loaded application runs and its own lifephases are taken into account. This lifephase is entered few CCLK cycles after the ATF280F has sensed the postamble, it then releases the configuration interface signals and all multiplexed signals are set to their GPIO function:

- M0, M1, M2: these signals remain inputs and are not used anymore,

- CCLK: this signal is an input with pull-up and is not used anymore,

- IO713 D0: this signal becomes a User I/O and takes its application configuration,

- CON: this signal is released to a high logic level.

- IO303 INIT: this signal becomes a User I/O and takes its application configuration,

- IO259\_LDC: this signal becomes a User I/O and takes its application configuration,

- IO265 HDC: this signal becomes a User I/O and takes its application configuration,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

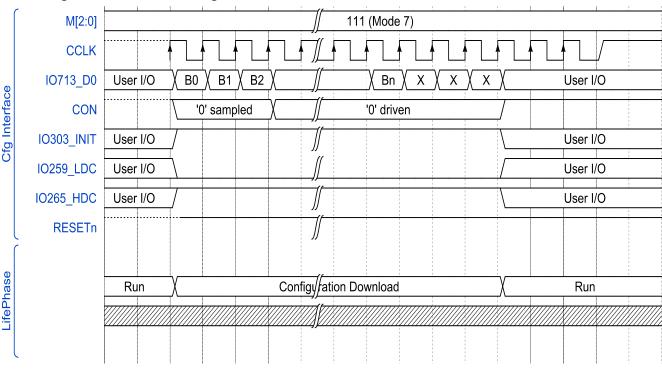

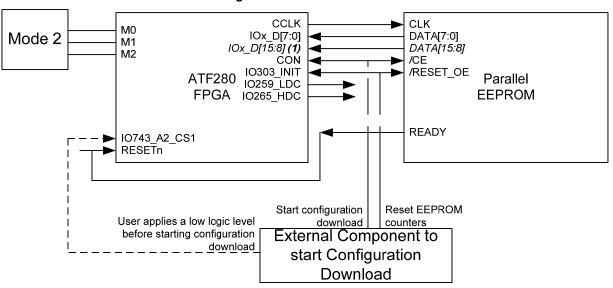

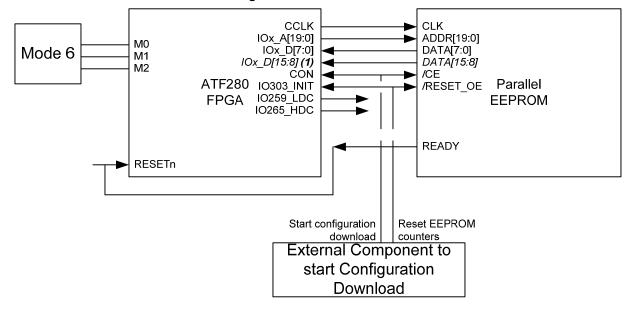

#### 5.2.3 Restart of Configuration Download in mode 0

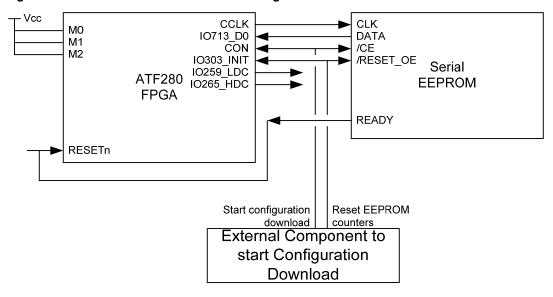

In mode 0, it is possible to restart the configuration download phase without proceding to a FPGA reboot (Power-On reset or Manual Reset). For this, it is required to use an external component in order to trig the start of the configuration download. The following synoptic shows the required signal to be used for restart of configuration download purpose in mode 0.

Figure 5-5. ATF280F restart configuration download in mode 0

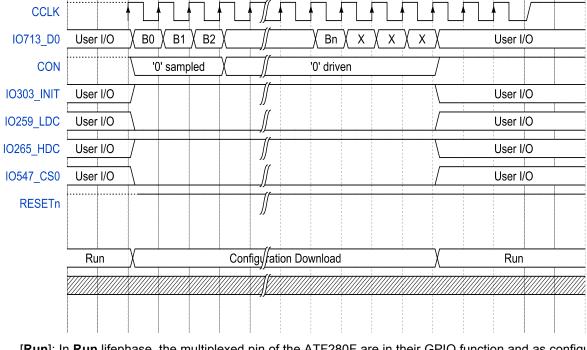

The chronogram described here after presents the sequence of ATF280F from a Run until Run. This is the global overview of ATF280F restart of configuration download when in Run.

M[2:0] 000 (Mode 0) **CCLK** IO713\_D0 B0 В1 B2 Bn User I/O User I/O Cfg Interface CON '0' sampled '0' driven IO303\_INIT User I/O User I/O 10259 LDC User I/O User I/O IO265 HDC User I/O User I/O **RESETn** LifePhase Configy/ration Download Run Run

Figure 5-6. ATF280F: Restart of Configuration Download in mode 0

[Run]: In Run liefphase, the multiplexed pin of the ATF280F are in their GPIO function and as configured by the already loaded application. This lifephase is exiting to enter in **Configuration Download** as soon as the CON pin is driven to a low logic level by an external master:

- M0, M1, M2: these signals remain inputs and are not used anymore (Mode is already sampled),

- CCLK: this signal is an input with pull-up and is not used,

- IO713 D0: this signal remains a User I/O,

- CON: this signal is released to a high logic level by the ATF280F itself,

- IO303 INIT: this signal remains a User I/O,

- IO259\_LDC: this signal remains a User I/O,

- IO265\_HDC: this signal remains a User I/O,

- RESETN: this signal is an input which immediately reset the configuration logic to a Manual Reset lifephase.

[Configuration Download]: During the Configuration Download lifephase, the ATF280F starts to drive the signal regarding configuration download interfaces, this lifephase starts when CON is lowered by an external master component:

- M0, M1, M2: these signals remain inputs and are not used anymore,

- CCLK: this signal is output as clock source for the serial EEPROM memory. At each rising edge of CCLK, the EEPROM memory outputs a new bit while the ATF280F senses the previous bit. By default, the CCLK frequency toggles at a frequency of approximatively 900 KHz.

- IO713\_D0: this signal is sampled by the FPGA at each rising edge of CCLK. It is the DATA outut of the EEPROM memory,

- CON: this signal shall be first maintained to a low logic level by an external master component. The

configuration download starts immediately and CCLK is directly output. Once the ATF280F has sampled the

CON pin to low during three CCLK periods, it starts to drive the CON pin to a low logic level. Then the external

master component shall release the CON signal,