SLES214C-DECEMBER 2007-REVISED SEPTEMBER 2010

# 4-Channel Low-Power PAL/NTSC/SECAM Video Decoder With Independent Scalers and Fast Lock

Check for Samples: TVP5154A

### 1 Introduction

#### 1.1 Features

- Four Separate Video Decoder Channels With Features for Each Channel:

- Accept NTSC (J, M, 4.43), PAL (B, D, G, H, I, M, N, Nc), and SECAM (B, D, G, K, K1, L)

Video

- Support ITU-R BT.601 Standard Sampling

- High-Speed 9-Bit Analog-to-Digital Converter (ADC)

- Two Composite Inputs or One S-Video Input (for Each Channel)

- Fully Differential CMOS Analog Preprocessing Channels With Clamping and Automatic Gain Control (AGC) for Best Signal to Noise (SNR) Performance

- Brightness, Contrast, Saturation, Hue, and Sharpness Control Through Inter-Integrated Circuit (I<sup>2</sup>C)

- Complementary 4-Line (3-H Delay) Adaptive Comb Filters for Both Cross-Luminance and Cross-Chrominance Noise Reduction

- Patented Architecture for Locking to Weak, Noisy, or Unstable Signals

- Four Independent Polymorphic Scalers

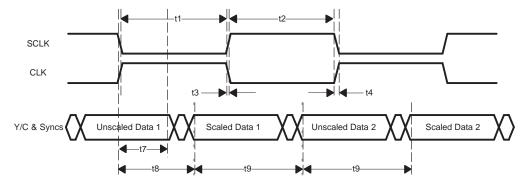

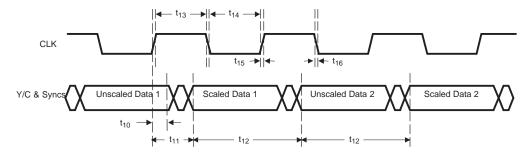

- Single or Concurrent Scaled and Unscaled Outputs Via Dual Clocking Data, Interleaved 54-MHz Data or Single 27-MHz Clock

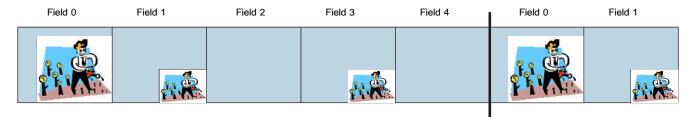

- Scaled/Unscaled Image Toggle Mode Gives Variable Field Rate for Both Scaled and Unscaled Video

- Low Power Consumption: 700 mW Typical

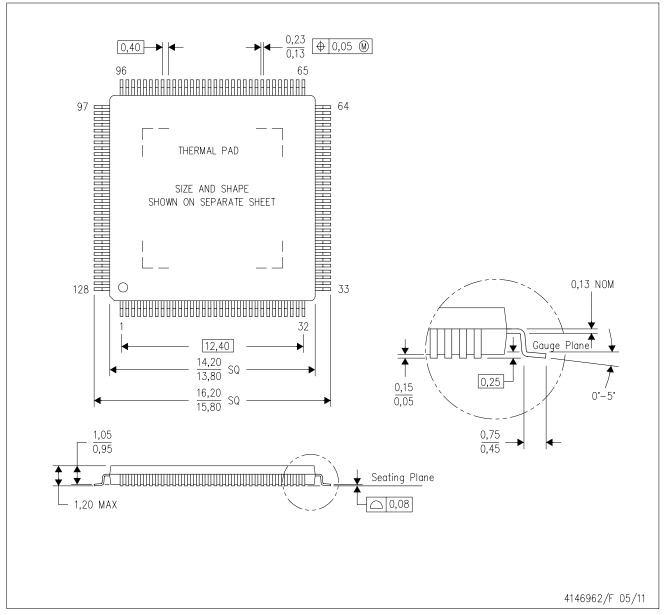

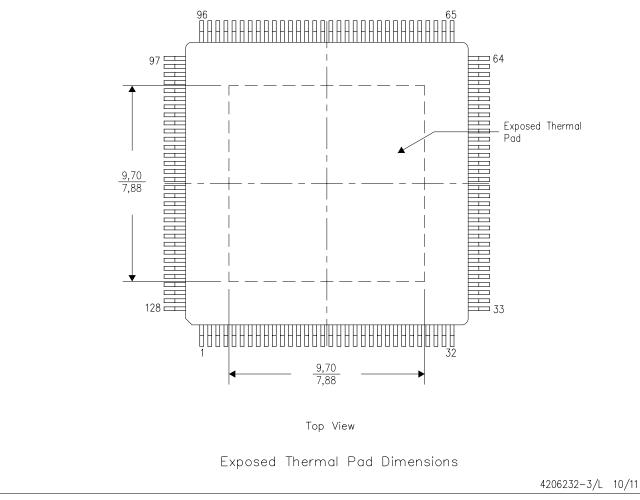

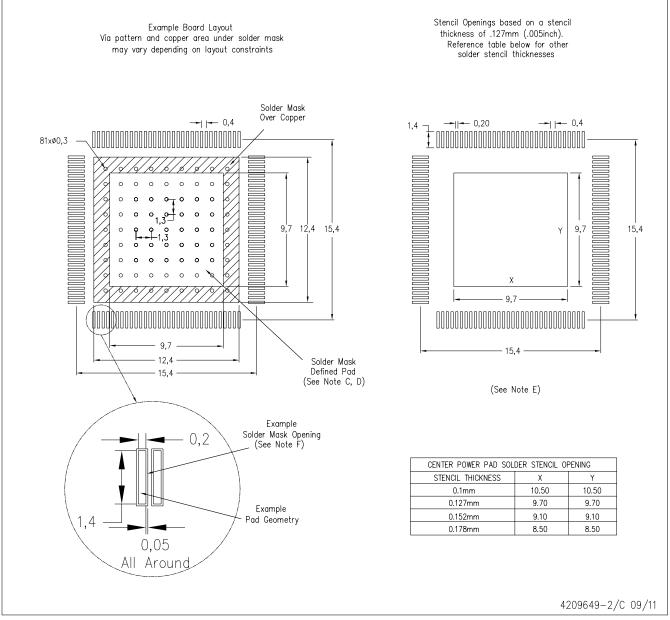

- 128-Pin Thin Quad Flat Pack (TQFP) Package

- Single 14.31818-MHz Crystal for All Standards and All Channels

- Internal Phase-Locked Loop (PLL) for Line-Locked Clock (Separate for Each Channel) and Sampling

- Sub-Carrier Genlock Output for Synchronizing Color Sub-Carrier of External Encoder

- Standard Programmable Video Output Format

- ITU-R BT.656, 8-Bit 4:2:2 With Embedded Syncs

- 8-Bit 4:2:2 With Discrete Syncs

- Advanced Programmable Video Output Formats

- 2x Over-Sampled Raw Vertical Blanking Interval (VBI) Data During Active Video

- Sliced VBI Data During Horizontal Blanking or Active Video

- VBI Modes Supported:

- Teletext (NABTS, WST)

- Closed-Caption Decode With FIFO, and Extended Data Services (EDS)

- Wide Screen Signaling (WSS), Video Program System (VPS), Copy Generation Management System (CGMS), Vertical Interval Time Code (VITC)

- Gemstar 1x/2x Electronic Program Guide Compatible Mode

- Custom Configuration Mode Allows User to Program the Slice Engine for Unique VBI Data Signals

- Improved Fast Lock Mode Can Be Used When Input Video Standard Is Known and Signals on Switching Channels Are Clean

- Four Possible I<sup>2</sup>C Addresses Allowing 16 Decoder Channels on a Single I<sup>2</sup>C Bus

- Available in Commercial (0°C to 70°C) and Industrial (-40°C to 85°C) Temperature Ranges

# 1.2 Description

The TVP5154A device is a 4-channel, low-power, NTSC/PAL/SECAM video decoder. Available in a space-saving 128-pin thin quad flat pack (TQFP) package, each channel of the TVP5154A decoder converts NTSC, PAL, or SECAM video signals to 8-bit ITU-R BT.656 format. Discrete syncs are also

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

available. All four channels of the TVP5154A are independently controllable. The decoders share one crystal for all channels and for all supported standards. The TVP5154A can be programmed using a single inter-integrated circuit (I<sup>2</sup>C) serial interface. The decoder uses a 1.8-V supply for its analog and digital supplies, and a 3.3-V supply for its I/O. The optimized architecture of the TVP5154A decoder allows for low power consumption. The decoder consumes less than 720 mW of power in typical operation.

Each channel of the TVP5154A is an independent video decoder with a programmable polymorphic scaler. Each channel converts baseband analog video into digital YCbCr 4:2:2 component video, which can then be scaled down to any resolution to 1/256 vertical and 15-bit horizontal in 2-pixel decrements. Composite and S-video inputs are supported. Each channel includes one 9-bit analog-to-digital converter (ADC) with 2x sampling. Sampling is ITU-R BT.601 (27.0) MHz, generated from a single 14.31818-MHz crystal or oscillator input) and is line locked. The output formats can be 8-bit 4:2:2 with discrete syncs or 8-bit ITU-R BT.656 with embedded synchronization.

The TVP5154A utilizes Texas Instruments patented technology for locking to weak, noisy, or unstable signals. A real-time control (RTC) output is generated for each channel for synchronizing downstream video encoders.

Complementary 4-line adaptive comb filtering is available per channel for both the luma and chroma data paths to reduce both cross-luma and cross-chroma artifacts. A chroma trap filter also is available.

An improved fast lock mode can be used when the input video standard is known and the signals on the switching channels are clean. Note, switching from snow and/or noisy channels to good channels takes longer. In fast lock mode, video lock is achieved in three fields or less.

Video characteristics, including hue, contrast, brightness, saturation, and sharpness, may be independently programmed for each channel using the industry standard I<sup>2</sup>C serial interface. The TVP5154A generates synchronization, blanking, lock, and clock signals in addition to digital video outputs for each channel. The TVP5154A includes methods for advanced vertical blanking interval (VBI) data retrieval. The VBI data processor slices, parses, and performs error checking on teletext, closed caption, and other data in several formats.

I<sup>2</sup>C commands can be sent to one or more decoder cores simultaneously, reducing the amount of I<sup>2</sup>C activity necessary to configure each core. A register controls which decoder core receives I<sup>2</sup>C commands, and can be configured such that all four decoders receive commands at the same time.

The main blocks for each of the channels of the TVP5154A decoder include:

- Robust sync detector

- ADC with analog processor

- Y/C separation using 4-line adaptive comb filter

- · Independent, concurrent scaler outputs

- Chrominance processor

- Luminance processor

- Video clock/timing processor and power-down control

- I<sup>2</sup>C interface

- VBI data processor

# 1.3 Applications

- Security/Surveillance Digital Video Recorders/Servers and PCI Products

- Automotive Infotainment Video Hub

- Large-Format Video Wall Displays

- Games Systems

### 1.4 Related Products

- TVP5150AM1

- TVP5151

- TVP5146M2

- TVP5147M1

- TVP5158

#### 1.5 Trademarks

PowerPAD is a trademark of Texas Instruments.

Macrovision is a trademark of Macrovision Corporation.

Gemstar is a trademark of Gemstar-TV Guide International.

Other trademarks are the property of their respective owners.

### 1.6 Document Conventions

Throughout this data manual, several conventions are used to convey information. These conventions are:

- To identify a binary number or field, a lower case b follows the numbers. For example: 000b is a 3-bit binary field.

- To identify a hexadecimal number or field, a lower case h follows the numbers. For example: 8AFh is a 12-bit hexadecimal field.

- All other numbers that appear in this document that do not have either a b or h following the number are assumed to be decimal format.

- If the signal or terminal name has a bar above the name (for example, RESETB), then this indicates the logical NOT function. When asserted, this signal is a logic low, 0, or 0b.

- · RSVD indicates that the referenced item is reserved.

### 1.7 Ordering Information

| т              | PACKAGED DEVICES <sup>(1)</sup> | PACKAGE OPTION |  |

|----------------|---------------------------------|----------------|--|

| T <sub>A</sub> | 128-PIN TQFP PowerPAD™          | PACKAGE OPTION |  |

| 0°C to 70°C    | TVP5154APNP                     | Tray           |  |

| 0°C to 70°C    | TVP5154APNPR                    | Tape and reel  |  |

| -40°C to 85°C  | TVP5154AIPNP                    | Tray           |  |

| -40°C to 65°C  | TVP5154AIPNPR                   | Tape and reel  |  |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# SLES214C-DECEMBER 2007-REVISED SEPTEMBER 2010

| 1 | Intro | duction <u>1</u>                               |    | 3.15               | Clock and Data Control             | . 18      |

|---|-------|------------------------------------------------|----|--------------------|------------------------------------|-----------|

|   | 1.1   | Features <u>1</u>                              | 4  | I <sup>2</sup> C H | ost Interface                      | 19        |

|   | 1.2   | Description <u>1</u>                           |    | 4.1                | I <sup>2</sup> C Write Operation   | <u>20</u> |

|   | 1.3   | Applications <u>2</u>                          |    | 4.2                | I <sup>2</sup> C Read Operation    | . 20      |

|   | 1.4   | Related Products         3                     | 5  |                    | k Circuits                         |           |

|   | 1.5   | Trademarks 3                                   | 6  | Genle              | ock Control and RTC                | 23        |

|   | 1.6   | Document Conventions                           |    | 6.1                | TVP5154A Genlock Control Interface | . 23      |

|   | 1.7   | Ordering Information                           |    | 6.2                | RTC Mode                           | . 23      |

| 2 | Devi  | ce Details <u>5</u>                            |    | 6.3                | Reset and Power Down               | . 24      |

|   | 2.1   | Functional Block Diagram 5                     |    | 6.4                | Reset Sequence                     | . 25      |

|   | 2.2   | Terminal Diagram 6                             | 7  | Interi             | nal Control Registers              | 26        |

|   | 2.3   | Terminal Functions                             |    | 7.1                | Overview                           | . 26      |

| 3 | Fund  | etional Description 9                          |    | 7.2                | Direct Register Definitions        |           |

|   | 3.1   | Analog Front End 9                             | _  | 7.3                | Indirect Register Definitions      | _         |

|   | 3.2   | Composite Processing Block Diagram 9           | 8  |                    | er Configuration                   |           |

|   | 3.3   | Adaptive Comb Filtering                        |    | 8.1                | Overview                           |           |

|   | 3.4   | Color Low-Pass Filter                          |    | 8.2                | Horizontal Scaling                 | _         |

|   | -     | ——————————————————————————————————————         |    | 8.3                | Vertical Scaling                   |           |

|   | 3.5   | Luminance Processing 11                        |    | 8.4                | Field Interleaving                 | _         |

|   | 3.6   | Chrominance Processing <u>11</u>               | 9  | Elect              | rical Specifications               | 82        |

|   | 3.7   | Timing Processor                               |    | 9.1                | Absolute Maximum Ratings           | . 82      |

|   | 3.8   | VBI Data Processor                             |    | 9.2                | Recommended Operating Conditions   | . 82      |

|   | 3.9   | VBI FIFO and Ancillary Data in Video Stream 13 |    | 9.3                | Reference Clock Specifications     | 82        |

|   | 3.10  | Raw Video Data Output                          |    | 9.4                | Electrical Characteristics         | 83        |

|   | 3.11  | Output Formatter                               |    | 9.5                | Timing Requirements                | 84        |

|   | 3.12  | Synchronization Signals                        |    | 9.6                | I <sup>2</sup> C Host Port Timing  | 85        |

|   | 3.13  | Active Video (AVID) Cropping                   |    | 9.7                | Thermal Specifications             | 85        |

|   | 3.14  | Embedded Syncs                                 | 10 | Sche               | matic                              | 86        |

|   |       | <del>-</del>                                   | 11 | Revis              | sion History                       | 87        |

|   |       |                                                |    |                    |                                    |           |

### 2 Device Details

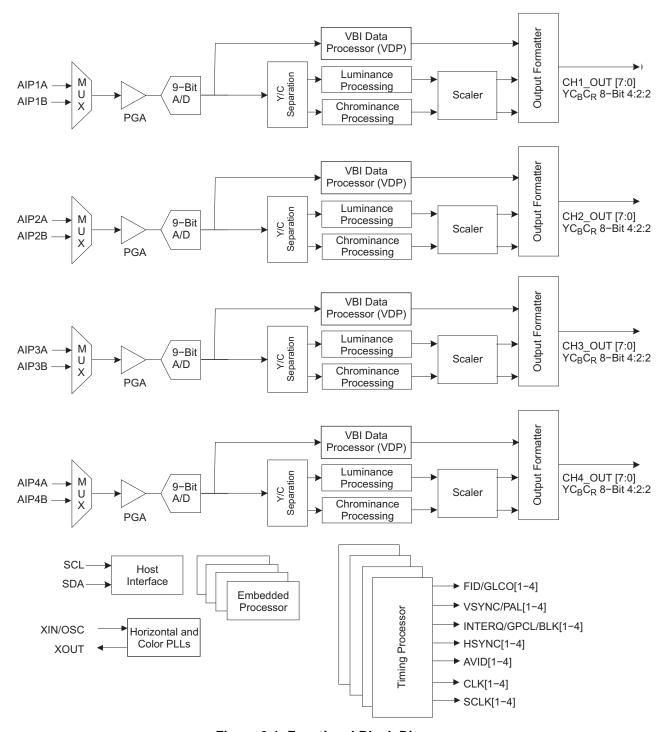

### 2.1 Functional Block Diagram

Figure 2-1. Functional Block Diagram

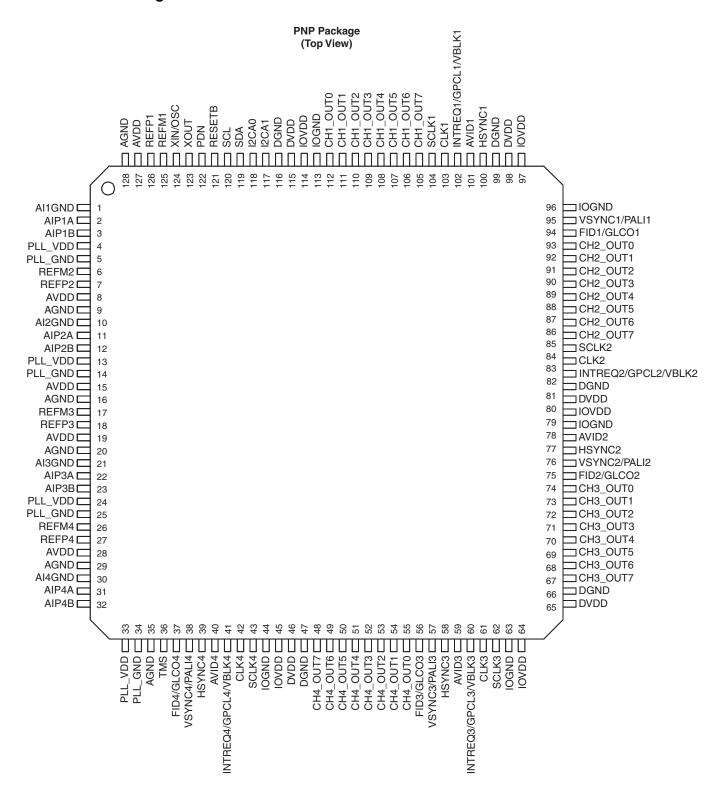

### 2.2 Terminal Diagram

### 2.3 Terminal Functions

| 2.3 Terminal Functions  TERMINAL                                                         |                              |     |                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                     | NO.                          | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |

| Analog Section                                                                           |                              |     |                                                                                                                                                                                                                                                                                                                                                                                             |

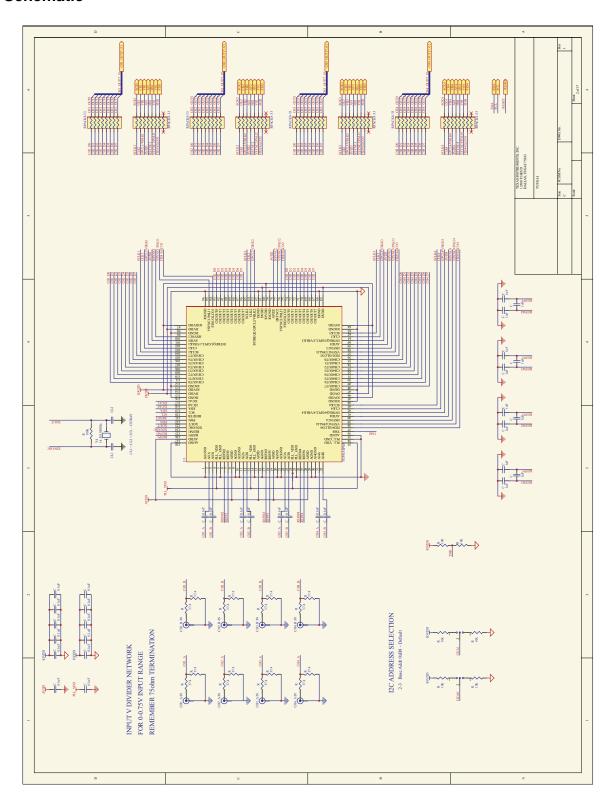

| AIP1A<br>AIP1B                                                                           | 2 3                          | I   | Analog inputs for Channel 1. Connect to the video analog input via a 0.1- $\mu$ F capacitor. The maximum input range is 0–0.75 V <sub>PP</sub> , and may require an attenuator to reduce the input amplitude to the desired level. If not used, connect to AGND via a 0.1- $\mu$ F capacitor. See the schematic in Section 10.                                                              |

| AIP2A<br>AIP2B                                                                           | 11<br>12                     | I   | Analog inputs for Channel 2. Connect to the video analog input via a $0.1-\mu F$ capacitor. The maximum input range is $0-0.75~V_{PP}$ , and may require an attenuator to reduce the input amplitude to the desired level. If not used, connect to AGND via a $0.1-\mu F$ capacitor. See the schematic in Section 10.                                                                       |

| AIP3A<br>AIP3B                                                                           | 22<br>23                     | I   | Analog inputs for Channel 3. Connect to the video analog input via a $0.1$ - $\mu$ F capacitor. The maximum input range is 0-0.75 V <sub>PP</sub> , and may require an attenuator to reduce the input amplitude to the desired level. If not used, connect to AGND via a $0.1$ - $\mu$ F capacitor. See the schematic in Section 10.                                                        |

| AIP4A<br>AIP4B                                                                           | 31<br>32                     | I   | Analog inputs for Channel 4. Connect to the video analog input via a $0.1-\mu F$ capacitor. The maximum input range is $0-0.75\ V_{PP}$ , and may require an attenuator to reduce the input amplitude to the desired level. If not used, connect to AGND via a $0.1-\mu F$ capacitor. See the schematic in Section 10.                                                                      |

| AVDD                                                                                     | 8, 15, 19,<br>28, 127        | Р   | Analog power supply. Connect to 1.8-V analog supply.                                                                                                                                                                                                                                                                                                                                        |

| AGND                                                                                     | 9, 16, 20,<br>29, 35,<br>128 | G   | Analog power supply return. Connect to analog ground.                                                                                                                                                                                                                                                                                                                                       |

| AlxGND                                                                                   | 1, 10, 21,<br>30             | G   | Analog input signal return. Connect to analog ground.                                                                                                                                                                                                                                                                                                                                       |

| PLL_GND                                                                                  | 5, 14, 25,<br>34             | G   | PLL power supply return. Connect to analog ground.                                                                                                                                                                                                                                                                                                                                          |

| PLL_VDD                                                                                  | 4, 13, 24,<br>33             | Р   | PLL power supply. Connect to 1.8-V analog supply.                                                                                                                                                                                                                                                                                                                                           |

| REFMx                                                                                    | 6, 17, 26,<br>125            | I   | Reference supply decoupling . Connect to analog ground through a 1- $\mu$ F capacitor. Connect to REFPx through a 1- $\mu$ F capacitor.                                                                                                                                                                                                                                                     |

| REFPx                                                                                    | 7, 18, 27,<br>126            | I   | Reference supply decoupling . Connect to analog ground through a 1- $\mu$ F capacitor. Connect to REFMx through a 1- $\mu$ F capacitor.                                                                                                                                                                                                                                                     |

| Digital Section                                                                          |                              |     |                                                                                                                                                                                                                                                                                                                                                                                             |

| DGND                                                                                     | 47, 66, 82,<br>99, 116       | G   | Digital power supply return. Connect to digital ground                                                                                                                                                                                                                                                                                                                                      |

| DVDD                                                                                     | 46, 65, 81,<br>98, 115       | Р   | Digital power supply. Connect to 1.8-V digital supply.                                                                                                                                                                                                                                                                                                                                      |

| IOGND                                                                                    | 44, 63, 79,<br>96, 113       | G   | I/O power supply return. Connect to digital ground.                                                                                                                                                                                                                                                                                                                                         |

| IOVDD                                                                                    | 45, 64, 80,<br>97, 114       | Р   | I/O power supply. Connect to 3.3-V digital supply                                                                                                                                                                                                                                                                                                                                           |

| FID1/GLCO1<br>FID2/GLCO2<br>FID3/GLCO3<br>FID4/GLCO4                                     | 94<br>75<br>56<br>37         | 0   | <ol> <li>FID: Odd/even field indicator or vertical lock indicator. For the odd/even indicator, a 1 indicates the odd field.</li> <li>GLCO: This serial output carries color PLL information. A slave device can decode the information to allow chroma frequency control from the TVP5154A decoder. Data is transmitted at the CLK rate in Genlock mode.</li> </ol>                         |

| AVID1<br>AVID2<br>AVID3<br>AVID4                                                         | 101<br>78<br>59<br>40        | 0   | Active video indicator. This signal is high during the horizontal active time of the video output.                                                                                                                                                                                                                                                                                          |

| INTREQ1/GPCL1/VBLK1<br>INTREQ2/GPCL2/VBLK2<br>INTREQ3/GPCL3/VBLK3<br>INTREQ4/GPCL4/VBLK4 | 102<br>83<br>60<br>41        | I/O | <ol> <li>Interrupt request: Open drain when active low.</li> <li>GPCL: General-purpose output. In this mode, the state of GPCL is directly programmed via I<sup>2</sup>C.</li> <li>VBLK: Vertical blank output. In this mode, the GPCL terminal is used to indicate the VBI of the output video. The beginning and end times of this signal are programmable via I<sup>2</sup>C.</li> </ol> |

# SLES214C-DECEMBER 2007-REVISED SEPTEMBER 2010

| TERMINAL                                                     |                       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |  |  |

|--------------------------------------------------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                         | NO.                   | 2   | DESCRIF HON                                                                                                                                                                                                                                                                                                                           |  |  |

| HSYNC1<br>HSYNC2<br>HSYNC3<br>HSYNC4                         | 100<br>77<br>58<br>39 | 0   | Horizontal synchronization                                                                                                                                                                                                                                                                                                            |  |  |

| VSYNC1/PALI1<br>VSYNC2/PALI2<br>VSYNC3/PALI3<br>VSYNC4/PALI4 | 95<br>76<br>57<br>38  | 0   | <ol> <li>VSYNC: Vertical synchronization</li> <li>PALI: PAL line indicator or horizontal lock indicator. For the PAL line indicator, a 1 indicates a noninverted line, and a 0 indicates an inverted line.</li> </ol>                                                                                                                 |  |  |

| PDN                                                          | 122                   | ı   | Power down (active low). A 0 on this pin puts the decoder in standby mode. PDN preserves the value of the registers.                                                                                                                                                                                                                  |  |  |

| RESETB                                                       | 121                   | ı   | Active-low reset. RESETB can be used only when PDN = 1. When RESETB is pulled low, it resets all the registers and restarts the internal microprocessor.                                                                                                                                                                              |  |  |

| SCL                                                          | 120                   | I/O | I <sup>2</sup> C serial clock (open drain)                                                                                                                                                                                                                                                                                            |  |  |

| SDA                                                          | 119                   | I/O | I <sup>2</sup> C serial data (open drain)                                                                                                                                                                                                                                                                                             |  |  |

| I2CA0                                                        | 118                   | ı   | During power-on reset, this pin is sampled along with pin 117 (I2CA1) to determine the I $^2$ C address the device is configured to. A 10-k $\Omega$ resistor should pull this either high (to IOVDD) or low to select different I $^2$ C device addresses.                                                                           |  |  |

| I2CA1                                                        | 117                   | 1   | During power-on reset, this pin is sampled along with pin 118 (I2CA0) to determine the I $^2$ C address the device is configured to. A 10-k $\Omega$ resistor should pull this either high (to IOVDD) or low to select different I $^2$ C device addresses.                                                                           |  |  |

| CLK1<br>CLK2<br>CLK3<br>CLK4                                 | 103<br>84<br>61<br>42 | 0   | Unscaled system data clock at either 27 MHz or 54 MHz                                                                                                                                                                                                                                                                                 |  |  |

| SCLK1<br>SCLK2<br>SCLK3<br>SCLK4                             | 104<br>85<br>62<br>43 | 0   | Scaled system data clock at 27 MHz. This signal can be used to qualify scaled/unscaled data when the unscaled system data clock is set to 54 MHz.                                                                                                                                                                                     |  |  |

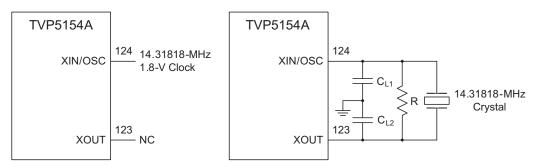

| XIN/OSC<br>XOUT                                              | 124<br>123            | -0  | External clock reference. The user may connect XIN to an oscillator or to one terminal of a crystal oscillator. The user may connect XOUT to the other terminal of the crystal oscillator or not connect XOUT at all. One single 14.31818-MHz crystal or oscillator is needed for ITU-R BT.601 sampling, for all supported standards. |  |  |

| CH1_OUT[7:0]                                                 | 105–112               | 0   | Decoded ITU-R BT.656 output/YCbCr 4:2:2 output with discrete sync for channel 1                                                                                                                                                                                                                                                       |  |  |

| CH2_OUT[7:0]                                                 | 86–93                 | 0   | Decoded ITU-R BT.656 output/YCbCr 4:2:2 output with discrete sync for channel 2                                                                                                                                                                                                                                                       |  |  |

| CH3_OUT[7:0]                                                 | 67–74                 | 0   | Decoded ITU-R BT.656 output/YCbCr 4:2:2 output with discrete sync for channel 3                                                                                                                                                                                                                                                       |  |  |

| CH4_OUT[7:0]                                                 | 48–55                 | 0   | Decoded ITU-R BT.656 output/YCbCr 4:2:2 output with discrete sync for channel 4                                                                                                                                                                                                                                                       |  |  |

| TMS                                                          | 36                    | I   | Test-mode select. This pin should be connected to digital ground for correct device operation.                                                                                                                                                                                                                                        |  |  |

# 3 Functional Description

# 3.1 Analog Front End

Each channel of the TVP5154A decoder has an analog input channel that accepts two video inputs, which should be ac coupled through 0.1- $\mu$ F capacitors. The decoder supports a maximum input voltage range of 0.75 V; therefore, an attenuation of one-half is needed for standard input signals with a peak-to-peak variation of 1.5 V. The maximum parallel termination before the input to the device is 75  $\Omega$ . See the schematic in Section 10 for recommended configuration. The two analog input ports can be connected as follows:

- · Two selectable composite video inputs or

- · One S-video input

An internal clamping circuit restores the ac-coupled video signal to a fixed dc level.

The programmable gain amplifier (PGA) and the automatic gain control (AGC) circuit work together to ensure that the input signal is amplified or attenuated correctly, ensuring the proper input range for the ADC.

When switching CVBS inputs from one input to the other, the AGC settings are internally stored and the previous settings for the new input are restored. This eliminates flashes and dark frames associated with switching between inputs that have different signal amplitudes.

The ADC has nine bits of resolution and runs at a maximum speed of 27 MHz. The clock input for the ADC comes from the PLL.

# 3.2 Composite Processing Block Diagram

The composite processing block processes NTSC/PAL/SECAM signals into the YCbCr color space. Figure 2-1 shows the basic architecture of this processing block.

Figure 2-1 shows the luminance/chrominance (Y/C) separation process in the TVP5154A decoders. The composite video is multiplied by sub-carrier signals in the quadrature modulator to generate the color difference signals Cb and Cr. Cb and Cr are then low pass (LP) filtered to achieve the desired bandwidth and to reduce crosstalk.

An adaptive 4-line comb filter separates CbCr from Y. Chroma is remodulated through another quadrature modulator and subtracted from the line-delayed composite video to generate luma. Contrast, brightness, hue, saturation, and sharpness (using the peaking filter) are programmable via I<sup>2</sup>C.

The Y/C separation is bypassed for S-video input. For S-video, the remodulation path is disabled.

# 3.3 Adaptive Comb Filtering

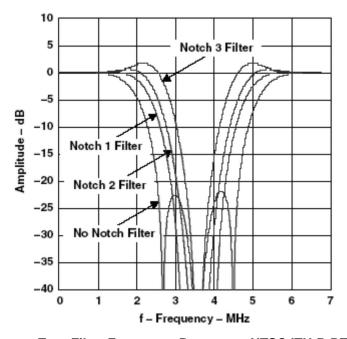

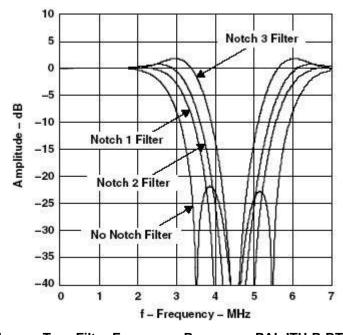

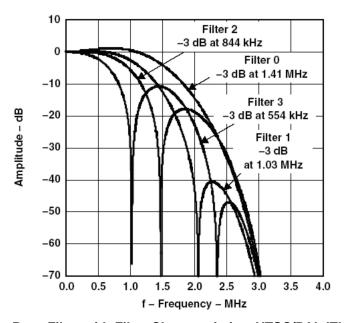

The 4-line comb filter can be selectively bypassed in the luma or chroma path. If the comb filter is bypassed in the luma path, then chroma trap filters are used which are shown in Figure 3-1 and Figure 3-2. TI's patented adaptive 4-line comb filter algorithm reduces artifacts, such as hanging dots at color boundaries, and detects and properly handles false colors in high-frequency luminance images, such as a multiburst pattern or circle pattern.

Figure 3-1. Chroma Trap Filter Frequency Response, NTSC ITU-R BT.601 Sampling

Figure 3-2. Chroma Trap Filter Frequency Response, PAL ITU-R BT.601 Sampling

### 3.4 Color Low-Pass Filter

In some applications, it is desirable to limit the Cb/Cr bandwidth to avoid crosstalk. This is especially true in the case of video signals that have asymmetrical Cb/Cr sidebands. The provided color LP filters limit the bandwidth of the Cb/Cr signals. Color LP filters are needed when the comb filtering turns off, due to extreme color transitions in the input image. See Chrominance Control #2 Register (Section 7.2.27), for the response of these filters. The filters have three options that allow three different frequency responses based on the color frequency characteristics of the input video as shown in Figure 3-3.

Figure 3-3. Color Low-Pass Filter with Filter Characteristics, NTSC/PAL ITU-R BT.601 Sampling

### 3.5 Luminance Processing

The luma component is derived from the composite signal by subtracting the remodulated chroma information. A line delay exists in this path to compensate for the line delay in the adaptive comb filter in the color processing chain. The luma information is then fed into the peaking circuit, which enhances the high-frequency components of the signal, thus, improving sharpness.

### 3.6 Chrominance Processing

For NTSC/PAL formats, the color processing begins with a quadrature demodulator. The Cb/Cr signals then pass through the gain control stage for chroma saturation adjustment. An adaptive comb filter is applied to the demodulated signals to separate chrominance and eliminate cross-chrominance artifacts. An automatic color-killer circuit is also included in this block. The color killer suppresses the chrominance processing when the burst amplitude falls below a programmable threshold (see I<sup>2</sup>C subaddress 06h, Section 7.2.7). The SECAM standard is similar to PAL except for the modulation of color, which is FM instead of QAM.

# 3.7 Timing Processor

The timing processor is a combination of hardware and software running in the internal microprocessor that serves to control horizontal lock to the input sync pulse edge, AGC and offset adjustment in the analog front end, and vertical sync detection.

### 3.8 VBI Data Processor

The TVP5154A VBI data processor (VDP) slices various data services, such as teletext (WST, NABTS), closed caption (CC), wide screen signaling (WSS), etc. These services are acquired by programming the VDP to enable standards in the VBI. The results are stored in a FIFO and/or registers. The teletext results are stored in a FIFO only. Table 3-1 lists a summary of the types of VBI data supported according to the video standard. It supports ITU-R BT.601 sampling for each.

Table 3-1. Data Types Supported by the VDP

| LINE MODE REGISTER<br>(D0h-FCh) BITS [3:0] | NAME                | DESCRIPTION                                                          |

|--------------------------------------------|---------------------|----------------------------------------------------------------------|

| 0000b                                      | WST SECAM           | Teletext, SECAM                                                      |

| 0001b                                      | WST PAL B           | Teletext, PAL, System B                                              |

| 0010b                                      | WST PAL C           | Teletext, PAL, System C                                              |

| 0011b                                      | WST, NTSC B         | Teletext, NTSC, System B                                             |

| 0100b                                      | NABTS, NTSC C       | Teletext, NTSC, System C                                             |

| 0101b                                      | NABTS, NTSC D       | Teletext, NTSC, System D (Japan)                                     |

| 0110b                                      | CC, PAL             | Closed caption PAL                                                   |

| 0111b                                      | CC, NTSC            | Closed caption NTSC                                                  |

| 1000b                                      | WSS/CGMS-A, PAL     | Wide-screen signaling/Copy Generation Management System-Analog, PAL  |

| 1001b                                      | WSS/CGMS-A, NTSC    | Wide-screen signaling/Copy Generation Management System-Analog, NTSC |

| 1010b                                      | VITC, PAL           | Vertical interval timecode, PAL                                      |

| 1011b                                      | VITC, NTSC          | Vertical interval timecode, NTSC                                     |

| 1100b                                      | VPS, PAL            | Video program system, PAL                                            |

| 1101b                                      | Gemstar 2x Custom 1 | Electronic program guide                                             |

| 1110b                                      | Reserved            | Reserved                                                             |

| 1111b                                      | Active Video        | Active video/full field                                              |

At power up, the host interface is required to program the VDP-configuration RAM (VDP-CRAM) contents with the lookup table (see Section 7.2.69). This is done through port address C3h. Each read from or write to this address auto increments an internal counter to the next RAM location. To access the VDP-CRAM, the line mode registers (D0h–FCh) must be programmed with FFh to avoid a conflict with the internal microprocessor and the VDP in both writing and reading. Full field mode must also be disabled.

Available VBI lines are from line 6 to line 27 of both field 1 and field 2. Each line can be any VBI mode.

Output data is available either through the VBI-FIFO (B0h) or through dedicated registers at 90h–AFh, both of which are available through the I<sup>2</sup>C port.

### 3.9 VBI FIFO and Ancillary Data in Video Stream

Sliced VBI data can be output as ancillary data in the video stream in the ITU-R BT.656 mode. VBI data is output during the horizontal blanking period following the line from which the data was retrieved. Table 3-2 shows the header format and sequence of the ancillary data inserted into the video stream. This format is also used to store any VBI data into the FIFO. The size of FIFO is 512 bytes. Therefore, the FIFO can store up to 11 lines of teletext data with the NTSC NABTS standard.

Table 3-2. Ancillary Data Format and Sequence

| BYTE NO. | D7<br>(MSB) | D6 | D5 | D4                        | D3       | D2       | D1        | D0<br>(LSB) | DESCRIPTION               |                 |  |

|----------|-------------|----|----|---------------------------|----------|----------|-----------|-------------|---------------------------|-----------------|--|

| 0        | 0           | 0  | 0  | 0                         | 0        | 0        | 0         | 0           | Ancillary data preamble   |                 |  |

| 1        | 1           | 1  | 1  | 1                         | 1        | 1        | 1         | 1           |                           |                 |  |

| 2        | 1           | 1  | 1  | 1                         | 1        | 1        | 1         | 1           |                           |                 |  |

| 3        | NEP         | EP | 0  | 1                         | 0        | DID2     | DID1      | DID0        | Data ID (DID)             | )               |  |

| 4        | NEP         | EP | F5 | F4                        | F3       | F2       | F1        | F0          | Secondary da              | ata ID (SDID)   |  |

| 5        | NEP         | EP | N5 | N4                        | N3       | N2       | N1        | N0          | Number of 32              | 2 bit data (NN) |  |

| 6        |             |    |    | Internal data ID0 (IDID0) |          |          |           |             |                           |                 |  |

| 7        | 0           | 0  | 0  | Data error                | Match #1 | Match #2 | Video lir | ne # [9:8]  | Internal data ID1 (IDID1) |                 |  |

| 8        |             | •  | •  | 1. [                      | Data     | •        | •         |             | Data byte                 | 1st word        |  |

| 9        |             |    |    | 2. 🛭                      | Data     |          |           |             | Data byte                 |                 |  |

| 10       |             |    |    | 3. 🛭                      | Data     |          |           |             | Data byte                 |                 |  |

| 11       |             |    |    | 4. 🛭                      | Data     |          |           |             | Data byte                 |                 |  |

| :        |             |    |    |                           | :        |          |           |             | :                         |                 |  |

|          |             |    |    | Data byte                 | Nth word |          |           |             |                           |                 |  |

|          |             |    |    | Data byte                 |          |          |           |             |                           |                 |  |

|          | NEP         | EP |    | Check sum                 |          |          |           |             |                           |                 |  |

| 4(N+2)-1 | 0           | 0  | 0  | 0                         | 0        | 0        | 0         | 0           | Fill byte                 |                 |  |

EP: Even parity for D0–D5

NEP: Negated even parity

DID: 91h: Sliced data of VBI lines of first field

53h: Sliced data of line 24 to end of first field 55h: Sliced data of VBI lines of second field 97h: Sliced data of line 24 to end of second field

SDID: This field holds the data format taken from the line mode register of the corresponding line.

NN: Number of Dwords beginning with byte 8 through 4(N+2). This value is the number of Dwords where each Dword is 4

bytes.

IDID0: Transaction video line number [7:0]

IDID1: Bit 0/1 = Transaction video line number [9:8]

Bit 2 = Match 2 flag Bit 3 = Match 1 flag

Bit 4 = 1 if an error was detected in the EDC block. 0 if not.

CS: Sum of D0-D7 of DID through last data byte

Fill byte: Fill bytes make a multiple of four bytes from byte 0 to last fill byte. For teletext modes, byte 8 is the sync pattern byte.

Byte 9 is 1. Data (the first data byte).

### 3.10 Raw Video Data Output

The TVP5154A decoder can output raw A/D video data at 2x sampling rate for external VBI slicing. This is transmitted as an ancillary data block during the active horizontal portion of the line and during vertical blanking.

### 3.11 Output Formatter

The output formatter is responsible for generating the output digital video stream. The YCbCr digital output can be programmed as 8-bit 4:2:2 or 8-bit ITU-R BT.656 parallel interface standard. Depending on which output mode is selected, the output for each channel can be unscaled data, scaled data, or both scaled and unscaled data interleaved in various ways.

Table 3-3. Summary of Line Frequencies, Data Rates and Pixel Counts for Different Standards

| STANDARDS<br>(ITU-R BT.601) | PIXELS PER<br>LINE | ACTIVE PIXELS<br>PER LINE | LINES PER<br>FRAME | PIXEL<br>FREQUENCY<br>(MHz) | COLOR<br>SUB-CARRIER<br>FREQUENCY<br>(MHz) | HORIZONTAL<br>LINE RATE<br>(kHz) |

|-----------------------------|--------------------|---------------------------|--------------------|-----------------------------|--------------------------------------------|----------------------------------|

| NTSC-J, M                   | 858                | 720                       | 525                | 13.5                        | 3.579545                                   | 15.73426                         |

| NTSC-4.43                   | 858                | 720                       | 525                | 13.5                        | 4.43361875                                 | 15.73426                         |

| PAL-M                       | 858                | 720                       | 525                | 13.5                        | 3.57561149                                 | 15.73426                         |

| PAL-B, D, G, H, I           | 864                | 720                       | 625                | 13.5                        | 4.43361875                                 | 15.625                           |

| PAL-N                       | 864                | 720                       | 625                | 13.5                        | 4.43361875                                 | 15.625                           |

| PAL-Nc                      | 864                | 720                       | 625                | 13.5                        | 3.58205625                                 | 15.625                           |

| SECAM                       | 864                | 720                       | 625                | 13.5                        | 4.40625/4.25                               | 15.625                           |

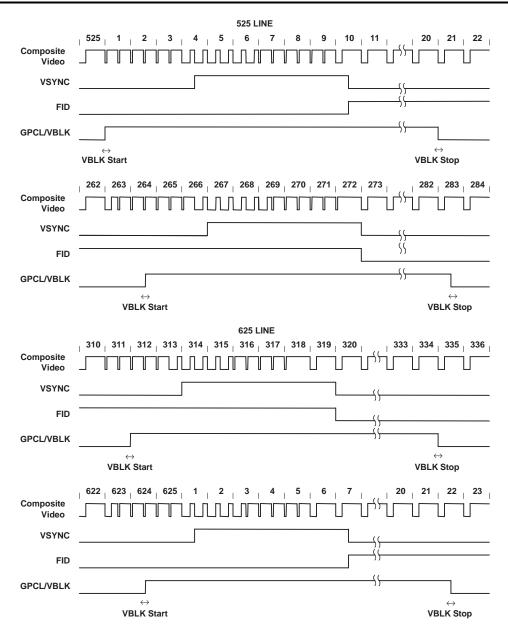

### 3.12 Synchronization Signals

External (discrete) syncs are provided via the following signals:

- VSYNC (vertical sync)

- FID/VLK (field indicator or vertical lock indicator)

- GPCL/VBLK (general-purpose I/O or vertical blanking indicator)

- PALI/HLK (PAL switch indicator or horizontal lock indicator)

- HSYNC (horizontal sync)

- · AVID (active video indicator)

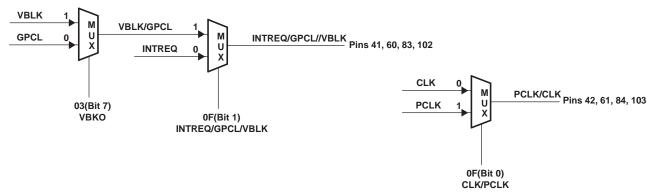

VSYNC, FID, PALI, and VBLK are software set and programmable to the CLK pixel count. This allows any possible alignment to the internal pixel count and line count. The default settings for a 525-/625-line video output are shown in Figure 3-4.

Line numbering conforms to ITU-R BT.470.

Figure 3-4. 8-Bit 4:2:2, Timing With 2x Pixel Clock (CLK) Reference

NOTE: AVID rising edge occurs four CLK cycles early when in ITU-R BT.656 output mode.

Figure 3-5. Horizontal Synchronization Signals

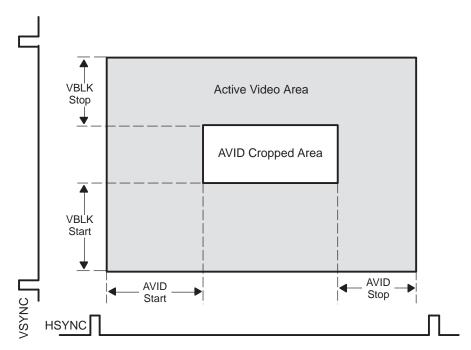

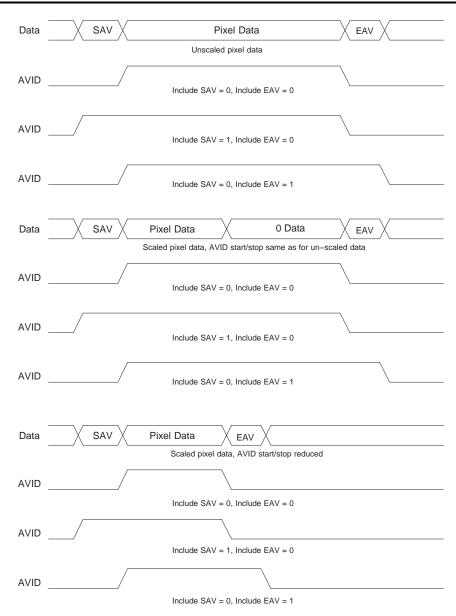

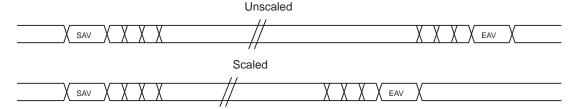

### 3.13 Active Video (AVID) Cropping

AVID cropping provides a means to decrease the amount of video data output. This is accomplished by horizontally blanking a number of AVID pulses and by vertically blanking a number of lines per frame. The horizontal AVID cropping is controlled using registers 11h and 12h for start pixels MSB and LSB, respectively.

Registers 13h and 14h provide access to stop pixels MSB and LSB, respectively. The vertical AVID cropping is controlled using the vertical blanking (VBLK) start and stop registers at addresses 18h and 19h. Figure 3-6 shows an AVID application.

AVID cropping can be independently controlled for scaled (registers 25h, 26h, 29h, and 2Ah) and unscaled (registers 11h thru 14h) data streams. AVID start and stop must be changed in multiples of two pixels to ensure correct UV alignment.

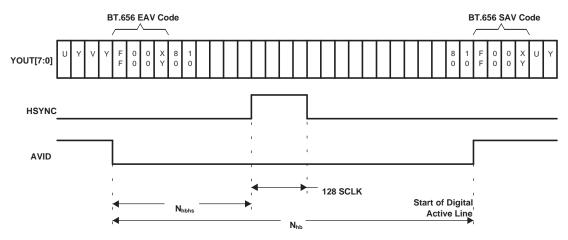

Additionally, AVID start and stop can be configured to include the SAV- and EAV-embedded sync signals or to exclude them, and to either include or exclude ITU656 ancillary data.

#### NOTE

The above settings alter AVID output timing, but the video output data is not forced to black level outside of the AVID interval.

Figure 3-6. AVID Application

# 3.14 Embedded Syncs

Standards with embedded syncs insert SAV and EAV codes into the data stream at the beginning and end of horizontal blanking. These codes contain the V and F bits that also define vertical timing. F and V change on EAV. Table 3-4 gives the format of the SAV and EAV codes.

H equals 1 always indicates EAV. H equals 0 always indicates SAV. The alignment of V and F to the line and field counter varies depending on the standard. See ITU-R BT.656 for more information on embedded syncs.

The P bits are protection bits:

$P3 = V \times or$   $H P2 = F \times or$   $H P1 = F \times or$  $V P0 = F \times or$

V x or H

Table 3-4. EAV and SAV Sequence

|             |          | 8-BIT DATA |    |    |    |    |    |    |  |  |  |  |

|-------------|----------|------------|----|----|----|----|----|----|--|--|--|--|

|             | D7 (MSB) | D6         | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

| Preamble    | 1        | 1          | 1  | 1  | 1  | 1  | 1  | 1  |  |  |  |  |

| Preamble    | 0        | 0          | 0  | 0  | 0  | 0  | 0  | 0  |  |  |  |  |

| Preamble    | 0        | 0          | 0  | 0  | 0  | 0  | 0  | 0  |  |  |  |  |

| Status word | 1        | F          | V  | Н  | P3 | P2 | P1 | P0 |  |  |  |  |

The status word may be modified to pass information about whether the current data corresponds to scaled or unscaled data. See register 1Fh for more information.

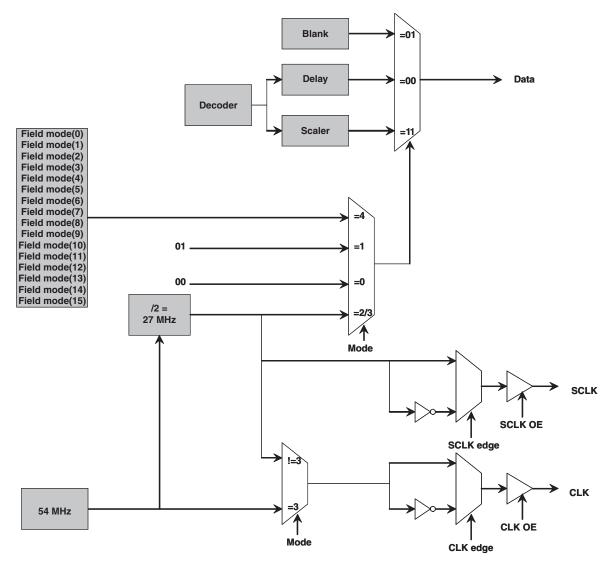

# 3.15 Clock and Data Control

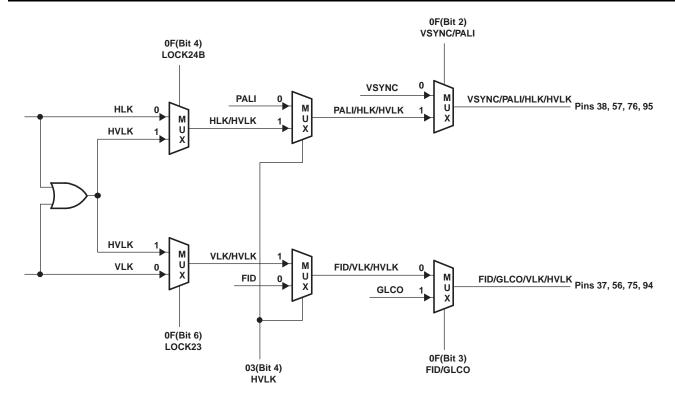

Figure 3-7 shows a logical schematic of the data and clock control signals.

Figure 3-7. Clock and Data Control

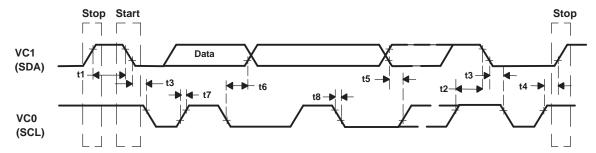

### 4 I<sup>2</sup>C Host Interface

The I<sup>2</sup>C standard consists of two signals, serial input/output data line (SDA) and input/output clock line (SCL), which carry information between the devices connected to the bus. The input pins I2CA0 and I2CA1 are used to select the slave address to which the device responds. Although the I<sup>2</sup>C system can be multimastered, the TVP5154A decoder functions as a slave device only.

Both SDA and SCL must be connected to IOVDD via pullup resistors. When the bus is free, both lines are high. The slave address select terminals (I2CA0 and I2CA1) enable the use of four TVP5154A decoders on the same I<sup>2</sup>C bus. At the trailing edge of reset, the status of the I2CA0 and I2CA1 lines are sampled to determine the device address used. Table 4-1 summarizes the terminal functions of the I<sup>2</sup>C-mode host interface. Table 4-2 shows the device address selection options.

SIGNAL

TYPE

DESCRIPTION

I2CA0

I Slave address selection

I2CA1

I Slave address selection

SCL

I/O (open drain)

Input/output clock line

SDA

I/O (open drain)

Input/output data line

Table 4-1. I<sup>2</sup>C Terminal Description

Table 4-2. I<sup>2</sup>C Host Interface Device Addresses

| A6 | A5 | A4 | А3 | A2 | A1 (I2CA1) | A0 (I2CA0) | R/W | HEX   |

|----|----|----|----|----|------------|------------|-----|-------|

| 1  | 0  | 1  | 1  | 1  | 0          | 0          | 1/0 | B9/B8 |

| 1  | 0  | 1  | 1  | 1  | 0          | 1          | 1/0 | BB/BA |

| 1  | 0  | 1  | 1  | 1  | 1          | 0          | 1/0 | BD/BC |

| 1  | 0  | 1  | 1  | 1  | 1          | 1          | 1/0 | BF/BE |

Data transfer rate on the bus is up to 400 kbit/s. The number of interfaces connected to the bus is dependent on the bus capacitance limit of 400 pF. The data on the SDA line must be stable during the high period of the SCL, except for start and stop conditions. The high or low state of the data line can only change with the clock signal on the SCL line being low. A high-to-low transition on the SDA line while the SCL is high indicates an  $I^2$ C start condition. A low-to-high transition on the SDA line while the SCL is high indicates an  $I^2$ C stop condition.

Every byte placed on the SDA must be eight bits long. The number of bytes that can be transferred is unrestricted. Each byte must be followed by an acknowledge bit. The acknowledge-related clock pulse is generated by the I<sup>2</sup>C master.

To simplify programming of each of the four decoder channels, a single  $I^2C$  write transaction can be transmitted to any one or more of the four cores in parallel. This reduces the time required to download firmware or to configure the device when all channels are to be configured in the same manner. It also enables the addresses for all registers to be common across all decoders.

$I^2C$  sub-address 0xFE contains four bits, with each bit corresponding to one of the decoder cores. If this bit is set,  $I^2C$  write transactions are sent to the corresponding decoder core. If the bit is 0, the corresponding decoder does not receive the  $I^2C$  write transactions.

$I^2C$  sub-address 0xFF contains four bits, with each bit corresponding to one of the decoder cores. If this bit is set,  $I^2C$  read transactions are sent to the corresponding decoder core. Note, only one of the bits in this register should be set at a given time, ensuring that only one decoder core is accessed at a time for read operations. If more than one bit is set, the lowest set bit number corresponds to the core that responds to the read transaction.

Note that, when register 0xFE is written to with any value, register 0xFF is set to 0x00. Likewise, when register 0xFF is written to with any value, register 0xFE is set to 0x00.

### 4.1 I<sup>2</sup>C Write Operation

Data transfers occur utilizing the following illustrated formats.

An I<sup>2</sup>C master initiates a write operation to the TVP5154A decoder by generating a start condition (S) followed by the TVP5154A I<sup>2</sup>C address (as shown below), in MSB first bit order, followed by a 0 to indicate a write cycle. After receiving an acknowledge from the TVP5154A decoder, the master presents the sub-address of the register, or the first of a block of registers it wants to write, followed by one or more bytes of data, MSB first. The TVP5154A decoder acknowledges each byte after completion of each transfer. The I<sup>2</sup>C master terminates the write operation by generating a stop condition (P).

| Step 1                                           | 0    |      |      |      |      |      |      |      |

|--------------------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C start (master)                  | S    |      |      |      |      |      |      |      |

| Step 2                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C general address (master)        | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

| Step 3                                           | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C acknowledge (slave)             | Α    |      |      |      |      |      |      |      |

| Step 4                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C write register address (master) | addr |

| Step 5                                           | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C acknowledge (slave)             | А    |      |      |      |      |      |      |      |

| Step 6                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C write data (master)             | Data |

| Step 7 <sup>(1)</sup>                            | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C acknowledge (slave)             | А    |      |      |      |      |      |      |      |

| Step 8                                           | 0    |      |      |      |      |      |      |      |

| I <sup>2</sup> C stop (master)                   | Р    |      |      |      |      |      |      |      |

<sup>(1)</sup> Repeat steps 6 and 7 until all data have been written.

### 4.2 I<sup>2</sup>C Read Operation

The read operation consists of two phases. The first phase is the address phase. In this phase, an I<sup>2</sup>C master initiates a write operation to the TVP5154A decoder by generating a start condition (S) followed by the TVP5154A I<sup>2</sup>C address, in MSB first bit order, followed by a 0 to indicate a write cycle. After receiving acknowledges from the TVP5154A decoder, the master presents the sub-address of the register or the first of a block of registers it wants to read. After the cycle is acknowledged, the master terminates the cycle immediately by generating a stop condition (P).

The second phase is the data phase. In this phase, an I<sup>2</sup>C master initiates a read operation to the TVP5154A decoder by generating a start condition followed by the TVP5154A I<sup>2</sup>C address (as shown below for a read operation), in MSB first bit order, followed by a 1 to indicate a read cycle. After an acknowledge from the TVP5154A decoder, the I<sup>2</sup>C master receives one or more bytes of data from the TVP5154A decoder. The I<sup>2</sup>C master acknowledges the transfer at the end of each byte. After the last data byte desired has been transferred from the TVP5154A decoder to the master, the master generates a not acknowledge followed by a stop.

www ti com

### Read Phase 1

| Step 1                                          | 0    | •    |      |      |      |      |      |      |

|-------------------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C start (master)                 | S    | :    |      |      |      |      |      |      |

| Step 2                                          | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C general address (master)       | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

| Step 3                                          | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C acknowledge (slave)            | Α    |      |      |      |      |      |      |      |

| Step 4                                          | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C read register address (master) | addr |

| Step 5                                          | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C acknowledge (slave)            | Α    |      |      |      |      |      |      |      |

| Step 6                                          | 0    |      |      |      |      |      |      |      |

| I <sup>2</sup> C stop (master)                  | Р    | •    |      |      |      |      |      |      |

### Read Phase 2

| Step 7                                    | 0    |      |      |      |      |      |      |      |

|-------------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C start (master)           | S    |      |      |      |      |      |      |      |

| Step 8                                    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C general address (master) | 1    | 0    | 1    | 1    | 1    | 0    | X    | 1    |

| Step 9                                    | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C acknowledge (slave)      | А    |      |      |      |      |      |      |      |

| Step 10                                   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C read data (slave)        | Data |

| Step 11 <sup>(1)</sup>                    | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C not acknowledge (master) | А    |      |      |      |      |      |      |      |

| Step 12                                   | 0    |      |      |      |      |      |      |      |

| 120                                       |      |      |      |      |      |      |      |      |

<sup>(1)</sup> Repeat steps 10 and 11 for all bytes read. Master does not acknowledge the last read data received.

# 4.2.1 FC Timing Requirements

The TVP5154A decoder requires delays in the I<sup>2</sup>C accesses to accommodate its internal processor's timing. In accordance with I<sup>2</sup>C specifications, the TVP5154A decoder holds the I<sup>2</sup>C clock line (SCL) low to indicate the wait period to the I<sup>2</sup>C master. If the I<sup>2</sup>C master is not designed to check for the I<sup>2</sup>C clock line held-low condition, the maximum delays must always be inserted where required. These delays are of variable length; maximum delays are indicated in the following diagram:

# Table 4-3. I<sup>2</sup>C Timing

| Start | Slave address<br>(B8h) | Ack | Subaddress | Ack | Data (XXh) | Ack | Wait 128 μs <sup>(1)</sup> | Stop |  |

|-------|------------------------|-----|------------|-----|------------|-----|----------------------------|------|--|

|-------|------------------------|-----|------------|-----|------------|-----|----------------------------|------|--|

(1) If the SCL pin is not monitored by the master to enable pausing, a delay of 128 μs should be inserted between transactions for registers 00h through 8Fh.

Clock Circuits

### 5 Clock Circuits

An internal line-locked PLL generates the system and pixel clocks. A 14.31818-MHz clock is required to drive the PLL. This may be input to the TVP5154A decoder on terminal 124 (XIN), or a crystal of 14.31818-MHz fundamental resonant frequency may be connected across terminals 123 and 124 (XIN and XOUT). Figure 5-1 shows the reference clock configurations. For the example crystal circuit shown (a parallel-resonant crystal with 14.31818-MHz fundamental frequency), the external capacitors must have the following relationship:

$$C_{L1} = C_{L2} = 2C_L - C_{STRAY}$$

where  $C_{STRAY}$  is the terminal capacitance with respect to ground and  $C_L$  is the crystal load capacitance specified by the crystal manufacturer. Figure 5-1 shows the reference clock configurations.

NOTE: The resistor (R) in parallel with the crystal is recommended to support a wide range of crystal types. A 100-kΩ resistor may be used for most crystal types.

Figure 5-1. Clock and Crystal Connectivity

22

### 6 Genlock Control and RTC

A Genlock control (GLCO) function is provided to support a standard video encoder to synchronize its internal color oscillator for properly reproduced color with unstable timebase sources like VCRs.

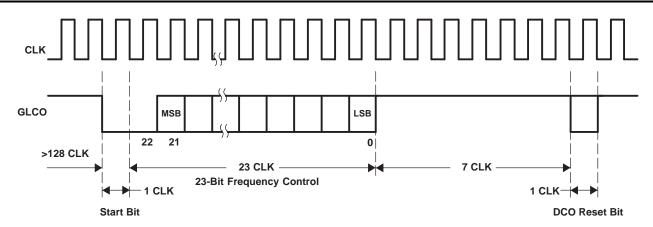

The frequency control word of the internal color subcarrier digital control oscillator (DTO) and the subcarrier phase reset bit are transmitted via the GLCO terminal. The frequency control word is a 23-bit binary number. The frequency of the DTO can be calculated from the following equation:

$$F_{dto} = \frac{F_{ctrl}}{2^{23}} \times F_{clk} \tag{1}$$

where  $F_{dto}$  is the frequency of the DTO,  $F_{ctrl}$  is the 23-bit DTO frequency control, and  $F_{clk}$  is the frequency of the CLK.

### 6.1 TVP5154A Genlock Control Interface

A write of 1 to bit 4 of the chrominance control register at I<sup>2</sup>C subaddress 1Ah causes the subcarrier DTO phase reset bit to be sent on the next scan line on GLCO. The active-low reset bit occurs seven CLKs after the transmission of the last bit of DCO frequency control. Upon the transmission of the reset bit, the phase of the TVP5154A internal subcarrier DCO is reset to zero.

A Genlock slave device can be connected to the GLCO terminal and uses the information on GLCO to synchronize its internal color phase DCO to achieve clean line and color lock.

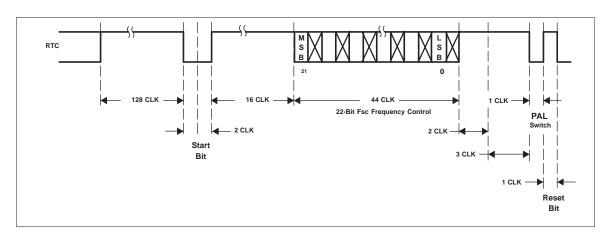

### 6.2 RTC Mode

Figure 6-1 shows the timing diagram of the RTC mode. Clock rate for the RTC mode is four times slower than the GLCO clock rate. For PLL frequency control, the upper 22 bits are used. Each frequency control bit is two clock cycles long. The active-low reset bit occurs six CLKs after the transmission of the last bit of PLL frequency control.

### **GLCO Timing**

Figure 6-1. RTC Timing

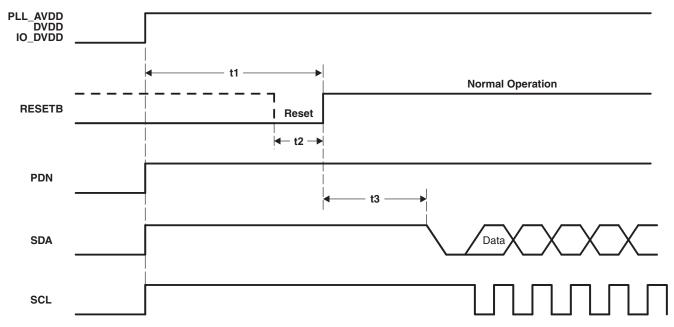

### 6.3 Reset and Power Down

The RESETB and PDN terminals work together to put the TVP5154A decoder into one of the two modes. Table 6-1 shows the configuration.

After power-up, the device is in an unknown state with its outputs undefined, until it receives a RESETB signal as depicted in Figure 6-2. After RESETB is released, the data (CHn\_OUT[7:0]), sync (HSYNCn, VSYNCn/PALIn), and clock (CLKn, SCLKn) outputs are Hi-Z until the chip is initialized and the outputs are activated.

### **NOTE**

I2C SCL and SDA signals must not change state until the TVP5154A reset sequence has been completed.

Table 6-1. Reset and Power-Down Modes

| PDN | RESETB | CONFIGURATION            |

|-----|--------|--------------------------|

| 0   | 0      | Reserved (unknown state) |

| 0   | 1      | Powers down the decoder  |

| 1   | 0      | Resets the decoder       |

| 1   | 1      | Normal operation         |

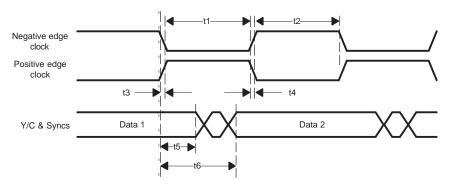

Figure 6-2. Power-On Reset Timing

Table 6-2. Power-On Reset Timing

| NO. | PARAMETER                                                  | MIN | MAX | UNIT |

|-----|------------------------------------------------------------|-----|-----|------|

| t1  | Delay time between power supplies active and reset         | 20  |     | ms   |

| t2  | RESETB pulse duration                                      | 500 |     | ns   |

| t3  | Delay time between end of reset to I <sup>2</sup> C active | 200 |     | μs   |

# 6.4 Reset Sequence

Table 6-3 shows the reset sequence of the TVP5154A pins status during reset time and immediately after reset time.

Table 6-3. Reset Sequence

| PIN DESCRIPTION                                                                                                                                                                                                                     | DURING RESETB | IMMEDIATELY<br>AFTER RESETB |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|

| INTREQ1/GPCL1/VBLK1, INTREQ2/GPCL2/VBLK2, INTREQ3/GPCL3/VBLK3, INTREQ4/GPCL4/VBLK4, HSYNC1, HSYNC2, HSYNC3, HSYNC4, VSYNC1/PALI1, VSYNC2/PALI2, VSYNC3/PALI3, VSYNC4/PALI4, CH1_OUT[7:0], CH2_OUT[7:0], CH3_OUT[7:0], CH4_OUT[7:0], | 3-state       | 3-state                     |

| AIP1A, AIP1B, AIP2A, AIP2B, AIP3A, AIP3B, AIP4A, AIP4B, RESETB, PDN, SDA, SCL, I2CA0, I2CA1, XIN/OSC, TMS                                                                                                                           | Input         | Input                       |

| FID1/GLCO1, FID2/GLCO2, FID3/GLCO3, FID4/GLCO4, AVID1, AVID2, AVID3, AVID4, CLK1, CLK2, CLK3, CLK4, SCLK1, SCLK2, SCLK3, SCLK4, XOUT                                                                                                | Output        | Output                      |

# 7 Internal Control Registers

#### 7.1 Overview

The TVP5154A decoder is initialized and controlled by sets of internal registers that set all device operating parameters. Communication between the external controller and the TVP5154A decoder is through the I<sup>2</sup>C. Two sets of registers exist, direct and indirect. Table 7-1 shows the summary of the direct registers. Reserved registers must not be written. Reserved bits in the defined registers must be written with zeros, unless otherwise noted. The detailed programming information of each register is described in the following sections.

I<sup>2</sup>C register FEh controls which of the four decoders receives I<sup>2</sup>C commands. I<sup>2</sup>C register FFh controls which decoder core responds to I<sup>2</sup>C reads. Note, for a read operation, it is necessary to perform a write first, to set the desired sub-address for reading.

After power up and the hardware reset, each decoder must be started by writing 00h to register 7Fh for all four decoders.

**Table 7-1. Direct Register Summary**

| REGISTER FUNCTION                                 | ADDRESS | DEFAULT | R/W <sup>(1)</sup> |

|---------------------------------------------------|---------|---------|--------------------|

| Video input source selection #1                   | 00h     | 00h     | R/W                |

| Analog channel controls                           | 01h     | 15h     | R/W                |

| Operation mode controls                           | 02h     | 00h     | R/W                |

| Miscellaneous controls                            | 03h     | 01h     | R/W                |

| Autoswitch mask                                   | 04h     | DCh     | R/W                |

| Clock control                                     | 05h     | 08h     | R/W                |

| Color killer threshold control                    | 06h     | 10h     | R/W                |

| Luminance processing control #1                   | 07h     | 60h     | R/W                |

| Luminance processing control #2                   | 08h     | 00h     | R/W                |

| Brightness control                                | 09h     | 80h     | R/W                |

| Color saturation control                          | 0Ah     | 80h     | R/W                |

| Hue control                                       | 0Bh     | 00h     | R/W                |

| Contrast control                                  | 0Ch     | 80h     | R/W                |

| Outputs and data rates select                     | 0Dh     | 47h     | R/W                |

| Luminance processing control #3                   | 0Eh     | 00h     | R/W                |

| Configuration shared pins                         | 0Fh     | 08h     | R/W                |

| Reserved                                          | 10h     |         |                    |

| Active video cropping start MSB for unscaled data | 11h     | 00h     | R/W                |

| Active video cropping start LSB for unscaled data | 12h     | 00h     | R/W                |

| Active video cropping stop MSB for unscaled data  | 13h     | 00h     | R/W                |

| Active video cropping stop LSB for unscaled data  | 14h     | 00h     | R/W                |

| Genlock/RTC                                       | 15h     | 01h     | R/W                |

| Horizontal sync start                             | 16h     | 80h     | R/W                |

| Ancillary SAV/EAV control                         | 17h     | 52h     | R/W                |

| Vertical blanking start                           | 18h     | 00h     | R/W                |

| Vertical blanking stop                            | 19h     | 00h     | R/W                |

| Chrominance processing control #1                 | 1Ah     | 0Ch     | R/W                |

| Chrominance processing control #2                 | 1Bh     | 14h     | R/W                |

| Interrupt reset register B                        | 1Ch     | 00h     | R/W                |

| Interrupt enable register B                       | 1Dh     | 00h     | R/W                |

(1) R = Read only, W = Write only, R/W = Read and write

**Table 7-1. Direct Register Summary (continued)**

| REGISTER FUNCTION                   | ADDRESS | DEFAULT | R/W <sup>(1)</sup> |

|-------------------------------------|---------|---------|--------------------|

| Interrupt configuration register B  | 1Eh     | 00h     | R/W                |

| Output control                      | 1Fh     | 00h     | R/W                |

| Reserved                            | 20h     |         |                    |

| Indirect Register Data              | 21h-22h | 00h     | R/W                |

| Indirect Register Address           | 23h     | 00h     | R/W                |

| Indirect Register Read/Write Strobe | 24h     | 00h     | R/W                |

| AVID start/control for scaled data  | 25h-26h | 00h     | R/W                |

| Reserved                            | 27h     |         |                    |

| Video standard                      | 28h     | 00h     | R/W                |

| AVID stop for scaled data           | 29h–2Ah | 00h     | R/W                |

| Reserved                            | 2Bh     |         |                    |

| Cb gain factor                      | 2Ch     |         | R                  |

| Cr gain factor                      | 2Dh     |         | R                  |

| Reserved                            | 2Eh–2Fh |         |                    |

| 656 Revision Select                 | 30      | 00h     | R/W                |

| Reserved                            | 31h–7Dh |         |                    |

| Patch Write Address                 | 7Eh     | 00h     | R/W <sup>(2)</sup> |

| Patch Code Execute                  | 7Fh     | 00h     | R/W <sup>(2)</sup> |

| MSB of device ID                    | 80h     | 51h     | R                  |

| LSB of device ID                    | 81h     | 54h     | R                  |

| ROM major version                   | 82h     | 02h     | R                  |

| ROM minor version                   | 83h     | 00h     | R                  |

| Vertical line count MSB             | 84h     |         | R                  |

| Vertical line count LSB             | 85h     |         | R                  |

| Interrupt status register B         | 86h     |         | R                  |

| Interrupt active register B         | 87h     |         | R                  |

| Status register #1                  | 88h     |         | R                  |

| Status register #2                  | 89h     |         | R                  |

| Status register #3                  | 8Ah     |         | R                  |

| Status register #4                  | 8Bh     |         | R                  |

| Status register #5                  | 8Ch     |         | R                  |

| Reserved                            | 8Dh     |         |                    |

| Patch Read Address                  | 8Eh     | 00h     | R/W <sup>(2)</sup> |

| Reserved                            | 8Fh     |         |                    |

| Closed caption data registers       | 90h–93h |         | R                  |

| WSS/CGMS-A data registers           | 94h–99h |         | R                  |

| VPS/Gemstar 2x data registers       | 9Ah–A6h |         | R                  |