# **BUCK/BOOST SWITCH-MODE REGULATOR**

Check for Samples: TPIC74101-Q1

#### **FEATURES**

- Qualified for Automotive Applications

- Switch-Mode Regulator

- 5 V ±2%, Buck Mode

- 5 V ±3%, Low-Power or Boost or Boost/buck Crossover Mode

- Switching Frequency, 380 kHz (typical)

- Input Operating Range, 1.5 V to 40 V, (V<sub>driver</sub>)

- 1-A Load-Current Capability

- 200-mA Load-Current Capability Down to 2-V Input (V<sub>driver</sub>)

- 120-mA Load-Current Capability Down to 1.5-V Input (V<sub>driver</sub>)

- Enable Function

- Low-Power Operation Mode

- Switched 5-V Regulated Output on 5Vg With Current Limit

- Programmable Slew Rate and Frequency Modulation for EMI Consideration

- Reset Function With Deglitch Timer and Programmable Delay

- Alarm Function for Undervoltage Detection and Indication

- Thermally Enhanced Package for Efficient Heat Management

## **APPLICATIONS**

Automotive Electronic Controller Power Supply

P0021-02

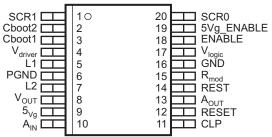

# PWP HTSSOP PACKAGE (TOP VIEW)

## **DESCRIPTION**

The TPIC74101-Q1 is a switch-mode regulator with integrated switches for voltage-mode control. With the aid of external components (LC combination), the device regulates the output to 5 V ±2% for a wide input-voltage range.

The TPIC74101-Q1 offers a reset function to detect and indicate when the 5-V output rail is outside of the specified tolerance. This reset delay is programmable using an external timing capacitor on the REST terminal. Additionally, an alarm  $(A_{OUT})$  feature is activated when the input supply rail  $V_{driver}$  is below a prescaled specified value (set by the  $A_{IN}$  terminal).

The TPIC74101-Q1 has a frequency-modulation scheme to minimize EMI. The clock modulator permits a modulation of the switching frequency to reduce interference energy in the frequency band.

The 5Vg output is a switched 5-V regulated output with internal current limiting to prevent RESET from being asserted when powering a capacitive load on the supply line. This function is controlled by the 5Vg\_ENABLE terminal. If there is a short to ground on this output (5Vg output), the output self-protects by operating in a chopping mode. This does, however, increase the output ripple voltage on V<sub>OUT</sub> during this fault condition.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

SLIS140 - OCTOBER 2011

**INSTRUMENTS**

www.ti.com

| T <sub>A</sub> | PACK         | AGE <sup>(2)</sup> | ORDERABLE PART NUMBER |

|----------------|--------------|--------------------|-----------------------|

| –40°C to 125°C | HTSSOP - PWP | Reel of 2000       | TPIC74101QPWPRQ1      |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- (2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

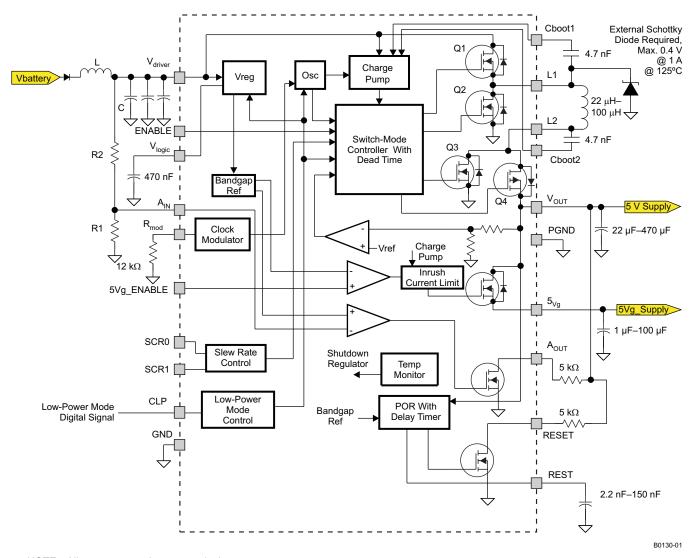

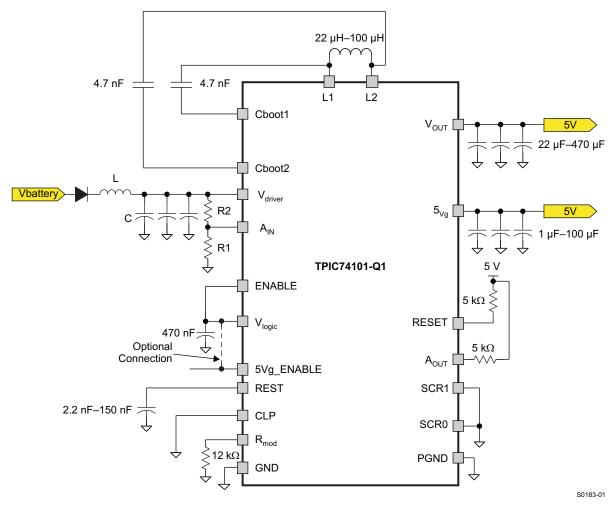

NOTE: All component values are typical.

# **Table 1. Terminal Functions**

| TERMINAL            |     |            | DESCRIPTION                                                                               |  |  |

|---------------------|-----|------------|-------------------------------------------------------------------------------------------|--|--|

| NAME                | NO. | 1/0        | DESCRIPTION                                                                               |  |  |

| SCR1                | 1   | I          | Programmable slew-rate control                                                            |  |  |

| Cboot2              | 2   | I          | External bootstrap capacitor                                                              |  |  |

| Cboot1              | 3   | I          | External bootstrap capacitor                                                              |  |  |

| V <sub>driver</sub> | 4   | I          | Input voltage source                                                                      |  |  |

| L1                  | 5   | I          | Inductor input (an external Schottky diode <sup>(1)</sup> to GND must be connected to L1) |  |  |

| PGND                | 6   | I          | Power ground                                                                              |  |  |

| L2                  | 7   | I          | Inductor output                                                                           |  |  |

| V <sub>OUT</sub>    | 8   | 0          | 5-V regulated output                                                                      |  |  |

| 5Vg                 | 9   | 0          | Switched 5-V supply                                                                       |  |  |

| A <sub>IN</sub>     | 10  | I          | Programmable alarm setting                                                                |  |  |

| CLP                 | 11  | I/O        | Low-power operation mode (digital input)                                                  |  |  |

| RESET               | 12  | 0          | Reset function (open drain)                                                               |  |  |

| A <sub>OUT</sub>    | 13  | 0          | Alarm output (open drain)                                                                 |  |  |

| REST                | 14  | 0          | Programmable reset timer delay                                                            |  |  |

| $R_{mod}$           | 15  | I          | Main switching frequency modulation setting to minimize EMI                               |  |  |

| GND                 | 16  | I          | Ground                                                                                    |  |  |

| V <sub>logic</sub>  | 17  | 0          | Supply decoupling output (may be used as a 5-V supply for logic-level inputs)             |  |  |

| ENABLE              | 18  | I          | Switch-mode regulator enable/disable                                                      |  |  |

| 5Vg_ENABLE          | 19  | I          | Switched 5-V voltage regulator output enable/disable                                      |  |  |

| SCR0                | 20  | I          | Programmable slew-rate control                                                            |  |  |

|                     |     | Exposed th | nermal pad of the package should be connected to GND or left floating.                    |  |  |

<sup>(1)</sup> Maximum 0.4 V at 1 A and 125°C

SLIS140 – OCTOBER 2011 www.ti.com

## **ABSOLUTE MAXIMUM RATINGS**

over recommended operating free-air temperature range (unless otherwise noted)(1)

| Unregulated input voltage                                    | e, V <sub>(driver)</sub> (2)                                                                             | -0.5 V to 40 V                  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

| Unregulated inputs, V <sub>(AIN)</sub>                       | , V <sub>(ENABLE)</sub> (2)                                                                              | –0.5 V to 40 V                  |  |  |

| Bootstrap voltages                                           | V <sub>(Cboot1)</sub>                                                                                    | 52 V                            |  |  |

|                                                              | V <sub>(Cboot2)</sub>                                                                                    | 14 V                            |  |  |

| Switch mode voltages                                         | V <sub>(L1)</sub>                                                                                        | –1 V to 40 V                    |  |  |

|                                                              | V <sub>(L2)</sub>                                                                                        | –1 V to 7 V                     |  |  |

| Logic input voltages, V <sub>(Rn</sub>                       | nod), V <sub>(SCR0)</sub> , V <sub>(SCR1)</sub> , V <sub>(CLP)</sub> , and V <sub>(5Vg_ENABLE)</sub> (2) | –0.5 V to 7 V                   |  |  |

| Low output voltages, V <sub>(RE</sub>                        | ESET), V <sub>(AOUT)</sub> , V <sub>(logic)</sub> , and V <sub>(REST)</sub> (2)                          | –0.5 V to 7 V                   |  |  |

| Electrostatic-discharge                                      | V <sub>(HBMESD)</sub> <sup>(3)</sup> , pin 7 (L2), pin 8 (V <sub>OUT</sub> ), pin 9 (5Vg)                | 800 V                           |  |  |

| susceptibility                                               | V <sub>(HBMESD)</sub> <sup>(3)</sup> , pins 1–6 and 10–20                                                | 2 kV                            |  |  |

| Thermal impedance, junc                                      | tion-to-case, R <sub>0JC</sub> <sup>(4)</sup>                                                            | 2°C/W                           |  |  |

| Thermal impedance,                                           | R <sub>θJA</sub> <sup>(4)</sup>                                                                          | 32°C/W                          |  |  |

| junction-to-ambient                                          | R <sub>0JA</sub> <sup>(5)</sup>                                                                          | 40°C/W                          |  |  |

| Continuous power dissipa                                     | •                                                                                                        | See Dissipation<br>Rating Table |  |  |

| Operating virtual junction temperature range, T <sub>J</sub> |                                                                                                          | -40°C to 150°C                  |  |  |

| Operating ambient temperature range, T <sub>A</sub>          |                                                                                                          |                                 |  |  |

| Storage temperature range, T <sub>stg</sub>                  |                                                                                                          | –65°C to 125°C                  |  |  |

| Lead temperature (soldering, 10 s), T <sub>(LEAD)</sub>      |                                                                                                          |                                 |  |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to ground.

- (3) The human body model is a 100-pF capacitor discharged through a 1.5-kΩ resistor into each terminal.

- (4) The thermal data is based on using 2-oz copper trace with at least four square inches of copper footprint for heat dissipation. The copper pad is soldered to the thermal land pattern. Correct attachment procedure must be incorporated.

- (5) The thermal data is based on using 1-oz copper trace with at least four square inches of copper footprint for heat dissipation. The copper pad is soldered to the thermal land pattern. Correct attachment procedure must be incorporated.

#### **DISSIPATION RATING TABLE**

| $R_{\theta JA}$ | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|-----------------|---------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|

| 32°C/W          | 3.9 W                                 | 31.25 mW/°C                                    | 2.03 W                                | 0.781 W                                |

| 40°C/W          | 3.125 W                               | 25 mW/°C                                       | 1.625 W                               | 0.625 W                                |

## RECOMMENDED OPERATING CONDITIONS

|                                                                                                                               |                          | MIN  | MAX                        | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|----------------------------|------|

| Unregulated input voltage, V <sub>(driver)</sub>                                                                              | 6                        | 24   | V                          |      |

| Unregulated input voltages, V <sub>(AIN)</sub> ar                                                                             | nd V <sub>(ENABLE)</sub> | 0    | 24                         | V    |

| Cuitab mada tarminala                                                                                                         | V <sub>(L1)</sub>        | -1   | 17                         | V    |

| Switch-mode terminals                                                                                                         | $V_{(L2)}$               | 5    | 5.5                        | V    |

| Doctotron voltogo                                                                                                             | V <sub>(Cboot1)</sub>    |      | V <sub>(driver)</sub> + 10 | V    |

| Bootstrap voltages                                                                                                            | V <sub>(Cboot2)</sub>    |      | 8                          | V    |

| Logic levels (I/O), $V_{(Rmod)}$ , $V_{(logic)}$ , $V_{(S}$                                                                   | 0                        | 5.25 | ٧                          |      |

| Operating ambient temperature rang                                                                                            | -40                      | 125  | °C                         |      |

| Logic levels (I/O), V <sub>(SCR0)</sub> , V <sub>(SCR1)</sub> , V <sub>(CLP)</sub> directly connected to V <sub>(logic)</sub> |                          |      | V <sub>(logic)</sub>       | V    |

## **ELECTRICAL CHARACTERISTICS**

$V_{(driver)}$  = 6 V to 17 V,  $T_A$  = -40°C to 125°C, unless otherwise noted

|                        | Parameters                                   | TEST CONDITIONS                                                   | MIN  | TYP  | MAX  | UNIT                                  |  |

|------------------------|----------------------------------------------|-------------------------------------------------------------------|------|------|------|---------------------------------------|--|

| V <sub>(driver)</sub>  | Unregulated input voltage                    |                                                                   | 1.5  |      | 40   | V                                     |  |

| V <sub>(driver)</sub>  | Start-up condition voltage                   | I <sub>O</sub> = 600 mA                                           |      |      | 5    | V                                     |  |

|                        | Coff start range                             | $C_{O} = 36 \mu F \text{ (min) to } 220 \mu F \text{ (max)}$      | 4    |      | 20   | \//                                   |  |

| S <sub>OM</sub>        | Soft-start ramp                              | $C_O = 220 \mu F \text{ (min) to } 470 \mu F \text{ (max)}^{(1)}$ | 2    |      | 20   | V/ms                                  |  |

| I <sub>(standby)</sub> | Standby current                              | ENABLE = low                                                      |      | 10   | 20   | μΑ                                    |  |

| l <sub>q</sub>         | Quiescent current                            | CLP = 0 V, V <sub>(driver)</sub> = 11 V, I <sub>O</sub> = 0 mA    |      | 110  | 160  | μΑ                                    |  |

| Vo                     | Output voltage                               | DC                                                                |      | 5    |      | V                                     |  |

|                        |                                              | Buck mode                                                         |      |      | 2    |                                       |  |

| Vo                     | Output-voltage tolerance                     | Low-Power or Boost or Boost/buck crossover mode                   |      |      | 3    | %                                     |  |

| lo                     | Output current                               | V <sub>(driver)</sub> ≥ 7 V                                       |      |      | 1    | Α                                     |  |

|                        | Output ourrent boost made                    | V <sub>(driver)</sub> = 2 V, see Note <sup>(2)</sup>              |      |      | 200  | mΛ                                    |  |

| I <sub>O(Boost)</sub>  | Output current, boost mode                   | V <sub>(driver)</sub> = 1.5 V, see Note <sup>(2)</sup>            | 120  |      | 120  | mA                                    |  |

| I <sub>PPn</sub>       | Internal peak current limit (normal mode)    | (1)                                                               | 1.75 |      | 2.5  | А                                     |  |

| I <sub>PPI</sub>       | Internal peak current limit (low-power mode) | (1)                                                               | 0.75 |      | 1.25 | А                                     |  |

| l <sub>P</sub>         | Peak current                                 | $V_{(driver)}$ = 16 V, $I_O$ = 1 A, and L = 33 $\mu$ H            |      | 1.5  |      | Α                                     |  |

| V <sub>(driver)</sub>  | Boost/buck crossover voltage window          | See Note (3)                                                      | 5    |      | 5.9  | V                                     |  |

| T <sub>ot</sub>        | Thermal shutdown (4)                         |                                                                   | 160  | 180  | 200  | °C                                    |  |

| 5Vg Output             | and ENABLE                                   |                                                                   |      |      |      |                                       |  |

| r <sub>DS(on)</sub>    | On-state resistance                          |                                                                   |      | 140  | 225  | mΩ                                    |  |

| l <sub>o</sub>         | Output current                               |                                                                   |      |      | 400  | mA                                    |  |

| VI                     | 5Vg_ENABLE input-voltage range               |                                                                   | -0.5 |      | Vo   | V                                     |  |

| V <sub>IH</sub>        | 5Vg_ENABLE threshold high voltage            | V <sub>(5Vg)</sub> = 5 V                                          | 2.5  | 3    | 3.5  | V                                     |  |

| V <sub>IL</sub>        | 5Vg_ENABLE threshold low voltage             | V <sub>(5Vg)</sub> = 0 V                                          | 1.5  | 2    | 2.5  | V                                     |  |

| V <sub>(hys)</sub>     | Hysteresis voltage                           |                                                                   | 0.5  | 1    |      | V                                     |  |

| r <sub>(pd)</sub>      | Internal pulldown resistor                   |                                                                   | 300  | 500  | 850  | kΩ                                    |  |

| ENABLE                 |                                              |                                                                   |      |      |      |                                       |  |

| VI                     | ENABLE input-voltage range                   |                                                                   | -0.5 |      | 40   | V                                     |  |

| V                      | ENABLE throughold high voltage               | 8 V ≤ V <sub>(driver)</sub> ≤ 17 V                                | 2.5  | 3    | 3.5  | \/                                    |  |

| $V_{IH}$               | ENABLE threshold high voltage                | 6 V ≤ V <sub>(driver)</sub> < 8 V                                 | 1.9  | 2.5  | 3.5  | V                                     |  |

| V <sub>IL</sub>        | ENABLE threshold low voltage                 | V <sub>O</sub> = 5 V                                              | 1.5  | 1.85 | 2.5  | V                                     |  |

| \/                     | Hyptorogic voltage                           | 8 V ≤ V <sub>(driver)</sub> ≤ 17 V                                | 0.5  | 1    |      | · · · · · · · · · · · · · · · · · · · |  |

| $V_{(hys)}$            | Hysteresis voltage                           | 6 V ≤ V <sub>(driver)</sub> < 8 V                                 | 0.1  | -    |      | V                                     |  |

<sup>(1)</sup> Ensured by characterization

<sup>(2)</sup> Tested with inductor having following characteristics: L = 33 μH, R<sub>max</sub> = 0.1 Ω, I<sub>R</sub> = 1.8 A. Output current must be verified in application when inductor R<sub>max</sub> (ESR) is increased.

<sup>(3)</sup> Ensured by characterization. For further details, see the Buck/Boost Transitioning section.

<sup>(4)</sup> Ensured by characterization; hysteresis 15°C (typical)

SLIS140 – OCTOBER 2011 www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{(driver)}$  = 6 V to 17 V,  $T_A$  = -40°C to 125°C, unless otherwise noted

|                      | Parameters                             | TEST CONDITIONS                                                     | MIN  | TYP  | MAX  | UNIT |  |  |

|----------------------|----------------------------------------|---------------------------------------------------------------------|------|------|------|------|--|--|

| RESET                |                                        | ·                                                                   |      |      |      |      |  |  |

| V <sub>(th)</sub>    | RESET threshold voltage                |                                                                     | 4.51 | 4.65 | 4.79 | V    |  |  |

| V <sub>(RESET)</sub> | RESET tolerance                        |                                                                     |      |      | 3%   |      |  |  |

|                      | DECET (to a                            | C <sub>(REST)</sub> = 10 nF                                         | 8 10 | 12   |      |      |  |  |

| (RESET)              | RESET time                             | C <sub>(REST)</sub> = 100 nF, see Note <sup>(5)</sup>               | 80   | 100  | 120  | ms   |  |  |

| ,                    | DECET autout laurus lie au             | I <sub>sink</sub> = 5 mA                                            |      |      | 450  | \/   |  |  |

| V <sub>OL</sub>      | RESET output low voltage               | I <sub>sink</sub> = 1 mA                                            |      |      | 84   | mV   |  |  |

| (deglitch)           | RESET deglitch time                    | See Note <sup>(5)</sup>                                             | 8    | 10   | 12.5 | μs   |  |  |

| Alarm                |                                        |                                                                     |      |      |      |      |  |  |

| V <sub>I</sub>       | Alarm input-voltage range              |                                                                     | -0.5 |      | 40   | V    |  |  |

| / <sub>IL</sub>      | Alarm threshold low voltage            |                                                                     | 2.2  | 2.3  | 2.35 | V    |  |  |

| / <sub>IH</sub>      | Alarm threshold high voltage           |                                                                     | 2.43 | 2.5  | 2.58 | V    |  |  |

| / <sub>(hys)</sub>   | Hysteresis voltage                     |                                                                     |      | 240  |      | mV   |  |  |

|                      | Alarm autout lauvualtaga               | I <sub>sink</sub> = 5 mA                                            |      |      | 450  | m\/  |  |  |

| / <sub>OL</sub>      | Alarm output low voltage               | I <sub>sink</sub> = 1 mA                                            |      |      | 84   | mV   |  |  |

| _ow-Power            | Mode (Pulse Mode) PFM                  |                                                                     |      |      |      |      |  |  |

| O(LPM)               | Load current in low-power mode         | V <sub>(driver)</sub> < 7 V                                         |      |      | 50   | mA   |  |  |

| I(avg)               | Average input current                  | $V_{(driver)} = 11 \text{ V}, I_O = 5 \text{ mA}, CLP = \text{low}$ |      |      | 3.55 | mA   |  |  |

| / <sub>0</sub>       | Output-voltage tolerance               | V <sub>O</sub> = 5 V                                                |      | 2.4% | 3%   |      |  |  |

| Digital Low-         | Power Mode (CLP)                       |                                                                     |      |      |      |      |  |  |

| J <sub>IH</sub>      | High-level CLP input threshold voltage | Normal mode                                                         | 2.6  |      |      | V    |  |  |

| $I_{IL}$             | Low-level CLP input threshold voltage  | Low-power mode                                                      |      |      | 1.15 | V    |  |  |

| Switching P          | arameters                              |                                                                     |      |      |      |      |  |  |

| (sw)                 | Switching frequency                    | V <sub>(Rmod)</sub> = 0 V, modulator OFF                            |      | 380  |      | kHz  |  |  |

| (sw)ac               | Operating-frequency accuracy           | $f_{(sw)} = 380 \text{ kHz}$                                        |      |      | 20   | %    |  |  |

| (sw)min              | Modulation minimum frequency           |                                                                     | 230  | 285  | 385  | kHz  |  |  |

| (sw)max              | Modulation maximum frequency           |                                                                     | 390  | 480  | 590  | kHz  |  |  |

| (mod)span            | Modulation span                        |                                                                     |      | 220  |      | kHz  |  |  |

| (mod)                | Modulation frequency                   | $R_{\text{mod}} = 12 \text{ k}\Omega \pm 1\%$                       |      | 28   |      | kHz  |  |  |

| (mod)ac              | Modulation-frequency accuracy          |                                                                     |      |      | 12   | %    |  |  |

<sup>(5)</sup> Ensured by characterization

#### PRINCIPLES OF OPERATION

## **Functional Principle**

The TPIC74101-Q1 is a buck/boost switch-mode regulator that operates in a power-supply concept to ensure a stable output voltage with input voltage excursions and specified load range.

The device provides an alarm indicator and reset output to interface with systems that require supervisory function.

The switching regulator offers a clock modulator and a current-mode slew-rate control for the internal switching transistor (Q1) to minimize EMI.

An internal low-r<sub>DS(on)</sub> switch has a current-limit feature to prevent inadvertent reset when turning on the 5Vg output.

## **Description of the Functional Terminals**

## Switch-Mode Input/Output Terminals (L1, L2)

The external inductor for the switch-mode regulator is connected between terminals L1 and L2. This inductor is placed close to the terminals to minimize parasitic effects. For stability, an inductor with 20 µH to 100 µH should be used.

## Supply Terminal (V<sub>driver</sub>)

The input voltage of the device is connected to the  $V_{driver}$  terminal. This input line requires a filter capacitor to minimize noise. A low-ESR aluminum or tantalum input capacitor is recommended. The relevant parameters for the input capacitor are the voltage rating and RMS current rating. The voltage rating should be approximately 1.5 times the maximum applied voltage for an aluminum capacitor and 2 times for a tantalum capacitor. In buck

mode, the RMS current is  $I_{\text{OUT}} \times \sqrt{D-D^2}$ , where D is the duty cycle and its maximum RMS current value is reached when D = 50% with  $I_{\text{RMS}} = I_{\text{OUT}}/2$ . In boost mode, the RMS current is 0.3 ×  $\Delta I$ , where  $\Delta I$  is the peak-to-peak ripple current in the inductor. To achieve this, ESR ceramic capacitors are used in parallel with the aluminum or tantalum capacitors.

## Internal Supply Decoupling Terminal (V<sub>logic</sub>)

The  $V_{logic}$  terminal is used to decouple the internal power-supply noise by use of a 470-nF capacitor. This terminal can also be used as an output supply for the logic-level inputs for this device (SCR0, SCR1, ENABLE, CLP, and  $5Vg\_ENABLE$ ).

## Input Voltage Monitoring Terminal (AIN)

The  $A_{IN}$  terminal is used to program the threshold voltage for monitoring and detecting undervoltage conditions on the input supply. A maximum of 40 V may be applied to this terminal and the voltage at this terminal may exceed the  $V_{(driver)}$  input voltage without effecting the device operation. The resistor divider network is programmed to set the undervoltage detection threshold on this terminal (see the application schematic). The input has a typical hysteresis of 200 mV with a typical upper limit threshold of 2.5 V and a typical lower limit threshold of 2.3 V. When  $V_{(AIN)}$  falls below 2.3 V,  $V_{(AOUT)}$  is asserted low; when  $V_{(AIN)}$  exceeds 2.5 V,  $V_{(AOUT)}$  is in the high-impedance state.

The equations to set the upper and lower thresholds of  $V_{(AIN)}$  are:

Upper:

$$V_{(driver)} = 2.5 \text{ V} \times \frac{\text{R1} + \text{R2}}{\text{R1}}$$

Lower:

$$V_{(driver)} = 2.3 \text{ V} \times \frac{\text{R1} + \text{R2}}{\text{R1}}$$

(1)

SLIS140 – OCTOBER 2011 www.ti.com

#### Input Undervoltage Alarm Terminal (A<sub>OUT</sub>)

The  $A_{OUT}$  terminal is an open-drain output that asserts low when the input voltage falls below the set threshold on the  $A_{IN}$  input.

#### **Reset Delay Timer Terminal (REST)**

The REST terminal sets the desired delay time to assert the RESET terminal low after the 5-V supply has exceeded 4.65 V (typical). The delay can be programmed in the range of 2.2 ms to 150 ms using capacitors in the range of 2.2 nF to 150 nF. The delay time is calculated using the following equation:

RESET delay =  $C_{(REST)} \times 1$  ms, where  $C_{(REST)}$  has nF units

### **Reset Terminal (RESET)**

The RESET terminal is an open-drain output. The power-on reset output is asserted low until the output voltage exceeds the 4.65-V threshold and the reset delay timer has expired. Additionally, whenever the ENABLE terminal is low, RESET is immediately asserted low regardless of the output voltage.

## Main Regulator Output Terminal (Vout)

The  $V_{OUT}$  terminal is the output of the switch-mode regulated supply. This terminal requires a filter capacitor with low-ESR characteristics to minimize output ripple voltage. For stability, a capacitor with 22  $\mu$ F to 470  $\mu$ F should be used. The total capacitance at pin  $V_{OUT}$  and pin 5Vg must be less than or equal to 470  $\mu$ F.

#### Low-Power-Mode Terminal (CLP)

The CLP terminal controls the low-power mode of the device. An external low digital signal switches the device to low-power mode or normal mode when the input is high.

#### Switch-Output Terminal (5Vg)

The 5Vg terminal switches the 5-V regulated output. The output voltage of the regulator can be enabled or disabled using this low- $r_{DS(on)}$  internal switch. This switch has a current-limiting function to prevent generation of a reset signal at turnon caused by the capacitive load on the output or overload condition. When the switch is enabled, the regulated output may deviate and drop momentarily to a tolerance of 7% until the 5Vg capacitor is fully charged. This deviation depends on the characteristics of the capacitors on  $V_{OUT}$  and 5Vg.

#### 5Vg-Enable Terminal (5Vg ENABLE)

The 5Vg\_ENABLE is a logic-level input for enabling the switch output on 5Vg.

For the functional terminal, 5Vg\_ENABLE results in the following table:

| 5Vg_ENABLE                                 | FUNCTION   |

|--------------------------------------------|------------|

| 0                                          | 5Vg is off |

| Open (internal pulldown = 500 k $\Omega$ ) | 5Vg is off |

| 1                                          | 5Vg is on  |

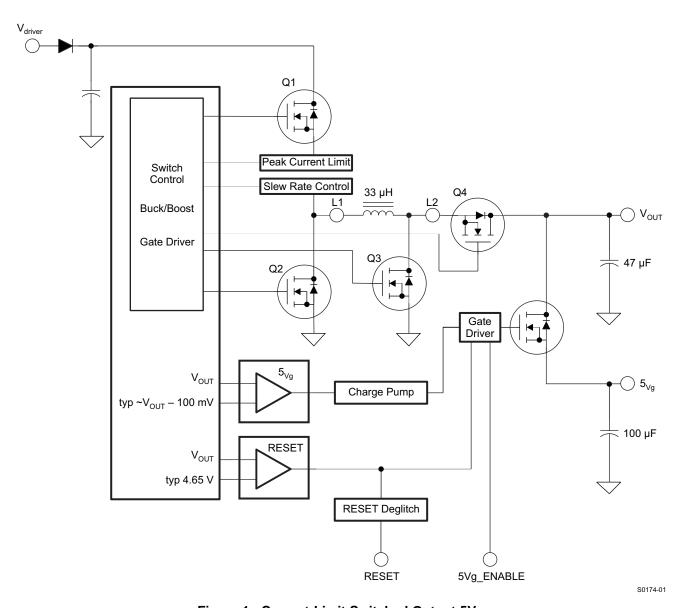

Figure 1. Current-Limit Switched Output 5Vg

## Slew-Rate Control Terminals (SCR0, SCR1)

The slew rate of the switching transistor Q1 is set using the SCR0 and SCR1 terminals.

The following table shows the values of the slew rate (SR):

| SCR1 | SCR0 | SR <sub>Q1</sub> |

|------|------|------------------|

| 0    | 0    | Slow             |

| 0    | 1    | Medium-slow      |

| 1    | 0    | Medium-fast      |

| 1    | 1    | Fast             |

SLIS140 – OCTOBER 2011 www.ti.com

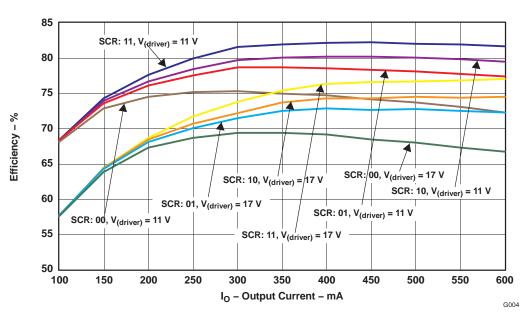

See the converter efficiency plots in the *Typical Characteristics* section to determine power dissipation.

## Modulator Frequency Setting (Terminal R<sub>mod</sub>)

The  $R_{mod}$  terminal adjusts the clock modulator frequency. A resistor of  $R_{mod}$  = 12 k $\Omega$  generates a modulation frequency of 28 kHz. The modulator function may be disabled by connecting  $R_{mod}$  to GND and the device operates with the nominal frequency. The modulator function cannot be activated during IC operation, only at IC start-up.

#### **Ground Terminal (PGND)**

The PGND terminal is the power ground for the device.

#### **Enable Terminal (ENABLE)**

The ENABLE terminal allows the enabling and disabling of the switch mode regulator. A maximum of 40 V may be applied to this terminal to enable the device and increasing it above the  $V_{(driver)}$  input voltage does not affect the device operation.

The functionality of the ENABLE terminal is described in the following table:

| ENABLE | FUNCTION     |

|--------|--------------|

| 0      | Vreg is off. |

| Open   | Undefined    |

| 1      | Vreg is on.  |

## **Bootstrap Terminals (Cboot1 and Cboot2)**

An external bootstrap capacitor is required for driving the internal high-side MOSFET switch. A 4.7-nF ceramic capacitor is typically required.

#### **Functional Modes**

#### **Clock Modulator**

To minimize EMI issues associated with the switch-mode regulator, the device offers an integrated clock modulator. The function of the clock modulator is to modulate the switching frequency and to distribute the energy over the wave band.

The average switching frequency is 380 kHz (typical) and varies between 285 kHz and 480 kHz at a rate set by the  $R_{mod}$  resistor. A typical value of 12 k $\Omega$  on the  $R_{mod}$  terminal relates to a 28-kHz modulation frequency. The clock modulator function can only be activated during IC start-up, not during IC operation.

The equation for the modulation frequency is as follows:

$f_{(mod)}$  (Hz) = (-2.2 ×  $R_{mod}$ ) + 54.5 kHz, when  $R_{mod}$  = 8 k $\Omega$  to 16 k $\Omega$ . Bigger resistor values like 100 k $\Omega$  are also allowed for Rmod.

#### **Buck/Boost Transitioning**

The operation mode switches automatically between buck and boost modes depending on the input voltage of  $V_{(driver)}$  and output load conditions. During start up, when  $V_{(driver)}$  is less than 5.8 V (typical), the device starts in boost mode and continues to run in boost mode until  $V_{(driver)}$  exceeds 5.8 V; at which time, the device switches over to buck mode. In buck mode, the device continues to run in buck mode until it is required to switch back to boost to hold regulation. This crossover window to switch to boost mode is when  $V_{(driver)}$  is between 5.8 V and 5 V and depends on the loading conditions. When  $V_{driver}$  drops below 5.8 V but the device is holding regulation (~2%), the device remains in buck mode. However, when  $V_{(driver)}$  is within the 5.8-V to 5-V window and  $V_{OUT}$  drops to 4.9 V, the device crosses over to boost mode to hold regulation. In boost mode, the device remains in

boost mode until  $V_{(driver)}$  exceeds 5.8 V; at which time, the device enters the buck mode. When the device is operating in boost mode and  $V_{(driver)}$  is in the crossover window of 5.8 V to 5 V, the output regulation may contain a higher than normal ripple and only maintain a 3% tolerance. This ripple and tolerance depends on the loading and improves with a higher loading condition. When the device is operated with low-power mode active (CLP = low) and high output currents (>50 mA), the buck/boost transitioning can cause a reset signal at the RESET pin.

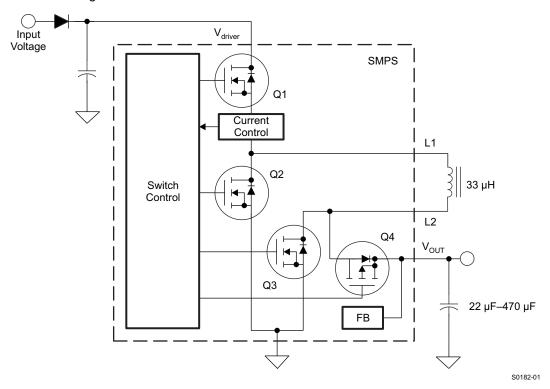

#### **Buck SMPS**

In buck mode, the duty cycle of transistor Q1 sets the voltage  $V_{OUT}$ . The duty cycle of transistor Q1 varies 10% to 99% depending on the input voltage,  $V_{(driver)}$ . If the peak inductor current (measured by Q1) exceeds 450 mA (typical), Q2 is turned on for this cycle (synchronized rectification). Otherwise, the current recirculates through Q2 as a free-wheeling diode. The detection for synchronous or asynchronous mode is done cycle-by-cycle.

To avoid a cross-conduction current between Q1 and Q2, an inherent delay is incorporated when switching Q1 off and Q2 on and vice versa.

In buck mode, transistor Q3 is not required and is switched off. Transistor Q4 is switched on to reduce power dissipation.

The switch timings for transistors Q3 and Q4 are not considered. In buck mode, the logical control of the transistors does not change.

Figure 2. Buck/Boost Switch Mode Configuration

#### **Boost SMPS**

In boost mode, the duty cycle of transistor Q3 controls the output voltage  $V_{OUT}$ . The duty cycle is internally adjusted 5% to 85% depending on the internally sensed voltage of the output. Synchronized rectification occurs when  $V_{(driver)}$  is below 5 V.

To avoid a discharging of the buffer capacitor, a simultaneous switching on of Q3 and Q4 is not allowed. An inherent delay is incorporated between Q3 switching off and Q4 switching on and vice versa.

In boost mode, transistor Q2 is not required and remains off. Transistor Q1 is switched on for the duration of the boost-mode operation (serves as a supply line).

Copyright © 2011, Texas Instruments Incorporated

SLIS140 – OCTOBER 2011 www.ti.com

The switch timings of transistors Q1 and Q2 are not considered. In boost mode, the logical control of the transistors does not change.

## Extension of the Input Voltage Range on V<sub>(driver)</sub>

To ensure a stable 5-V output voltage with the output load in the specified range, the  $V_{(driver)}$  supply must be greater than or equal to 5 V for greater than 1 ms (typical). After a period of 1 ms (typical), the logic may be supplied by the  $V_{OUT}$  regulator and the  $V_{(driver)}$  supply may be capable of operating down to 1.5 V.

The switch-mode regulator does not start at V<sub>(driver)</sub> less than 5 V.

#### Low-Power Mode

To reduce quiescent current and to provide efficient operation, the regulator enters a pulsed mode.

The device enters this mode by a logic-level low on this terminal.

Automatic low-power mode is not available. The low-power-mode function is not available in boost mode. The device leaves low-power mode during boost mode regardless of the logic level on the CLP terminal.

#### **Temperature and Short-Circuit Protection**

To prevent thermal destruction, the device offers overtemperature protection to disable the IC. Also, short-circuit protection is included for added protection on  $V_{OUT}$  and 5Vg.

#### Switch Output Terminal (5Vg) Current Limitation

A charge pump drives the internal FET, which switches the primary output voltage  $V_{OUT}$  to the 5Vg pin. Protection is implemented to prevent the output voltage from dropping below its specified value while enabling the secondary output voltage. An explanation of the block diagram (see Figure 1) is given by the following example:

- Device is enabled, output voltage V<sub>OUT</sub> is up and stable.

- 5Vg is enabled (pin 5Vg\_ENABLE set to high) with load resistance connected to 5Vg pin.

- If output voltage V<sub>OUT</sub> drops below typical (V<sub>OUT</sub> 100 mV), the charge pump of the 5Vg FET is switched off and the FET remains on for a while as the gate voltage drops slowly.

- If V<sub>OUT</sub> drops below the RESET threshold of 4.65 V (typical), the FET of the secondary output voltage 5Vg is switched off (gate drawn to ground level).

- A deglitch time ensures that a device reset does not occur if V<sub>OUT</sub> drops to the reset level during the 5Vg turnon phase.

- If V<sub>OUT</sub> rises above typical (V<sub>OUT</sub> 100 mV), the charge pump of the 5Vg FET is switched on and drives the gate of the 5Vg FET on.

#### **Soft Start**

On power up, the device offers a soft-start feature which ramps the output of the regulator at a slew of 10 V/ms. When a reset occurs, the soft start is reenabled. Additionally, if the output capacitor is greater than 220 µF (typical), the slew rate decreases to a value set by the internal current limit. In boost mode, the soft-start feature is not active.

## **TYPICAL CHARACTERISTICS**

Maximum characteristic specified by design.

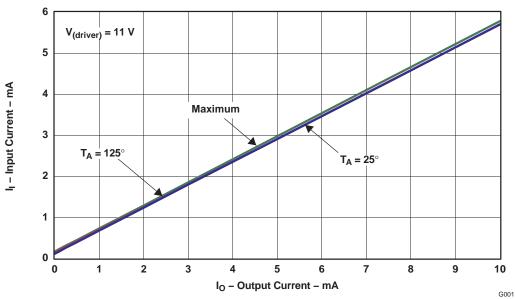

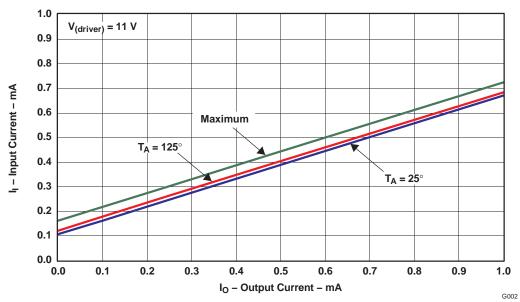

Figure 3. Low-Power Mode Current, I<sub>O</sub> = 0 mA-10 mA

Maximum characteristic specified by design.

Figure 4. Low-Power-Mode Current, I<sub>O</sub> = 0 mA-1 mA

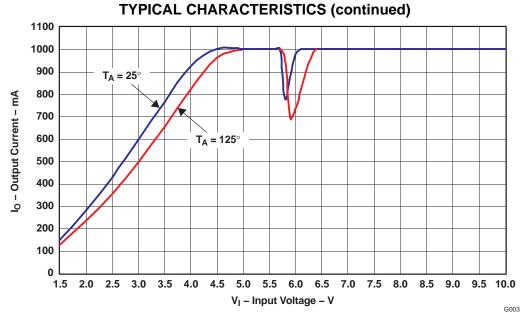

- (1) Typical representation of input voltage vs output load current at T<sub>A</sub> = 25°C and 125°C, after the correct power-up sequence is invoked.

- (2) The dip in the output current at 5.8 V is caused by the buck/boost transition of the IC.

- (3) The output current is clipped to 1 A by the measurement setup.

Figure 5. Typical Input Voltage (V<sub>(driver)</sub>) vs Maximum Output Load Current (I<sub>O</sub>)

The average converter efficiency with four different slew rate controls (SCRx) on the Q1 switching FET with input voltage  $V_{(driver)} = 11 \text{ V}$  and 17 V,  $T_A = 125^{\circ}\text{C}$ .

Figure 6. Converter Efficiency

www.ti.com

# TYPICAL CHARACTERISTICS (continued)

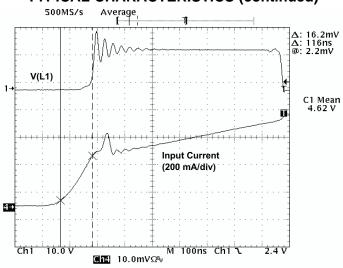

Figure 7. Input Current With Slope Control, SCR0 = 0, SCR1 = 0, Input-Current Slew Rate = 2.8 A/ $\mu$ s, I<sub>L</sub> = 500 mA, V<sub>(driver)</sub> = 15 V

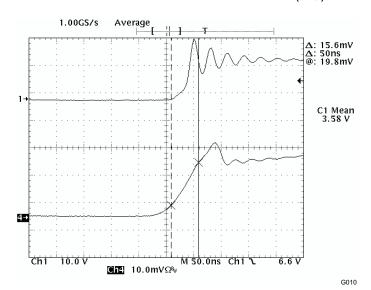

Figure 8. Input Current With Slope Control, SCR1 = 0, SCR0 = 1, Input-Current Slew Rate = 6.25 A/ $\mu$ s, I $_L$  = 500 mA, V $_{(driver)}$  = 15 V

# TYPICAL CHARACTERISTICS (continued)

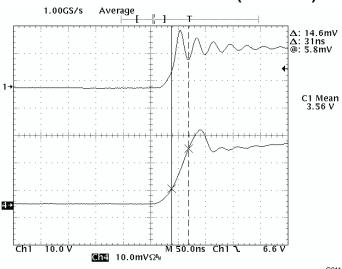

Figure 9. Input Current With Slope Control, SCR1 = 1, SCR0 = 0, Input-Current Slew Rate = 9.4 A/ $\mu$ s, I<sub>L</sub> = 500 mA, V<sub>(driver)</sub> = 15 V

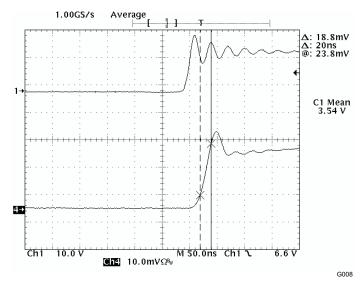

Figure 10. Input Current With Slope Control, SCR0 = 1, SCR1 = 1, Input-Current Slew Rate = 18.8 A/ $\mu$ s, I $_L$  = 500 mA, V $_{(driver)}$  = 15 V

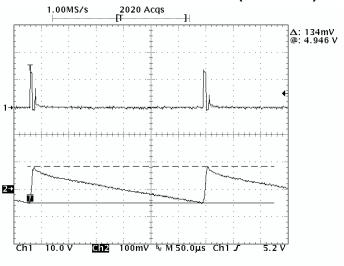

# **TYPICAL CHARACTERISTICS (continued)**

Figure 11. Low-Power-Mode Operation,  $I_L$  = 15 mA,  $C_O$  = 47  $\mu\text{F}$

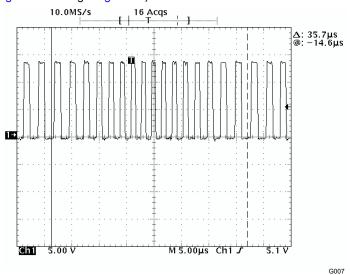

Figure 12. Nominal Switching Frequency of Q1 Switch (446 kHz) With Modulation Function Disabled,  $I_L=200\ mA$

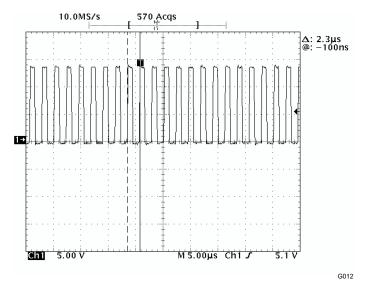

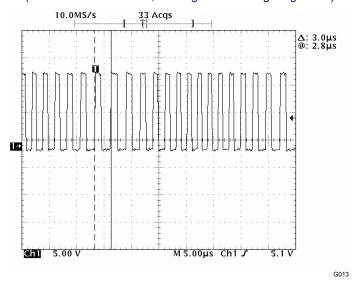

# **TYPICAL CHARACTERISTICS (continued)**

(Reference L1 Terminal, see Figure 13 through Figure 15)

Figure 13. Minimum Switching Frequency (333 kHz) With Modulation Enabled,  $R_{mod}$  = 12  $k\Omega,\,I_L$  = 200 mA

Figure 14. Maximum Switching Frequency (555 kHz) With Modulation Enabled,  $R_{mod}$  = 12 k $\Omega,\,I_L$  = 200 mA

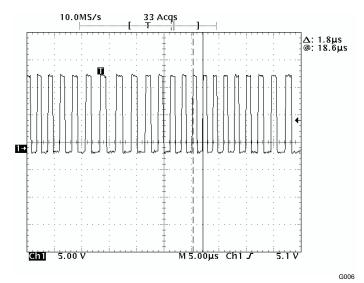

# **TYPICAL CHARACTERISTICS (continued)**

(Reference L1 Terminal, see Figure 13 through Figure 15)

Figure 15. Modulation Frequency (Full Span) of 28 kHz

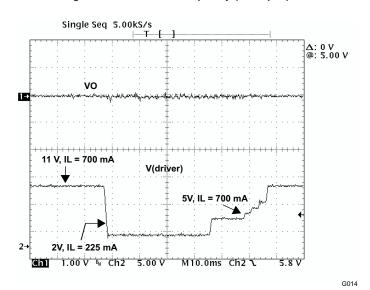

Figure 16. Input Voltage Excursions (Similar to Low-Crank Conditions)

# **TYPICAL CHARACTERISTICS (continued)**

(Reference L1 Terminal, see Figure 13 through Figure 15)

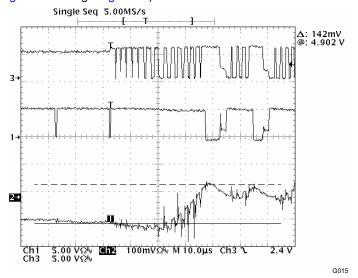

Figure 17. Switch-Mode Regulator Transition From Buck Mode to Boost Mode,  $I_L$  = 400 mA

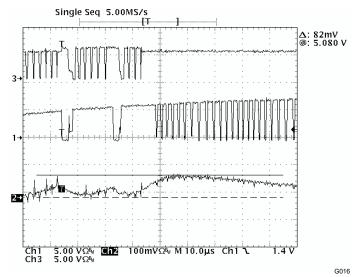

Figure 18. Switch-Mode Regulator Transition From Boost Mode to Buck Mode,  $I_L$  = 400 mA

20

SLIS140 - OCTOBER 2011 www.ti.com

## TYPICAL CHARACTERISTICS (continued)

(Reference L1 Terminal, see Figure 13 through Figure 15)

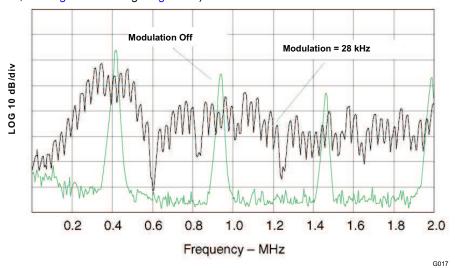

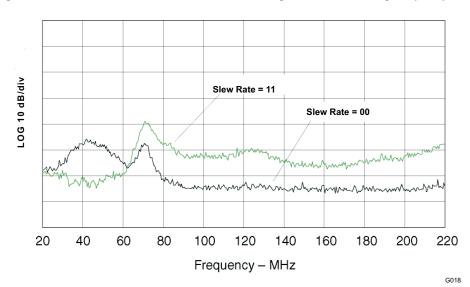

These values represent conducted EMI results of a test board for display purposes only. Actual results may vary greatly depending on board layout and external components and must be verified in actual application.

Figure 19. Conducted Emissions on Test Board Showing Effects of Switching-Frequency Modulation

These values represent conducted EMI results of a test board for display purposes only. Actual results may vary greatly depending on board layout and external components and must be verified in actual application.

Figure 20. Conducted Emissions on Test Board Showing Effects of Minimum and Maximum Slew Rate Settings

Product Folder Link(s): TPIC74101-Q1

SLIS140 – OCTOBER 2011 www.ti.com

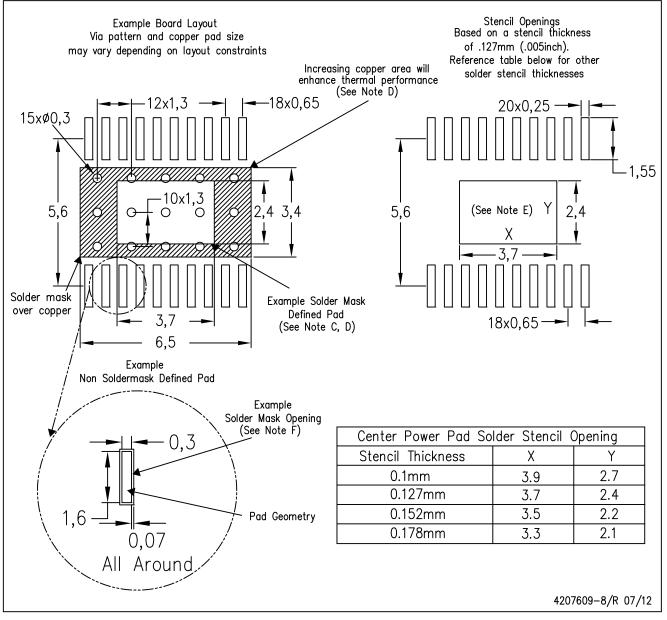

#### APPLICATION INFORMATION

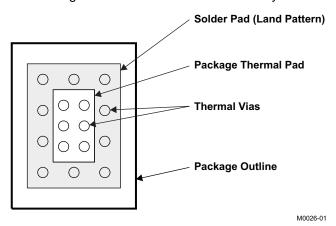

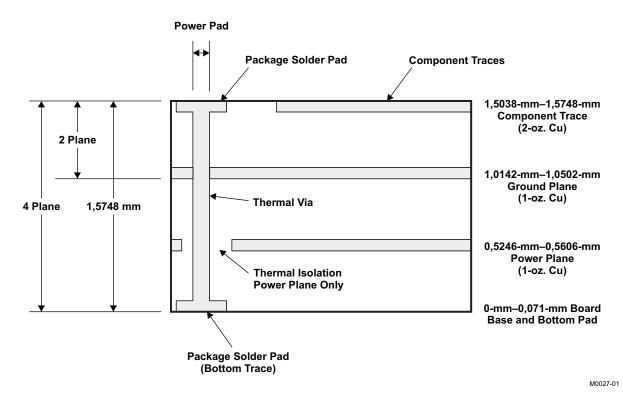

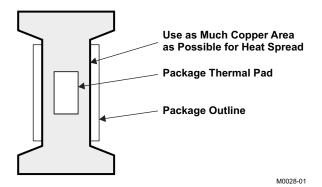

To maximize the efficiency of this package for application on a single-layer or multilayer PCB, certain guidelines must be followed when laying out this device on the PCB.

The following information is to be used as a guideline only.

For further information see the PowerPAD Thermally Enhanced Package technical brief (SLMA002).

The following are guidelines for mounting the PowerPAD™ IC on a multilayer PCB with a ground plane

Figure 21. Package and PCB Land Configuration for a Multilayer PCB

Figure 22. Multilayer Board (Side View)

In a multilayer board application, the thermal vias are the primary method of heat transfer from the package thermal pad to the internal ground plane.

The efficiency of this method depends on several factors (die area, number of thermal vias, thickness of copper, etc.). See the *PowerPAD Thermally Enhanced Package* technical brief (SLMA002).

Figure 23. Land Configuration for Single-Layer PCB

Layout recommendation is to use as much copper area for the power-management section of a single-layer board as possible. In a single-layer board application, the thermal pad is attached to a heat spreader (copper areas) by using a low-thermal-impedance attachment method (solder paste or thermal-conductive epoxy). In both of these cases, it is advisable to use as much copper and as many traces as possible to dissipate the heat.

## **IMPORTANT**

When this attachment method is not implemented correctly, this product may operate inefficiently. Power dissipation capability may be adversely affected when the device is incorrectly mounted onto the circuit board.

**NSTRUMENTS**

SLIS140 – OCTOBER 2011 www.ti.com

- A. To minimize voltage ripple on the output due to transients, it is recommended to use a low-ESR capacitor on the V<sub>OUT</sub> line.

- B. The L and C component values are system application dependent for EMI consideration.

Figure 24. Application Schematic

## **Layout Guidelines for Switch-Mode Power Supply**

The following guidelines are recommended for PCB layout of the TPIC74101-Q1 device.

#### Inductor

Use a low-EMI inductor with a ferrite-type closed core. Other types of inductors may be used; however, they must have low-EMI characteristics and be located away from the low-power traces and components in the circuit.

#### **Filter Capacitors**

Input ceramic filter capacitors should be located in the close proximity of the  $V_{driver}$  terminal. Surface-mount capacitors are recommended to minimize lead length and reduce noise coupling.

#### **Traces and Ground Plane**

All power (high-current) traces should be thick and as short as possible. The inductor and output capacitors should be as close to each other as possible. This reduces EMI radiated by the power traces due to high switching currents.

In a two-sided PCB, it is recommended to have ground planes on both sides of the PCB to help reduce noise and ground-loop errors. The ground connection for the input and output capacitors and IC ground should be connected to this ground plane.

In a multilayer PCB, the ground plane is used to separate the power plane (where high switching currents and components are placed) from the signal plane (where the feedback trace and components are) for improved performance.

Also, arrange the components such that the switching-current loops curl in the same direction. Place the high-current components such that during conduction, the current path is in the same direction. This prevents magnetic field reversal caused by the traces between the two half-cycles, helping to reduce radiated EMI.

#### **Buck Mode**

- Select inductor ripple current ΔI<sub>1</sub>: for example ΔI<sub>1</sub> = 0.2 × I<sub>OUT</sub>

- Calculate inductor L

$$L = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{f_{SW} \times \Delta I_L \times V_{IN}} \quad (H)$$

(2)

where f<sub>SW</sub> is the regulator switching frequency.

Inductor peak current

$$I_{L,max} = I_{OUT} + \frac{\Delta I_L}{2} \quad (A)$$

Output voltage ripple

$$\Delta V_{OUT} = \Delta I_{L} \times \left( ESR + \frac{1}{8 \times f_{SW} \times C_{OUT}} \right) \quad (V_{(p-p)})$$

(4)

Usually, the first term is dominant.

$$C_{OUT} = \frac{I_{pk}(t_{on} + t_{off})}{8 \times V_{ripple}}$$

(F) (5)

## **Boost Mode**

- Select inductor ripple current  $\Delta I_1$ : for example  $\Delta I_1 = 0.2 \times I_{1N}$

- · Calculate inductor L

$$L = \frac{(V_{OUT} - V_{IN}) \times V_{IN}}{f_{SW} \times \Delta I_L \times V_{OUT}} \quad (H)$$

(6)

where f<sub>SW</sub> is the regulator switching frequency.

Inductor peak current

$$I_{p} = I_{L,max} = I_{IN} + \frac{\Delta I_{L}}{2} \quad (A)$$

· Output voltage ripple

$$\Delta V_{OUT} = I_{p} \times ESR + \frac{I_{OUT} \times \left(1 - \frac{V_{IN}}{V_{OUT}}\right)}{f_{SW} \times C_{OUT}} \quad (V_{(p-p)})$$

(8)

Copyright © 2011, Texas Instruments Incorporated

# PACKAGE OPTION ADDENDUM

12-Oct-2012

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TPIC74101QPWPRQ1 | ACTIVE                | HTSSOP       | PWP                | 20   | 1           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR          |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 12-Oct-2012

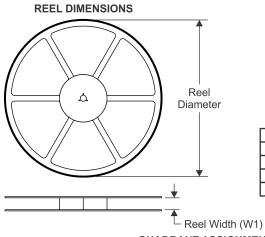

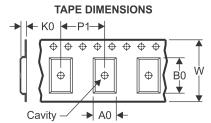

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

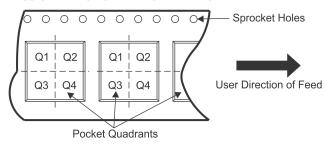

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPIC74101QPWPRQ1 | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

www.ti.com 12-Oct-2012

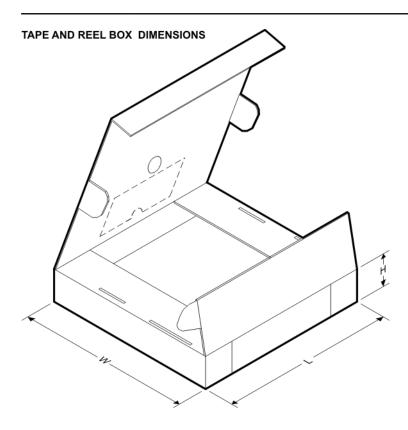

#### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPIC74101QPWPRQ1 | HTSSOP       | PWP             | 20   | 2000 | 367.0       | 367.0      | 38.0        |

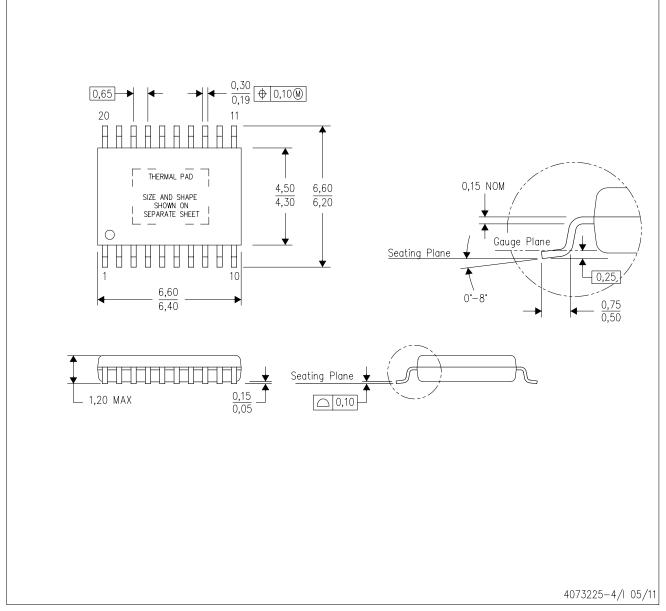

PWP (R-PDSO-G20)

# PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

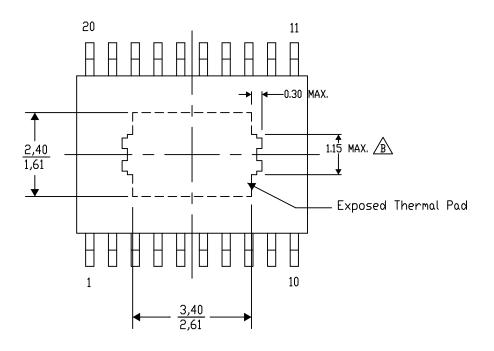

# PWP (R-PDSO-G20) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-15/AC 07/12

NOTE: A. All linear dimensions are in millimeters

Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

# PWP (R-PDSO-G20)

# PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

#### Products Applications

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers DI P® Products Consumer Electronics www.dlp.com www.ti.com/consumer-apps

DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface Medical www.ti.com/medical interface.ti.com Logic logic.ti.com Security www.ti.com/security

Power Mgmt <u>power.ti.com</u> Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>