# 30-MHz TO 66-MHz, 10:1 LVDS SERIALIZER/DESERIALIZER

## FEATURES

- 300-Mbps to 660-Mbps Serial LVDS Data Payload Bandwidth at 30-MHz to 66-MHz System Clock

- Pin-Compatible Superset of NSM DS92LV1023/DS92LV1224

RUMENTS

www.ti.com

- Chipset (Serializer/Deserializer) Power Consumption <450 mW (Typ) at 66 MHz</li>

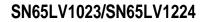

- SN65LV1023 Serializer SYNC1 III 1 O 28 SYNC2 27 2 26 3 D<sub>IN1</sub> 🗖 4 25 AGND D<sub>IN2</sub> 24 5 D<sub>IN3</sub> 23 6 AGND D<sub>IN4</sub> 7 22 🖵 D<sub>0</sub>+ \_\_\_ D<sub>0</sub>-D<sub>IN5</sub> 21 8 D<sub>IN6</sub> 9 20 AGND 10 19 DEN 11 18 AGND 17 D<sub>IN9</sub> 12 TCLK\_R/F DGND 13 16 TCLK 🗖 14 15

- Synchronization Mode for Faster Lock

- Lock Indicator

- No External Components Required for PLL

- Low-Cost 28-Pin SSOP Package

- Industrial Temperature Qualified, T<sub>A</sub> = -40°C to 85°C

- Programmable Edge Trigger on Clock

- Flow-Through Pinout for Easy PCB Layout

## DESCRIPTION

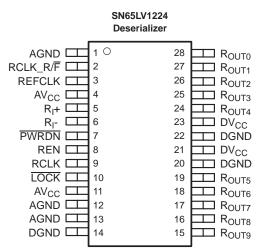

The SN65LV1023 serializer and SN65LV1224 deserializer comprise a 10-bit serdes chipset designed to transmit and receive serial data over LVDS differential backplanes at equivalent parallel word rates from 30 MHz to 66 MHz. Including overhead, this translates into a serial data rate between 360-Mbps and 792-Mbps payload encoded throughput.

Upon power up, the chipset link can be initialized via a synchronization mode with internally generated SYNC patterns, or the deserializer can be allowed to synchronize to random data. By using the synchronization mode, the deserializer establishes lock within specified, shorter time parameters.

The device can be entered into a power-down state when no data transfer is required. Alternatively, a mode is available to place the output pins in the high-impedance state without losing PLL lock.

The SN65LV1023 and SN65LV1224 are characterized for operation over ambient air temperature of -40°C to 85°C.

| DEVICE       | PART NUMBER <sup>(1)</sup> |

|--------------|----------------------------|

| Serializer   | SN65LV1023DB               |

| Deserializer | SN65LV1224DB               |

### **ORDERING INFORMATION**

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

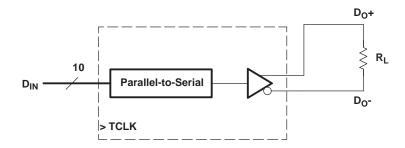

**BLOCK DIAGRAMS**

### FUNCTIONAL DESCRIPTION

The SN65LV1023 and SN65LV1224 are a 10-bit serializer/deserializer chipset designed to transmit data over differential backplanes or unshielded twisted pair (UTP) at clock speeds from 30 MHz to 66 MHz. The chipset has five states of operation: initialization mode, synchronization mode, data transmission mode, power-down mode, and high-impedance mode. The following sections describe each state of operation.

### INITIALIZATION MODE

Initialization of both devices must occur before data transmission can commence. Initialization refers to synchronization of the serializer and deserializer PLLs to local clocks.

When  $V_{CC}$  is applied to the serializer and/or deserializer, the respective outputs enter the high-impedance state, while on-chip power-on circuitry disables internal circuitry. When  $V_{CC}$  reaches 2.45 V, the PLL in each device begins locking to a local clock. For the serializer, the local clock is the transmit clock (TCLK) provided by an external source. For the deserializer, a local clock must be applied to the REFCLK pin. The serializer outputs remain in the high-impedance state, while the PLL locks to the TCLK.

### SYNCHRONIZATION MODE

The deserializer PLL must synchronize to the serializer in order to receive valid data. Synchronization can be accomplished in one of two ways:

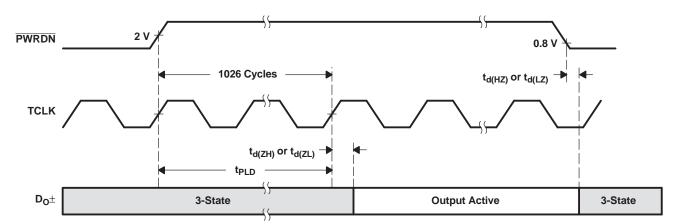

Rapid Synchronization: The serializer has the capability to send specific SYNC patterns consisting of six

ones and six zeros switching at the input clock rate. The transmission of SYNC patterns enables the

deserializer to lock to the serializer signal within a deterministic time frame. This transmission of SYNC

patterns is selected via the SYNC1 and SYNC2 inputs on the serializer. Upon receiving valid SYNC1 or

SYNC2 pulse (wider than 6 clock cycles), 1026 cycles of SYNC pattern are sent.

When the deserializer detects edge transitions at the LVDS input, it attempts to lock to the embedded clock information. The deserializer LOCK output remains high while its PLL locks to the incoming data or SYNC patterns present on the serial input. When the deserializer locks to the LVDS data, the LOCK output goes low. When LOCK is low, the deserializer outputs represent incoming LVDS data. One approach is to tie the deserializer LOCK output directly to SYNC1 or SYNC2.

• Random-Lock Synchronization: The deserializer can attain lock to a data stream without requiring the serializer to send special SYNC patterns. This allows the SN65LV1224 to operate in open-loop applications. Equally important is the deserializer's ability to support hot insertion into a running backplane. In the open-loop or hot-insertion case, it is assumed the data stream is essentially random. Therefore, because lock time varies due to data stream characteristics, the exact lock time cannot be predicted. The primary constraint on the random lock time is the initial phase relation between the incoming data and the REFCLK when the deserializer powers up.

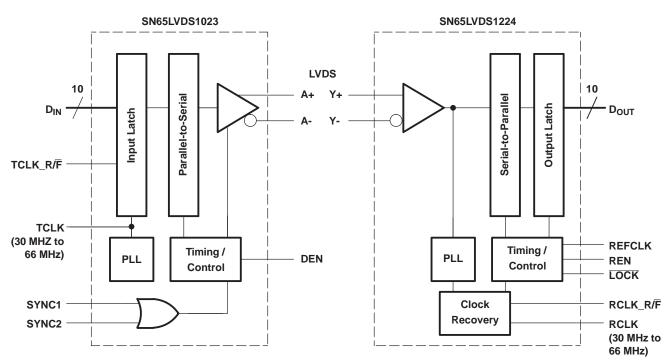

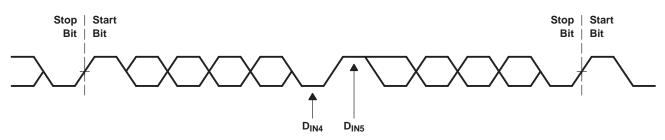

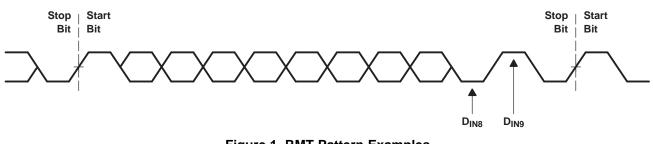

The data contained in the data stream can also affect lock time. If a specific pattern is repetitive, the deserializer could enter false lock—falsely recognizing the data pattern as the start/stop bits. This is referred to as repetitive multitransition (RMT);see Figure 1 for RMT examples. This occurs when more than one low-high transition takes place per clock cycle over multiple cycles. In the worst case, the deserializer could become locked to the data pattern rather than the clock. Circuitry within the deserializer can detect that the possibility of false lock exists. Upon detection, the circuitry prevents the LOCK output from becoming active until the potential false lock pattern changes. Notice that the RMT pattern only affects the deserializer lock time, and once the deserializer is in lock, the RMT pattern does not affect the deserializer state as long as the same data boundary happens each cycle. The deserializer does not go into lock until it finds a unique four consecutive cycles of data boundary (stop/start bits) at the same position.

The deserializer stays in lock until it cannot detect the same data boundary (stop/start bits) for four consecutive cycles. Then the desiralizer goes out of lock and hunts for the new data boundary (stop/start bits). In the event of loss of synchronization, the  $\overline{LOCK}$  pin output goes high and the outputs (including RCLK) enter a high-impedance state. The user's system should monitor the  $\overline{LOCK}$  pin in order to detect a loss of synchronization. Upon detection of lock, sending sync patterns for resynchronization is desirable if reestablishing lock within a specific time is critical. However, the deserializer can lock to random data as previously noted.

D<sub>IN0</sub> Held Low and D<sub>IN1</sub> Held High

DIN4 Held Low and DIN5 Held High

DIN8 Held Low and DIN9 Held High

### DATA TRANSMISSION MODE

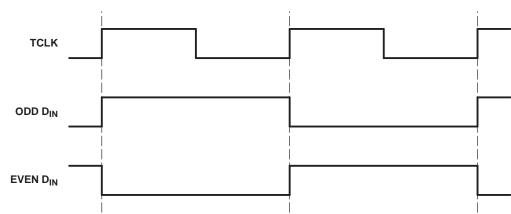

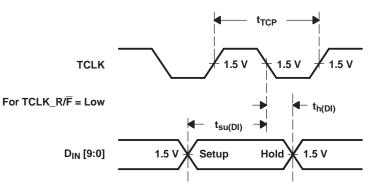

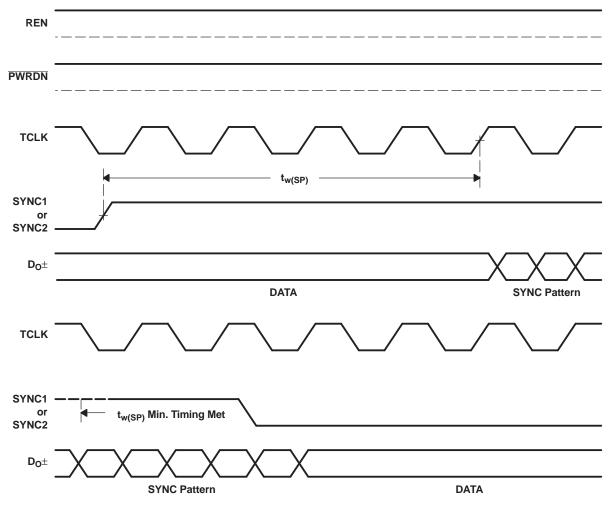

After initialization and synchronization, the serializer accepts parallel data from inputs  $D_{IN0}$ - $D_{IN9}$ . The serializer uses the TCLK input to latch the incoming data. The TCLK\_R/F pin selects which edge the serializer uses to strobe incoming data. If either of the SYNC inputs is high for 6 TCLK cycles, the data at  $D_{IN0}$ - $D_{IN9}$  is ignored regardless of the clock edge selected and 1026 cycles of SYNC pattern are sent.

After determining which clock edge to use, a start and stop bit, appended internally, frames the data bits in the register. The start bit is always high and the stop bit is always low. The start and stop bits function as the embedded clock bits in the serial stream.

The serializer transmits serialized data and appended clock bits (10+2 bits) from the serial data output (DO±) at 12 times the TCLK frequency. For example, if TCLK is 66 MHz, the serial rate is  $66 \times 12 = 792$  Mbps. Because only 10 bits are input data, the useful data rate is 10 times the TCLK frequency. For instance, if TCLK = 66 MHz, the useful data rate is  $66 \times 10 = 660$  Mbps. The data source, which provides TCLK, must be in the range of 30 MHz to 66 MHz.

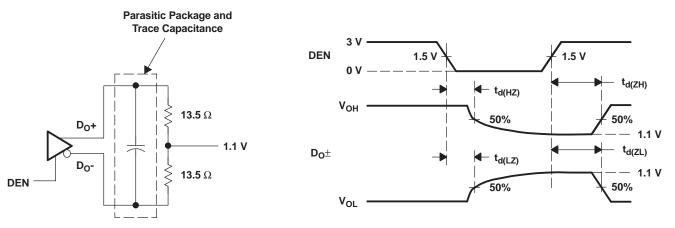

The serializer outputs  $(DO\pm)$  can drive point-to-point connections or limited multipoint or multidrop backplanes. The outputs transmit data when the enable pin (DEN) is high, PWRDN = high, and SYNC1 and SYNC2 are low. When DEN is driven low, the serializer output pins enter the high-impedance state. Once the deserializer has synchronized to the serializer, the  $\overline{LOCK}$  pin transitions low. The deserializer locks to the embedded clock and uses it to recover the serialized data.  $R_{OUT}$  data is valid when  $\overline{LOCK}$  is low, otherwise  $R_{OUT0}$ - $R_{OUT0}$ -R

### POWER DOWN

When no data transfer is required, the power-down mode can be used. The serializer and deserializer use the power-down state, a low-power sleep mode, to reduce power consumption. The deserializer enters power down when you drive PWRDN and REN low. The serializer enters power down when you drive PWRDN low. In power down, the PLL stops and the outputs enter a high-impedance state, which disables load current and reduces supply current to the milliampere range. To exit power down, you must drive the PWRDN pin high.

Before valid data exchanges between the serializer and deserializer can resume, you must reinitialize and resynchronize the devices to each other. Initialization of the serializer takes 1026 TCLK cycles. The deserializer initialize and drives LOCK high until lock to the LVDS clock occurs.

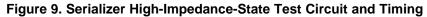

### HIGH-IMPEDANCE MODE

The serializer enters the high-impedance mode when the DEN pin is driven low. This puts both driver output pins (DO+ and DO-) into a high-impedance state. When you drive DEN high, the serializer returns to the previous state, as long as all other control pins remain static (SYNC1, SYNC2, PWRDN, TCLK\_R/F). When the REN pin is driven low, the deserializer enters high-impedance mode. Consequently, the receiver output pins ( $R_{OUT0}$ - $R_{OUT9}$ ) and RCLK are placed into the high-impedance state. The LOCK output remains active, reflecting the state of the PLL.

| INPUT | S   |                                                  | OUTPUTS |                                   |  |                     |  |

|-------|-----|--------------------------------------------------|---------|-----------------------------------|--|---------------------|--|

| PWRDN | REN | REN ROUT[0:9] <sup>(1)</sup> LOCK <sup>(2)</sup> |         | REN ROUT[0:9] <sup>(1)</sup> LOCK |  | RCLK <sup>(3)</sup> |  |

| Н     | Н   | Z                                                | Н       | Z                                 |  |                     |  |

| Н     | Н   | Active                                           | L       | Active                            |  |                     |  |

| L     | Х   | Z                                                | Z       | Z                                 |  |                     |  |

| Н     | L   | Z                                                | Active  | Z                                 |  |                     |  |

#### **Deserializer Truth Table**

(1) RCLK active indicates the RCLK is running if the deserializer is locked. The timing of RCLK with respect to ROUT is determined by RCLK\_R/F.

(2) LOCK output reflects the state of the deserializer with regard to the selected data stream.

(3) ROUT and RCLK are 3-stated when LOCK is asserted high.

## **Terminal Functions**

| PIN               | NAME                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERIALIZER        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18, 20, 23,<br>25 | AGND                                 | Analog circuit ground (PLL and analog circuits)                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17, 26            | AV <sub>CC</sub>                     | Analog circuit power supply (PLL and analog circuits)                                                                                                                                                                                                                                                                                                                                                                                           |

| 19                | DEN                                  | LVTTL logic input. Low puts the LVDS serial output into the high-impedance state. High enables serial data output.                                                                                                                                                                                                                                                                                                                              |

| 15, 16            | DGND                                 | Digital circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3-12              | $D_{IN0} - D_{IN9}$                  | Parallel LVTTL data inputs                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21                | D <sub>O</sub> -                     | Inverting LVDS differential output                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22                | D <sub>O</sub> +                     | Noninverting LVDS differential output                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27, 28            | DV <sub>CC</sub>                     | Digital circuit power supply                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24                | PWRDN                                | LVTTL logic input. Asserting this pin low turns off the PLL and places the outputs into the high-impedance state, putting the device into a low-power mode.                                                                                                                                                                                                                                                                                     |

| 1, 2              | SYNC1,<br>SYNC2                      | LVTTL logic inputs SYNC1 and SYNC2 are ORed together. When at least one of the two pins is asserted high for 6 cycles of TCLK, the serializer initiates transmission of a minimum 1026 SYNC patterns. If after completion of the transmission of 1026 patterns SYNC continues to be asserted, then the transmission continues until SYNC is driven low and if the time SYNC holds > 6 cycles, another 1026 SYNC pattern transmission initiates. |

| 13                | TCLK_R/F                             | LVTTL logic input. Low selects a TCLK falling-edge data strobe; high selects a TCLK rising-edge data strobe.                                                                                                                                                                                                                                                                                                                                    |

| 14                | TCLK                                 | LVTTL-level reference clock input. The SN65LV1023 accepts a 30-MHz to 66-MHz clock. TCLK strobes parallel data into the input latch and provides a reference frequency to the PLL.                                                                                                                                                                                                                                                              |

| DESERIALIZI       | ER                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1, 12, 13         | AGND                                 | Analog circuit ground (PLL and analog circuits)                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4, 11             | AV <sub>CC</sub>                     | Analog circuit power supply (PLL and analog circuits)                                                                                                                                                                                                                                                                                                                                                                                           |

| 14, 20, 22        | DGND                                 | Digital circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21, 23            | DV <sub>CC</sub>                     | Digital circuit power supply                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10                | LOCK                                 | LVTTL level output. LOCK goes low when the deserializer PLL locks onto the embedded clock edge.                                                                                                                                                                                                                                                                                                                                                 |

| 7                 | PWRDN                                | LVTTL logic input. Asserting this pin low turns off the PLL and places outputs into a high-impedance state, putting the device into a low-power mode.                                                                                                                                                                                                                                                                                           |

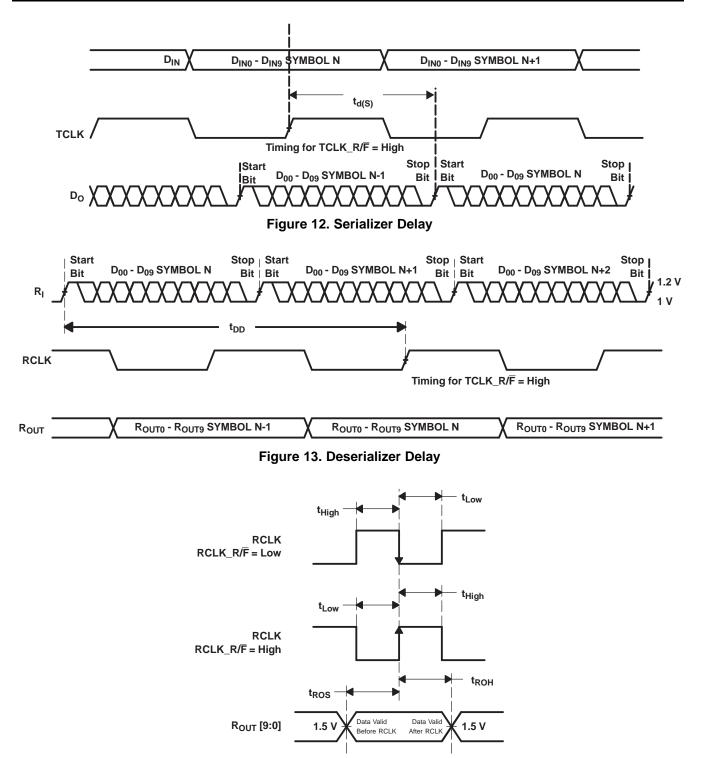

| 2                 | RCLK_R/F                             | LVTTL logic input. Low selects an RCLK falling-edge data strobe; high selects an RCLK rising-edge data strobe.                                                                                                                                                                                                                                                                                                                                  |

| 9                 | RCLK                                 | LVTTL level output recovered clock. Use RCLK to strobe R <sub>OUTx</sub> .                                                                                                                                                                                                                                                                                                                                                                      |

| 3                 | REFCLK                               | LVTTL logic input. Use this pin to supply a REFCLK signal for the internal PLL frequency.                                                                                                                                                                                                                                                                                                                                                       |

| 8                 | REN                                  | LVTTL logic input. Low places R <sub>OUT0</sub> -R <sub>OUT9</sub> and RCLK in the high-impedance state.                                                                                                                                                                                                                                                                                                                                        |

| 5                 | R <sub>I</sub> +                     | Serial data input. Noninverting LVDS differential input                                                                                                                                                                                                                                                                                                                                                                                         |

| 6                 | R <sub>I</sub> -                     | Serial data input. Inverting LVDS differential input                                                                                                                                                                                                                                                                                                                                                                                            |

| 15-19, 24-28      | R <sub>OUT0</sub> -R <sub>OUT9</sub> | Parallel LVTTL data outputs                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                        |                | UNIT                                |

|--------------------------------------------------------|----------------|-------------------------------------|

| V <sub>CC</sub> to GND                                 |                | –0.3 V to 4 V                       |

| LVTTL input voltage                                    |                | -0.3 V to (V <sub>CC</sub> + 0.3 V) |

| LVTTL output voltage                                   |                | -0.3 V to (V <sub>CC</sub> + 0.3 V) |

| LVDS receiver input volta                              | ge             | –0.3 V to 3.9 V                     |

| LVDS driver output voltag                              | e              | –0.3 V to 3.9 V                     |

| LVDS output short circuit                              | duration       | 10 ms                               |

| Electrostatia diaskanas                                | НВМ            | Up to 6 kV                          |

| Electrostatic discharge                                | MM             | Up to 200 V                         |

| Junction temperature                                   |                | 150°C                               |

| Storage temperature                                    |                | –65°C to 150°C                      |

| Lead temperature (solder                               | ng, 4 seconds) | 260°C                               |

| Maximum package power dissipation, $T_A = 25^{\circ}C$ |                | 1.27 W                              |

| Package derating                                       |                | 10.3 mW/°C above 25°C               |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

|                                |                                  | MIN                | NOM | MAX                                   | UNIT             |

|--------------------------------|----------------------------------|--------------------|-----|---------------------------------------|------------------|

| V <sub>CC</sub> <sup>(1)</sup> | Supply voltage                   | 3                  | 3.3 | 3.6                                   | V                |

|                                | Receiver input voltage range     | 0                  |     | 2.4                                   | V                |

| V <sub>CM</sub>                | Receiver input common mode range | $\frac{V_{ID}}{2}$ |     | $2.4 - \left(\frac{V_{ID}}{2}\right)$ | V                |

|                                | Supply noise voltage             |                    |     | 100                                   | mV <sub>PP</sub> |

| T <sub>A</sub>                 | Operating free-air temperature   | -40                | 25  | 85                                    | °C               |

(1) By design, DVCC and AVCC are separated internally and does not matter what the difference is for |DVCC-AVCC|, as long as both are within 3 V to 3.6 V.

## **ELECTRICAL CHARACTERISTICS**

over recommended operating supply and temperature ranges (unless otherwise noted)

|                 | PARAMETER                                                 | TEST CONDITIONS                | MIN  | ТҮР   | MAX             | UNIT |

|-----------------|-----------------------------------------------------------|--------------------------------|------|-------|-----------------|------|

| SERI            | ALIZER LVCMOS/LVTTL DC SPECIFICA                          | TIONS <sup>(1)</sup>           | L.   |       |                 |      |

| V <sub>IH</sub> | High-level input voltage                                  |                                | 2    |       | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Low-level input voltage                                   |                                | GND  |       | 0.8             | V    |

| $V_{CL}$        | Input clamp voltage                                       | I <sub>CL</sub> = -18 mA       |      | -0.86 | -1.5            | V    |

| I <sub>IN</sub> | Input current <sup>(2)</sup>                              | V <sub>IN</sub> = 0 V or 3.6 V | -200 | ±100  | 200             | μA   |

| DESE            | ERIALIZER LVCMOS/LVTTL DC SPECIFI                         | CATIONS <sup>(3)</sup>         |      |       |                 |      |

| V <sub>IH</sub> | High-level input voltage                                  |                                | 2    |       | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Low-level input voltage                                   |                                | GND  |       | 0.8             | V    |

| $V_{CL}$        | Input clamp voltage                                       | I <sub>CL</sub> = -18 mA       |      | -0.62 | -1.5            | V    |

| I <sub>IN</sub> | Input current (pull-up and pull-down resistors on inputs) | V <sub>IN</sub> = 0 V or 3.6 V | -200 |       | 200             | μA   |

| V <sub>OH</sub> | High-level output voltage                                 | I <sub>OH</sub> = -5 mA        | 2.2  | 3     | V <sub>CC</sub> | V    |

| V <sub>OL</sub> | Low-level output voltage                                  | I <sub>OL</sub> = 5 mA         | GND  | 0.25  | 0.5             | V    |

Apply to DINO-DINO, TCLK, PWRDN, TCLK\_R/F, SYNC1, SYNC2, DEN (1)

(2)

High I<sub>IN</sub> values are due to pull-up and pull-down resistors on the inputs. Apply to pins <u>PWRDN</u>, RCLK\_R/F, REN, REFCLK = inputs; apply to pins R<sub>OUTx</sub>, RCLK, <u>LOCK</u> = outputs (3)

## **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating supply and temperature ranges (unless otherwise noted)

|                   | PARAMETER                               | TEST CONDIT                                                      | IONS                                            | MIN | TYP   | MAX     | UNIT |

|-------------------|-----------------------------------------|------------------------------------------------------------------|-------------------------------------------------|-----|-------|---------|------|

| l <sub>os</sub>   | Output short-circuit current            | V <sub>OUT</sub> = 0 V                                           | V <sub>OUT</sub> = 0 V                          |     |       | -85     | mA   |

| I <sub>oz</sub>   | High-impedance output current           | <b>PWRDN</b> or REN = 0.8 V, $V_{OU}$                            | $T = 0 V \text{ or } V_{CC}$                    | -10 | ±1    | 10      | μA   |

| SERIA             | ALIZER LVDS DC SPECIFICATIONS (Appl     | y to pins DO+ and DO-)                                           |                                                 |     |       |         |      |

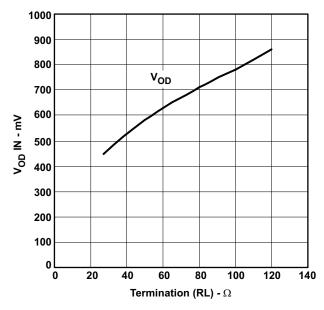

| V <sub>OD</sub>   | Output differential voltage (DO+)-(DO-) | $R_L = 27 \Omega$ , See Figure 2                                 |                                                 | 350 | 450   |         | mV   |

| $\Delta V_{OD}$   | Output differential voltage unbalance   |                                                                  |                                                 |     |       | 35      | mV   |

| Vos               | Offset voltage                          |                                                                  |                                                 | 1.1 | 1.2   | 1.3     | V    |

| $\Delta V_{OS}$   | Offset voltage unbalance                |                                                                  |                                                 |     | 4.8   | 35      | mV   |

| l <sub>os</sub>   | Output short circuit current            | $D0 = 0 V, D_{INx} = high, \overline{PWRDN}$                     | and DEN = 2.4 V                                 |     | -10   | -90     | mA   |

| l <sub>oz</sub>   | High-impedance output current           | PWRDN or DEN = 0.8 V, DO =                                       | = 0 V or V <sub>CC</sub>                        | -10 | ±1    | 10      | μA   |

| I <sub>OX</sub>   | Power-off output current                | $V_{CC} = 0 V, DO = 0 V \text{ or } 3.6 V$                       |                                                 | -20 | ±1    | 25      | μA   |

| Co                | Output single-ended capacitance         |                                                                  |                                                 |     |       | 1±20%   | pF   |

| DESE              | RIALIZER LVDS DC SPECIFICATIONS (A      | oply to pins RI+ and RI-)                                        |                                                 |     |       |         |      |

| V <sub>TH</sub>   | Differential threshold high voltage     | V <sub>CM</sub> = 1.1 V                                          |                                                 |     |       | 50      | mV   |

| V <sub>TL</sub>   | Differential threshold low voltage      |                                                                  |                                                 | -50 |       |         | mV   |

|                   | loout ourroot                           | $V_{IN} = 2.4 \text{ V}, V_{CC} = 3.6 \text{ V or } 0 \text{ V}$ | /                                               | -10 | ±1    | 15      | ^    |

| I <sub>IN</sub>   | Input current                           | $V_{IN} = 0 \text{ V}, V_{CC} = 3.6 \text{ V or } 0 \text{ V}$   |                                                 | -10 | ±0.05 | 10      | μA   |

| CI                | Input single-ended capacitance          |                                                                  |                                                 |     |       | 0.5±20% | pF   |

| SERI/             | LIZER SUPPLY CURRENT (Applies to pi     | ns DVCC and AVCC)                                                |                                                 |     |       |         |      |

|                   | Carializar auguly autrent warst appa    |                                                                  | f = 30 MHz                                      |     | 30    | 45      |      |

| ICCD              | Serializer supply current worst case    | $R_L = 27 \Omega$ , See Figure 3                                 | f = 66 MHz                                      |     | 55    | 70      | mA   |

| I <sub>CCXD</sub> | Serializer supply current               | <u>PWRDN</u> = 0.8 V                                             |                                                 |     | 200   | 500     | μA   |

| DESE              | RIALIZER SUPPLY CURRENT (Applies to     | pins DVCC and AVCC)                                              |                                                 |     |       | Ļ       |      |

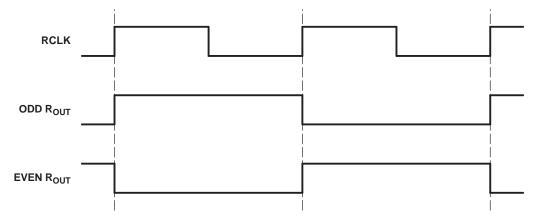

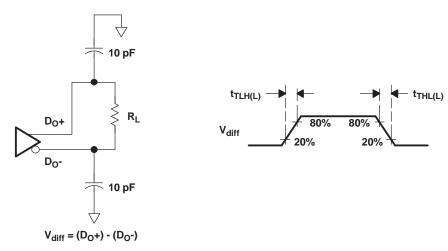

|                   |                                         |                                                                  | f = 30 MHz                                      |     | 40    | 50      |      |

| I <sub>CCR</sub>  | Deserializer supply current, worst case | $o_L = 15 \text{ pr}, \text{ See Figure 4}$                      | $C_L = 15 \text{ pF}$ , See Figure 4 f = 66 MHz |     | 80    | 95      | mA   |

| I <sub>CCXR</sub> | Deserializer supply current, power down | PWRDN = 0.8 V, REN = 0.8 V                                       | ,                                               |     | 0.36  | 1       | mA   |

Figure 2. Typical  $V_{OD}$  Curve

## SERIALIZER TIMING REQUIREMENTS

for TCLK over recommended operating supply and temperature ranges (unless otherwise specified)

|                     | PARAMETER                  | TEST CONDITIONS | MIN   | TYP  | MAX   | UNIT    |

|---------------------|----------------------------|-----------------|-------|------|-------|---------|

| t <sub>TCP</sub>    | Transmit clock period      |                 | 15.15 | Т    | 33.33 | ns      |

| t <sub>TCIH</sub>   | Transmit clock high time   |                 | 0.4T  | 0.5T | 0.6T  | ns      |

| t <sub>TCIL</sub>   | Transmit clock low time    |                 | 0.4T  | 0.5T | 0.6T  | ns      |

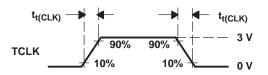

| t <sub>t(CLK)</sub> | TCLK input transition time |                 |       | 3    | 6     | ns      |

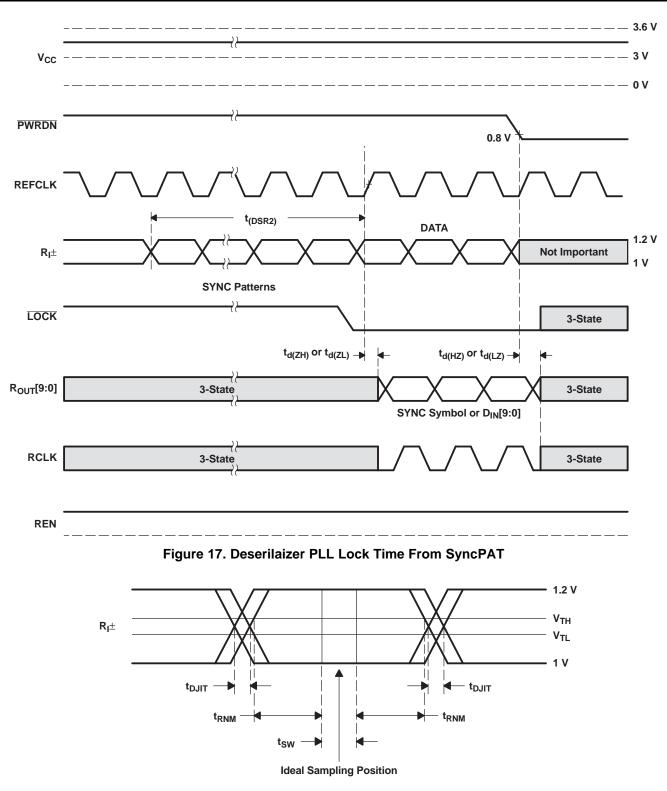

| t <sub>JIT</sub>    | TCLK input jitter          | See Figure 18   |       |      | 150   | ps (RMS |

### SERIALIZER SWITCHING CHARACTERISTICS

over recommended operating supply and temperature ranges (unless otherwise specified)

|                      | PARAM                                                | ETER                  | TEST CONDITIONS                                           | MIN                   | TYP  | MAX                       | UNIT     |

|----------------------|------------------------------------------------------|-----------------------|-----------------------------------------------------------|-----------------------|------|---------------------------|----------|

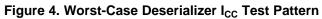

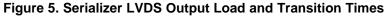

| t <sub>TLH(L)</sub>  | LVDS low-to-high transition time                     |                       | $R_1 = 27 \Omega$ , $C_1 = 10 pF$ to GND,                 |                       | 0.2  | 0.4                       | ns       |

| t <sub>LTHL(L)</sub> | LVDS high-to-lov                                     | v transition time     | See Figure 5                                              |                       | 0.25 | 0.4                       | ns       |

| t <sub>su(DI)</sub>  | D <sub>IN0</sub> –D <sub>IN9</sub> setup t           | to TCLK               | Soo Eiguro 8                                              | 0.5                   |      |                           | ns       |

| t <sub>su(DI)</sub>  | D <sub>IN0</sub> –D <sub>IN9</sub> hold fr           | om TCLK               | See Figure 8                                              | 4                     |      |                           | ns       |

| t <sub>d(HZ)</sub>   | DO± high-to-high-impedance-state delay               |                       |                                                           |                       | 2.5  | 5                         |          |

| t <sub>d(LZ)</sub>   | DO± low-to-high-                                     | impedance-state delay |                                                           |                       | 2.5  | 5                         |          |

| t <sub>d(ZH)</sub>   | DO±<br>high-to-high-impedance-state-to-high<br>delay |                       | $R_L = 27 \Omega$ , $C_L = 10 pF$ to GND,<br>See Figure 9 |                       | 5    | 10                        | ns       |

| t <sub>d(ZL)</sub>   | DO±<br>high-to-high-impe<br>delay                    | edance-state-to-low   |                                                           |                       | 6.5  | 10                        |          |

| t <sub>w(SPW)</sub>  | SYNC pulse dura                                      | ation                 |                                                           | 6×t <sub>TCP</sub>    |      |                           | ns       |

| t <sub>(PLD)</sub>   | Serializer PLL loo                                   | ck time               | See Figure 11                                             | 1026×t <sub>TCP</sub> |      |                           | ns       |

| t <sub>d(S)</sub>    | Serializer delay                                     |                       | See Figure 12                                             |                       |      | $\frac{t_{TCP}}{2} + 3.6$ | ns       |

|                      | Deterministic 30 MHz<br>jitter 66 MHz                |                       |                                                           |                       |      | 230                       |          |

| t <sub>DJIT</sub>    |                                                      |                       | $R_L = 27 \Omega$ , $C_L = 10 pF$ to GND                  |                       |      | 150                       | ps       |

| t <sub>RJIT</sub>    | Random jitter                                        |                       | $R_L = 27 \Omega$ , $C_L = 10 pF$ to GND                  |                       | 10   | 19                        | ps (RMS) |

### DESERIALIZER TIMING REQUIREMENTS

for REFCLK over recommended operating supply and temperature ranges (unless otherwise specified)

|                    | PARAMETER              | TEST CONDITIONS | MIN   | TYP | MAX   | UNIT |

|--------------------|------------------------|-----------------|-------|-----|-------|------|

| t <sub>RFCP</sub>  | REFCLK period          |                 | 15.15 | Т   | 33.33 | ns   |

| t <sub>RFDC</sub>  | REFCLK duty cycle      |                 | 30%   | 50% | 70%   |      |

| t <sub>t(RF)</sub> | REFCLK transition time |                 |       | 3   | 6     | ns   |

## DESERIALIZER SWITCHING CHARACTERISTICS

over recommended operating supply and temperature ranges (unless otherwise specified)

|                      | PARAMETER                                    | TEST CONDITIONS                                            | PIN/FREQ                               | MIN                    | ТҮР                   | MAX                         | UNIT |

|----------------------|----------------------------------------------|------------------------------------------------------------|----------------------------------------|------------------------|-----------------------|-----------------------------|------|

| t <sub>(RCP)</sub>   | Receiver out clockperiod                     | t <sub>(RCP)</sub> = t <sub>(TCP)</sub> ,<br>See Figure 12 | RCLK                                   | 15.15                  |                       | 33.33                       | ns   |

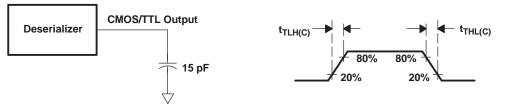

| t <sub>TLH(C)</sub>  | CMOS/TTL low-to-high transition time         | C <sub>L</sub> = 15 pF,                                    | R <sub>OUT0</sub> –R <sub>OUT9</sub> , |                        | 1.2                   | 2.5                         |      |

| t <sub>THL(C)</sub>  | CMOS/TTL high-to-low transition time         | See Figure 6                                               | LOCK, RCLK                             |                        | 1.1                   | 2.5                         | ns   |

|                      | Deserializer delay,                          | Room temperature, 3.3 V                                    | 30 MHz                                 | 2×t <sub>RCP</sub> + 7 |                       | 2.833×t <sub>RCP</sub> + 11 | ns   |

| t <sub>d(D)</sub>    | See Figure 13                                | Room temperature, 5.5 v                                    | 66 MHz                                 | $2 \times t_{RCP} + 4$ |                       | 2.833×t <sub>RCP</sub> + 7  | 115  |

|                      | D data valid bafara DCLK                     |                                                            | RCLK 30 MHz                            | 0.4×t <sub>RCP</sub>   | 0.5×t <sub>RCP</sub>  |                             |      |

| t <sub>(ROS)</sub>   | R <sub>OUTx</sub> data valid before RCLK     | See Figure 14                                              | RCLK 66 MHz                            | 0.4×t <sub>RCP</sub>   | 0.5×t <sub>RCP</sub>  |                             |      |

|                      |                                              | - See Figure 14                                            | 30 MHz                                 | -0.4×t <sub>RCP</sub>  | -0.5×t <sub>RCP</sub> |                             | ns   |

| t <sub>(ROH)</sub>   | R <sub>OUTx</sub> data valid after RCLK      |                                                            | 66 MHz                                 | -0.4×t <sub>RCP</sub>  | -0.5×t <sub>RCP</sub> |                             |      |

| t <sub>(RDC)</sub>   | RCLK duty cycle                              |                                                            |                                        | 40%                    | 50%                   | 60%                         |      |

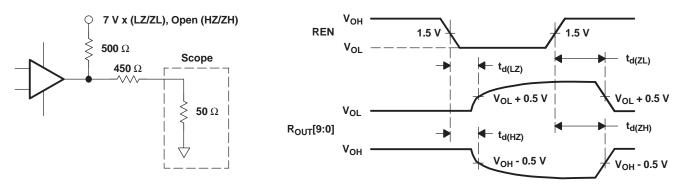

| t <sub>d(HZ)</sub>   | High-to-high-impedance state delay           |                                                            |                                        |                        | 6.5                   | 8                           | ns   |

| t <sub>d(LZ)</sub>   | Low-to-high-impedance state delay            | - See Figure 15                                            |                                        |                        | 4.7                   | 8                           | ns   |

| t <sub>d(HR)</sub>   | High-impedance state-to-high delay           |                                                            | R <sub>OUT0</sub> –R <sub>OUT9</sub>   |                        | 5.3                   | 8                           | ns   |

| t <sub>d(ZL)</sub>   | High-impedance-state-to-low delay            |                                                            |                                        |                        | 4.7                   | 8                           | ns   |

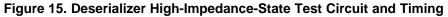

|                      | Deserializer PLL lock time from              |                                                            | 30 MHz                                 |                        |                       | (1024+26)t <sub>RFCP</sub>  |      |

| t <sub>(DSR1)</sub>  | PWRDN(with SYNCPAT)                          |                                                            | 66 MHz                                 |                        |                       | (1024+26)t <sub>RFCP</sub>  | 1    |

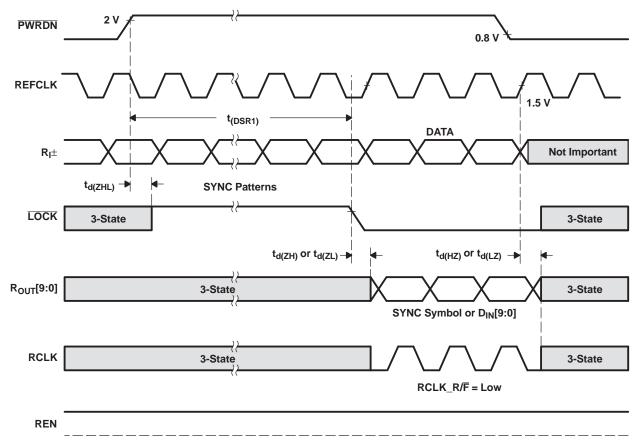

|                      | Deserializer PLL lock time from              | See Figure 16, Figure 17,                                  | 30 MHz                                 |                        |                       | 0.3                         | μs   |

| t <sub>(DSR2)</sub>  | SYNCPAT                                      | and Note (1)                                               | 66 MHz                                 |                        |                       | 0.2                         | 1    |

| t <sub>d(ZHLK)</sub> | High-impedance-state to-high delay(power up) |                                                            | LOCK                                   |                        |                       | 3                           | ns   |

|                      | Descriptizer seise merzie                    | Cap Figure 10 and Note (2)                                 | 30 MHz                                 |                        | 1380                  |                             |      |

| t <sub>RNM</sub>     | Deserializer noise margin                    | See Figure 18 and Note (2)                                 | 66 MHz                                 |                        | 540                   |                             | ps   |

(1) t<sub>(DSR1)</sub> represents the time required for the deserializer to register that a lock has occurred upon powerup or when leaving the powerdown mode.  $t_{(DSR2)}$  represents the time required to register that a lock has occurred for the powerd up and enabled deserializer when the input (RI±) conditions change from not receiving data to receiving synchronization patterns (SYNCPATs). In order to specify deserializer PLL performance t<sub>DSR1</sub> and t<sub>DSR2</sub> are specified with REFCLK active and stable and specific conditions of SYNCPATs.

(2) t<sub>RNM</sub> represents the phase noise or jitter that the deserializer can withstand in the incoming data stream before bit errors occur.

TEXAS INSTRUMENTS www.ti.com

SLLS527H-FEBRUARY 2002-REVISED FEBRUARY 2007

## TIMING DIAGRAMS AND TEST CIRCUITS

Figure 6. Deserializer CMOS/TTL Output Load and Transition Times

Figure 7. Serializer Input Clock Transition Time

Figure 8. Serializer Setup/Hold Times

SLLS527H-FEBRUARY 2002-REVISED FEBRUARY 2007

Ĵ.

INS

Texas

TRUMENTS www.ti.com

Figure 10. Serializer PLL Lock Time and PWRDN High-Impedance-State Delays

Figure 11. SYNC Timing Delays

SLLS527H-FEBRUARY 2002-REVISED FEBRUARY 2007

Figure 14. Deserializer Data Valid Out Times

SLLS527H-FEBRUARY 2002-REVISED FEBRUARY 2007

Figure 16. Deserializer PLL Lock Times and PWRDN 3-State Delays

#### SLLS527H-FEBRUARY 2002-REVISED FEBRUARY 2007

$t_{SW}$ : Setup and Hold Time (Internal Data Sampling Window)  $t_{DJIT}$ : Serializer Output Bit Position Jitter That Results From Jitter on TCLK  $t_{RNM}$ : Receiver Noise Margin Time

#### Figure 18. Receiver LVDS Input Skew Margin

$V_{OD}$  = (D<sub>0</sub>+) - (D<sub>0</sub>-) Differential Output Signal Is Shown as (D<sub>0</sub>+) - (D<sub>0</sub>-)

Figure 19. V<sub>OD</sub> Diagram

www.ti.com

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login)   |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-------------------------------|

| SN65LV1023DB     | NRND                  | SSOP         | DB                 | 28   | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Replaced by<br>SN65LV1023ADB  |

| SN65LV1023DBG4   | NRND                  | SSOP         | DB                 | 28   | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Samples Not Available         |

| SN65LV1224DB     | NRND                  | SSOP         | DB                 | 28   | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Replaced by<br>SN65LV1224BDB  |

| SN65LV1224DBG4   | NRND                  | SSOP         | DB                 | 28   | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Samples Not Available         |

| SN65LV1224DBR    | NRND                  | SSOP         | DB                 | 28   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Replaced by<br>SN65LV1224BDBR |

| SN65LV1224DBRG4  | NRND                  | SSOP         | DB                 | 28   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           | Samples Not Available         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND**: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

28-Aug-2010

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

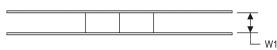

## TAPE AND REEL INFORMATION

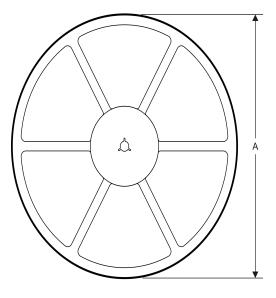

### REEL DIMENSIONS

Texas Instruments

#### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

TAPE AND REEL INFORMATION

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| SN65LV1224DBR               | SSOP            | DB                 | 28 | 2000 | 330.0                    | 16.4                     | 8.1        | 10.4       | 2.5        | 12.0       | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

14-Jul-2012

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65LV1224DBR | SSOP         | DB              | 28   | 2000 | 367.0       | 367.0      | 38.0        |

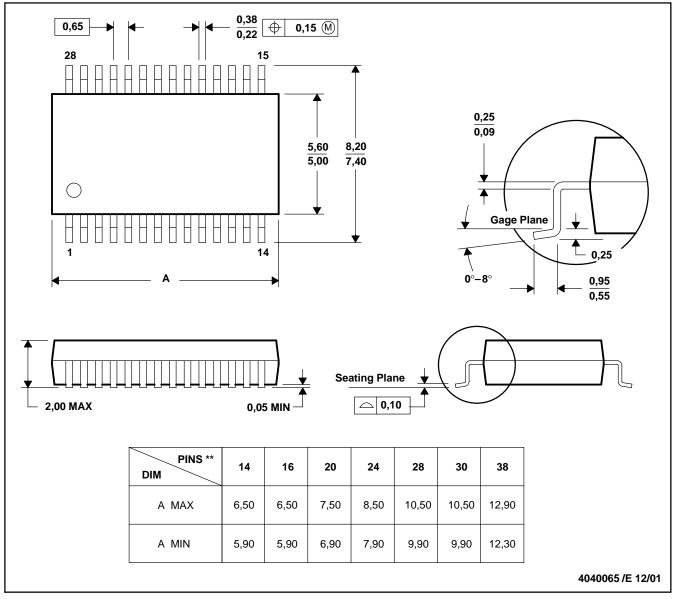

# **MECHANICAL DATA**

MSSO002E - JANUARY 1995 - REVISED DECEMBER 2001

## DB (R-PDSO-G\*\*)

PLASTIC SMALL-OUTLINE

28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-150

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated