# Broadband, Fully-Differential, 14-/16-Bit ADC Driver Amplifier

Check for Samples: THS770012

#### **FEATURES**

- 900MHz Bandwidth at Gain of +10dB

- 3300V/µs Slew Rate, V<sub>OUT</sub> = 2V step

- Adjustable Gain: +10dB to +13.7dB

- IMD<sub>3</sub>: -100dBc,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$ , f = 100MHz

- OIP3: 47dBm, f = 100MHz

- Noise Figure: 10.7 dB, f = 100MHz

# **APPLICATIONS**

- 14-/16-Bit ADC Driver

- ADC Driver for Wireless Base Station Signal Chains: GSM, WCDMA, MC-GSM, LTE

- ADC Driver for High Dynamic Range Test and Measurement Equipment

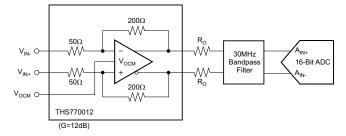

Figure 1. THS770012 Driving 16-Bit ADC

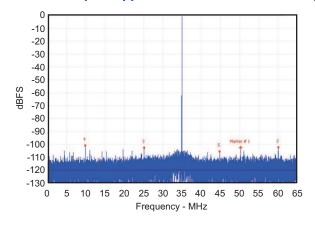

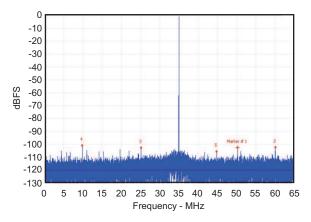

Figure 2. FFT Plot with Two-Tone Input at 96MHz and 100MHz (see *Application Information* section)

#### DESCRIPTION

The THS770012 is a wideband, fully-differential amplifier, with adjustable gain range from +10dB to +13.7dB (with external components). It is designed optimized specifically for driving analog-to-digital converters (ADCs) at input frequencies up to 130MHz, and 14-bit ADCs at input frequencies up to 200MHz. This device provides high bandwidth, high-voltage output with low distortion and low noise, critical in high-speed data acquisition systems that require very high dynamic range, such as wireless base stations and test and measurement applications. This device also makes an excellent differential amplifier for general-purpose, high-speed differential signal chain and short line driver applications.

The THS770012 operates on a nominal +5V single supply, offers very fast, 7.5ns maximum recovery time from overdrive conditions, and has a power-down mode for power saving. The THS770012 is offered in a Pb-free (RoHS compliant) and green, QFN-24 thermally-enhanced package. It is characterized for operation over the industrial temperature range of -40°C to +85°C.

#### **RELATED DEVICES**

| DEVICE                | DESCRIPTION                                                                                    |

|-----------------------|------------------------------------------------------------------------------------------------|

| THS770006             | Fixed Gain of +6dB, wideband, low-noise, low-distortion, fully-differential amplifier          |

| THS4509               | Wideband, low-noise, low-distortion, fully-differential amplifier                              |

| PGA870                | Wideband, low-noise, low-distortion, fully-differential, digitally-programmable gain amplifier |

| ADS5481 to<br>ADS5485 | 16-bit, 80MSPS to 200MSPS ADCs                                                                 |

| ADS6145               | 14-bit, 125MSPS ADC                                                                            |

| ADS6149               | 14-bit, 250MSPS ADC                                                                            |

Plea Insti

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

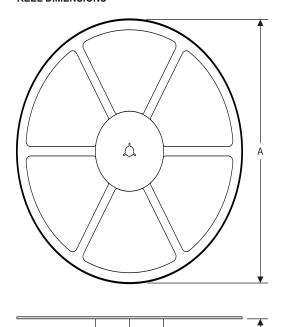

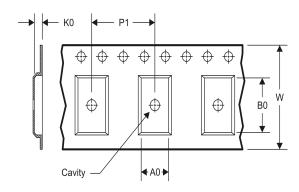

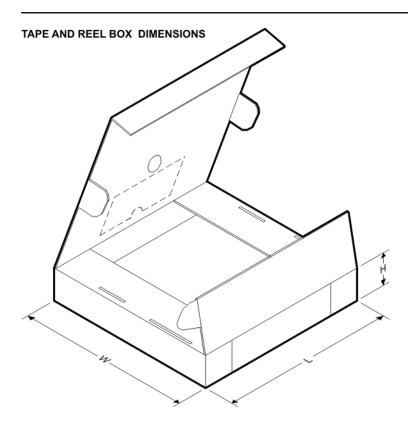

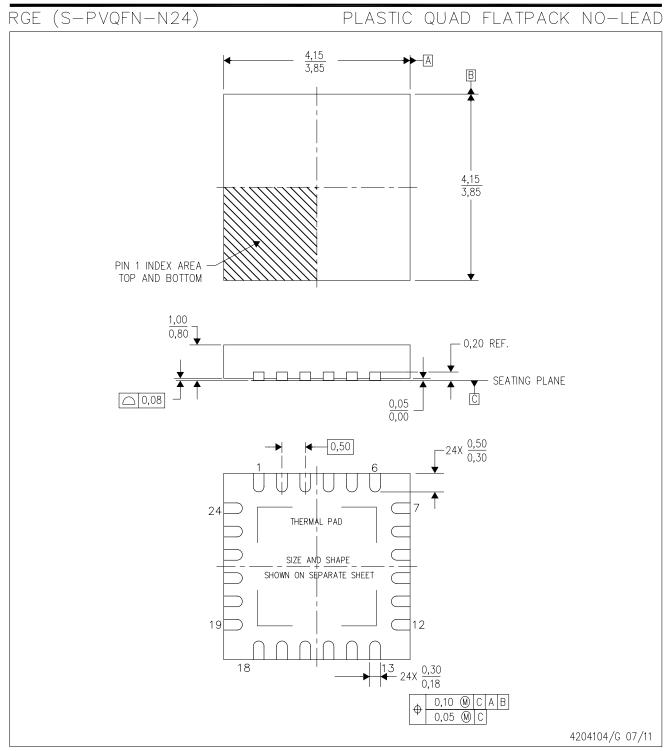

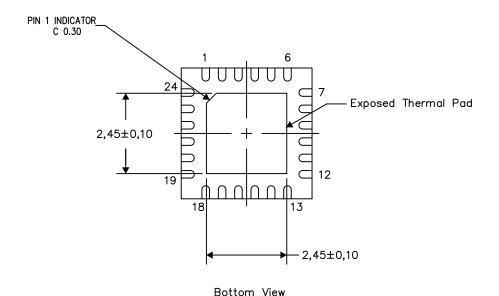

# PACKAGE/ORDERING INFORMATION(1)

| PRODUCT   | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|-----------|-----------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| THS770012 | VQFN-24         | RGE                   | 40°C to 195°C                     | THS770012IRGE      | THS770012IRGET     | Tape and reel, 250           |

| 105//0012 | VQFN-24         | RGE                   | –40°C to +85°C                    | THS770012IRGE      | THS770012IRGER     | Tape and reel, 3000          |

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder on www.ti.com.

# Figure 3. DEVICE MARKING INFORMATION

| $\circ$ |         |

|---------|---------|

|         | THS7700 |

|         | 12IRGE  |

|         | TIYMS   |

|         | LLLL    |

|         |         |

|         |         |

○ = Pin 1 designator

THS7700012IRGE = device name

TI = TI LETTERS

YM = YEAR MONTH DATE CODE

S = ASSEMBLY SITE CODE

LLLL = ASSY LOT CODE

# **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                                              |                                                              | THS770012                 | UNIT |

|----------------------------------------------|--------------------------------------------------------------|---------------------------|------|

| Power supply (V <sub>S+</sub> to GND)        |                                                              | 5.5                       | V    |

| Input voltage ra                             | ange                                                         | Ground to V <sub>S+</sub> | V    |

| Differential inpu                            | ut voltage, V <sub>ID</sub>                                  | Ground to V <sub>S+</sub> | V    |

| Continuous inp                               | ut current, I <sub>I</sub>                                   | 10                        | mA   |

| Continuous output current, I <sub>O</sub>    |                                                              | 100                       | mA   |

| Storage temperature range, T <sub>stg</sub>  |                                                              | −65°C to +150°C           | °C   |

| Maximum junction temperature, T <sub>J</sub> |                                                              | +150                      | °C   |

| Maximum junct                                | ion temperature, continuous operation, long term reliability | +125                      | °C   |

|                                              | Human body model (HBM)                                       | 2500                      | V    |

| ESD ratings                                  | Charged device model (CDM)                                   | 1000                      | V    |

|                                              | Machine model (MM)                                           | 100                       | V    |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

### THERMAL INFORMATION

|                       | THERMAL METRIC <sup>(1)</sup>                |               | LIMITO |

|-----------------------|----------------------------------------------|---------------|--------|

|                       | THERMAL METRIC                               | RGE (24) PINS | UNITS  |

| $\theta_{JA}$         | Junction-to-ambient thermal resistance       | 44.1          |        |

| $\theta_{JC(top)}$    | Junction-to-case(top) thermal resistance     | 35            |        |

| $\theta_{JB}$         | Junction-to-board thermal resistance         | 19            | °C/W   |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.5           | C/VV   |

| ΨЈВ                   | Junction-to-board characterization parameter | 18.8          |        |

| $\theta_{JC(bottom)}$ | Junction-to-case(bottom) thermal resistance  | 8.9           |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# **ELECTRICAL CHARACTERISTICS**

Test conditions are at  $T_A = +25$ °C,  $V_{S+} = +5V$ ,  $V_{OCM} = +2.5V$ ,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$  differential, G = +12dB, differential input and output, and input and output referenced to midsupply, unless otherwise noted. Measured using evaluation module as discussed in *Test Circuits* section.

| PARAMETER                                                               | TEST CONDITIONS                                      | MIN | TYP  | MAX | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------------------------------------|------------------------------------------------------|-----|------|-----|------|------------------------------|

| AC PERFORMANCE                                                          |                                                      | 11  |      |     |      |                              |

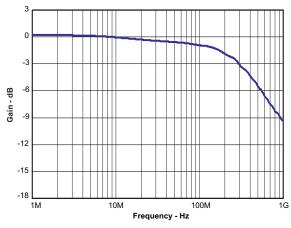

|                                                                         | Gain = +10dB, V <sub>OUT</sub> = 200mV <sub>PP</sub> |     | 900  |     | MHz  | С                            |

| Concil aignal handwidth                                                 | Gain = +11dB, V <sub>OUT</sub> = 200mV <sub>PP</sub> |     | 810  |     | MHz  | С                            |

| Small-signal bandwidth                                                  | Gain = +12dB, V <sub>OUT</sub> = 200mV <sub>PP</sub> |     | 680  |     | MHz  | С                            |

|                                                                         | $Gain = +13.7dB, V_{OUT} = 200mV_{PP}$               |     | 540  |     | MHz  | С                            |

|                                                                         | Gain = +10dB, V <sub>OUT</sub> = 2V <sub>PP</sub>    |     | 845  |     | MHz  | С                            |

| Large signal bandwidth                                                  | Gain = +11dB, V <sub>OUT</sub> = 2V <sub>PP</sub>    |     | 790  |     | MHz  | С                            |

| Large-signal bandwidth                                                  | Gain = +12dB, V <sub>OUT</sub> = 2V <sub>PP</sub>    |     | 680  |     | MHz  | С                            |

|                                                                         | Gain = +13.7dB, V <sub>OUT</sub> = 2V <sub>PP</sub>  |     | 548  |     | MHz  | С                            |

| Bandwidth for 0.1dB flatness                                            | Gain = +12dB, V <sub>OUT</sub> = 2V <sub>PP</sub>    |     | 130  |     | MHz  | С                            |

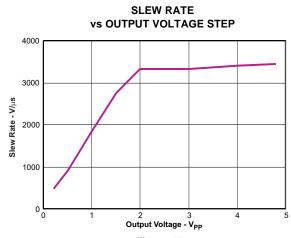

| Claus rate                                                              | V <sub>OUT</sub> = 2V step                           |     | 3300 |     | V/µs | С                            |

| Slew rate                                                               | V <sub>OUT</sub> = 4V step                           |     | 3400 |     | V/µs | С                            |

| Rise time                                                               | V <sub>OUT</sub> = 2V step                           |     | 0.6  |     | ns   | С                            |

| Fall time                                                               | V <sub>OUT</sub> = 2V step                           |     | 0.6  |     | ns   | С                            |

| Settling time to 0.1%                                                   | V <sub>OUT</sub> = 2V step                           |     | 2.2  |     | ns   | С                            |

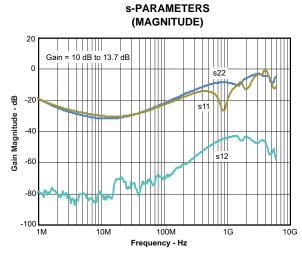

| Input return loss, s11                                                  | See s-Parameters section, f < 200MHz                 |     | -18  |     | dB   | С                            |

| Output return loss, s22                                                 | See s-Parameterssection, f < 200MHz                  |     | -16  |     | dB   | С                            |

| Reverse isolation, s12                                                  | See s-Parameters section, f < 200MHz                 |     | -60  |     | dB   | С                            |

|                                                                         | f = 10MHz                                            |     | -90  |     | dBc  | С                            |

| Second-order harmonic                                                   | f = 50MHz                                            |     | -70  |     | dBc  | С                            |

| distortion, Gain = +12dB, $R_L$ = 400 $\Omega$ , $V_{OUT}$ = 2 $V_{PP}$ | f = 100MHz                                           |     | -73  |     | dBc  | С                            |

|                                                                         | f = 200MHz                                           |     | -74  |     | dBc  | С                            |

|                                                                         | f = 10MHz                                            |     | -100 |     | dBc  | С                            |

| Third-order harmonic distortion,                                        | f = 50MHz                                            |     | -85  |     | dBc  | С                            |

| Gain = +12dB, $R_L = 400\Omega$ , $V_{OUT} = 2V_{PP}$                   | f = 100MHz                                           |     | -84  |     | dBc  | С                            |

| • •                                                                     | f = 200MHz                                           |     | -73  |     | dBc  | С                            |

|                                                                         | f = 50MHz, 10MHz spacing                             |     | -62  |     | dBc  | С                            |

| Second-order intermodulation                                            | f = 100MHz, 10MHz spacing                            |     | -76  |     | dBc  | С                            |

| distortion, Gain = +12dB, $R_L$ = 400 $\Omega$ , $V_{OUT}$ = 2 $V_{PP}$ | f = 150MHz, 10MHz spacing                            |     | -78  |     | dBc  | С                            |

| , 001 11                                                                | f = 200MHz, 10MHz spacing                            |     | -78  |     | dBc  | С                            |

<sup>(1)</sup> Test levels: (A) 100% tested at +25°C. Over-temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

Test conditions are at  $T_A = +25^{\circ}C$ ,  $V_{S+} = +5V$ ,  $V_{OCM} = +2.5V$ ,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$  differential, G = +12dB, differential input and output, and input and output referenced to midsupply, unless otherwise noted. Measured using evaluation module as discussed in *Test Circuits* section.

| PARAMETER                                                              | TE                                                                                                           | ST CONDITIONS                                       | MIN   | TYP      | MAX   | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------|----------|-------|--------------------|------------------------------|

|                                                                        | f = 50MHz, 10MHz spacing                                                                                     |                                                     |       | -97      |       | dBc                | С                            |

| Third-order intermodulation distortion, Gain = +12dB, R <sub>I</sub> = | f = 100MHz, 10MHz spacing                                                                                    |                                                     |       | -100     |       | dBc                | С                            |

| $400\Omega$ , $V_{OUT} = 2V_{PP}$                                      | f = 150MHz, 10MHz                                                                                            | spacing                                             |       | -92      |       | dBc                | С                            |

|                                                                        | f = 200MHz, 10MHz                                                                                            | spacing                                             |       | -81      |       | dBc                | С                            |

| AdDinint                                                               | f 400MU-                                                                                                     | $R_L = 20\Omega$                                    |       | 19.6     |       | dBm                | С                            |

| 1dB compression point                                                  | f = 100MHz                                                                                                   | $R_L = 400\Omega$                                   |       | 8.7      |       | dBm                | С                            |

| Output third-order intercept point                                     | At device outputs, R <sub>L</sub>                                                                            | = 400Ω, f = 100MHz                                  |       | 47       |       | dBm                | С                            |

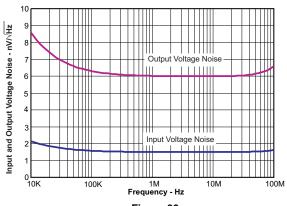

| Input-referred voltage noise                                           | f = 1MHz                                                                                                     |                                                     |       | 1.5      |       | nV/√ <del>Hz</del> | С                            |

| Ouput-referred voltage noise                                           | f = 1MHz                                                                                                     |                                                     |       | 6        |       | nV/√ <del>Hz</del> | С                            |

|                                                                        |                                                                                                              | f = 50 MHz                                          |       | 9.5      |       | dB                 | С                            |

| Noise figure                                                           | 100Ω differential source                                                                                     | f = 100 MHz                                         |       | 10.7     |       | dB                 | С                            |

|                                                                        | Source                                                                                                       | f = 200 MHz                                         |       | 12.3     |       | dB                 | С                            |

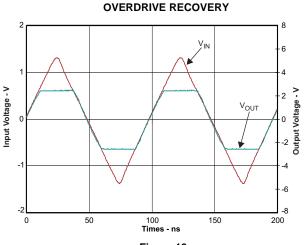

| Overdrive recovery                                                     | Overdrive = ±0.5V                                                                                            | ı                                                   |       | 5        | 7.5   | ns                 | В                            |

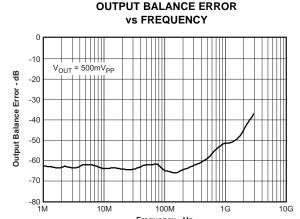

| Output balance error                                                   | f = 200MHz                                                                                                   |                                                     |       | -60      |       | dB                 | С                            |

| Output impedance                                                       | f = 100MHz                                                                                                   |                                                     |       | 4        |       | Ω                  | С                            |

| DC PERFORMANCE                                                         |                                                                                                              |                                                     |       | <u> </u> |       |                    |                              |

|                                                                        | $T_A = +25^{\circ}C, R_L = 400\Omega$                                                                        |                                                     | 11.65 | 11.9     | 12.15 | dB                 | Α                            |

|                                                                        | $T_A = +25^{\circ}C, R_L = 100\Omega$                                                                        |                                                     | 11.4  | 11.6     | 11.85 | dB                 | В                            |

| Gain (+12dB gain setting)                                              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, R_L = 400\Omega$                                         |                                                     | 11.6  |          | 12.2  | dB                 | В                            |

|                                                                        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          | 11.6                                                |       | 12.2     | dB    | В                  |                              |

|                                                                        | T <sub>A</sub> = +25°C                                                                                       |                                                     | -20   | ±2       | 20    | mV                 | Α                            |

| Output offset                                                          | $T_A = -40$ °C to +85°C                                                                                      |                                                     | -22.5 |          | 22.5  | mV                 | В                            |

|                                                                        | T <sub>A</sub> = +25°C                                                                                       |                                                     | 36    | 60       |       | dB                 | Α                            |

| Common-mode rejection ratio                                            | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          |                                                     | 35    |          |       | dB                 | В                            |

| INPUT                                                                  |                                                                                                              |                                                     |       |          |       |                    |                              |

| Differential input resistance                                          |                                                                                                              |                                                     | 85    | 100      | 115   | Ω                  | Α                            |

| Input common-mode range                                                | Inputs shorted togeth                                                                                        | er, V <sub>OCM</sub> = 2.5V                         | 2.25  |          | 2.75  | V                  | Α                            |

| OUTPUT                                                                 | , ,                                                                                                          | ,                                                   |       |          |       |                    |                              |

|                                                                        | Each output with                                                                                             | T <sub>A</sub> = +25°C                              | 3.64  | 3.7      |       | V                  | Α                            |

| Most positive output voltage                                           | 200Ω to midsupply                                                                                            | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | 3.59  |          |       | V                  | В                            |

|                                                                        | Each output with                                                                                             | T <sub>A</sub> = +25°C                              |       | 1.3      | 1.4   | V                  | Α                            |

| Least positive output voltage                                          | 200Ω to midsupply                                                                                            | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |       |          | 1.45  | V                  | В                            |

|                                                                        | Each output with                                                                                             | T <sub>A</sub> = +25°C                              | 3.59  | 3.6      |       | V                  | Α                            |

| Most positive output voltage                                           | 50Ω to midsupply                                                                                             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | 3.54  |          |       | V                  | В                            |

|                                                                        | Each output with                                                                                             | T <sub>A</sub> = +25°C                              |       | 1.3      | 1.5   | V                  | A                            |

| Least positive output voltage                                          | 50Ω to midsupply                                                                                             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |       |          | 1.55  | V                  | В                            |

|                                                                        | $T_A = +25^{\circ}C, R_L = 400$                                                                              | **                                                  | 4.4   | 4.8      |       | V <sub>PP</sub>    | В                            |

| Differential output voltage                                            | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                          |                                                     | 4.2   |          |       | V <sub>PP</sub>    | В                            |

|                                                                        | $T_A = +25^{\circ}C, R_L = 100$                                                                              |                                                     |       | 80       |       | mA                 | В                            |

| Differential output current drive                                      | $T_A = +25 \text{ C}, R_L = 10\Omega$<br>$T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, R_L = 10\Omega$ |                                                     |       | 80       |       | mA                 | В                            |

|                                                                        | $I_A = -40^{\circ} \text{C to } +85^{\circ} \text{C}, R_L = 10\Omega$                                        |                                                     |       | 00       |       | 111/1              |                              |

# **ELECTRICAL CHARACTERISTICS (continued)**

Test conditions are at  $T_A = +25^{\circ}C$ ,  $V_{S+} = +5V$ ,  $V_{OCM} = +2.5V$ ,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$  differential, G = +12dB, differential input and output, and input and output referenced to midsupply, unless otherwise noted. Measured using evaluation module as discussed in *Test Circuits* section.

| PARAMETER                                             | TEST CONDITIONS                                                                           | MIN      | TYP      | MAX  | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------|----------|----------|------|------|------------------------------|

| OUTPUT COMMON-MODE VO                                 | LTAGE CONTROL                                                                             |          | <u>.</u> |      |      |                              |

| V <sub>OCM</sub> small-signal bandwidth               | $V_{OUT\_CM} = 200 \text{mV}_{PP}$                                                        |          | 300      |      | MHz  | С                            |

| V <sub>OCM</sub> slew rate                            | V <sub>OUT_CM</sub> = 500mV step                                                          |          | 150      |      | V/µs | С                            |

| V <sub>OCM</sub> voltage range                        | Supplied by external source <sup>(2)</sup>                                                | 2.25     | 2.5      | 2.75 | V    | С                            |

| V <sub>OCM</sub> gain                                 | V <sub>OCM</sub> = 2.5V                                                                   | 0.98     | 1        | 1.02 | V/V  | Α                            |

| Output common-mode offset from V <sub>OCM</sub> input | V <sub>OCM</sub> = 2.5V                                                                   | -30      | ±12      | 30   | mV   | А                            |

| V <sub>OCM</sub> input bias current                   | 2.25V ≤ V <sub>OCM</sub> ≤ 2.75V                                                          | -400     | ±30      | 400  | μA   | Α                            |

| POWER SUPPLY                                          |                                                                                           | <u> </u> |          |      |      |                              |

| Specified operating voltage                           |                                                                                           | 4.75     | 5        | 5.25 | V    | С                            |

| Quiescent current                                     | T <sub>A</sub> = +25°C                                                                    | 85       | 100      | 115  | mA   | Α                            |

|                                                       | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                       | 80       |          | 125  | mA   | В                            |

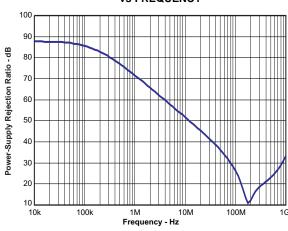

|                                                       | $T_A = +25^{\circ}C, V_{S+} = 5V \pm 0.25V$                                               | 60       | 90       |      | dB   | Α                            |

| Power-supply rejection ratio                          | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \ V_{S+} = 5\text{V} \pm 0.5\text{V}$ | 59       |          |      | dB   | В                            |

| POWER-DOWN                                            |                                                                                           | <u> </u> |          |      |      |                              |

| Enable voltage threshold                              | Device powers on below 0.5V                                                               |          |          | 0.5  | V    | Α                            |

| Disable voltage threshold                             | Device powers down above 2.0V                                                             | 2        |          |      | V    | Α                            |

| Power-down quiescent current                          |                                                                                           |          | 0.8      | 3    | mA   | Α                            |

| Input bias current                                    |                                                                                           |          | 80       | 100  | μA   | Α                            |

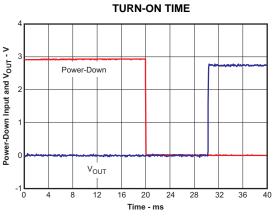

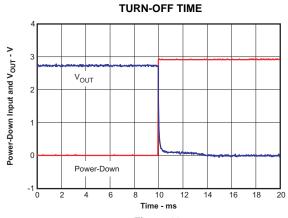

| Turn-on time delay                                    | Time to V <sub>OUT</sub> = 90% of final value                                             |          | 10       |      | μs   | С                            |

| Turn-off time delay                                   | Time to V <sub>OUT</sub> = 10% of original value                                          |          | 0.15     |      | μs   | С                            |

| THERMAL CHARACTERISTIC                                | s                                                                                         |          | •        | •    |      | •                            |

| Specified operating range                             |                                                                                           | -40      |          | +85  | °C   | С                            |

| Thermal resistance, $\theta_{JC}^{(3)}$               | Junction to case (bottom)                                                                 |          | 8.9      |      | °C/W | С                            |

| Thermal resistance, θ <sub>JA</sub> (3)               | Junction to ambient                                                                       |          | 44.1     |      | °C/W | С                            |

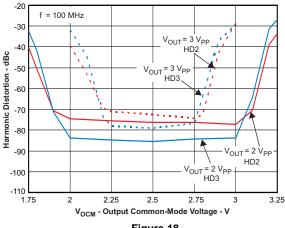

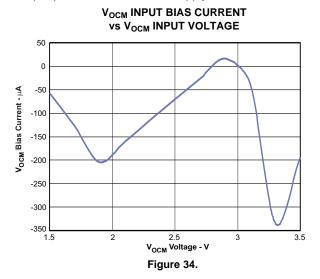

<sup>(2)</sup> Limits set by best harmonic distortion with V<sub>OUT</sub> = 3V<sub>PP</sub>. V<sub>OCM</sub> voltage range can be extended if lower output swing is used or distortion degradation is allowed, and increased bias current into pin is acceptable. For more information, see Figure 18 and Figure 34.

Copyright © 2010–2012, Texas Instruments Incorporated

<sup>(3)</sup> Tested using JEDEC High-K test PCB. Thermal management of the final printed circuit board (PCB) should keep the junction temperature below +125°C for long term reliability.

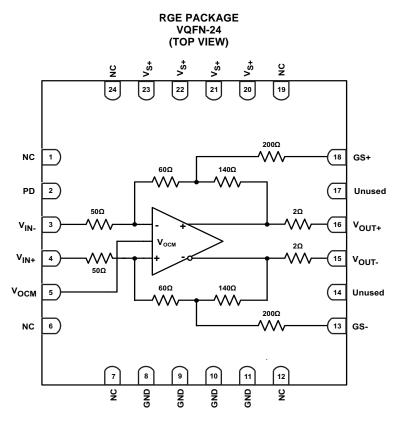

# **PIN CONFIGURATION**

# **PIN DESCRIPTIONS**

| PIN               |                   | DESCRIPTION                                                                          |

|-------------------|-------------------|--------------------------------------------------------------------------------------|

| NO.               | NAME              | DESCRIPTION                                                                          |

| 1                 | NC                | No internal connection                                                               |

| 2                 | PD                | Power down. High = low power (sleep) mode. Low = active.                             |

| 3                 | $V_{IN-}$         | Inverting input pin                                                                  |

| 4                 | $V_{IN+}$         | Non-inverting input pin                                                              |

| 5                 | V <sub>OCM</sub>  | Output common-mode voltage control input pin                                         |

| 6, 7              | NC                | No internal connection                                                               |

| 8, 9, 10, 11      | GND               | Ground. Must be connected to thermal pad.                                            |

| 12                | NC                | No internal connection                                                               |

| 13                | GS-               | Gain-setting connection for inverting output                                         |

| 14                | Unused            | Bonded to die, but not used. Tie to GND.                                             |

| 15                | V <sub>OUT</sub>  | Inverting output pin                                                                 |

| 16                | V <sub>OUT+</sub> | Non-inverting output pin                                                             |

| 17                | Unused            | Bonded to die, but not used. Tie to GND.                                             |

| 18                | GS+               | Gain-setting connection for non-inverting output                                     |

| 19                | NC                | No internal connection                                                               |

| 20, 21, 22,<br>23 | V <sub>S+</sub>   | Power supply pins, +5V nominal                                                       |

| 24                | NC                | No internal connection                                                               |

| Thermal           | pad               | Thermal pad on bottom of device is used for heat dissipation and must be tied to GND |

# **TYPICAL CHARACTERISTICS**

# **TABLE OF GRAPHS**

| TITLE                                                                                  | FIGURE    |

|----------------------------------------------------------------------------------------|-----------|

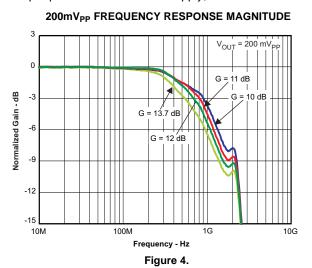

| 200mV <sub>PP</sub> Frequency Response Magnitude                                       | Figure 4  |

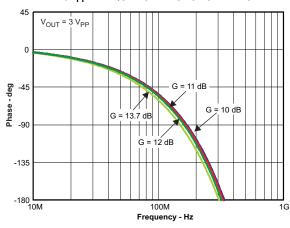

| 200mV <sub>PP</sub> Frequency Response Phase                                           | Figure 5  |

| 2V <sub>PP</sub> Frequency Response Magnitude                                          | Figure 6  |

| 2V <sub>PP</sub> Frequency Response Phase                                              | Figure 7  |

| 3V <sub>PP</sub> Frequency Response Magnitude                                          | Figure 8  |

| 3V <sub>PP</sub> Frequency Response Phase                                              | Figure 9  |

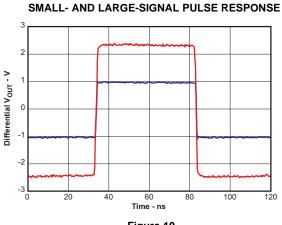

| Small- and Large-Signal Pulse Response                                                 | Figure 10 |

| Slew Rate vs Output Voltage Step                                                       | Figure 11 |

| Overdrive Recovery                                                                     | Figure 12 |

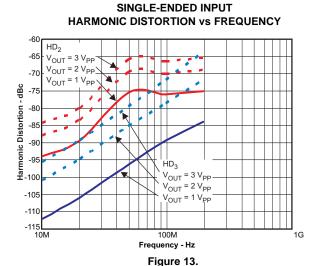

| Single-Ended Input Harmonic Distortion vs Frequency                                    | Figure 13 |

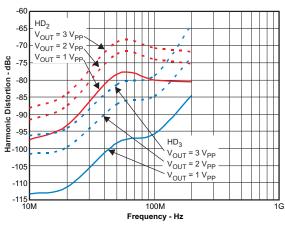

| Harmonic Distortion vs Frequency                                                       | Figure 14 |

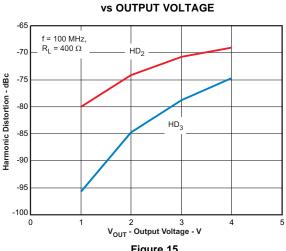

| Harmonic Distortion vs Output Voltage                                                  | Figure 15 |

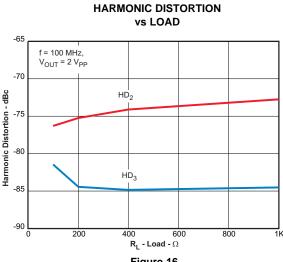

| Harmonic Distortion vs Load                                                            | Figure 16 |

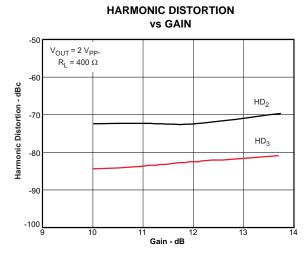

| Harmonic Distortion vs Gain                                                            | Figure 17 |

| Harmonic Distortion vs Output Common-Mode Voltage                                      | Figure 18 |

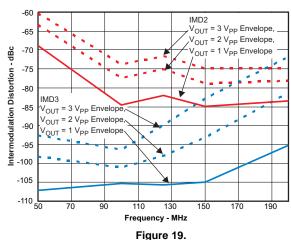

| Intermodulation Distortion vs Frequency                                                | Figure 19 |

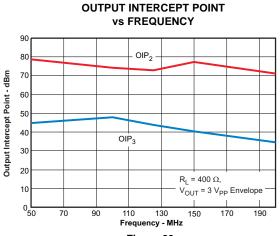

| Output Intercept Point vs Frequency                                                    | Figure 20 |

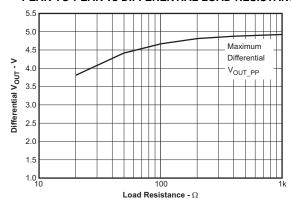

| Maximum Differential Output Voltage Swing Peak-to-Peak vs Differential Load Resistance | Figure 21 |

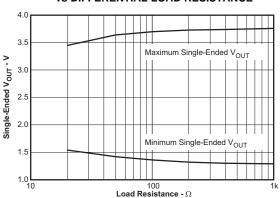

| Maximum/Minimum Single-Ended Output Voltage vs Differential Load Resistance            | Figure 22 |

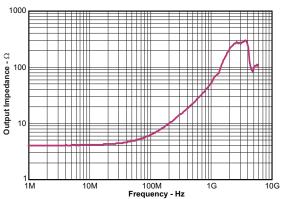

| Differential Output Impedance vs Frequency                                             | Figure 23 |

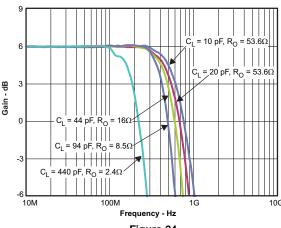

| Frequency Response vs Capacitive Load                                                  | Figure 24 |

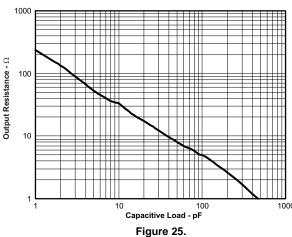

| Recommended Output Resistance vs Capacitive Load                                       | Figure 25 |

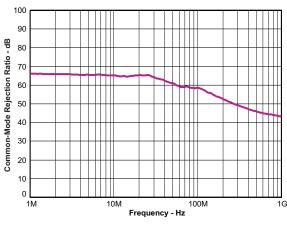

| Common-Mode Rejection Ratio vs Frequency                                               | Figure 26 |

| Power-Supply Rejection Ratio vs Frequency                                              | Figure 27 |

| Turn-On Time                                                                           | Figure 28 |

| Turn-Off Time                                                                          | Figure 29 |

| Input and Output Voltage Noise vs Frequency                                            | Figure 30 |

| Output Balance Error vs Frequency                                                      | Figure 31 |

| V <sub>OCM</sub> Small-Signal Frequency Response                                       | Figure 32 |

| Output Common-Mode Pulse Response                                                      | Figure 33 |

| V <sub>OCM</sub> Input Bias Current vs V <sub>OCM</sub> Input Voltage                  | Figure 34 |

| s-Parameters (Magnitude)                                                               | Figure 35 |

| Noise Figure vs Frequency                                                              | Figure 36 |

#### TYPICAL CHARACTERISTICS

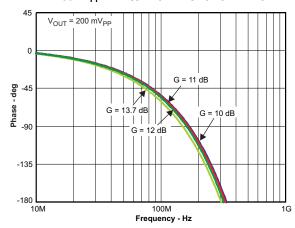

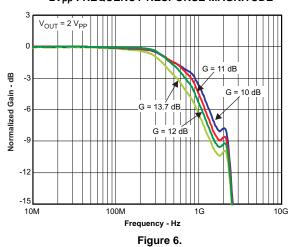

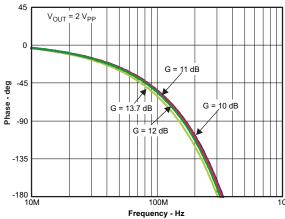

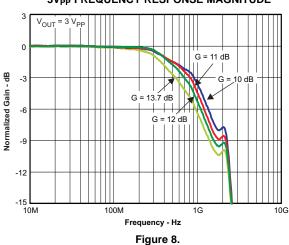

At  $T_A = +25^{\circ}\text{C}$ ,  $V_{S+} = +5\text{V}$ ,  $V_{OCM} = +2.5\text{V}$ ,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$  differential, G = +12dB, differential input and output, input and output pins referenced to midsupply, unless otherwise noted. Measured using EVM as discussed in *Test Circuits* section.

# 200mV<sub>PP</sub> FREQUENCY RESPONSE PHASE

Figure 5.

# 2V<sub>PP</sub> FREQUENCY RESPONSE MAGNITUDE

2V<sub>PP</sub> FREQUENCY RESPONSE PHASE

Figure 7.

#### 3V<sub>PP</sub> FREQUENCY RESPONSE MAGNITUDE

#### 3VPP FREQUENCY RESPONSE PHASE

Figure 9.

At  $T_A$  = +25°C,  $V_{S+}$  = +5V,  $V_{OCM}$  = +2.5V,  $V_{OUT}$  = 2 $V_{PP}$ ,  $R_L$  = 400 $\Omega$  differential, G = +12dB, differential input and output, input and output pins referenced to midsupply, unless otherwise noted. Measured using EVM as discussed in *Test Circuits* section.

Figure 10.

Figure 11.

Figure 12.

HARMONIC DISTORTION

vs FREQUENCY

HARMONIC DISTORTION

Figure 14.

Figure 15.

At  $T_A$  = +25°C,  $V_{S+}$  = +5V,  $V_{OCM}$  = +2.5V,  $V_{OUT}$  = 2 $V_{PP}$ ,  $R_L$  = 400 $\Omega$  differential, G = +12dB, differential input and output, input and output pins referenced to midsupply, unless otherwise noted. Measured using EVM as discussed in *Test Circuits* section.

Figure 16.

Figure 17.

#### HARMONIC DISTORTION **vs OUTPUT COMMON-MODE VOLTAGE**

Figure 18.

#### INTERMODULATION DISTORTION vs FREQUENCY

Figure 20.

#### MAXIMUM DIFFERENTIAL OUTPUT VOLTAGE SWING PEAK-TO-PEAK vs DIFFERENTIAL LOAD RESISTANCE

Figure 21.

At  $T_A$  = +25°C,  $V_{S+}$  = +5V,  $V_{OCM}$  = +2.5V,  $V_{OUT}$  = 2 $V_{PP}$ ,  $R_L$  = 400 $\Omega$  differential, G = +12dB, differential input and output, input and output pins referenced to midsupply, unless otherwise noted. Measured using EVM as discussed in *Test Circuits* section.

# MAXIMUM/MINIMUM SINGLE-ENDED OUTPUT VOLTAGE vs DIFFERENTIAL LOAD RESISTANCE

Figure 22.

# DIFFERENTIAL OUTPUT IMPEDANCE vs FREQUENCY

Figure 23.

# FREQUENCY RESPONSE vs CAPACITIVE LOAD

Figure 24.

# RECOMMENDED OUTPUT RESISTANCE vs CAPACITIVE LOAD

COMMON-MODE REJECTION RATIO vs FREQUENCY

Figure 26.

# POWER-SUPPLY REJECTION RATIO vs FREQUENCY

Figure 27.

At  $T_A = +25^{\circ}C$ ,  $V_{S+} = +5V$ ,  $V_{OCM} = +2.5V$ ,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$  differential, G = +12dB, differential input and output, input and output pins referenced to midsupply, unless otherwise noted. Measured using EVM as discussed in *Test Circuits* section.

Figure 28.

Figure 29.

# INPUT AND OUTPUT VOLTAGE NOISE vs FREQUENCY

Figure 30.

Frequency - Hz Figure 31.

#### **VOCM SMALL-SIGNAL FREQUENCY RESPONSE**

Figure 32.

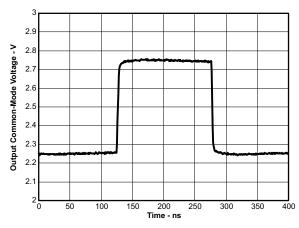

#### **OUTPUT COMMON-MODE PULSE RESPONSE**

Figure 33.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ ,  $V_{S+} = +5V$ ,  $V_{OCM} = +2.5V$ ,  $V_{OUT} = 2V_{PP}$ ,  $R_L = 400\Omega$  differential, G = +12dB, differential input and output, input and output pins referenced to midsupply, unless otherwise noted. Measured using EVM as discussed in *Test Circuits* section.

Figure 35.

#

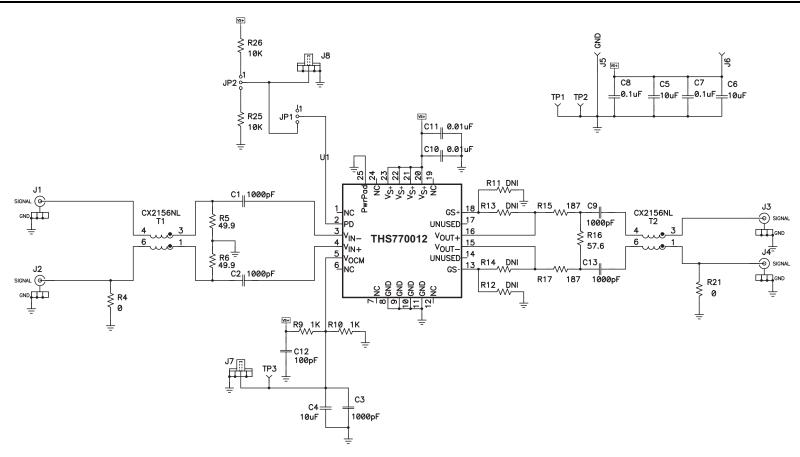

#### **TEST CIRCUITS**

#### **OVERVIEW**

The standard THS770012 evaluation module (EVM) is used for testing the typical performance shown in the Typical Characteristics, with changes as noted below. The EVM schematic is shown in Figure 37. The signal generators and analyzers used for most tests have single-ended  $50\Omega$  input and output impedance. The THS770012 EVM is configured to convert to and from a single-ended  $50\Omega$  impedance by using RF transformers or baluns 1:1 (CX2156NL from Pulse, supplied as a standard configuration of the EVM) to allow easy connection to standard lab equipment. For line input termination, two  $49.9\Omega$  resistors (R5 and R6) are placed to ground on the input transformer output pins (terminals 1 and 3). In combination with the  $100\Omega$  input impedance of the device, the total impedance seen by the line is  $50\Omega$ .

Gain is set by placing external components R11, R12, R13, and R14 as described below in Setting the Gain section.

A resistor network is used on the amplifier output to present various loads ( $R_L$ ) and maintain line output termination to  $50\Omega$ . Depending on the test conditions, component values are changed as shown in Table 1, or as otherwise noted. As a result of the voltage divider on the output formed by the load component values, the amplifier output is attenuated. The Loss column in Table 1 shows the attenuation expected from the resistor divider. The output transformer causes slightly more loss, so these numbers are approximate.

Table 1. Load Component Values (1)

| LOAD R <sub>L</sub> | R15 AND R17 | R16   | LOSS   |

|---------------------|-------------|-------|--------|

| 100Ω                | 25Ω         | Open  | 6dB    |

| 200Ω                | 86.6Ω       | 69.8Ω | 16.8dB |

| 400Ω                | 187Ω        | 57.6Ω | 25.5dB |

| 1kΩ                 | 487Ω        | 52.3Ω | 31.8dB |

<sup>(1)</sup> The total load includes  $50\Omega$  termination by the test equipment. Components are chosen to achieve load and  $50\Omega$  line termination through a 1:1 transformer.

Figure 37. THS770012IRGE EVM Schematic

#### TEST DESCRIPTIONS

The following sections describe how the tests were performed, as well as the EVM circuit modifications that were made (if any). Modifications made for test purposes include changing capacitors to resistors, resistors to capacitors, the shorting/opening of components, etc., as noted. Unless otherwise noted, C1, C2, C9, and C13 are all changed to  $0.1\mu\text{F}$  to give basically flat frequency response from below 1MHz to the bandwidth of the amplifier, and gain is set to nominal +12dB.

# Frequency Response: 200mV<sub>PP</sub>, 2V<sub>PP</sub>, 3V<sub>pp</sub>

The test is run on the standard EVM using the transformers in the signal path.

A network analyzer is connected to the input and output of the EVM with  $50\Omega$  coaxial cables and set to measure the forward transfer function (s21). The input signal frequency is swept with signal level set for desired output amplitude.

The test ran for gains of +10dB, +11dB, +12dB and +13.7dB with component values changed per Table 2 in Setting the Gain section.

#### s-Parameters: s11, s22, and s12

The standard EVM is used with both R15 and R17 =  $24.9\Omega$ , and R16 = open, to test the input return loss, output return loss, and reverse isolation. A network analyzer is connected to the input and output of the EVM with  $50\Omega$  coaxial cables and set to measure the appropriate transfer function: s11, s22, or s12. Note the transformers are included in the signal chain in order to retrieve proper measurements with single-ended test equipment. The impact is minimal from 10MHz to 200MHz, but further analysis is required to fully de-embed the respective effects.

#### Frequency Response with Capacitive Load

The standard EVM is used with R15 and R17 =  $R_O$ , R16 =  $C_{LOAD}$ , C9 and C13 = 953 $\Omega$ , R21 = open, T2 removed, and jumpers placed across terminals 3 to 4 and 1 to 6. A network analyzer is connected to the input and output of the EVM with  $50\Omega$  coaxial cables and set to measure the forward transfer function (s21). Different values of load capacitance are placed on the output (at R16) and the output resistor values (R15 and R17) changed until an optimally flat frequency response is achieved with maximum bandwidth.

# **Distortion**

The standard EVM is used for measurement of single-tone harmonic distortion and two-tone intermodulation distortion. For differential distortion measurements, the standard EVM is used with no modification. For single-ended input distortion measurements, the standard EVM is used with with T1 removed and jumpers placed across terminals 3 to 4 and 1 to 6, and R5 and R6 =  $100\Omega$ . A signal generator is connected to the J1 input of the EVM with  $50\Omega$  coaxial cables, with filters inserted inline to reduce distortion from the generator. The J3 output of the EVM is connected with  $50\Omega$  coaxial cables to a spectrum analyzer to measure the fundamental(s) and distortion products.

# **Noise Figure**

The standard EVM is used with T1 changed to a 1:2 impedance ratio transformer (Mini-Circuits ADT2), R15 and R17 = 24.9 $\Omega$ , and R5, R6, and R16 = open. A noise figure analyzer is connected to the input and output of the EVM with  $50\Omega$  coaxial cables. The noise figure analyzer provides a  $50\Omega$  (noise) source so that the data are adjusted to refer to a  $100\Omega$  source.

#### Transient Response, Slew Rate, Overdrive Recovery

The standard EVM is used with T1 and T2 removed and jumpers placed across terminals 3 to 4 and 1 to 6; R15, R17, and R25 =  $49.9\Omega$ ; C1, C2, C9, and C13 =  $0\Omega$ ; and R5, R6, R16, and R21 = open. A differential waveform generator is connected to the input of the EVM with  $50\Omega$  coaxial cables at J1 and J2. The differential output at J3 and J4 is connected with  $50\Omega$  coaxial cables to an oscilloscope to measure the outputs. Waveform math in the oscilloscope is used to combine the differential output of the device.

#### **Power-Down**

The standard EVM is used with T1 and T2 removed, jumpers placed across terminals 3 to 4 and 1 to 6, R15 and R17 =  $49.9\Omega$ , C9 and C13 =  $0\Omega$ , and R5, R6, R16, and R21 = open. A waveform generator is connected to the power-down input of the EVM with a  $50\Omega$  coaxial cable at J8. The differential output at J3 and J4 is connected with  $50\Omega$  coaxial cables to an oscilloscope to measure the outputs. J1 is left disconnected so that the output is driven to the  $V_{OCM}$  voltage when the device is active, and discharged through the resistive load on the output when disabled. Both outputs are the same and only one is shown.

#### **Differential Z-out**

The standard EVM is used with R15 and R17 =  $24.9\Omega$ , and R16 = open. A network analyzer is connected to the output of the EVM at J3 with  $50\Omega$  coaxial cable, both inputs are terminated with a  $50\Omega$  load, and a high-impedance differential probe is used for the measurement. The analyzer is set to measure the forward transfer function (s21). The analyzer with probe input is calibrated across the open resistor pads of R16 and the signal is measured at the output pins of the device. The output impedance is calculated using the known resistor values and the attenuation caused by R15 and R17.

# **Output Balance Error**

The standard EVM is used with R15 and R17 =  $100\Omega$ , and R16 =  $0\Omega$ . A network analyzer is connected to the input of the EVM with  $50\Omega$  coaxial cable, the output is left open, and a high-impedance differential probe is used for the measurement. The analyzer is set to measure the forward transfer function (s21). The analyzer with probe input is calibrated at the input pins of the device and the signal is measured from the shorted pads of R16 to ground.

### **Common-Mode Rejection**

The standard EVM is used with T1 removed and jumpers place across terminals 3 to 4, 1 to 6, and 1 to 3. A network analyzer is connected to the input and output of the EVM with  $50\Omega$  coaxial cable and set to measure the forward transfer function (s21).

# **V<sub>OCM</sub>** Frequency Response

The standard EVM is used with T2 removed and jumpers across terminals 3 to 4 and 1 to 6; R10, R15, and R17 =  $49.9\Omega$ ; C3 and C4 =  $0\Omega$ ; and R9, R16, and R21 = open. A network analyzer is connected to the V<sub>OCM</sub> input of the EVM at J7 and output of the EVM with  $50\Omega$  coaxial cable, and set to measure the forward transfer function (s21). The input signal frequency is swept with the signal level set for 200mV. Each output at J3 and J4 is measured as single-ended, and because both are the same, only one output is shown.

# **V<sub>OCM</sub> Slew Rate and Pulse Response**

The standard EVM is used with T2 removed and jumpers across terminals 3 to 4 and 1 to 6; R10, R15, and R17 =  $49.9\Omega$ ; C9 and C13 =  $0\Omega$ ; and C3, C4, R9, R16, and R21 = open. A waveform generator is connected to the  $V_{OCM}$  input of the EVM at J7 with  $50\Omega$  coaxial cable. The differential output at J3 and J4 is connected with  $50\Omega$  coaxial cable to an oscilloscope to measure the outputs. J1 is left disconnected so that the output is driven to the  $V_{OCM}$  voltage. Both outputs are the same, so only one is shown.

# Input/Output Voltage Noise, Settling Time, and Power-Supply Rejection

These parameters are taken from simulation.

#### THEORY OF OPERATION

### **GENERAL DESCRIPTION**

The THS770012 is a wideband, fully differential amplifier designed and optimized specifically for driving 14-bit and 16-bit ADCs at input frequencies up to 200MHz. This device provides high bandwidth, low distortion, and low noise, which are critical parameters in high-speed data acquisition systems that require very high dynamic range, such as wireless base stations and test and measurement applications. It also makes an excellent differential amplifier for general-purpose, high-speed differential signal chain and short line-driver applications. The device has an operating power-supply range of 4.75V to 5.5V. The THS770012 has proprietary circuitry to provide very fast recovery from overdrive conditions and has a power-down mode for power saving. The THS770012 is offered in a Pb-free (RoHS compliant) and green, QFN-24 thermally-enhanced package. It is characterized for operation over the industrial temperature range of -40°C to +85°C.

The amplifier uses two negative-feedback loops. One is for the primary differential amplifier and the other controls the common-mode operation.

#### **Primary Differential Amplifier**

The primary amplifier of the THS770012 is a fully-differential op amp with on-chip gain setting resistors. The gain of the device can be changed by using external components as described in Setting the Gain section below. The nominal gain with no external connections is set to +12dB with  $R_F = 200\Omega$  and  $R_G = 50\Omega$ .

# **Vocm Control Loop**

The output common-mode voltage is controlled through a second negative-feedback loop. The output common-mode voltage is internally sensed and compared to the  $V_{\rm OCM}$  pin. The loop then works to drive the difference, or error voltage, to zero in order to maintain the output common-mode voltage =  $V_{\rm OCM}$  (within the loop gain and bandwidth of the loop). For more details on fully-differential amplifier theory and use, see application report SLOA054, *Fully-Differential Amplifiers*, available for download from www.ti.com.

#### **OPERATION**

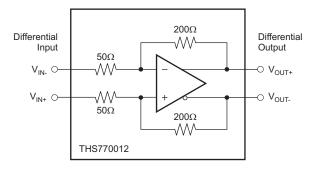

#### **Differential to Differential**

The THS770012 is a fully-differential amplifier that can be used to amplify differential input signals to differential output signals. A basic block diagram of the circuit with nominal gain of +12dB is shown in Figure 38. The differential input to differential output configuration gives the best performance; the signal source and load should be balanced.

Figure 38. Differential Input to Differential Output Amplifier

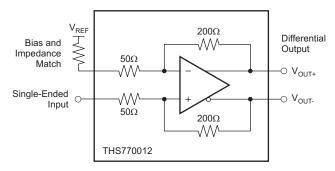

### Single-Ended to Differential

The THS770012 can be used to amplify and convert single-ended input signals to differential output signals. A basic block diagram of the circuit with nominal gain of +12dB is shown in Figure 39. In order to maintain proper balance in the amplifier and avoid offsets at the output, the alternate input must be biased and the impedance matched to the signal input. For example, if a  $50\Omega$  source biased to 2.5V provides the input, the alternate input should be tied to 2.5V through  $50\Omega$ . If a  $50\Omega$  source is ac-coupled to the input, the alternate input should be ac-coupled to ground through  $50\Omega$ . Note that the ac coupling should provide a similar frequency response to balance the gain over frequency.

Figure 39. Single-Ended Input to Differential Output Amplifier

### **Setting the Gain**

Gain is adjustable by placing external components in positions R11, R12, R13, and R14 on the EVM. Table 2 below shows the component values for setting gain from +10dB to +13.7dB. The different configurations and values change the effective value of the internal feedback, where the gain is determined by the resultant effective  $R_F/R_G$ , where  $R_G = 50\Omega$

| GAIN                                              | R11, R12          | R13, R14 | EFFECTIVE R <sub>F</sub>                                              |

|---------------------------------------------------|-------------------|----------|-----------------------------------------------------------------------|

| +10dB                                             | Open              | 140 Ω    | 140    340 + 60 = 159 Ω                                               |

| +11dB                                             | Open              | 523 Ω    | 140    723 + 60 = 177 Ω                                               |

| +12dB                                             | Open              | Open     | 140 + 60 = 200 Ω                                                      |

| +13.7dB (AC gain), +12dB (DC gain) <sup>(1)</sup> | 0.1 μF capacitors | Open     | $\frac{(140 \mid\mid 200 + 60) \times (140 + 200)}{200} = 242 \Omega$ |

Table 2. Gain Settings

# **Setting the Output Common-Mode Voltage**

The  $V_{OCM}$  input controls the output common-mode voltage.  $V_{OCM}$  has no internal biasing network and must be driven by an external source or resistor divider network to the positive power supply. In ac-coupled applications, the  $V_{OCM}$  input impedance and bias current are not critical, but in dc-coupled applications where more accuracy is desired, the input bias current of the pin should be considered. For best harmonic distortion with  $V_{OUT} = 3V_{PP}$ , the  $V_{OCM}$  input should be maintained within the operating range of 2.25V to 2.75V. The  $V_{OCM}$  input voltage can be operated outside this range if lower output swing is used or distortion degradation is allowed, and increased bias current into the pin is acceptable. For more information, see Figure 18 and Figure 34. It is recommended to use a  $0.1\mu F$  decoupling capacitor from the  $V_{OCM}$  pin to ground to prevent noise and other spurious signals from coupling into the common-mode loop of the amplifier.

#### Input Common-Mode Voltage Range

The THS770012 is designed primarily for ac-coupled operation. With input dc blocking, the input common-mode voltage of the device is driven to the same voltage as  $V_{\rm OCM}$  by the outputs. Therefore, as long as the  $V_{\rm OCM}$  input is maintained within the operating range of 2.25V to 2.75V, the input common-mode of the main amplifier is also maintained within its linear operating range of 2.25V to 2.75V. If the device is used with dc coupled input, the driving source needs to bias the input to its linear operating range of 2.25V to 2.75V for proper operation.

Using 0.1 μF capacitors for R11 and R12 limits the low frequency response to the default value of +12dB at frequency below about 10kHz. For +13.7dB gain at DC, connect pins 13 and 18 of the device to a low impedance voltage source equal to V<sub>OCM</sub> (+2.5V nominal).

### Operation with Split Supply ±2.5V

The THS770012 can be operated using a split  $\pm 2.5 \text{V}$  supply. In this case,  $\text{V}_{\text{S+}}$  is connected to  $\pm 2.5 \text{V}$ , and GND (and any other pin noted to be connected to GND) is connected to  $\pm 2.5 \text{V}$ . As with any device, the THS770012 is impervious to what the user decides to name the levels in the system. In essence, it is simply a level shift of the power pins by  $\pm 2.5 \text{V}$ . If everything else is level-shifted by the same amount, the device sees no difference. With a  $\pm 2.5 \text{V}$  power supply, the  $\pm 2.5 \text{V}$  and input and output voltage ranges are symmetrical about 0V. This design has certain advantages in systems where signals are referenced to ground, and as noted in the following section, for driving ADCs with low input common-mode voltage requirements in dc-coupled applications.

#### **Driving Capcitive Loads**

The THS770012 is tested as described previously, with the data shown in the typical graphs. Due to the internal gain resistor architecture used on the device, the only practical means to avoid stability problems such as overshoot/ringing, gain peaking, and oscillation when driving capacitive loads is to place small resistors in series with the outputs ( $R_O$ ) to isolate the phase shift caused by the capacitive load from the feedback loop of the amplifier. Note there are  $2\Omega$  internal resistors in series with each output to help maintain stability. The Typical Characteristics graphs show recommended values for an optimally flat frequency response with maximum bandwidth. Smaller values of  $R_O$  can be used if more peaking is allowed, and larger values can be used to reduce the bandwidth.

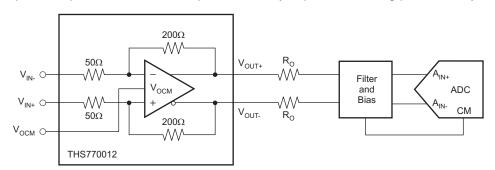

# **Driving ADCs**

The THS770012 is designed and optimized for the highest performance to drive differential input ADCs. Figure 40 shows a generic block diagram of the THS770012 driving an ADC. The primary interface circuit between the amplifier and the ADC is usually a filter of some type for antialias purposes, and provides a means to bias the signal to the input common-mode voltage required by the ADC. Filters range from single-order real RC poles to higher-order LC filters, depending on the requirements of the application. Output resistors (R<sub>O</sub>) are shown on the amplifier outputs to isolate the amplifier from any capacitive loading presented by the filter.

Figure 40. Generic ADC Driver Block Diagram

The key points to consider for implementation are described in the following three subsections.

#### SNR Considerations

The signal-to-noise ratio (SNR) of the amplifier + filter + ADC adds in RMS fashion. Noise from the amplifier is bandwidth-limited by the filter. Depending on the amplitude of the signal and the bandwidth of the filter, the SNR of the amplifier + filter can be calculated. To get the combined SNR, this value is then squared, added to the square of the ADC SNR, and the square-root is taken. If the SNR of the amplifier + filter equals the SNR of the ADC, the combined SNR is 3dB higher and for minimal inpact on the ADC's SNR the SNR of the amplifier + filter should be 10dB or more lower. The combined SNR calculated in this manner is usually accurate to within ±1dB of actual implementation.

#### SFDR Considerations

Theoretically, the spurious-free dynamic range (SFDR) of the amplifier + filter + ADC adds linearly on a spur-by-spur basis. The amplifier output spurs are linearly related solely to the input signal and the SFDR is usually set by second-order or third-order harmonic distortion for single-tone inputs, and by second-order or third-order intermodulation distortion for two-tone inputs. Harmonic and second-order intermodulation distortion can be filtered to some degree by the antialias filter, but not third-order intermodulation distortion. Generally, the ADC also has the same distortion products, but as a result of the sampling nature and potential for clock feedthrough, there may be spurs not linearly related solely to the input signal. When the spurs from the amplifier + filter are known, each can be directly added to the same spur from the ADC. This is a worst-case analysis based on the assumption the spurs sources are in phase. If the spur of the amplifier + filter equals the spur of the ADC, the combined spur is 6dB higher. The combined spur calculated in this manner is usually accurate to within ±6dB of actual implementation, but higher variations have been observed especially in second-order performance as a result of phase shift in the filter.

Common-mode phase shift introduced by the filter nullifies the basic assumption that the spur sources are in phase. This phase shift can lead to better performance than predicted as the spurs become phase shifted, and there is the potential for cancellation as the phase shift reaches 180°.

Differential phase and magnitude imbalance in the filter as a result of mismatched components caused by nominal tolerance can severely degrade the second-order distortion of the ADC. Single-order RC filters cause very little differential phase shift with nominal tolerances of 5% or less, but higher-order LC filters are very sensitive to component mismatch. For instance, a third-order Butterworth bandpass filter with 100MHz center frequency and 20MHz bandwidth shows up to 20° differential phase imbalance in a Spice Monte Carlo analysis with 2% component tolerances. Therefore, while a prototype may work, production variance is unacceptable. Low tolerance 1% components and low order filter is recommended for best performance. Otherwise a transformer or balun is recommended at the ADC input to restore the phase balance in the input signal to the ADC.

### ADC Input Common-Mode Voltage Considerations

The input common-mode voltage range of the ADC must be observed for proper operation. In an ac-coupled application between the amplifier and the ADC, the input common-mode voltage bias of the ADC is accomplished in different ways depending on the ADC. Some use internal bias networks and others use external components, such as resistors, from each input to the CM output of the ADC. When ac coupling, the output common-mode voltage of the amplifier is a *don't care* for the ADC, and V<sub>OCM</sub> should be set for optimum performance of the amplifier.

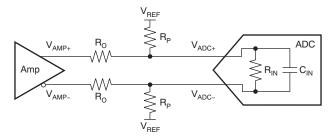

DC-coupled applications vary in complexity and requirements, depending on the ADC. Devices such as the ADS5424 require a nominal 2.4V input common-mode, while others such as the ADS5485 require a nominal 3.1V input common-mode, and still others like the ADS6149 require 1.5V and the ADS4149 require 0.95V. Given the THS770012 output common-mode range, ADCs with input common-mode closer to 2.5V are easier to dc-couple to, and require little or no level shifting. For applications that require a different common-mode voltage between the amplifier and the ADC, a resistor network can be used, as shown in Figure 41. With ADCs that have internal resistors ( $R_{\rm INT}$ ) that bias the ADC input to  $V_{\rm CM}$ , the bias resistors do not affect the desired value of  $R_{\rm P}$ , but do cause more attenuation of the differential input signal. Knowing the differential input resistance is required and sometimes, that is all that is provided.

Figure 41. Resistor Network to DC Level Shift Common-Mode Voltage

For common-mode analysis, assume that  $V_{AMP\pm} = V_{OCM}$  and  $V_{ADC\pm} = V_{ADC}$  (the specification for the ADC input common-mode voltage).  $V_{REF}$  is chosen to be a voltage within the system (such as the ADC or amplifier analog supply) or ground, depending on whether the voltage must be pulled up or down, and  $R_O$  is chosen to be a reasonable value, such as  $49.9\Omega$ . With these known values,  $R_P$  can be found by using Equation 1:

$$R_{P} = R_{O} \left( \frac{V_{ADC} - V_{REF}}{V_{AMP} - V_{ADC}} \right) \tag{1}$$

The insertion of this resistor network also attenuates the amplifier output signal. The gain (or loss) can be calculated by Equation 2:

GAIN =

$$\frac{2R_{P} || Z_{IN}}{2R_{O} + 2R_{P} || Z_{IN}}$$

(2)

Using the gain and knowing the full-scale input of the ADC, V<sub>ADC FS</sub>, the required amplitude to drive the ADC with the network can be calculated using Equation 3:

$$V_{AMPPP} = \frac{V_{ADCFS}}{GAIN}$$

(3)

Using the ADC examples given previously, Table 3 shows sample calculations of the value of  $R_P$  and  $V_{AMP\ FS}$  for full-scale drive, and then for -1dB (often times, the ADC drive is backed off from full-scale in applications, so lower amplitudes may be acceptable). All voltages are in volts, resistors in  $\Omega$  (the nearest standard value should be used), and gain as noted. Table 3 does not include the ADS5424 because no level shift is required with this device.

Table 3. Example  $R_P$  for Various ADCs

| ADC     | V <sub>OCM</sub><br>(V <sub>DC</sub> ) | V <sub>ADC</sub><br>(V <sub>DC</sub> ) | V <sub>REF</sub><br>(V <sub>DC</sub> ) | R <sub>INT</sub> (Ω) | R <sub>O</sub><br>(Ω) | R <sub>P</sub><br>(Ω) | GAIN<br>(V/V) | GAIN<br>(dB) | V <sub>ADC FS</sub> (V <sub>PP</sub> ) | V <sub>AMP PP</sub><br>FS (V <sub>PP</sub> ) | V <sub>AMP PP</sub><br>-1dBFS (V <sub>PP</sub> ) |

|---------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------|-----------------------|-----------------------|---------------|--------------|----------------------------------------|----------------------------------------------|--------------------------------------------------|

| ADS5485 | 2.5                                    | 3.1                                    | 5                                      | 1k                   | 50                    | 158.3                 | 0.73          | -2.71        | 2                                      | 4.10                                         | 3.65                                             |

| ADS6149 | 2.5                                    | 1.5                                    | 0                                      | NA                   | 50                    | 75.0                  | 0.60          | -4.44        | 2                                      | 3.33                                         | 2.97                                             |

| ADS4149 | 2.5                                    | 0.95                                   | 0                                      | NA                   | 50                    | 30.6                  | 0.38          | -8.40        | 2                                      | 5.26                                         | 4.69                                             |

| ADS4149 | 0 <sup>(1)</sup>                       | 0.95                                   | 2.5                                    | NA                   | 50                    | 81.6                  | 0.62          | -4.15        | 2                                      | 3.23                                         | 2.88                                             |

<sup>(1)</sup> THS770012 with ±2.5V supply.

The calculated values for the ADS5485 give the lowest attenuation, and because of the high  $V_{FS}$ , it requires  $3.65V_{PP}$  from the amplifier to drive to -1dBFS. Performance of the THS770012 is still very good up to 130MHz at this level, but the designer may want to further back off from full-scale for best performance and consider trading reduced SNR performance for better SFDR performance.

The values calculated for the ADS6149 show reasonable design targets and should work with good performance. Note the ADS6149 does not have buffered inputs, and the inputs have equivalent resistive impedance that varies with sampling frequency. In order to account for the increased loss, half of this resistance should be used for the value of  $R_{\rm INT}$  in Equation 2.

The values calculated for the low input common-mode of the ADS4149 result in large attenuation of the amplifier signal leading to  $5.26V_{PP}$  being required for full-scale ADC drive. This amplitude is greater than the maximum capability of the device. With a single +5V supply, the THS770012 is not suitable to drive this ADC in dc-coupled applications unless the ADC input is backed off towards –6dBFS. Another option is to operate the THS770012 with a split  $\pm 2.5V$  supply, and is shown in the last row of Table 3. For this situation, if the  $\pm 2.5V$  is used as the pull-up voltage, only  $\pm 2.8V_{PP}$  is required for the  $\pm 1.00$  hours of the ADS4149. See the Operation with Split Supply  $\pm 2.5V$  section for more detail. Note that the ADS4149 does not have buffered inputs and the inputs have equivalent resistive impedance that varies with sampling frequency. In order to account for the increased loss, half of this resistance should be used for the value of  $R_{INT}$  in Equation 2.

As with any design, testing is recommended to validate whether it meets the specific design goals.

22

#### APPLICATION INFORMATION

#### THS770012 DRIVING 16-BIT ADC

To illustrate the performance of the THS770012 as an ADC driver, the device is tested with a 16-bit ADC.

For testing purposes, a 30MHz, second-order Butterworth bandpass filter with center frequency at 100MHz is designed. The design target for the source impedance is  $40\Omega$  differential, and for load impedance is  $400\Omega$  differential. Therefore, approximately 1dB insertion loss is expected in the pass-band, requiring the amplifier output amplitude to be  $2.5V_{PP}$  to drive the ADC to -1dBFS.

The output noise voltage specification for the THS770012 is 6 nV/ $\sqrt{\text{Hz}}$ . With 2.5V<sub>PP</sub> amplifier output voltage swing and 30MHz bandwidth, the expected SNR from the amplifier + antialias filter is 88.5dBc. When added in combination with the 16-bit ADC, the expected total SNR is 75.2dBFS for the typical case.

Figure 42 shows the resulting FFT plot when driving the ADC to -1dBFS with a single-tone 95MHz sine wave, and sampling at 130MSPS. Test results show 100dBc SFDR from the forth-order harmonic and 74.4 dBFS SNR; analysis of the plot is shown in Table 4 versus typical ADC specifications. The test results from circuit board to circuit board shows over 10dB of variation in the second order harmonic due to component tolerance. Using lower 1% tolerance components or adding a balun between the filter and ADC inputs resulted in less variation and the typical expected results should be better than 95dBc SFDR and 74dB SNR.

Figure 42. FFT Plot of THS770012 + 30MHz BPF + 16-Bit ADC with 95MHz Single-Tone Input Sampling at 130MSPS

Table 4. Analysis of FFT for THS770012 + BPF + 16-Bit ADC at 95MHz vs Typical ADC Specifications

| CONFIGURATION               | ADC INPUT | SNR      | HD2     | HD3     |  |

|-----------------------------|-----------|----------|---------|---------|--|

| THS770012 + BPF + 16Bit ADC | -1dBFS    | 74.4dBFS | -101dBc | -101dBc |  |

| 16-Bit ADC Only (typ)       | -1dBFS    | 75.2dBFS | -100dBc | -100dBc |  |

uments Incorporated Submit Documentation Feedback

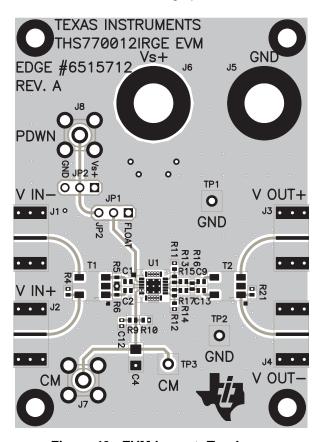

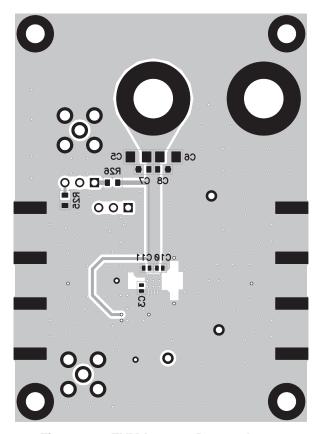

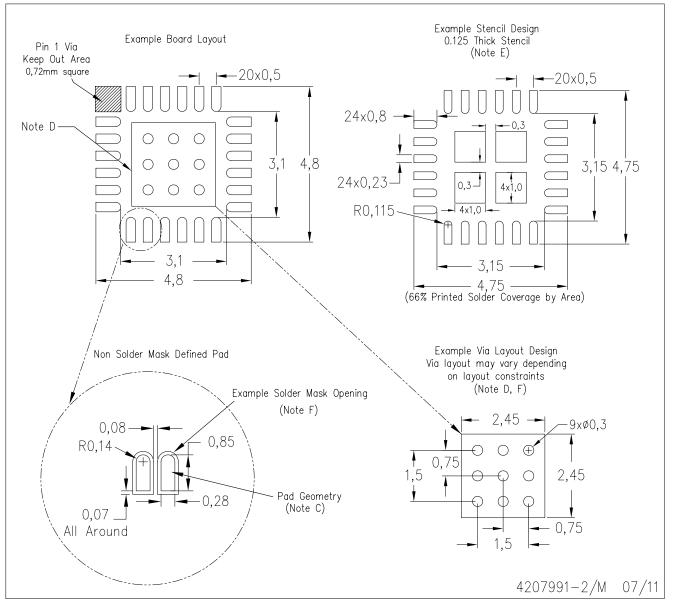

#### **EVM AND LAYOUT RECOMMENDATIONS**

Figure 37 is the THS770012RGE EVM schematic, and Figure 43 through Figure 46 show the layout details of the EVM PCB. Table 5 is the bill of materials for the EVM as supplied from TI. It is recommended to follow the layout of the external components as close as possible to the amplifier, ground plane construction, and power routing. General layout guidelines are:

- 1. Place a 2.2μF to 10μF capacitor on each supply pin within 2 inches from the device. It can be shared among other op amps.

- 2. Place a 0.01μF to 0.1μF capacitor on each supply pin to ground as close as possible to the device. Placement within 1mm of the device supply pins ensures best performance.

- 3. Keep output traces as short as possible to minimize parasitic capacitance and inductance. Doing so reduces unwanted characteristics such as peaking in the frequency response, overshoot, and ringing in the pulse response, and results in a more stable design.

- 4. To reduce parasitic capacitance, ground plane and power-supply planes should be removed from device output pins.

- The V<sub>OCM</sub> pin must be biased to a voltage between 2.25V to 2.75V for proper operation. Place a 0.1μF to