# MULTI-PROTOCOL FULLY INTEGRATED 13.56-MHz RFID READER/WRITER IC

Check for Samples: TRF7960A

#### Introduction 1

#### **Features** 1.1

- **Completely Integrated Protocol Handling for** ISO15693, ISO18000-3, ISO14443A/B, NFC Forum Device Types 1 to 4, and FeliCa

- Input Voltage Range: 2.7 VDC to 5.5 VDC

- **Programmable Output Power:** +20 dBm (100 mW) or +23 dBm (200 mW)

- Programmable I/O Voltage Levels: 1.8 VDC to 5.5 VDC

- **Programmable System Clock Frequency** Output (RF, RF/2, RF/4)

- **Programmable Modulation Depth**

- 1.2 Applications

- **Secure Access Control**

- Product Authentication

- **Contactless Payment Systems**

- Passport Reader Systems

- **Medical Systems**

- **Remote Sensor Applications**

#### 1.3 Description

- Dual Receiver Architecture With RSSI for Elimination of "Read Holes" and Adjacent Reader System/Ambient In-Band Noise Detection

- Programmable Power Modes for Ultra-Low • Power System Design (Power Down <0.5 µA)

- · Parallel or SPI Interface

- Integrated Voltage Regulator for Microcontroller Supply

- Temperature Range: -40°C to 110°C

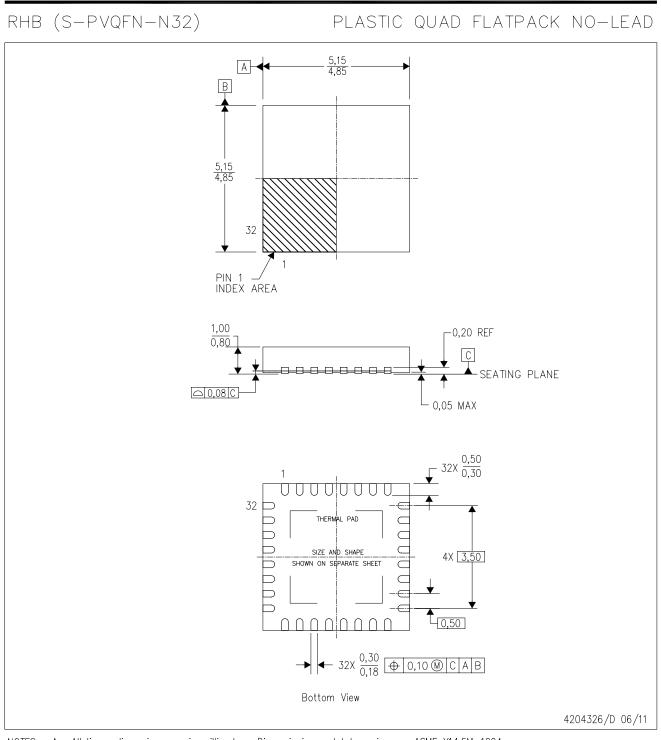

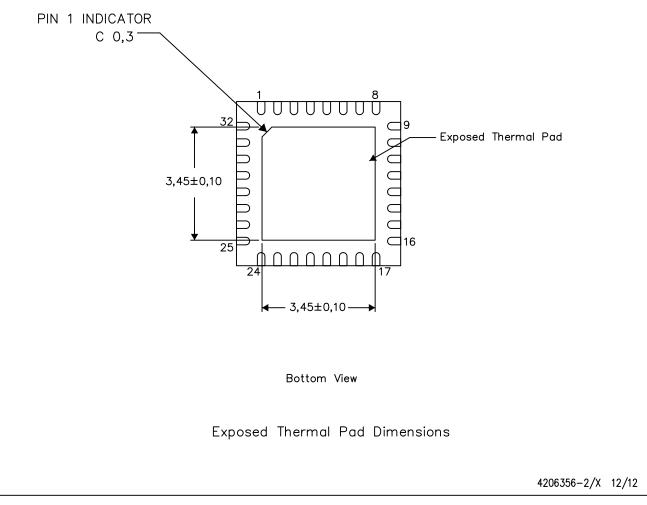

- 32-Pin QFN Package (5 mm x 5 mm) (RHB)

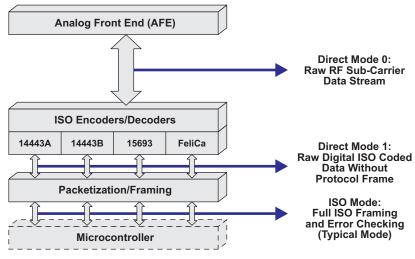

The TRF7960A is an integrated analog front end and data-framing device for a 13.56-MHz RFID reader/writer system. Built-in programming options make it suitable for a wide range of applications for proximity and vicinity identification systems.

The reader is configured by selecting the desired protocol in the control registers. Direct access to all control registers allows fine tuning of various reader parameters as needed.

Comprehensive documentation, reference designs, evaluation modules, and TI microcontrollers (based on MSP430<sup>™</sup> or ARM<sup>™</sup> technology) source code are available.

The TRF7960A is a high-performance 13.56-MHz HF RFID reader IC comprising an integrated analog front end (AFE) and a built-in data framing engine for ISO15693, ISO14443A/B, and FeliCa. It supports data rates up to 848 kbps for ISO14443 with all framing and synchronization tasks on board (in ISO Mode, default). The TRF7960A also supports NFC Forum Tag Types 1, 2, 3, and 4 operations (as reader/writer only). This architecture enables the customer to build a complete and cost-effective yet high-performance multiprotocol HF RFID/NFC reader/writer using a low-cost microcontroller (for example, an MSP430).

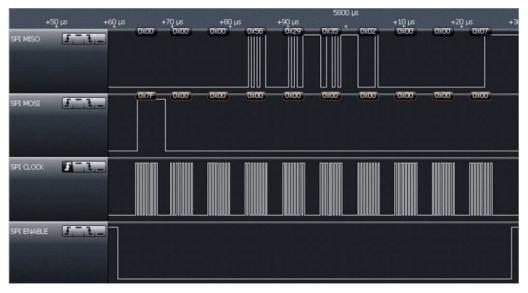

Other standards and even custom protocols can be implemented by using two of the Direct Modes the device offers. These Direct Modes (0 and 1) allow the user to fully control the analog front end (AFE) and also gain access to the raw subcarrier data or the unframed, but already ISO formatted data and the associated (extracted) clock signal.

ÆΑ

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. MSP430 is a trademark of Texas Instruments. ARM is a trademark of ARM Limited.

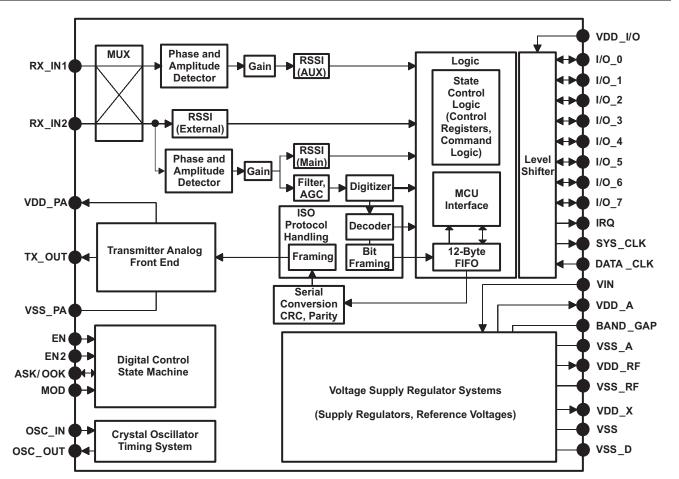

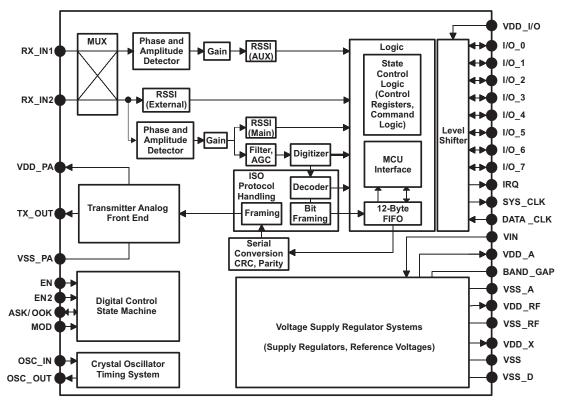

Figure 1-1. Block Diagram

The receiver system has a dual-input receiver architecture. The receivers also include various automatic and manual gain control options. The received input bandwidth can be selected to cover a broad range of input subcarrier signal options.

The received signal strength from transponders, ambient sources or internal levels is available via the RSSI register. The receiver output is selectable among a digitized subcarrier signal and any of the integrated subcarrier decoders. The selected subcarrier decoder delivers the data bit stream and the data clock as outputs.

The TRF7960A includes a receiver framing engine. This receiver framing engine performs the CRC and/or parity check, removes the EOF and SOF settings, and organizes the data in bytes for ISO14443A/B, ISO15693, and NFC Forum protocols. Framed data is then accessible to the microcontroller (MCU) via a 12-byte FIFO register.

A parallel or serial interface (SPI) can be used for the communication between the MCU and the TRF7960A reader. When the built-in hardware encoders and decoders are used, transmit and receive functions use a 12-byte FIFO register. For direct transmit or receive functions, the encoders or decoders can be bypassed so the MCU can process the data in real time. The TRF7960A supports data communication levels from 1.8 V to 5.5 V for the MCU I/O interface. The transmitter has selectable output power levels of 100 mW (+20 dBm) or 200 mW (+23 dBm) equivalent into a 50- $\Omega$  load when using a 5-V supply.

2 Introduction

www.ti.com

SLOS732C – JUNE 2011 – REVISED JANUARY 2013

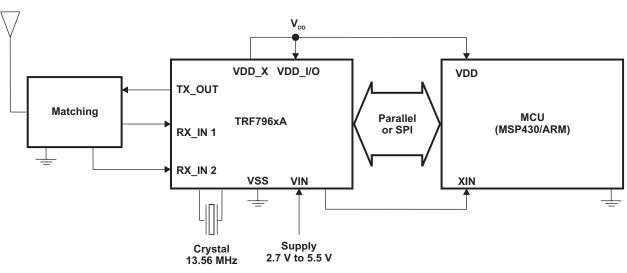

### Figure 1-2. Application Block Diagram

The transmitter supports OOK and ASK modulation with selectable modulation depth. The TRF7960A includes a data transmission engine that supports low-level encoding for ISO15693 and modified Miller encoding for ISO14443A/B and FeliCa. Included with the transmit data coding is the automatic generation of Start Of Frame (SOF), End Of Frame (EOF), Cyclic Redundancy Check (CRC), and parity bits. Several integrated voltage regulators ensure a proper power-supply noise rejection for the complete reader system. The built-in programmable auxiliary voltage regulator VDD\_X (pin 32) delivers up to 20 mA to supply a microcontroller and additional external circuits within the reader system.

| Table 1-1. Supported Prot | ocols |

|---------------------------|-------|

|---------------------------|-------|

|          |          |          | S        | upported Protoco | ols      |            |              |  |

|----------|----------|----------|----------|------------------|----------|------------|--------------|--|

| Device   |          | ISO14    | 443A/B   |                  | 18015602 | ISO18000-3 | NFC Forum    |  |

|          | 106 kbps | 212 kbps | 424 kbps | 848 kbps         | ISO15693 | Mode 1     | Types 1 to 4 |  |

| TRF7960A | √        | 1        | 1        | 1                | 1        | 1          | 1            |  |

## **1.4 Ordering Information**

| Packaged Devices <sup>(1)</sup> | Package Type <sup>(2)</sup> | Transport Media | Quantity |

|---------------------------------|-----------------------------|-----------------|----------|

| TRF7960ARHBT                    |                             | Tana and Deal   | 250      |

| TRF7960ARHBR                    | RHB-32                      | Tape and Reel   | 3000     |

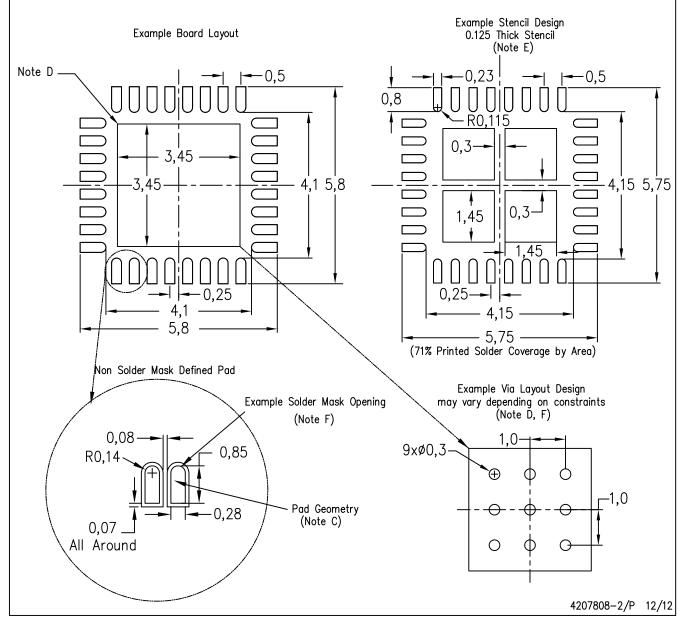

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

(2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at <a href="http://www.ti.com/sc/package">www.ti.com/sc/package</a>.

# **TRF7960A**

SLOS732C - JUNE 2011 - REVISED JANUARY 2013

| 1 | Intro | duction <u>1</u>                                                   |

|---|-------|--------------------------------------------------------------------|

|   | 1.1   | Features <u>1</u>                                                  |

|   | 1.2   | Applications <u>1</u>                                              |

|   | 1.3   | Description <u>1</u>                                               |

|   | 1.4   | Ordering Information 3                                             |

| 2 | Phys  | ical Characteristics 5                                             |

|   | 2.1   | Device Pinout <u>5</u>                                             |

|   | 2.2   | Terminal Functions5                                                |

| 3 | Elect | rical Characteristics7                                             |

|   | 3.1   | Absolute Maximum Ratings 7                                         |

|   | 3.2   | Dissipation Ratings 7                                              |

|   | 3.3   | Recommended Operating Conditions 7                                 |

|   | 3.4   | Electrical Characteristics                                         |

|   | 3.5   | Switching Characteristics                                          |

| 4 |       | ication Schematic and Layout<br>siderations                        |

|   | 4.1   | TRF7960A Reader System Using Parallel<br>Microcontroller Interface |

|   | 4.2   | TRF7960A Reader System Using SPI With SS<br>Mode                   |

| 5 | Detai | led System Description $\frac{12}{12}$                             |

Submit Documentation Feedback Product Folder Links: TRF7960A

#### www.ti.com

|     | 5.1    | System Block Diagram                                         | <u>12</u> |

|-----|--------|--------------------------------------------------------------|-----------|

|     | 5.2    | Power Supplies                                               | <u>12</u> |

|     | 5.3    | Supply Arrangements                                          | <u>12</u> |

|     | 5.4    | Supply Regulator Settings                                    | <u>14</u> |

|     | 5.5    | Power Modes                                                  | <u>15</u> |

|     | 5.6    | Receiver - Analog Section                                    | <u>17</u> |

|     | 5.7    | Receiver - Digital Section                                   | <u>18</u> |

|     | 5.8    | Oscillator Section                                           | <u>21</u> |

|     | 5.9    | Transmitter - Analog Section                                 | <u>22</u> |

|     | 5.10   | Transmitter - Digital Section                                | <u>23</u> |

|     | 5.11   | Transmitter – External Power Amplifier / Subcarrier detector | 24        |

|     | 5.12   | TRF7960A Communication Interface                             | <u>24</u> |

|     | 5.13   | Direct Commands from MCU to Reader                           | 42        |

| 6   |        | ster Description                                             | 46        |

|     | 6.1    | Register Overview                                            | 46        |

| 7   | Syste  | em Design                                                    | 63        |

|     | 7.1    | Layout Considerations                                        | 63        |

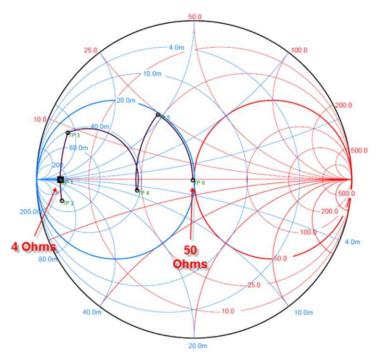

|     | 7.2    | Impedance Matching TX_Out (Pin 5) to 50 $\Omega$             | 63        |

|     | 7.3    | Reader Antenna Design Guidelines                             | 64        |

| Rev | vision | History                                                      | 65        |

|     |        |                                                              |           |

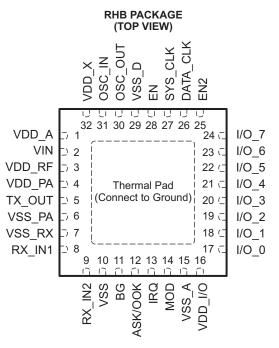

## 2 Physical Characteristics

## 2.1 Device Pinout

## 2.2 Terminal Functions

**Table 2-1. Terminal Functions**

| Terminal |           | Type <sup>(1)</sup> | Description                                                                                                                                                             |  |

|----------|-----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name     | No.       | Type 🗘              | Description                                                                                                                                                             |  |

| VDD_A    | 1         | OUT                 | Internal regulated supply (2.7 V to 3.4 V) for analog circuitry                                                                                                         |  |

| VIN      | 2         | SUP                 | External supply input to chip (2.7 V to 5.5 V)                                                                                                                          |  |

| VDD_RF   | 3         | OUT                 | Internal regulated supply (2.7 V to 5 V); normally connected to VDD_PA (pin 4)                                                                                          |  |

| VDD_PA   | 4         | INP                 | Supply for PA; normally connected externally to VDD_RF (pin 3)                                                                                                          |  |

| TX_OUT   | 5         | OUT                 | RF output (selectable output power: 100 mW or 200 mW, with $V_{DD} = 5 \text{ V}$ )                                                                                     |  |

| VSS_PA   | 6         | SUP                 | Negative supply for PA; normally connected to circuit ground                                                                                                            |  |

| VSS_RX   | 7         | SUP                 | Negative supply for receive inputs; normally connected to circuit ground                                                                                                |  |

| RX_IN1   | 8         | INP                 | Main receive input                                                                                                                                                      |  |

| RX_IN2   | 9         | INP                 | Auxiliary receive input                                                                                                                                                 |  |

| VSS      | 10        | SUP                 | Chip substrate ground                                                                                                                                                   |  |

| BAND_GAP | 11        | OUT                 | Bandgap voltage (V <sub>BG</sub> = 1.6 V); internal analog voltage reference                                                                                            |  |

| ASK/OOK  | 12        | BID                 | Selection between ASK and OOK modulation (0 = ASK, 1 = OOK) for Direct Mode 0 and 1.<br>It can be configured as an output to provide the received analog signal output. |  |

| IRQ      | 13        | OUT                 | Interrupt request                                                                                                                                                       |  |

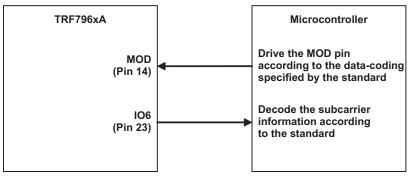

| MOD      |           | INP                 | External data modulation input for Direct Mode 0 or 1                                                                                                                   |  |

| MOD      | OD 14 OUT |                     | Subcarrier digital data output (see register 0x1A and 0x1B definitions)                                                                                                 |  |

| VSS_A    | 15        | SUP                 | Negative supply for internal analog circuits; connected to GND                                                                                                          |  |

| VDD_I/O  | 16        | INP                 | Supply for I/O communications (1.8 V to VIN) level shifter. VIN should be never exceeded.                                                                               |  |

(1) SUP = Supply, INP = Input, BID = Bidirectional, OUT = Output

Copyright © 2011–2013, Texas Instruments Incorporated

SLOS732C – JUNE 2011 – REVISED JANUARY 2013

www.ti.com

## Table 2-1. Terminal Functions (continued)

| Termin   | al  | - (1)               |                                                                                                                                                                                                                                  |

|----------|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | No. | Type <sup>(1)</sup> | Description                                                                                                                                                                                                                      |

| I/O_0    | 17  | BID                 | I/O pin for parallel communication                                                                                                                                                                                               |

| I/O_1    | 18  | BID                 | I/O pin for parallel communication                                                                                                                                                                                               |

| I/O_2    | 19  | BID                 | I/O pin for parallel communication                                                                                                                                                                                               |

| I/O_3    | 20  | BID                 | I/O pin for parallel communication                                                                                                                                                                                               |

| I/O_4    | 21  | BID                 | I/O pin for parallel communication<br>Slave select signal in SPI mode                                                                                                                                                            |

| I/O_5    | 22  | BID                 | I/O pin for parallel communication<br>Data clock output in Direct Mode 1                                                                                                                                                         |

| I/O_6    | 23  | BID                 | I/O pin for parallel communication<br>MISO for serial communication (SPI)<br>Serial bit data output in Direct Mode 1 or subcarrier signal in Direct Mode 0                                                                       |

| I/O_7    | 24  | BID                 | I/O pin for parallel communication.<br>MOSI for serial communication (SPI)                                                                                                                                                       |

| EN2      | 25  | INP                 | Selection of power down mode. If EN2 is connected to VIN, then VDD_X is active during power down mode 2 (for example, to supply the MCU).                                                                                        |

| DATA_CLK | 26  | INP                 | Data clock input for MCU communication (parallel and serial)                                                                                                                                                                     |

| SYS_CLK  | 27  | OUT                 | If EN = 1 (EN2 = don't care) the system clock for the MCU is configured with register 0x09 (off, $3.39 \text{ MHz}$ , $6.78 \text{ MHz}$ , or $13.56 \text{ MHz}$ ).<br>If EN = 0 and EN2 = 1, the system clock is set to 60 kHz |

| EN       | 28  | INP                 | Chip enable input (If EN = 0, then the chip is in sleep or power-down mode)                                                                                                                                                      |

| VSS_D    | 29  | SUP                 | Negative supply for internal digital circuits                                                                                                                                                                                    |

| OSC_OUT  | 30  | OUT                 | Crystal or oscillator output                                                                                                                                                                                                     |

| OSC_IN   | 31  | INP                 | Crystal or oscillator input                                                                                                                                                                                                      |

| VDD_X    | 32  | OUT                 | Internally regulated supply (2.7 V to 3.4 V) for digital circuit and external devices (for example, an MCU)                                                                                                                      |

| PAD      | PAD | SUP                 | Chip substrate ground                                                                                                                                                                                                            |

SLOS732C – JUNE 2011 – REVISED JANUARY 2013

www.ti.com

## **3** Electrical Characteristics

## 3.1 Absolute Maximum Ratings <sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted) (2)

|                  |                                                    | ,                                           |                |

|------------------|----------------------------------------------------|---------------------------------------------|----------------|

| VIN              | Input voltage range                                |                                             | -0.3 V to 6 V  |

| I <sub>IN</sub>  | Maximum current                                    |                                             | 150 mA         |

| ESD              | Electrostatic discharge rating                     | Human-body model (HBM)                      | 2 kV           |

|                  |                                                    | Charged-device model (CDM)                  | 500 V          |

|                  |                                                    | Machine model (MM)                          | 200 V          |

| TJ               | Maximum operating virtual junction temperature (3) | Any condition                               | 140°C          |

|                  |                                                    | Continuous operation, long-term reliability | 125°C          |

| T <sub>STG</sub> | Storage temperature range                          | *                                           | -55°C to 150°C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to substrate ground terminal VSS.

(3) The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device.

## 3.2 Dissipation Ratings

| PACKAGE  | ٥      | ο (1)    | POWER F                                          | RATING <sup>(2)</sup> |  |

|----------|--------|----------|--------------------------------------------------|-----------------------|--|

|          | PIC    | OJA(*)   | $T_A \le 25^{\circ}C \qquad T_A \le 85^{\circ}C$ |                       |  |

| RHB (32) | 31°C/W | 36.4°C/W | 2.7 W                                            | 1.1 W                 |  |

(1) This data was taken using the JEDEC standard high-K test PCB.

(2) Power rating is determined with a junction temperature of 125°C. This is the point where distortion starts to increase substantially. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and longterm reliability.

## 3.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                        | MIN | TYP | MAX | UNIT |

|----------------|----------------------------------------|-----|-----|-----|------|

| VIN            | Operating input voltage                | 2.7 | 5   | 5.5 | V    |

| T <sub>A</sub> | Operating ambient temperature          | -40 | 25  | 110 | °C   |

| TJ             | Operating virtual junction temperature | -40 | 25  | 125 | °C   |

STRUMENTS

EXAS

## 3.4 Electrical Characteristics

TYP operating conditions are  $T_A = 25^{\circ}$ C, VIN = 5 V, full-power mode (unless otherwise noted)

MIN and MAX operating conditions are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       | PARAMETER                                                                        | CONDITIONS                                                                                                                         | MIN | TYP   | MAX              | UNIT             |

|-----------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------|------------------|

| I <sub>PD1</sub>      | Supply current in Power Down Mode 1                                              | All building blocks disabled, including supply-<br>voltage regulators; measured after 500-ms<br>settling time (EN = 0, EN2 = 0)    |     | <0.5  | 5                | μA               |

| I <sub>PD2</sub>      | Supply current in Power Down Mode 2<br>(Sleep Mode)                              | The SYS_CLK generator and VDD_X remain active to support external circuitry, measured after 100-ms settling time (EN = 0, EN2 = 1) |     | 120   | 200              | μA               |

| I <sub>STBY</sub>     | Supply current in stand-by mode                                                  | Oscillator running, supply-voltage regulators in low-consumption mode (EN = 1, EN2 = $x$ )                                         |     | 1.9   | 3.5              | mA               |

| I <sub>ON1</sub>      | Supply current without antenna driver<br>current                                 | Oscillator, regulators, RX, and AGC are active, TX is off                                                                          |     | 10.5  | 14               | mA               |

| I <sub>ON2</sub>      | Supply current – TX (half power)                                                 | Oscillator, regulators, RX, AGC, and TX active, $P_{OUT} = 100 \text{ mW}$                                                         |     | 70    | 78               | mA               |

| I <sub>ON3</sub>      | Supply current – TX (full power)                                                 | Oscillator, regulators, RX, AGC, and TX active, $P_{OUT} = 200 \text{ mW}$                                                         |     | 130   | 170              | mA               |

| V <sub>POR</sub>      | Power-on reset voltage                                                           | Input voltage at VIN                                                                                                               | 1.4 | 2     | 2.6              | V                |

| V <sub>BG</sub>       | Bandgap voltage (pin 11)                                                         | Internal analog reference voltage                                                                                                  | 1.5 | 1.6   | 1.7              | V                |

| VDD_A                 | Regulated output voltage for analog circuitry (pin 1)                            | VIN = 5 V                                                                                                                          | 3.1 | 3.5   | 3.8              | V                |

| VDD_X                 | Regulated supply for external circuitry                                          | Output voltage pin 32, VIN = 5 V                                                                                                   | 3.1 | 3.4   | 3.8              | V                |

| I <sub>VDD Xmax</sub> | Maximum output current of VDD_X                                                  | Output current pin 32, VIN = 5 V                                                                                                   |     |       | 20               | mA               |

| D                     | A                                                                                | Half power mode, VIN = 2.7 V to 5.5 V                                                                                              |     | 8     | 12               | Ω                |

| R <sub>RFOUT</sub>    | Antenna driver output resistance <sup>(1)</sup>                                  | Full power mode, VIN = 2.7 V to 5.5 V                                                                                              |     | 4     | 6                | Ω                |

| R <sub>RFIN</sub>     | RX_IN1 and RX_IN2 input resistance                                               |                                                                                                                                    | 4   | 10    | 20               | kΩ               |

| V <sub>RF_INmax</sub> | Maximum RF input voltage at RX_IN1, RX_IN2                                       | V <sub>RF_INmax</sub> should not exceed VIN                                                                                        |     | 3.5   |                  | V <sub>pp</sub>  |

| V <sub>RF_INmin</sub> | Minimum RF input voltage at RX_IN1,<br>RX_IN2 (input sensitivity) <sup>(2)</sup> | f <sub>SUBCARRIER</sub> = 424 kHz                                                                                                  |     | 1.4   | 2.5              | mV <sub>pp</sub> |

|                       |                                                                                  | f <sub>SUBCARRIER</sub> = 848 kHz                                                                                                  |     | 2.1   | 3                | mV <sub>pp</sub> |

| f <sub>SYS_CLK</sub>  | SYS_CLK frequency                                                                | In power mode 2, $EN = 0$ , $EN2 = 1$                                                                                              | 25  | 60    | 120              | kHz              |

| f <sub>C</sub>        | Carrier frequency                                                                | Defined by external crystal                                                                                                        |     | 13.56 |                  | MHz              |

| t <sub>CRYSTAL</sub>  | Crystal run-in time                                                              | Time until oscillator stable bit is set (register 0x0F) $^{(3)}$                                                                   |     | 5     |                  | ms               |

| f <sub>D_CLKmax</sub> | Maximum DATA_CLK frequency (4)                                                   | Depends on capacitive load on the I/O lines, recommendation is 2 MHz $^{\rm (4)}$                                                  | 2   | 8     | 10               | MHz              |

| V <sub>IL</sub>       | Input voltage, logic low                                                         | I/O lines, IRQ, SYS_CLK, DATA_CLK, EN, EN2                                                                                         |     |       | 0.2 ×<br>VDD_I/O | V                |

| V <sub>IH</sub>       | Input voltage threshold, logic high                                              | I/O lines, IRQ, SYS_CLK, DATA_CLK, EN, EN2                                                                                         |     |       | 0.8 ×<br>VDD_I/O | V                |

| R <sub>OUT</sub>      | Output resistance, I/O_0 to I/O_7                                                |                                                                                                                                    |     | 500   | 800              | Ω                |

| R <sub>SYS_CLK</sub>  | Output resistance R <sub>SYS_CLK</sub>                                           |                                                                                                                                    |     | 200   | 400              | Ω                |

(1) Antenna driver output resistance

(2) Measured with subcarrier signal at RX\_IN1/2 and measured the digital output at MOD pin with register 0x1A bit 6 = 1

(3) Depending on the crystal parameters and components

(4) Recommended DATA\_CLK speed is 2 MHz; higher data clock depends on the capacitive load. Maximum SPI clock speed should not exceed 10 MHz. This clock speed is acceptable only when external capacitive load is less than 30 pF. MISO driver has a typical output resistance of 400 Ω (12-ns time constant when 30-pF load is used).

SLOS732C -JUNE 2011-REVISED JANUARY 2013

#### www.ti.com

## 3.5 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                           | CONDITIONS                                           | MIN | TYP  | MAX | UNIT |

|-----------------------|---------------------------------------------------------------------|------------------------------------------------------|-----|------|-----|------|

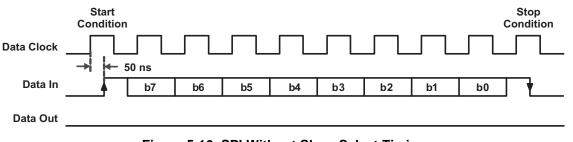

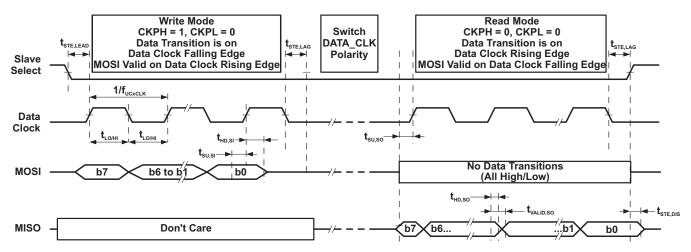

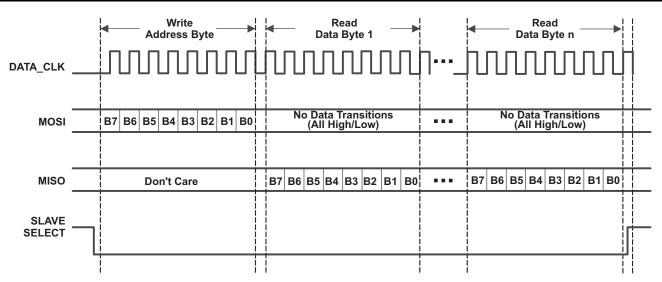

| t <sub>LO/HI</sub>    | DATA_CLK time, high or low (one half of DATA_CLK at 50% duty cycle) | Depends on capacitive load on the I/O lines $^{(1)}$ | 50  | 62.5 | 250 | ns   |

| t <sub>STE,LEAD</sub> | Slave select lead time, slave select low to clock                   |                                                      |     | 200  |     | ns   |

| t <sub>STE,LAG</sub>  | Slave select lag time, last clock to slave select high              |                                                      |     | 200  |     | ns   |

| t <sub>SU,SI</sub>    | MOSI input data setup time                                          |                                                      | 15  |      |     | ns   |

| t <sub>HD,SI</sub>    | MOSI input data hold time                                           |                                                      | 15  |      |     | ns   |

| t <sub>SU,SO</sub>    | MISO input data setup time                                          |                                                      | 15  |      |     | ns   |

| t <sub>HD,SO</sub>    | MISO input data hold time                                           |                                                      | 15  |      |     | ns   |

| t <sub>VALID,SO</sub> | MISO output data valid time                                         | DATA_CLK edge to MISO valid, $C_L = <30 \text{ pF}$  | 30  | 50   | 75  | ns   |

(1) Recommended DATA\_CLK speed is 2 MHz; higher data clock depends on the capacitive load. Maximum SPI clock speed should not exceed 10 MHz. This clock speed is acceptable only when external capacitive load is less than 30 pF. MISO driver has a typical output resistance of 400 Ω (12-ns time constant when 30-pF load is used).

# 4 Application Schematic and Layout Considerations

# 4.1 TRF7960A Reader System Using Parallel Microcontroller Interface

# 4.1.1 General Application Considerations

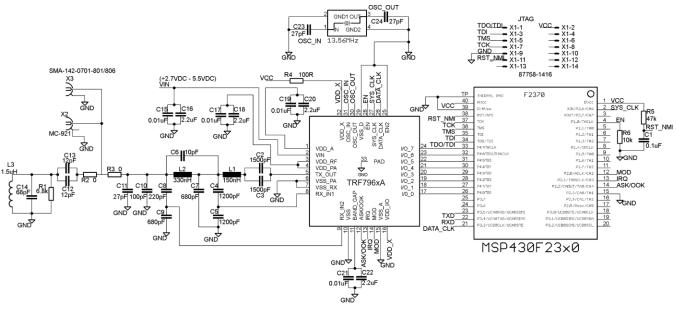

Figure 4-1 shows the most flexible TRF7960A application. Both ISO15693 and ISO14443 systems can be addressed. Due to the low clock frequency on the DATA\_CLK line, the parallel interface is the most robust way to connect the TRF7960A with the MCU.

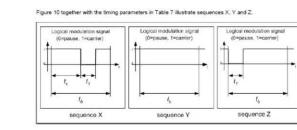

This schematic shows matching to a  $50-\Omega$  port, which allows connection to a properly matched  $50-\Omega$  antenna circuit or RF measurement equipment (for example, a spectrum analyzer or power meter).

# 4.1.2 Schematic

Figure 4-1 shows a sample application schematic with a parallel interface to the MCU.

Figure 4-1. Application Schematic, Parallel MCU Interface

The MSP430F2370 (32kB flash, 2kB RAM) is shown in Figure 4-1. Minimum MCU requirements depend on application requirements and coding style. If only one ISO protocol and/or a limited command set of a protocol must be supported, MCU flash and RAM requirements can be significantly reduced. Note that recursive inventory and anticollision commands require more RAM than single slotted operations. For example, current reference firmware for ISO15693 (with host interface) is approximately 8kB, using 512B RAM and for all supported protocols (also with same host interface) the reference firmware is approximately 12kB, using a minimum of 1kB RAM. An MCU that is capable of running a GPIO at 13.56 MHz is required for Direct Mode 0 operations with nonstandard transponders.

## 4.2 TRF7960A Reader System Using SPI With SS Mode

### 4.2.1 General Application Considerations

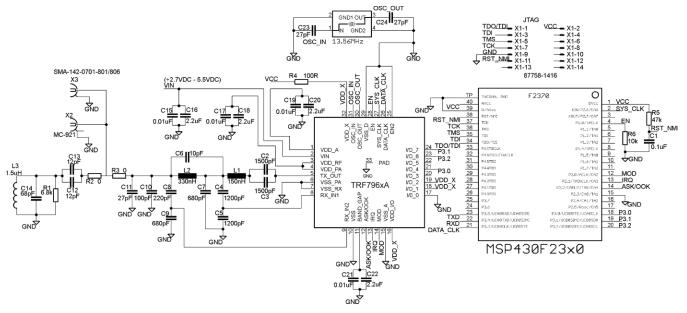

Figure 4-2 shows the TRF7960A application schematic optimized for both ISO15693 and ISO14443 systems using the Serial Port Interface (SPI). Short SPI lines, proper isolation to radio frequency lines, and a proper ground area are essential to avoid interference. The recommended clock frequency on the DATA\_CLK line is 2 MHz.

This schematic shows matching to a 50- $\Omega$  port, which allows connection to a properly matched 50- $\Omega$  antenna circuit or RF measurement equipment (for example, a spectrum analyzer or power meter).

### 4.2.2 Schematic

Figure 4-2 shows a sample application schematic with a serial interface to the MCU.

Figure 4-2. Application Schematic, SPI With SS Mode MCU Interface

The MSP430F2370 (32kB flash, 2kB RAM) is shown in Figure 4-2. Minimum MCU requirements depend on application requirements and coding style. If only one ISO protocol and/or a limited command set of a protocol must be supported, MCU flash and RAM requirements can be significantly reduced and user should be aware that recursive inventory/anticollision commands require more RAM than single slotted operations. For example, current reference firmware for ISO15693 (with host interface) is approximately 8kB, using 512B RAM and for all supported protocols (also with same host interface) the reference firmware is approximately 12kB, using minimum 1kB RAM. An MCU that is capable of running a GPIO at 13.56 MHz is required for Direct Mode 0 operations with nonstandard transponders.

ISTRUMENTS

**EXAS**

# 5 Detailed System Description

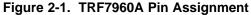

## 5.1 System Block Diagram

Figure 5-1. System Block Diagram

## 5.2 Power Supplies

The TRF7960A positive supply input VIN (pin 2) sources three internal regulators with output voltages VDD\_RF, VDD\_A, and VDD\_X. All regulators require external bypass capacitors for supply noise filtering and must be connected as indicated in reference schematics. These regulators provide a high power supply reject ratio (PSRR) as required for RFID reader systems. All regulators are supplied via VIN (pin 2).

The regulators are not independent and have common control bits in register 0x0B for output voltage setting. The regulators can be configured to operate in either automatic or manual mode (register 0x0B, bit 7). The automatic regulator setting mode ensures an optimal compromise between PSRR and the highest possible supply voltage for RF output (to ensure maximum RF power output). The manual mode allows the user to manually configure the regulator settings.

## 5.3 Supply Arrangements

## **Regulator Supply Input: VIN**

The positive supply at VIN (pin 2) has an input voltage range of 2.7 V to 5.5 V. VIN provides the supply input sources for three internal regulators with the output voltages VDD\_RF, VDD\_A, and VDD\_X. External bypass capacitors for supply noise filtering must be used (per reference schematics).

**NOTE** VIN must be the highest voltage supplied to the TRF7960A.

#### RF Power Amplifier Regulator: VDD\_RF

The VDD\_RF (pin 3) regulator is supplying the RF power amplifier. The voltage regulator can be set for either 5V or 3V operation. External bypass capacitors for supply noise filtering must be used (per reference schematics). When configured for 5V manual-operation, the VDD\_RF output voltage can be set from 4.3 V to 5 V in 100-mV steps. In 3-V manual operation, the output can be programmed from 2.7 V to 3.4 V in 100-mV steps (see Table 5-2). The maximum output current capability for 5-V operation is 150 mA and for 3-V operation is 100 mA.

### Analog Supply Regulator: VDD\_A

Regulator VDD\_A (pin 1) supplies the analog circuits of the device. The output voltage setting depends on the input voltage and can be set for 5-V and 3-V operation. When configured for 5-V manual operation, the output voltage is fixed at 3.4 V. External bypass capacitors for supply noise filtering must be used (per reference schematics). When configured for 3-V manual operation, the VDD\_A output can be set from 2.7 V to 3.4 V in 100-mV steps (see Table 5-2).

### NOTE

The configuration of VDD\_A and VDD\_X regulators are not independent from each other. The VDD\_A output current should not exceed 20 mA.

### Digital Supply Regulator: VDD\_X

The Digital Supply Regulator VDD\_X (pin 32) provides the power for the internal digital building blocks and can also be used to supply external electronics within the reader system. When configured for 3-V operation, the output voltage can be set from 2.7 to 3.4 V in 100-mV steps. External bypass capacitors for supply noise filtering must be used (per reference schematics).

#### NOTE

The configuration of the VDD\_A and VDD\_X regulators are not independent from each other. The VDD\_X output current should not exceed 20 mA.

The RF power amplifier regulator (VDD\_RF), analog supply regulator (VDD\_A), and digital supply regulator (VDD\_X) can be configured to operate in either automatic or manual mode described in Table 5-1. The automatic regulator setting mode ensures an optimal compromise between PSRR and the highest possible supply voltage to ensure maximum RF power output.

By default, the regulators are set in automatic regulator setting mode. In this mode, the regulators are automatically set every time the system is activated by setting EN input High or each time the automatic regulator setting bit, B7 in register 0x0B is set to a 1. The action is started on the 0 to 1 transition. This means that, if the user wants to re-run the automatic setting from a state in which the automatic setting bit is already high, the automatic setting bit (B7 in register 0x0B) should be changed: 1-0-1.

By default, the regulator setting algorithm sets the regulator outputs to a "Delta Voltage" of 250 mV below VIN, but not higher than 5 V for VDD\_RF and 3.4 V for VDD\_A and VDD\_A. The "Delta Voltage" in automatic regulator mode can be increased up to 400 mV (for more details, see bits B0 to B2 in register 0x0B).

#### Power Amplifier Supply: VDD\_PA

The power amplifier of the TRF7960A is supplied through VDD\_PA (pin 4). The positive supply pin for the RF power amplifier is externally connected to the regulator output VDD\_RF (pin 3).

#### I/O Level Shifter Supply: VDD\_I/O

The TRF7960A has a separate supply input VDD\_I/O (pin 16) for the build in I/O level shifter. The supported input voltage ranges from 1.8 V to VIN, however not exceeding 5.5 V. Pin 16 is used to supply the I/O interface pins (I/O\_0 to I/O\_7), IRQ, SYS\_CLK, and DATA\_CLK pins of the reader. In typical applications, VDD\_I/O is directly connected to VDD\_X while VDD\_X also supplies the MCU. This ensures that the I/O signal levels of the MCU match with the logic levels of the TRF7960A.

## Negative Supply Connections: VSS, VSS\_RX, VSS\_A, VSS\_PA

The negative supply connections VSS\_X of each functional block are all externally connected to GND.

The substrate connection is VSS (pin 10), the analog negative supply is VSS\_A (pin 15), the logic negative supply is VSS\_D (pin 29), the RF output stage negative supply is VSS\_PA (pin 6), and the negative supply for the RF receiver VSS\_RX (pin 7).

### 5.4 Supply Regulator Settings

The input supply voltage mode of the reader must be selected. This is done in the Chip Status Control register (0x00). Bit 0 in register 0x00 selects between 5-V or 3-V input supply voltage. The default configuration is 5 V, which reflects an operating supply voltage range of 4.3 V to 5.5 V. If the supply voltage is below 4.3 V, the 3-V configuration should be used.

The various regulators can be configured to operate in automatic or manual mode. This is done in the

Regulator and I/O Control register (0x0B) as shown in Table 5-1.

| Register  | c       | Option Bi | its Settir | ng in Reg | gulator ( | Control F | Register | [1] | Commente                                      |

|-----------|---------|-----------|------------|-----------|-----------|-----------|----------|-----|-----------------------------------------------|

| Address   | B7      | B6        | B5         | B4        | B3        | B2        | B1       | B0  | Comments                                      |

| Automatic | Mode (d | efault)   |            |           |           |           |          |     |                                               |

| 0B        | 1       | х         | х          | х         | х         | х         | 1        | 1   | Automatic regulator setting 250-mV difference |

| 0B        | 1       | х         | х          | х         | х         | х         | 1        | 0   | Automatic regulator setting 350-mV difference |

| 0B        | 1       | х         | х          | х         | х         | х         | 0        | 0   | Automatic regulator setting 400-mV difference |

| Manual Mo | de      |           |            |           |           |           |          |     |                                               |

| 0B        | 0       | х         | х          | х         | х         | 1         | 1        | 1   | VDD_RF = 5 V, VDD_A = 3.4 V, VDD_X = 3.4 V    |

| 0B        | 0       | x         | х          | х         | х         | 1         | 1        | 0   | VDD_RF = 4.9 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

| 0B        | 0       | x         | х          | х         | х         | 1         | 0        | 1   | VDD_RF = 4.8 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

| 0B        | 0       | x         | х          | х         | х         | 1         | 0        | 0   | VDD_RF = 4.7 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

| 0B        | 0       | х         | х          | х         | х         | 0         | 1        | 1   | VDD_RF = 4.6 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

| 0B        | 0       | х         | х          | х         | х         | 0         | 1        | 0   | VDD_RF = 4.5 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

| 0B        | 0       | x         | х          | х         | х         | 0         | 0        | 1   | VDD_RF = 4.4 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

| 0B        | 0       | x         | х          | x         | x         | 0         | 0        | 0   | VDD_RF = 4.3 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |

Table 5-1. Supply Regulator Setting: 5-V System

(1) x = don't care

| Register    | c       | ption Bi | ts Settir | ng in Reg | gulator ( | Control F | Register | (1) | Commente                                      |  |  |  |

|-------------|---------|----------|-----------|-----------|-----------|-----------|----------|-----|-----------------------------------------------|--|--|--|

| Address     | B7      | B6       | B5        | B4        | B3        | B2        | B1       | B0  | Comments                                      |  |  |  |

| Automatic I | Node (d | efault)  |           |           |           |           |          |     |                                               |  |  |  |

| 0B          | 1       | х        | х         | х         | х         | х         | 1        | 1   | Automatic regulator setting 250-mV difference |  |  |  |

| 0B          | 1       | х        | х         | х         | х         | х         | 1        | 0   | Automatic regulator setting 350-mV difference |  |  |  |

| 0B          | 1       | x        | х         | х         | х         | х         | 0        | 0   | Automatic regulator setting 400-mV difference |  |  |  |

| Manual Mod  | le      |          |           |           |           |           |          |     |                                               |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 1         | 1        | 1   | VDD_RF = 3.4 V, VDD_A = 3.4 V, VDD_X = 3.4 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 1         | 1        | 0   | VDD_RF = 3.3 V, VDD_A = 3.3 V, VDD_X = 3.3 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 1         | 0        | 1   | VDD_RF = 3.2 V, VDD_A = 3.2 V, VDD_X = 3.2 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 1         | 0        | 0   | VDD_RF = 3.1 V, VDD_A = 3.1 V, VDD_X = 3.1 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 0         | 1        | 1   | VDD_RF = 3.0 V, VDD_A = 3.0 V, VDD_X = 3.0 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 0         | 1        | 0   | VDD_RF = 2.9 V, VDD_A = 2.9 V, VDD_X = 2.9 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 0         | 0        | 1   | VDD_RF = 2.8 V, VDD_A = 2.8 V, VDD_X = 2.8 V  |  |  |  |

| 0B          | 0       | х        | х         | х         | х         | 0         | 0        | 0   | VDD_RF = 2.7 V, VDD_A = 2.7 V, VDD_X = 2.7 V  |  |  |  |

## Table 5-2. Supply Regulator Setting: 3-V System

(1) x = don't care

The regulator configuration function adjusts the regulator outputs by default to 250 mV below VIN level, but not higher than 5 V for VDD\_RF, 3.4 V for VDD\_A and VDD\_X. This ensures the highest possible supply voltage for the RF output stage while maintaining an adequate PSRR (power supply rejection ratio).

To further improve the PSRR, it is possible to increase the target voltage difference across VDD\_X and VDD\_A from its default to 350 mV or even 400 mV (for details, see Regulator and I/O Control register 0x0B definition and Table 5-2.)

## 5.5 Power Modes

The chip has several power states, which are controlled by two input pins (EN and EN2) and several bits in the Chip Status Control register (0x00).

Table 5-3 is a consolidated table showing the configuration for the different power modes when using a 5-V or 3-V system supply. The main reader enable signal is pin EN. When EN is set high, all of the reader regulators are enabled, the 13.56-MHz oscillator is running and the SYS\_CLK (output clock for external microcontroller) is also available.

The Regulator Control register settings shown are for optimized power out. The automatic setting (normally 0x87) is optimized for best PSRR and noise reduction.

| Mode                              | EN2 | EN | Chip<br>Status<br>Control<br>Register<br>(0x00) | Regulator<br>Control<br>Register<br>(0x0B) | Trans-<br>mitter | Receiver | SYS_CLK<br>(13.56<br>MHz) | SYS_CLK<br>(60 kHz) | VDD_X | Typical<br>Current<br>(mA) | Typical<br>Power<br>Out<br>(dBm) | Time<br>(From<br>Previous<br>State) |

|-----------------------------------|-----|----|-------------------------------------------------|--------------------------------------------|------------------|----------|---------------------------|---------------------|-------|----------------------------|----------------------------------|-------------------------------------|

| Mode 4<br>(Full Power)<br>5 VDC   | x   | 1  | 21                                              | 07                                         | On               | On       | On                        | x                   | On    | 130                        | 23                               | ~20-25 µs                           |

| Mode 4<br>(Full Power)<br>3.3 VDC | x   | 1  | 20                                              | 07                                         | On               | On       | On                        | x                   | On    | 67                         | 18                               |                                     |

| Mode 3<br>(Half Power)<br>5 VDC   | x   | 1  | 31                                              | 07                                         | On               | On       | On                        | x                   | On    | 70                         | 20                               | ~20-25 µs                           |

| Mode 3<br>(Half Power)<br>3.3 VDC | x   | 1  | 30                                              | 07                                         | On               | On       | On                        | x                   | On    | 53                         | 15                               |                                     |

Table 5-3. Power Modes<sup>(1)</sup>

(1) x = don't care

Copyright © 2011–2013, Texas Instruments Incorporated

| SLOS732C – JUNE 2011 – REVISED JANUARY 2013 |

|---------------------------------------------|

|                                             |

|                         |     |    |                                                 |                                            |                  | mouco    |                           | nucuj               |       |                            |                                  |                                     |

|-------------------------|-----|----|-------------------------------------------------|--------------------------------------------|------------------|----------|---------------------------|---------------------|-------|----------------------------|----------------------------------|-------------------------------------|

| Mode                    | EN2 | EN | Chip<br>Status<br>Control<br>Register<br>(0x00) | Regulator<br>Control<br>Register<br>(0x0B) | Trans-<br>mitter | Receiver | SYS_CLK<br>(13.56<br>MHz) | SYS_CLK<br>(60 kHz) | VDD_X | Typical<br>Current<br>(mA) | Typical<br>Power<br>Out<br>(dBm) | Time<br>(From<br>Previous<br>State) |

| Mode 2<br>5 VDC         | х   | 1  | 03                                              | 07                                         | Off              | On       | On                        | x                   | On    | 10.5                       | _                                | ~20-25 µs                           |

| Mode 2<br>3.3 VDC       | x   | 1  | 02                                              | 00                                         | Off              | On       | On                        | x                   | On    | 9                          | _                                |                                     |

| Mode 1<br>5 VDC         | x   | 1  | 01                                              | 07                                         | Off              | Off      | On                        | x                   | On    | 5                          | _                                | ~20-25 µs                           |

| Mode 1<br>3.3 VDC       | х   | 1  | 00                                              | 00                                         | Off              | Off      | On                        | x                   | On    | 3                          |                                  |                                     |

| Standby Mode<br>5 VDC   | х   | 1  | 81                                              | 07                                         | Off              | Off      | On                        | x                   | On    | 3                          | —                                | 4.8 ms                              |

| Standby Mode<br>3.3 VDC | х   | 1  | 80                                              | 00                                         | Off              | Off      | On                        | x                   | On    | 2                          | —                                |                                     |

| Sleep Mode              | 1   | 0  | х                                               | х                                          | Off              | Off      | Off                       | On                  | On    | 0.120                      | _                                | 1.5 ms                              |

| Power Down              | 0   | 0  | х                                               | x                                          | Off              | Off      | Off                       | Off                 | Off   | <0.001                     | —                                | Start                               |

Table 5-3. Power Modes<sup>(1)</sup> (continued)

The input pin EN2 has two functions:

- A direct connection from EN2 to VIN to ensure the availability of the regulated supply VDD\_X and an auxiliary clock signal (60 kHz, SYS\_CLK) for an external MCU. This mode (EN = 0, EN2 = 1) is intended for systems in which the MCU is also being supplied by the reader supply regulator (VDD\_X) and the MCU clock is supplied by the SYS\_CLK output of the reader. This allows the MCU supply and clock to be available during sleep mode.

- EN2 enables the start-up of the reader system from complete power down (EN = 0, EN2 = 0). In this case, the EN input is being controlled by the MCU (or other system device) that is without supply voltage during complete power down (thus unable to control the EN input). A rising edge applied to the EN2 input (which has an approximately 1-V threshold level) starts the reader supply system and 13.56-MHz oscillator (identical to condition EN = 1).

When user MCU is controlling EN and EN2, a delay of 5 ms between EN and EN2 must be used. In cases where MCU is only controlling EN, EN2 is recommended to be connected to either VIN or GND, depending on the application MCU requirements/needs for VDD\_X and SYS\_CLK.

#### NOTE

Using EN=1 and EN2=1 in parallel at start up should not be done as it may cause incorrect operation.

This start-up mode lasts until all of the regulators have settled and the 13.56-MHz oscillator has stabilized. If the EN input is set high (EN = 1) by the MCU (or other system device), the reader stays active. If the EN input is not set high (EN = 0) within 100  $\mu$ s after the SYS\_CLK output is switched from auxiliary clock (60 kHz) to high-frequency clock (derived from the crystal oscillator), the reader system returns to complete Power-Down Mode 1. This option can be used to wake the reader system from complete Power Down (PD Mode 1) by using a pushbutton switch or by sending a single pulse.

After the reader EN line is high, the other power modes are selected by control bits within the Chip Status Control register (0x00). The power mode options and states are listed in Table 5-3.

When EN is set high (or on rising edge of EN2 and then confirmed by EN = 1) the supply regulators are activated and the 13.56-MHz oscillator started. When the supplies are settled and the oscillator frequency is stable, the SYS\_CLK output is switched from the auxiliary frequency of 60 kHz to the 13.56-MHz frequency derived from the crystal oscillator. At this time, the reader is ready to communicate and perform the required tasks. The MCU can then program the Chip Status Control register 0x00 and select the operation mode by programming the additional registers.

- Stand-by Mode (bit 7 = 1 of register 0x00), the reader is capable of recovering to full operation in 100  $\mu$ s.

- Mode 1 (active mode with RF output disabled, bit 5 = 0 and bit 1 = 0 of register 0x00) is a low-power mode that allows the reader to recover to full operation within  $25 \,\mu$ s.

- Mode 2 (active mode with only the RF receiver active, bit 1 = 1 of register 0x00) can be used to measure the external RF field (as described in RSSI measurements paragraph) if reader-to-reader anticollision is implemented.

- Mode 3 and Mode 4 (active modes with the entire RF section active, bit 5 = 1 of register 0x00) are the normal modes used for normal transmit and receive operations.

## 5.6 Receiver - Analog Section

## 5.6.1 Main and Auxiliary Receiver

The TRF7960A has two receiver inputs: RX\_IN1 (pin 8) and RX\_IN2 (pin 9). Each of the inputs is connected to an external capacitive voltage divider to ensure that the modulated signal from the tag is available on at least one of the two inputs. This architecture eliminates any possible communication holes that may occur from the tag to the reader.

The two RX inputs (RX\_IN1 and RX\_IN2) are multiplexed into two receivers-the main receiver and the auxiliary receiver. Only the main receiver is used for reception; the auxiliary receiver is used for signal quality monitoring. Receiver input multiplexing is controlled by bit B3 in the Chip Status Control register (address 0x00).

After startup, RX\_IN1 is multiplexed to the main receiver which is composed of an RF envelope detection, first gain and band-pass filtering stage, second gain and filtering stage with AGC. Only the main receiver is connected to the digitizing stage which output is connected to the digital processing block. The main receiver also has an RSSI measuring stage, which measures the strength of the demodulated signal (subcarrier signal).

The primary function of the auxiliary receiver is to monitor the RX signal quality by measuring the RSSI of the demodulated subcarrier signal (internal RSSI). After startup, RX\_IN2 is multiplexed to the auxiliary receiver. The auxiliary receiver has an RF envelope detection stage, first gain and filtering with AGC stage and finally the auxiliary RSSI block.

The default MUX setting is RX\_IN1 connected to the main receiver and RX\_IN2 connected to the auxiliary receiver. To determine the signal quality, the response from the tag is detected by the "main" (pin RX\_IN1) and "auxiliary" (pin RX\_IN2) RSSI. Both values measured and stored in the RSSI level register (address 0x0F). The MCU can read the RSSI values from the TRF7960A RSSI register and decide if swapping the input signals is preferable or not. Setting B3 in the Chip Status Control register (address 0x00) to 1 connects RX\_IN1 (pin 8) to the auxiliary receiver and RX\_IN2 (pin 9) to the main receiver. This mechanism must be used to avoid reading holes.

The main and auxiliary receiver input stages are RF envelope detectors. The RF amplitude at RX\_IN1 and RX\_IN2 should be approximately 3  $V_{PP}$  for a VIN supply level greater than 3.3 V. If the VIN level is lower, the RF input peak-to-peak voltage level should not exceed the VIN level.

## 5.6.2 Receiver Gain and Filter Stages

The first gain and filtering stage has a nominal gain of 15 dB with an adjustable band-pass filter. The band-pass filter has programmable 3-dB corner frequencies between 110 kHz to 450 kHz for the high-pass filter and between 570 kHz to 1500 kHz for the low-pass filter. After the band-pass filter, there is another gain-and-filtering stage with a nominal gain of 8 dB and with frequency characteristics identical to the first band-pass stage.

The internal filters are configured automatically depending on the selected ISO communication standard in the ISO Control register (address 0x01). If required, additional fine tuning can be done by writing directly to the RX special setting registers (address 0x0A).

TEXAS INSTRUMENTS

The main receiver also has a second receiver gain and digitizer stage which is included in the AGC loop. The AGC loop is activated by setting the bit B2 = 1 in the Chip Status Control register (address 0x00). When activated, the AGC continuously monitors the input signal level. If the signal level is significantly higher than an internal threshold level, gain reduction is activated.

By default, the AGC is frozen after the first four pulses of the subcarrier signal. This prevents the AGC from interfering with the reception of the remaining data packet. In certain situations, this "AGC freeze" is not optimal, so it can be removed by setting BO = 1 in the RX Special Setting register (address 0x0A).

Table 5-4 shows the various settings for the receiver analog section. It is important to note that setting B4, B5, B6, and B7 to 0 results in a band-pass characteristic of 240 kHz to 1.4 MHz, which is appropriate for ISO14443B 106 kbps, ISO14443A/B data-rates of 212 kbps and 424 kbps, and FeliCa 424 kbps.

| Bit | Function                                                                                       | Comments                                                                                                                                                                                                                                                                                                 |

|-----|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7  | Bandpass from 110 kHz to 570 kHz                                                               | Appropriate for any 212-kHz subcarrier systems like FeliCa                                                                                                                                                                                                                                               |

| B6  | Bandpass from 200 kHz to 900 kHz                                                               | Appropriate for 424-kHz subcarrier systems (for example, used in ISO15693).                                                                                                                                                                                                                              |

| B5  | Bandpass from 450 kHz to 1.5 MHz                                                               | Appropriate for Manchester-coded 106-kbps 848-kHz subcarrier systems (for example, used in ISO14443A).                                                                                                                                                                                                   |

| B4  | Bandpass from 100 kHz to 1.5 MHz                                                               | Appropriate for highest bit rate (848 kbps) used in high-bit-rate ISO14443B. Gain is reduced by 7 dB.                                                                                                                                                                                                    |

| B3  | 00 = no gain reduction                                                                         |                                                                                                                                                                                                                                                                                                          |

| B2  | 01 = gain reduction for 5 dB<br>10 = gain reduction for 10 dB<br>11 = gain reduction for 15 dB | Sets the RX digital gain reduction (changing the window of the digitizing comparator).                                                                                                                                                                                                                   |

| B1  | 0 = 5 times minimum digitizing level<br>1 = 3 times minimum digitizing level                   | AGC activation level change. From five times higher to the minimum RX digitizing level to three times the minimum digitizing level. The minimum RX digitizing level can be adjusted by B2 and B3 (gain reduction).                                                                                       |

| В0  | 0 = AGC freeze after 16 subcarrier edges<br>1 = AGC always on during receive                   | AGC action is not limited in time or to the start of receive. AGC action can be done<br>any time during receive process. The AGC can only increase and, hence, clips on<br>the peak RX level during the enable period. AGC level is reset automatically at the<br>beginning of each receive start frame. |

### Table 5-4. RX Special Setting Register (0x0A)

## 5.7 Receiver - Digital Section

The output of the TRF7960A analog receiver block is a digitized subcarrier signal and is the input to the digital receiver block. This block includes a Protocol Bit Decoder section and the Framing Logic section.

The protocol bit decoders convert the subcarrier coded signal into a serial bit stream and a data clock. The decoder logic is designed for maximum error tolerance. This enables the decoder section to successfully decode even partly corrupted subcarrier signals that otherwise would be lost due to noise or interference.

In the framing logic section, the serial bit stream data is formatted in bytes. Special signals such as the start of frame (SOF), end of frame (EOF), start of communication, and end of communication are automatically removed. The parity bits and CRC bytes are also checked and removed. This "clean" data is then sent to the 12-byte FIFO register where it can be read by the external microcontroller system. Providing the data this way, in conjunction with the timing register settings of the TRF7960A, means the firmware developer has to know about much less of the finer details of the ISO protocols to create a very robust application, especially in low-cost platforms where code space is at a premium and high performance is still required.

The start of the receive operation (successfully received SOF) sets the IRQ flags in the IRQ and Status register (0x0C). The end of the receive operation is signaled to the external system MCU by setting pin 13 (IRQ) high. If the receive data packet is longer than 8 bytes, an interrupt is sent to the MCU as the received data occupies 75% of the FIFO capacity. The data should be immediately removed from the FIFO.

Any error in the data format, parity, or CRC is detected and notified to the external system by an interrupt request pulse. The source condition of the interrupt request pulse is available in the IRQ Status register (0x0C). The main register controlling the digital part of the receiver is the ISO Control register (0x01). By writing to this register, the user selects the protocol to be used. With each new write in this register, the default presets are reloaded in all related registers, so no further adjustments in other registers are needed for proper operation.

#### NOTE

If register setting changes are needed for fine tuning the system, they must be done after setting the ISO Control register (0x01).

The framing section also supports the bit-collision detection as specified in ISO14443A (0x01). When a bit collision is detected, an interrupt request is sent and a flag is set in the IRQ and Status register (0x0C). The position of the bit collision is written in two registers: Collision Position register (0x0E) and partly in Collision Position and Interrupt Mask register (0x0D) (bits B6 and B7).

The collision position is presented as sequential bit number, where the count starts immediately after the start bit. This means a collision in the first bit of a UID would give the value 00 0001 0000 in these registers when their contents are combined after being read. (the count starts with 0 and the first 16 bits are the command code and the Number of Valid Bits (NVB) byte)

The receive section also includes two timers. The RX wait time timer is controlled by the value in the RX Wait Time register (0x08). This timer defines the time interval after the end of the transmit operation in which the receive decoders are not active (held in reset state). This prevents false detections resulting from transients following the transmit operation. The value of the RX Wait Time register (0x08) defines the time in increments of 9.44  $\mu$ s. This register is preset at every write to ISO Control register (0x01) according to the minimum tag response time defined by each standard.

The RX no response timer is controlled by the RX No Response Wait Time register (0x07). This timer measures the time from the start of slot in the anticollision sequence until the start of tag response. If there is no tag response in the defined time, an interrupt request is sent and a flag is set in the IRQ Status register (0x0C). This enables the external controller to be relieved of the task of detecting empty slots. The wait time is stored in the register in increments of 37.76  $\mu$ s. This register is also automatically preset for every new protocol selection.

## 5.7.1 Received Signal Strength Indicator (RSSI)

The TRF7960A incorporates in total three independent RSSI building blocks: Internal Main RSSI, Internal Auxiliary RSSI, and External RSSI. The internal RSSI blocks are measuring the amplitude of the subcarrier signal, and the external RSSI block measures the amplitude of the RF carrier signal at the receiver input.

## 5.7.1.1 Internal RSSI – Main and Auxiliary Receivers

Each receiver path has its own RSSI block to measure the envelope of the demodulated RF signal (subcarrier). Internal Main RSSI and Internal Auxiliary RSSI are identical except that they are connected to different RF input pins. The Internal RSSI is intended for diagnostic purposes to set the correct RX path conditions.

The Internal RSSI values can be used to adjust the RX gain settings and/or decide which RX path (main or auxiliary) provides the greater amplitude and, hence, to decide if the MUX may need to be reprogrammed to swap the RX input signal. The measuring system latches the peak value, so the RSSI level can be read after the end of each receive packet. The RSSI register values are reset with every transmission (TX) by the reader. This guarantees an updated RSSI measurement for each new tag response.

Copyright © 2011–2013, Texas Instruments Incorporated

SLOS732C - JUNE 2011 - REVISED JANUARY 2013

STRUMENTS

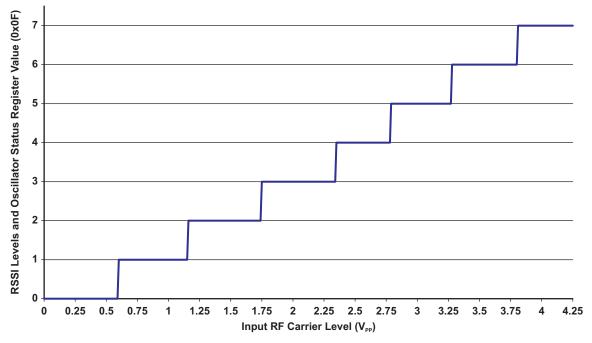

The Internal RSSI has 7 steps (3 bit) with a typical increment of about 4 dB. The operating range is between 600 mVp and 4.2 Vpp with a typical step size of about 600 mV. Both RSSI values "Internal Main" and "Internal Aux" RSSI are stored in the RSSI Levels and Oscillator Status register (0x0F).

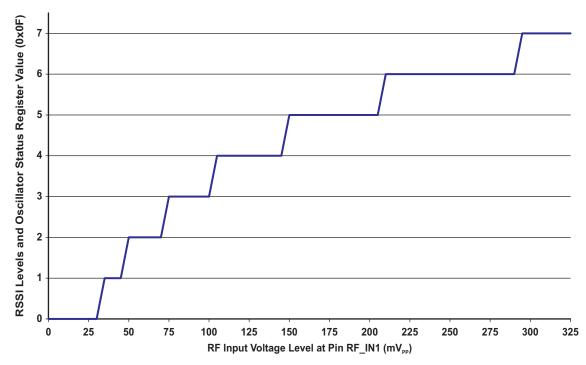

The nominal relationship between the input RF peak level and the RSSI value is shown in Figure 5-2.

Figure 5-2. Digital Internal RSSI (Main and Auxiliary) Value vs RF Input Level

This RSSI measurement is done during the communication to the Tag; this means the TX must be on. Bit 1 in the Chip Status Control register (0x00) defines if internal RSSI or the external RSSI value is stored in the RSSI Levels and Oscillator Status register 0x0F. Direct command 0x18 is used to trigger an internal RSSI measurement.

## 5.7.1.2 External RSSI

The external RSSI is mainly used for test and diagnostic in order to sense the amplitude of any 13.56-MHz signal at the receivers RX\_IN1 input. The external RSSI measurement is typically done in active mode when the receiver is on but transmitter output is off. The level of the RF signal received at the antenna is measured and stored in the RSSI Levels and Oscillator Status Register 0x0F.

The relationship between the voltage at the RX\_IN1 input and the 3-bit code is shown in Figure 5-3.

SLOS732C – JUNE 2011 – REVISED JANUARY 2013

Figure 5-3. Digital External RSSI Value vs RF Input Level

The relation between the 3-bit code and the external RF field strength (A/m) sensed by the antenna must be determined by calculation or by experiments for each antenna design. The antenna Q-factor and connection to the RF input influence the result. Direct command 0x19 is used to trigger an internal RSSI measurement.

To check the internal or external RSSI value independent of any other operation, the user must:

- 1. Set transmitter to desired state (on or off) using Bit 5 of Chip Status Control register (0x00)

- 2. Set the receiver using direct command 0x17.

- 3. Check internal or external RSSI using direct commands 0x18 or 0x19, respectively.

This action latches/places RSSI value in RSSI register

- 4. Read RSSI register using direct command 0x0F, values range from 0x40 to 0x7F.

- 5. Repeat steps 1-4 as desired, as register is reset after read.

## 5.8 Oscillator Section

The 13.56-MHz oscillator is controlled via the Chip Status Control register (0x00) and the EN and EN2 signals. The oscillator generates the RF frequency for the RF output stage and the clock source for the digital section. The buffered clock signal is available at pin 27 (SYS\_CLK) for external circuits. B4 and B5 inside the Modulation and SYS\_CLK register (0x09) can be used to divide the external SYS\_CLK signal at pin 27 by 1, 2, or 4.

Typical start-up time from complete power down is in the range of 3.5 ms.

During Power Down Mode 2 (EN = 0, EN2 = 1) the frequency of SYS\_CLK is switched to 60 kHz (typical).

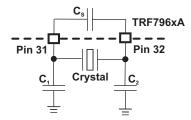

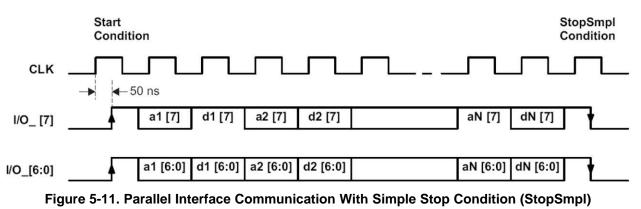

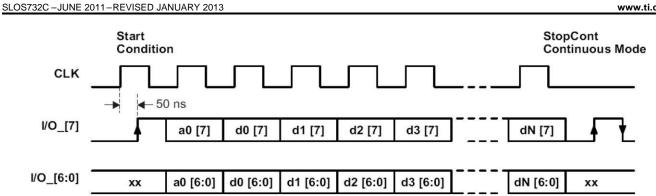

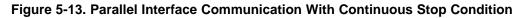

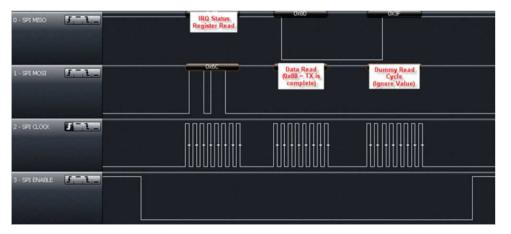

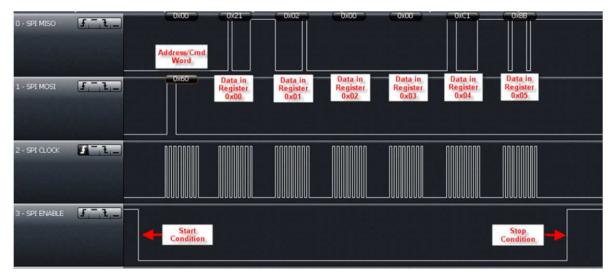

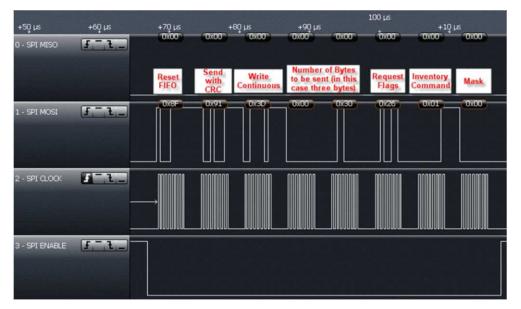

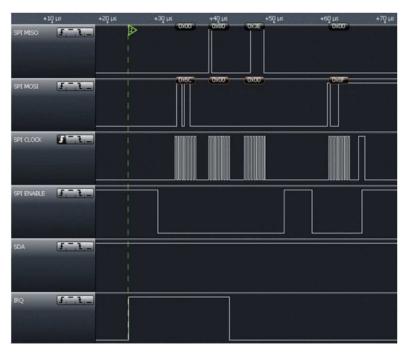

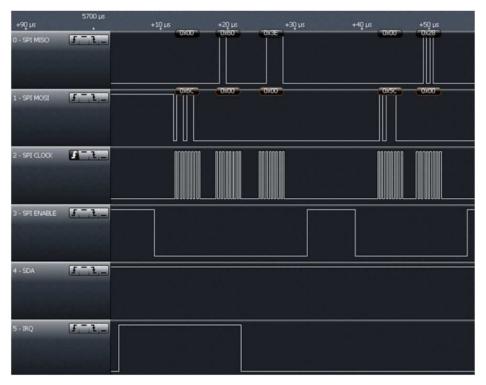

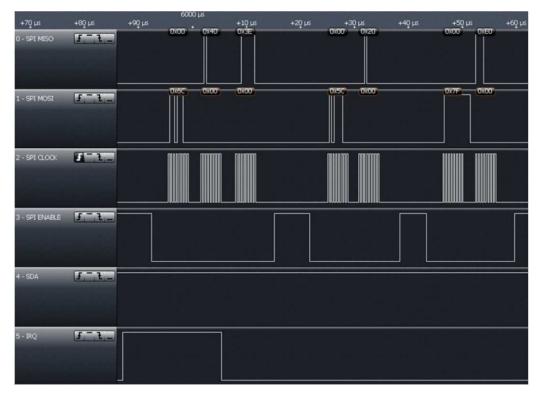

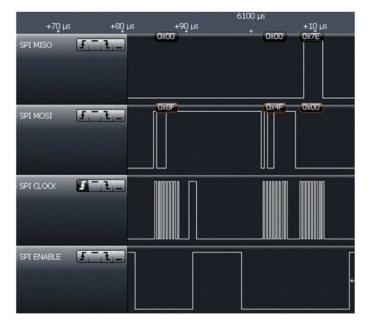

The 13.56-MHz crystal must be connected between pin 31 and pin 32. The external shunt capacitors values for  $C_1$  and  $C_2$  must be calculated based on the specified load capacitance of the crystal being used. The external shunt capacitors are calculated as two identical capacitors in series plus the stray capacitance of the TRF7960A and parasitic PCB capacitance in parallel to the crystal.