### **USB Charging Port Controller and Power Switch with Load Detection**

Check for Samples: TPS2543-Q1

#### **FEATURES**

- Qualified for Automotive Application

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: –40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level H2

- Device CDM ESD Classification Level C5

- D+/D- CDP/DCP Modes per USB Battery Charging Specification 1.2

- D+/D- Shorted Mode per Chinese Telecommunication Industry Standard YD/T 1591-2009

- Supports non-BC1.2 Charging Modes by Automatic Selection

- D+/D- Divider Modes 2.0V/2.7V and 2.7/2.0V

- Supports Sleep-Mode Charging and Low Speed Mouse/Keyboard Wake Up

- Load Detection for Power Supply Control in S4/S5 Charging and Port Power Management in all Charge Modes

- Compatible with USB 2.0 and 3.0 Power Switch requirements

- Integrated 73-mΩ (typ) High-Side MOSFET

- Adjustable Current-Limit up to 3 A (typ)

- Operating Range: 4.5 V to 5.5 V

- Max Device Current

- 2 µA When Device Disabled

- 260 µA When Device Enabled

- Drop-In and BOM Compatible with TPS2543

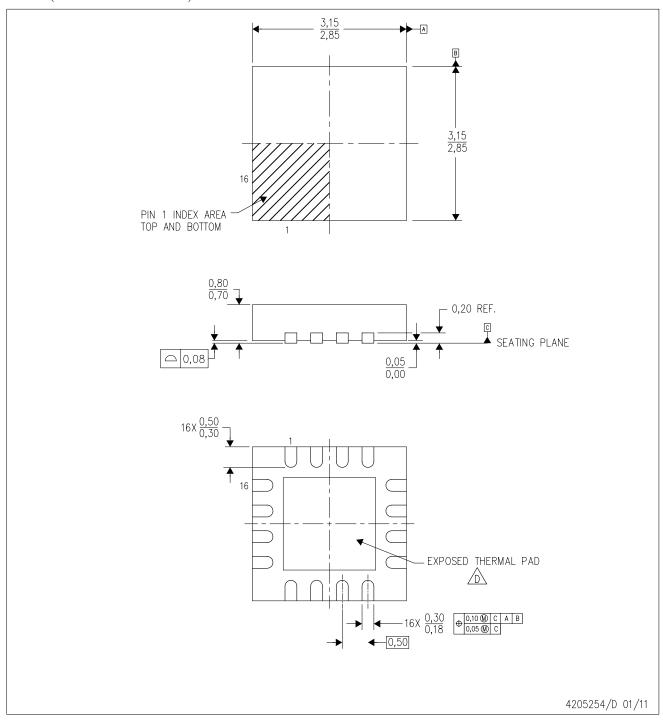

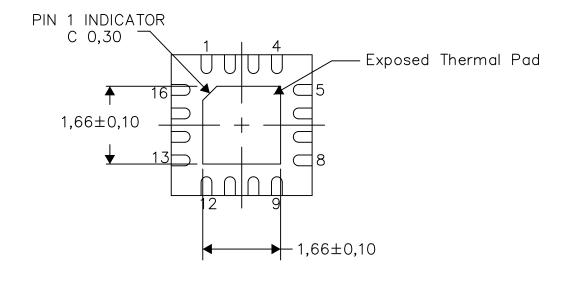

- Available in 16-Pin QFN (3x3) Package

- UL Listed and CB File No. E169910

#### **APPLICATIONS**

- USB Ports (Host and Hubs)

- Notebook and Desktop PCs

- Automotive Infotainment System

#### DESCRIPTION

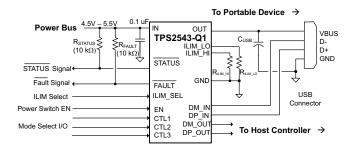

The TPS2543-Q1 is a USB charging port controller and power switch with an integrated USB 2.0 high-speed data line (D+/D-) switch. TPS2543-Q1 provides the electrical signatures on D+/D- lines to support charging schemes listed under device feature section. TI tests charging of popular mobile phones, tablets and media devices with the TPS2543-Q1 to ensure compatibility with both BC1.2 compliant and non-BC1.2 compliant devices

In addition to charging popular devices, the TPS2543-Q1 also supports two distinct power management features, namely, power wake and port power management (PPM) via the STATUS pin. Power wake allows for power supply control in S4/S5 charging and PPM the ability to manage port power in a multi-port applications. Additionally, system wake up (from S3) with a mouse/keyboard (low speed only) is also supported in the TPS2543-Q1

The TPS2543-Q1 73-m $\Omega$  power-distribution switch is intended for applications where heavy capacitive loads and short-circuits are likely to be encountered. Two programmable current thresholds provide flexibility for setting current limits and load detect thresholds.

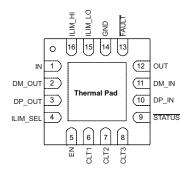

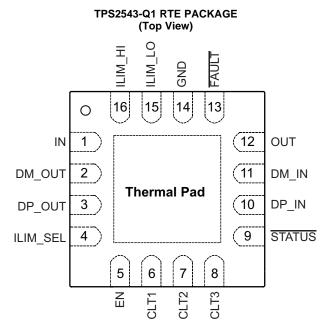

#### TPS2543-Q1 RTE PACKAGE AND TYPICAL APPLICATION DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TEXAS INSTRUMENTS

SLVSBW2 -MARCH 2013 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| $T_A = T_J$    | PACKAGE | DEVICE     | TOP-SIDE MARKING |

|----------------|---------|------------|------------------|

| -40°C to 125°C | QFN16   | TPS2543-Q1 | 2543Q            |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range, voltages are referenced to GND (unless otherwise noted)

|                                                |                                                                          | LIMIT                     | UNIT  |

|------------------------------------------------|--------------------------------------------------------------------------|---------------------------|-------|

|                                                | IN, EN, ILIM_LO, ILIM_HI, FAULT, STATUS, ILIM_SEL, CTL1, CTL2, CTL3, OUT | -0.3 to 7                 |       |

| Voltage range                                  | IN to OUT                                                                | -7 to 7                   | V     |

|                                                | DP_IN, DM_IN, DP_OUT, DM_OUT                                             | -0.3 to (IN + 0.3) or 5.7 |       |

| Input clamp current                            | DP_IN, DM_IN, DP_OUT, DM_OUT                                             | ±20                       | mA    |

| Continuous current in SDP or CDP mode          | DP_IN to DP_OUT or DM_IN to DM_OUT                                       | ±100                      | mA    |

| Continuous current in BC1.2 DCP mode           | DP_IN to DM_IN                                                           | ±50                       | mA    |

| Continuous output current                      | OUT                                                                      | Internally limited        |       |

| Continuous output sink current                 | FAULT, STATUS                                                            | 25                        | mA    |

| Continuous output source current               | ILIM_LO, ILIM_HI                                                         | Internally limited        | mA    |

| CCD rating                                     | НВМ                                                                      | 2000                      | V     |

| ESD rating                                     | CDM                                                                      | 500                       | \ \ \ |

| Operating junction temperature, T <sub>J</sub> |                                                                          | -40 to Internally limited | °C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                  |                                                             | TPS2543-Q1 |       |

|------------------|-------------------------------------------------------------|------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | RTE        | UNITS |

|                  |                                                             | 16 PINS    |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 53.4       |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 51.4       |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 17.2       | 9000  |

| ΨЈТ              | Junction-to-top characterization parameter (5)              | 3.7        | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 20.7       |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 3.9        |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### RECOMMENDED OPERATING CONDITIONS

voltages are referenced to GND (unless otherwise noted)

|                  |                                                                                         | MIN  | NOM | MAX      | UNIT |

|------------------|-----------------------------------------------------------------------------------------|------|-----|----------|------|

| V <sub>IN</sub>  | Input voltage, IN                                                                       | 4.5  |     | 5.5      | V    |

|                  | Input voltage, logic-level inputs, EN, CTL1, CTL2, CTL3, ILIM_SEL                       | 0    |     | 5.5      | V    |

|                  | Input voltage, data line inputs, DP_IN, DM_IN, DP_OUT, DM_OUT                           | 0    |     | $V_{IN}$ | V    |

| V <sub>IH</sub>  | High-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL                                | 1.8  |     |          | V    |

| $V_{IL}$         | Low-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL                                 |      |     | 0.8      | V    |

|                  | Continuous current, data line inputs, SDP or CDP mode, DP_IN to DP_OUT, DM_IN to DM_OUT |      |     | ±30      | mA   |

|                  | Continuous current, data line inputs, BC1.2 DCP mode, DP_IN to DM_IN                    |      |     | ±15      | mA   |

| I <sub>OUT</sub> | Continuous output current, OUT                                                          | 0    |     | 2.5      | Α    |

|                  | Continuous output sink current, FAULT, STATUS                                           | 0    |     | 10       | mA   |

| $R_{ILIM\_XX}$   | Current-limit set resistors                                                             | 16.9 |     | 750      | kΩ   |

| TJ               | Operating virtual junction temperature                                                  | -40  |     | 125      | °C   |

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5V \le V_{IN} \le 5.5 V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $\overline{_{FAULT}} = R \overline{_{STATUS}} = 10 \text{ k}\Omega$ ,  $R_{ILIM\_HI} = 20 \text{ k}\Omega$ ,  $R_{ILIM\_LO} = 80.6 \text{ k}\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

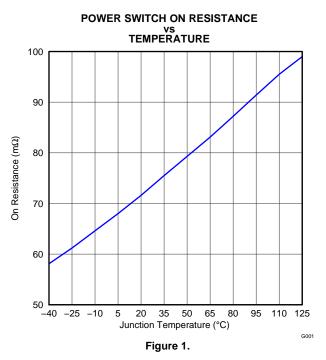

| PARAMETER           |                           | TEST CONDITIONS                                                                                                      | MIN      | TYP  | MAX  | UNIT      |

|---------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|----------|------|------|-----------|

| POWER               | SWITCH                    |                                                                                                                      | <u> </u> |      |      |           |

|                     |                           | $T_J = 25^{\circ}C$ , $I_{OUT} = 2 A$                                                                                |          | 73   | 84   |           |

| R <sub>DS(on)</sub> | On resistance (1)         | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}, \ \text{I}_{\text{OUT}} = 2 \text{ A}$          |          | 73   | 105  | $m\Omega$ |

|                     |                           | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C},  \text{I}_{\text{OUT}} = 2 \text{ A}$          |          | 73   | 120  |           |

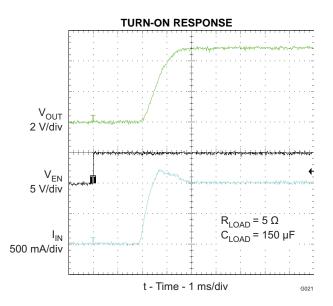

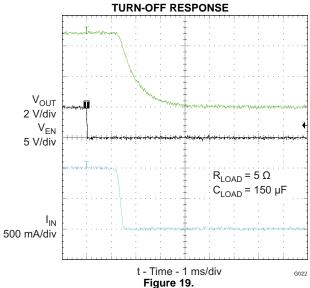

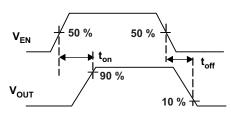

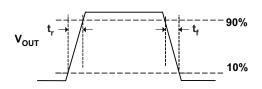

| t <sub>r</sub>      | OUT voltage rise time     | $V_{IN}$ = 5 V, $C_L$ = 1 μF, $R_L$ = 100 $\Omega$ (see Figure 23 and Figure 24)                                     |          | 1.0  | 1.60 |           |

| t <sub>f</sub>      | OUT voltage fall time     |                                                                                                                      |          | 0.35 | 0.5  | ms        |

| t <sub>on</sub>     | OUT voltage turn-on time  | $V_{IN}$ = 5V, $C_L$ = 1 $\mu$ F, $R_L$ = 100 $\Omega$ (see Figure 23 and                                            |          | 2.7  | 4    |           |

| t <sub>off</sub>    | OUT voltage turn-off time | Figure 25)                                                                                                           |          | 1.7  | 3    | ms        |

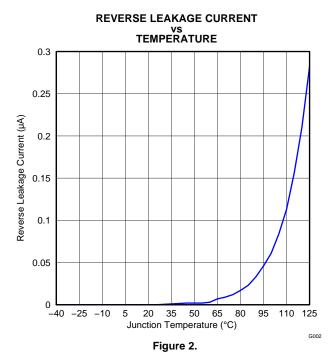

| I <sub>REV</sub>    | Reverse leakage current   | $V_{OUT} = 5.5 \text{ V}, V_{IN} = V_{EN} = 0 \text{ V}, -40 \le T_{J} \le 85^{\circ}\text{C},$<br>Measure $I_{OUT}$ |          |      | 2    | μΑ        |

| DISCHA              | RGE                       |                                                                                                                      |          |      |      |           |

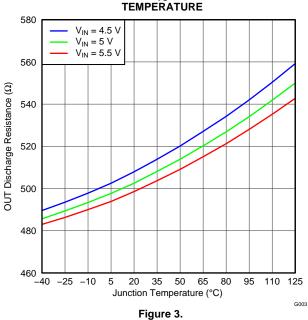

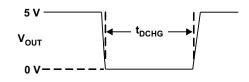

| R <sub>DCHG</sub>   | OUT discharge resistance  | V <sub>OUT</sub> = 4 V, V <sub>EN</sub> = 0 V                                                                        | 400      | 500  | 630  | Ω         |

| t <sub>DCHG</sub>   | OUT discharge hold time   | Time V <sub>OUT</sub> < 0.7 V (see Figure 26)                                                                        | 205      | 310  | 450  | ms        |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account separately.

Submit Documentation Feedback

#### **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5V \le V_{IN} \le 5.5 \text{ V}$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $_{\overline{FAULT}} = R$   $_{\overline{STATUS}} = 10$  k $\Omega$ ,  $R_{ILIM\_HI} = 20$  k $\Omega$ ,  $R_{ILIM\_LO} = 80.6$  k $\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                     | PARAMETER                                         | TEST CONDITIONS                                                                       | MIN  | TYP  | MAX  | UNIT |

|---------------------|---------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|

| EN, ILIM            | SEL, CTL1, CTL2, CTL3 INPUTS                      |                                                                                       |      |      |      |      |

|                     | Input pin rising logic threshold voltage          |                                                                                       | 1    | 1.35 | 1.70 | V    |

|                     | Input pin falling logic threshold voltage         |                                                                                       | 0.85 | 1.15 | 1.45 |      |

|                     | Hysteresis (2)                                    |                                                                                       |      | 200  |      | mV   |

|                     | Input current                                     | Pin voltage = 0 V or 5.5 V                                                            | -0.5 |      | 0.5  | μΑ   |

| ILIMSEL             | CURRENT LIMIT                                     |                                                                                       |      |      |      |      |

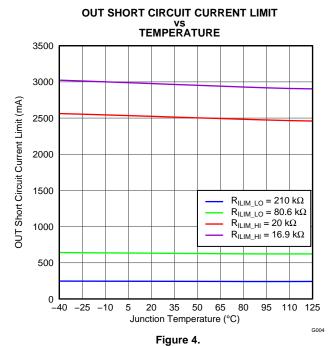

|                     |                                                   | $V_{ILIM\_SEL} = 0 \text{ V}, R_{ILIM\_LO} = 210 \text{ k}\Omega$                     | 205  | 240  | 275  |      |

|                     |                                                   | $V_{ILIM\_SEL} = 0 \text{ V}, R_{ILIM\_LO} = 80.6 \text{ k}\Omega$                    | 575  | 625  | 680  |      |

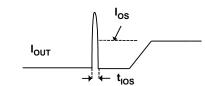

| Ios                 | OUT short circuit current limit (3)               | $V_{ILIM\_SEL} = 0 \text{ V}, R_{ILIM\_LO} = 22.1 \text{ k}\Omega$                    | 2120 | 2275 | 2430 | mA   |

|                     |                                                   | $V_{ILIM\_SEL} = V_{IN}, R_{ILIM\_HI} = 20 \text{ k}\Omega$                           | 2340 | 2510 | 2685 |      |

|                     |                                                   | $V_{ILIM\_SEL} = V_{IN}$ , $R_{ILIM\_HI} = 16.9 \text{ k}\Omega$                      | 2770 | 2970 | 3170 |      |

| t <sub>IOS</sub>    | Response time to OUT short-circuit <sup>(2)</sup> | $V_{IN} = 5.0 \text{ V}$ , R = 0.1 $\Omega$ , lead length = 2 inches (see Figure 27)  |      | 1.5  |      | μs   |

| SUPPLY              | CURRENT                                           | •                                                                                     |      |      | •    |      |

| I <sub>IN_OFF</sub> | Disabled IN supply current                        | $V_{EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}, -40 \le T_{J} \le 85^{\circ}\text{C}$   |      | 0.1  | 2    | μΑ   |

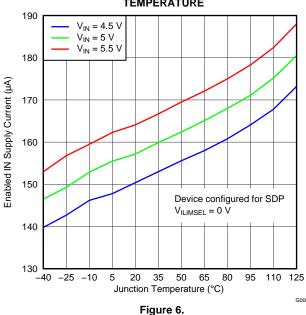

|                     |                                                   | $V_{CTL1} = V_{CTL2} = V_{IN}$ , $V_{CTL3} = 0$ V or $V_{IN}$ , $V_{ILIM\_SEL} = 0$ V |      | 155  | 210  |      |

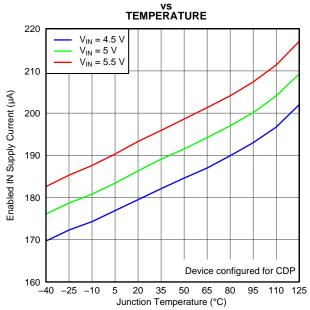

|                     | Enabled IN comply correct                         | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = 0V, V_{ILIM\_SEL} = V_{IN}$                 |      | 175  | 230  | μΑ   |

| I <sub>IN_ON</sub>  | Enabled IN supply current                         | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = VIN, V_{ILIM\_SEL} = V_{IN}$                |      | 185  | 240  |      |

|                     |                                                   | $V_{CTL1} = 0V$ , $V_{CTL2} = V_{CTL3} = V_{IN}$                                      |      | 205  | 260  |      |

| UNDER               | OLTAGE LOCKOUT                                    |                                                                                       | *    |      | •    |      |

| $V_{UVLO}$          | IN rising UVLO threshold voltage                  |                                                                                       | 3.9  | 4.1  | 4.3  | V    |

|                     | Hysteresis (2)                                    |                                                                                       |      | 100  |      | mV   |

| FAULT               |                                                   |                                                                                       |      |      |      |      |

|                     | Output low voltage                                | $I_{\overline{FAULT}} = 1 \text{ mA}$                                                 |      |      | 100  | mV   |

|                     | Off-state leakage                                 | V <sub>FAULT</sub> = 5.5 V                                                            |      |      | 1    | μΑ   |

|                     | Over current FAULT rising and falling deglitch    |                                                                                       | 5    | 8.2  | 12   | ms   |

| STATUS              |                                                   |                                                                                       |      |      |      |      |

|                     | Output low voltage                                | I STATUS = 1 mA                                                                       |      |      | 100  | mV   |

|                     | Off-state leakage                                 | V <sub>STATUS</sub> = 5.5 V                                                           |      |      | 1    | μΑ   |

| THERM               | AL SHUTDOWN                                       |                                                                                       |      |      | ,    |      |

|                     | Thermal shutdown threshold                        |                                                                                       | 155  |      |      |      |

|                     | Thermal shutdown threshold in current-limit       |                                                                                       | 135  |      |      | °C   |

|                     | Hysteresis (2)                                    |                                                                                       |      | 20   |      |      |

<sup>(2)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account

Copyright © 2013, Texas Instruments Incorporated

separately.

SLVSBW2 -MARCH 2013 www.ti.com

#### **ELECTRICAL CHARACTERISTICS, HIGH-BANDWIDTH SWITCH**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN} \le 5.5 \ V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $\overline{_{FAULT}} = R \overline{_{STATUS}} = 10 \ k\Omega$ ,  $R_{ILIM\_HI} = 20 \ k\Omega$ ,  $R_{ILIM\_LO} = 80.6 \ k\Omega$ , Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                              | PARAMETER                                                                      | TEST CONDITIONS                                                                                               | MIN | TYP  | MAX  | UNIT |  |  |

|------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|------|------|------|--|--|

| HIGH-BANDWIDTH ANALOG SWITCH |                                                                                |                                                                                                               |     |      |      |      |  |  |

|                              | DP/DM switch on resistance                                                     | $V_{DP/DM\_OUT} = 0 \text{ V}, I_{DP/DM\_IN} = 30 \text{ mA}$                                                 |     | 2    | 4    | Ω    |  |  |

|                              | DP/DIVI SWITCH OH TESISTATICE                                                  | $V_{DP/DM\_OUT} = 2.4 \text{ V}, I_{DP/DM\_IN} = -15 \text{ mA}$                                              |     | 3    | 6    | Ω    |  |  |

|                              | Switch resistance mismatch between                                             | $V_{DP/DM\_OUT} = 0 \text{ V}, I_{DP/DM\_IN} = 30 \text{ mA}$                                                 |     | 0.05 | 0.15 | Ω    |  |  |

|                              | DP / DM channels                                                               | $V_{DP/DM\_OUT} = 2.4 \text{ V}, I_{DP/DM\_IN} = -15 \text{ mA}$                                              |     | 0.05 | 0.15 | Ω    |  |  |

|                              | DP/DM switch off-state capacitance <sup>(1)</sup> , <sup>(2)</sup>             | $V_{EN} = 0 \text{ V}, V_{DP/DM\_IN} = 0.3 \text{ V}, V_{ac} = 0.6 \text{ V}_{pk-pk}, f = 1 \text{ MHz}$      |     | 3    |      | pF   |  |  |

|                              | DP/DM switch on-state capacitance (3), (2)                                     | $V_{DP/DM\_IN} = 0.3 \text{ V}, V_{ac} = 0.6 V_{pk-pk}, f = 1 \text{ MHz}$                                    |     | 5.4  |      | pF   |  |  |

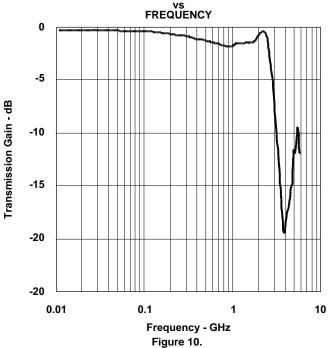

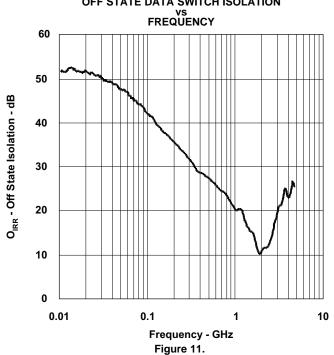

| O <sub>IRR</sub>             | Off-state isolation (2)                                                        | V <sub>EN</sub> = 0 V, f = 250 MHz                                                                            |     | 33   |      | dB   |  |  |

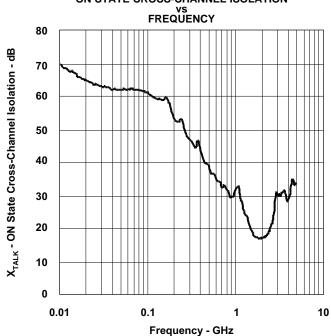

| X <sub>TALK</sub>            | On-state cross channel isolation (2)                                           | f = 250 MHz                                                                                                   |     | 52   |      | dB   |  |  |

|                              | Off state leakage current                                                      | $V_{EN} = 0 \text{ V}, V_{DP/DM\_IN} = 3.6 \text{ V}, V_{DP/DM\_OUT} = 0 \text{ V},$ measure $I_{DP/DM\_OUT}$ |     | 0.1  | 1.5  | μΑ   |  |  |

| BW                           | Bandwidth (-3dB) <sup>(2)</sup>                                                | R <sub>L</sub> = 50 Ω                                                                                         |     | 2.6  |      | GHz  |  |  |

| t <sub>pd</sub>              | Propagation delay <sup>(2)</sup>                                               |                                                                                                               |     | 0.25 |      | ns   |  |  |

| t <sub>SK</sub>              | Skew between opposite transitions of the same port $(t_{PHL} - t_{PLH})^{(2)}$ |                                                                                                               |     | 0.1  |      | ns   |  |  |

<sup>(1)</sup> The resistance in series with the parasitic capacitance to GND is typically 250  $\Omega$ .

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

<sup>(2)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

<sup>(3)</sup> The resistance in series with the parasitic capacitance to GND is typically 150  $\Omega$

#### **ELECTRICAL CHARACTERISTICS, CHARGING CONTROLLER**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN} \le 5.5 \ V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = 0 \ V$ ,  $V_{CTL2} = V_{CTL3} = V_{IN}$ . R  $_{\overline{FAULT}} = R _{\overline{STATUS}} = 10 \ k\Omega$ ,  $R_{ILIM\_HI} = 20 \ k\Omega$ ,  $R_{ILIM\_LO} = 80.6 \ k\Omega$ , Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                      | PARAMETER                                                                 | TEST CONDITIONS                                                                        | MIN  | TYP  | MAX  | UNIT |

|----------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| SHORTED              | MODE (BC1.2 DCP)                                                          | VCTL1 = VIN, VCTL2 = VCTL3 = 0V                                                        |      |      |      |      |

|                      | DP_IN / DM_IN shorting resistance                                         |                                                                                        |      | 125  | 200  | Ω    |

| DIVIDER1 N           | ODE                                                                       | •                                                                                      |      |      | •    |      |

|                      | DP_IN Divider1 output voltage                                             |                                                                                        | 1.9  | 2.0  | 2.1  | V    |

|                      | DM_IN Divider1 output voltage                                             |                                                                                        | 2.57 | 2.7  | 2.84 | V    |

|                      | DP_IN output impedance                                                    |                                                                                        | 8    | 10.5 | 12.5 | kΩ   |

|                      | DM_IN output impedance                                                    |                                                                                        | 8    | 10.5 | 12.5 | kΩ   |

| DIVIDER2 N           | IODE                                                                      | IOUT = 1A                                                                              |      |      | •    |      |

|                      | DP_IN Divider2 output voltage                                             |                                                                                        | 2.57 | 2.7  | 2.84 | V    |

| ·                    | DM_IN Divider2 output voltage                                             |                                                                                        | 1.9  | 2.0  | 2.1  | V    |

|                      | DP_IN output impedance                                                    |                                                                                        | 8    | 10.5 | 12.5 | kΩ   |

|                      | DM_IN output impedance                                                    |                                                                                        | 8    | 10.5 | 12.5 | kΩ   |

| CHARGING             | DOWNSTREAM PORT                                                           | VCTL1 = VCTL2 = VCTL3 = VIN                                                            |      |      | •    |      |

| V <sub>DM_SRC</sub>  | DM_IN CDP output voltage                                                  | $V_{DP_{-}IN} = 0.6 \text{ V},$<br>-250 $\mu\text{A} < I_{DM_{-}IN} < 0 \ \mu\text{A}$ | 0.5  | 0.6  | 0.7  | V    |

| V <sub>DAT_REF</sub> | DP_IN rising lower window threshold for V <sub>DM_SRC</sub> activation    |                                                                                        | 0.25 |      | 0.4  | V    |

|                      | Hysteresis (1)                                                            |                                                                                        |      | 50   |      | mV   |

| $V_{LGC\_SRC}$       | DP_IN rising upper window threshold for V <sub>DM_SRC</sub> de-activation |                                                                                        | 0.8  |      | 1    | V    |

|                      | hysteresis <sup>(1)</sup>                                                 |                                                                                        |      | 100  |      | mV   |

| I <sub>DP_SINK</sub> | DP_IN sink current                                                        | V <sub>DP_IN</sub> = 0.6 V                                                             | 40   | 70   | 100  | μΑ   |

| LOAD DETI            | ECT – NON POWER WAKE                                                      | VCTL1 = VCTL2 = VCTL3 = VIN                                                            |      |      |      |      |

| $I_{LD}$             | IOUT rising load detect current threshold                                 |                                                                                        | 635  | 700  | 765  | mA   |

|                      | hysteresis <sup>(1)</sup>                                                 |                                                                                        |      | 50   |      | mA   |

| t <sub>LD_SET</sub>  | Load detect set time                                                      |                                                                                        | 140  | 200  | 275  | ms   |

|                      | Load detect reset time                                                    |                                                                                        | 1.9  | 3    | 4.2  | s    |

| LOAD DETI            | ECT – POWER WAKE                                                          | VCTL1 = VCTL2 = 0V, VCTL3 = VIN                                                        |      |      |      |      |

| I <sub>OS_PW</sub>   | Power wake short circuit current limit                                    |                                                                                        | 32   | 55   | 78   | mA   |

|                      | I <sub>OUT</sub> falling power wake reset current detection threshold     |                                                                                        | 23   | 45   | 67   | mA   |

|                      | Reset current hysteresis <sup>(1)</sup>                                   |                                                                                        |      | 5    |      | mA   |

|                      | Power wake reset time                                                     |                                                                                        | 10.7 | 15   | 20.6 | S    |

|                      |                                                                           |                                                                                        |      |      |      |      |

<sup>(1)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

#### **TYPICAL CHARACTERISTICS**

#### **OUT DISCHARGE RESISTANCE** vs TEMPERATURE $V_{IN} = 4.5 \text{ V}$ $V_{IN} = 5 \text{ V}$ $V_{IN} = 5.5 \text{ V}$

### TYPICAL CHARACTERISTICS (continued) DISABLED IN SUPPLY CURRENT - SDP

#### vs TEMPERATURE 12 $V_{IN} = 5.5 \text{ V}$ 1 Disabled IN Supply Current (µA) 8.0 0.6 0.4 0.2 0 -20 60 80 -40 20 100 Junction Temperature (°C)

#### vs TEMPERATURE 190

Figure 5.

Figure 7.

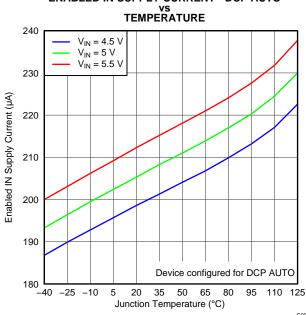

### **ENABLED IN SUPPLY CURRENT - DCP AUTO**

Figure 8.

Copyright © 2013, Texas Instruments Incorporated

SLVSBW2 -MARCH 2013 www.ti.com

TYPICAL CHARACTERISTICS (continued)

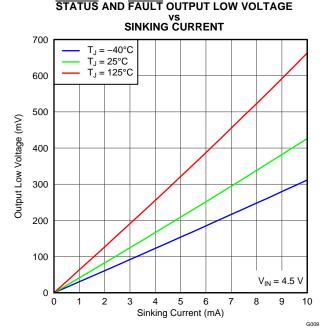

STATUS AND FAULT OUTPUT LOW VOLTAGE

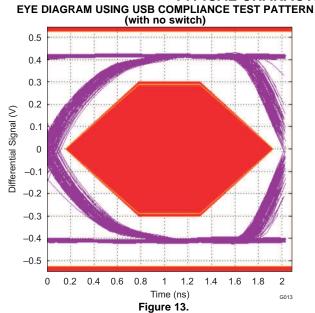

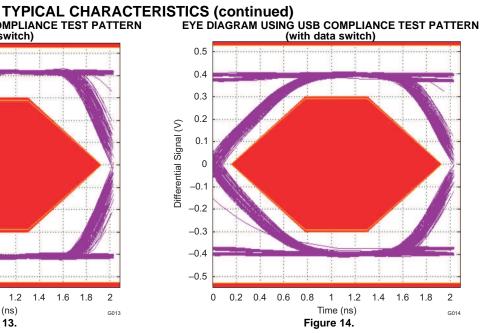

DATA TRANSMISSION CHARACTERISTICS

Figure 9.

#### ON STATE CROSS-CHANNEL ISOLATION

Figure 12.

Submit Documentation Feedback

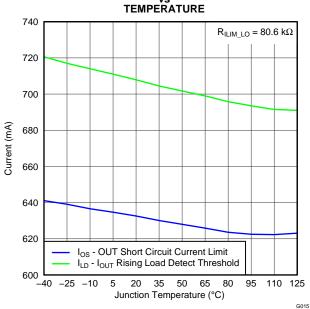

# I<sub>OUT</sub> RISING LOAD DETECT THRESHOLD AND OUT SHORT CIRCUIT CURRENT LIMIT VS TEMPERATURE

Figure 15.

SLVSBW2 -MARCH 2013 www.ti.com

## TEXAS INSTRUMENTS

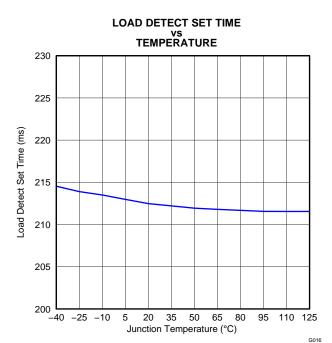

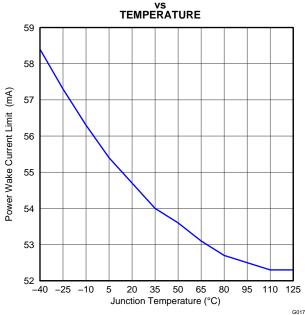

## TYPICAL CHARACTERISTICS (continued) POWER WAKE CURRENT LIMIT

Figure 17.

Figure 18.

#### PARAMETER MEASUREMENT DESCRIPTION

Figure 23. OUT Rise/Fall Test Load

Figure 25. Enable Timing, Active High Enable

Figure 24. Power-On and Off Timing

Figure 26. OUT Discharge During Mode Change

Figure 27. Output Short Circuit Parameters

Submit Documentation Feedback

#### **DEVICE INFORMATION**

#### PIN FUNCTIONS

|     |          | - 40                | PIN FUNCTIONS                                                                                                                                                                                                                         |  |  |  |  |  |

|-----|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO. | NAME     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                           |  |  |  |  |  |

| 1   | IN       | Р                   | Input voltage and supply voltage; connect 0.1 $\mu F$ or greater ceramic capacitor from IN to GND as close to the device as possible                                                                                                  |  |  |  |  |  |

| 2   | DM_OUT   | I/O                 | D– data line to USB host controller                                                                                                                                                                                                   |  |  |  |  |  |

| 3   | DP_OUT   | I/O                 | D+ data line to USB host controller                                                                                                                                                                                                   |  |  |  |  |  |

| 4   | ILIM_SEL | I                   | Logic-level input signal used to control the charging mode, current limit threshold, and load detection; see the control truth table. Can be tied directly to IN or GND without pull-up or pull-down resistor.                        |  |  |  |  |  |

| 5   | EN       | I                   | Logic-level input for turning the power switch and the signal switches on/off; logic low turns off the signal and power switches and holds OUT in discharge. Can be tied directly to IN or GND without pull-up or pull-down resistor. |  |  |  |  |  |

| 6   | CTL1     | 1                   |                                                                                                                                                                                                                                       |  |  |  |  |  |

| 7   | CTL2     | 1                   | Logic-level inputs used to control the charging mode and the signal switches; see the control truth to Can be tied directly to IN or GND without pull-up or pull-down resistor.                                                       |  |  |  |  |  |

| 8   | CTL3     | I                   | Can be used already to invest Grib without pain up of pain down resistor.                                                                                                                                                             |  |  |  |  |  |

| 9   | STATUS   | 0                   | Active-low open-drain output, asserted in load detection conditions                                                                                                                                                                   |  |  |  |  |  |

| 10  | DP_IN    | I/O                 | D+ data line to downstream connector                                                                                                                                                                                                  |  |  |  |  |  |

| 11  | DM_IN    | I/O                 | D– data line to downstream connector                                                                                                                                                                                                  |  |  |  |  |  |

| 12  | OUT      | Р                   | Power-switch output                                                                                                                                                                                                                   |  |  |  |  |  |

| 13  | FAULT    | 0                   | Active-low open-drain output, asserted during over-temperature or current limit conditions                                                                                                                                            |  |  |  |  |  |

| 14  | GND      | Р                   | Ground connection                                                                                                                                                                                                                     |  |  |  |  |  |

| 15  | ILIM_LO  | I                   | External resistor connection used to set the low current-limit threshold and the load detection current threshold. A resistor to ILIM_LO is optional; see Current-Limit Settings in DETAILED DESCRIPTION.                             |  |  |  |  |  |

| 16  | ILIM_HI  | 1                   | External resistor connection used to set the high current-limit threshold                                                                                                                                                             |  |  |  |  |  |

| NA  | PowerPAD |                     | Internally connected to GND; used to heat-sink the part to the circuit board traces. Connect to GND plane.                                                                                                                            |  |  |  |  |  |

<sup>(1)</sup> G = Ground, I = Input, O = Output, P = Power

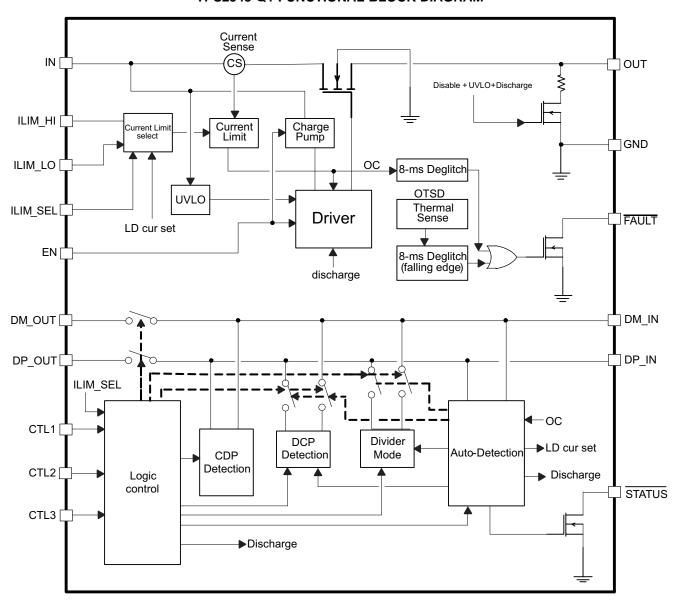

#### **TPS2543-Q1 FUNCTIONAL BLOCK DIAGRAM**

#### DETAILED DESCRIPTION

#### Overview

The following overview references various industry standards. It is always recommended to consult the most up-to-date standard to ensure the most recent and accurate information. Rechargeable portable equipment requires an external power source to charge its batteries. USB ports are a convenient location for charging because of an available 5V power source. Universally accepted standards are required to make sure host and client-side devices operate together in a system to ensure power management requirements are met. Traditionally, host ports following the USB 2.0 specification must provide at least 500mA to downstream client-side devices. Because multiple USB devices can be attached to a single USB port through a bus-powered hub, it is the responsibility of the client-side device to negotiate its power allotment from the host to ensure the total current draw does not exceed 500mA. In general, each USB device is granted 100mA and may request more current in 100mA unit steps up to 500mA. The host may grant or deny based on the available current. A USB 3.0 host port not only provides higher data rate than USB 2.0 port but also raises the unit load from 100mA to 150mA. It is also required to provide a minimum current of 900mA to downstream client-side devices.

Additionally, the success of USB has made the mini-USB connector a popular choice for wall adapter cables. This allows a portable device to charge from both a wall adapter and USB port with only one connector. As USB charging has gained popularity, the 500mA minimum defined by USB 2.0 or 900mA for USB 3.0 has become insufficient for many handset and personal media players which need a higher charging rate. Wall adapters can provide much more current than 500mA/900mA. Several new standards have been introduced defining protocol handshaking methods that allow host and client devices to acknowledge and draw additional current beyond the 500mA/900mA minimum defined by USB 2.0/3.0 while still using a single micro-USB input connector.

The TPS2543-Q1 supports three of the most common USB charging schemes found in popular hand-held media and cellular devices:

- USB Battery Charging Specification BC1.2

- Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider Mode

YD/T 1591-2009 is a subset of BC1.2 spec. supported by vast majority of devices that implement USB changing. Divider charging scheme is supported in devices from specific yet popular device maker.

BC1.2 lists three different port types as listed below.

- Standard Downstream Port (SDP)

- Charging Downstream Port (CDP)

- Dedicated Charging Port (DCP)

BC1.2 defines a charging port as a downstream facing USB port that provides power for charging portable equipment, under this definition CDP and DCP are defined as charging ports

Table 1 shows the differences between these ports.

**Table 1. Operating Modes**

| PORT TYPE     | SUPPORT USB<br>2.0 COMMUNICATION | MAX. ALLOWABLE CURRENT<br>DRAW BY PORTABLE DEVICE (A) |

|---------------|----------------------------------|-------------------------------------------------------|

| SDP (USB 2.0) | Yes                              | 0.5                                                   |

| SDP (USB 3.0) | Yes                              | 0.9                                                   |

| CDP           | Yes                              | 1.5                                                   |

| DCP           | No                               | 1.5                                                   |

#### Standard Downstream Port (SDP) USB 2.0/USB 3.0

An SDP is a traditional USB port that follows USB 2.0/3.0 protocol and supplies a minimum of 500mA/900mA per port. USB 2.0/3.0 communications is supported, and the host controller must be active to allow charging. TPS2543-Q1 supports SDP mode in system power state S0 when system is completely powered ON and fully operational. For more details on control pin (CTL1-CTL3) settings to program this state please refer to device truth table.

SLVSBW2 -MARCH 2013 www.ti.com

#### **Charging Downstream Port (CDP)**

A CDP is a USB port that follows USB BC1.2 and supplies a minimum of 1.5A per port. It provides power and meets USB 2.0 requirements for device enumeration. USB 2.0 communications is supported, and the host controller must be active to allow charging. What separates a CDP from an SDP is the host-charge handshaking logic that identifies this port as a CDP. A CDP is identifiable by a compliant BC1.2 client device and allows for additional current draw by the client device.

The CDP hand-shaking process is done in two steps. During step one the portable equipment outputs a nominal 0.6V output on its D+ line and reads the voltage input on its D- line. The portable device concludes it is connected to an SDP if the voltage is less than the nominal data detect voltage of 0.3V. The portable device concludes that it is connected to a Charging Port if the D- voltage is greater than the nominal data detect voltage of 0.3V and optionally less than 0.8V.

The second step is necessary for portable equipment to determine if it is connected to CDP or DCP. The portable device outputs a nominal 0.6V output on its D- line and reads the voltage input on its D+ line. The portable device concludes it is connected to a CDP if the data line being read remains less than the nominal data detect voltage of 0.3V. The portable device concludes it is connected to a DCP if the data line being read is greater than the nominal data detect voltage of 0.3V.

TPS2543-Q1 supports CDP mode in system power state S0 when system is completely powered ON and fully operational. For more details on control pin (CTL1-CTL3) settings to program this state please refer to device truth table.

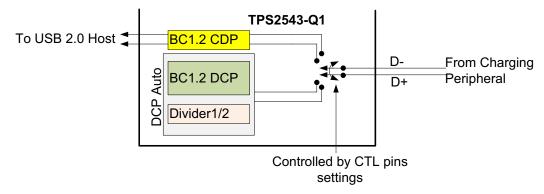

#### **Dedicated Charging Port (DCP)**

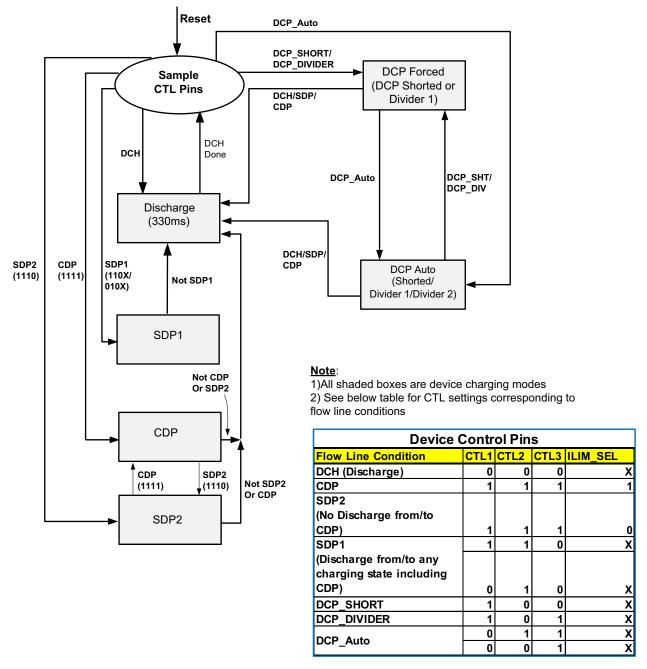

A DCP only provides power but does not support data connection to an upstream port. As shown in following sections, a DCP is identified by the electrical characteristics of its data lines. The TPS2543-Q1 emulates DCP in two charging states, namely DCP Forced and DCP Auto as shown in Figure 32. In DCP Forced state the device will support one of the two DCP charging schemes, namely Divider1 or Shorted. In the DCP Auto state, the device charge detection state machine is activated to selectively implement charging schemes involved with the Shorted, Divider1 and Divider2 modes. Shorted DCP mode complies with BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009, while the Divider mode is employed to charge devices that do not comply with BC1.2 DCP standard.

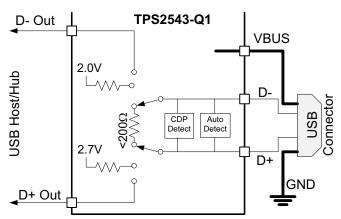

#### DCP BC1.2 and YD/T 1591-2009

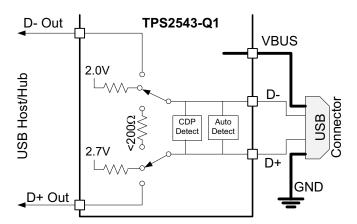

Both standards define that the D+ and D- data lines should be shorted together with a maximum series impedance of 200  $\Omega$ . This is shown in Figure 28.

Figure 28. DCP Supporting BC1.2/YD/T 1591-2009

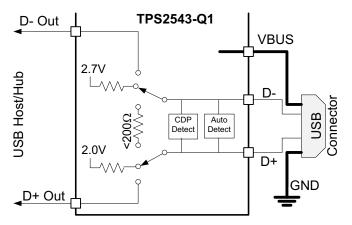

#### **DCP Divider Charging Scheme**

There are two Divider charging scheme supported by the device, Divider1 and Divider2 as shown in Figure 29 and Figure 30. In Divider1 charging scheme the device applies 2.0V and 2.7V to D+ and D- data line respectively. This is reversed in Divider2 mode.

Submit Documentation Feedback

SLVSBW2 -MARCH 2013 www.ti.com

Figure 29. DCP Divider1 Charging Scheme

Figure 30. Divider2 Charging Scheme

#### **DCP Auto Mode**

As mentioned above the TPS2543-Q1 integrates an auto-detect state machine that supports all the above DCP charging schemes. It starts in Divider1 scheme, however if a BC1.2 or YD/T 1591-2009 compliant device is attached, the TPS2543-Q1 responds by discharging OUT, turning back on the power switch and then moving to BC1.2 DCP mode. It then stays in that mode until the device releases the data line, in which case it goes back to Divider1 scheme. When a Divider1 compliant device is attached the TPS2543-Q1 will stay in Divider1 state.

Also, the TPS2543-Q1 will automatically switch between the Divider1 and Divider2 schemes based on charging current drawn by the connected device. Initially the device will set the data lines to Divider1 scheme. If charging current of >750mA is measured by the TPS2543-Q1 it switches to Divider2 scheme and test to see if the peripheral device will still charge at a high current. If it does then it stays in Divider2 scheme otherwise it will revert to Divider1 scheme

SLVSBW2 -MARCH 2013 www.ti.com

Figure 31. DCP Auto Mode

#### DCP Forced Shorted / DCP Forced Divider1

In this mode the device is permanently set to one of the DCP schemes (BC1.2/ YD/T 1591-2009 or Divider1) as commanded by its control pin setting per device truth table.

#### **High-Bandwidth Data Line Switch**

The TPS2543-Q1 passes the D+ and D- data lines through the device to enable monitoring and handshaking while supporting charging operation. A wide bandwidth signal switch is used, allowing data to pass through the device without corrupting signal integrity. The data line switches are turned on in any of CDP or SDP operating modes. The EN input also needs to be at logic High for the data line switches to be enabled.

#### **NOTE**

- 1. While in CDP mode, the data switches are ON even while CDP handshaking is occurring.

- 2. The data line switches are OFF if EN or all CTL pins are held low, or if in DCP mode. They are not automatically turned off if the power switch (IN to OUT) is in current limit.

- 3. The data switches are for USB 2.0 differential pair only. In the case of a USB 3.0 host, the super speed differential pairs must be routed directly to the USB connector without passing through the TPS2543-Q1.

- 4. Data switches are OFF during OUT (VBUS) discharge

20 Sub

#### **Device Operation**

Please refer to the simplified device state diagram in Figure 32. Power-on-reset (POR) holds device in initial state while output is held in discharge mode. Any POR event will take the device back to initial state. After POR clears, device goes to the next state depending on the CTL lines as shown in Figure 32.

Figure 32. TPS2543-Q1 Charging States

#### **Output Discharge**

To allow a charging port to renegotiate current with a portable device, TPS2543-Q1 uses the OUT discharge function. It proceeds by turning off the power switch while discharging OUT, then turning back on the power switch to reassert the OUT voltage. This discharge function is automatically applied as shown in device state diagram.

TEXAS INSTRUMENTS

SLVSBW2 -MARCH 2013 www.ti.com

#### Wake on USB Feature (Mouse/Keyboard Wake Feature)

#### **USB 2.0 Background Information**

The TPS2543-Q1 data lines interface with USB 2.0 devices. USB 2.0 defines three types of devices according to data rate. These devices and their characteristics relevant to TPS2543-Q1 Wake on USB operation are shown below

#### Low-speed USB devices

- 1.5 Mb/s

- Wired mice and keyboards are examples

- · No devices that need battery charging

- All signaling performed at 2.0V and 0.8V hi/lo logic levels

- D- high to signal connect and when placed into suspend

- · D- high when not transmitting data packets

#### Full-speed USB devices

- 12 Mb/s

- Wireless mice and keyboards are examples

- Legacy phones and music players are examples

- Some legacy devices that need battery charging

- All signaling performed at 2.0V and 0.8V hi/lo logic levels

- · D+ high to signal connect and when placed into suspend

- · D+ high when not transmitting data packets

#### High-speed USB devices

- 480 Mb/s

- Tablets, phones and music players are examples

- Many devices that need battery charging

- Connect and suspend signaling performed at 2.0V and 0.8V hi/lo logic levels

- Data packet signaling performed a logic levels below 0.8V

- D+ high to signal connect and when placed into suspend (same as a full-speed device)

- D+ and D- low when not transmitting data packets

#### Wake On USB

Wake on USB is the ability of a wake configured USB device to wake a computer system from its S3 sleep state back to its S0 working state. Wake on USB requires the data lines to be connected to the system USB host before the system is placed into its S3 sleep state and remain continuously connected until they are used to wake the system.

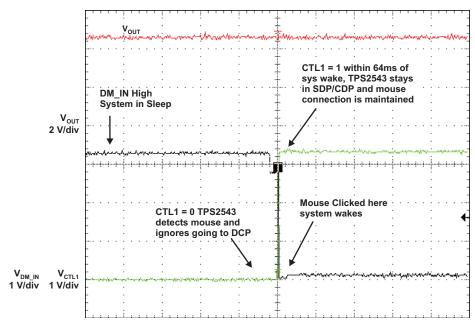

The TPS2543-Q1 supports low speed HID (human interface device like mouse/key board) wake function only. There are two scenarios (as listed below) under which wake on HID are supported by the TPS2543-Q1. The specific CTL pin changes that the TPS2543-Q1 will override are shown below. The information is presented as CTL1, CTL2, CTL3. The ILIM\_SEL pin plays no role

- 1. 111 (CDP/SDP2) to 011 (DCP-Auto)

- 2. 010 (SDP1) to 011 (DCP-Auto)

#### Note:

The 110 (SDP1) to 011 (DCP-Auto) transition is not supported. This is done for practical reasons since the transition involves changes to two CTL pins. Depending on which CTL pin changes first, the device will see either a temporary 111 or 010 command. The 010 command is safe but the 111 command will cause an OUT discharge as the TPS2543-Q1 will instead proceed to the 111 state.

#### **USB Slow-Speed Device Recognition and Operation**

TPS2543-Q1 is capable of detecting LS device attachment when TPS2543-Q1 is in SDP or CDP mode. Per USB spec when no device is attached, the D+ and D- lines are near ground level. When a low speed compliant device is attached to the TPS2543-Q1 charging port, D- line will be pulled high in its idle state (mouse/keyboard not activated). However when a FS device is attached the opposite is true in its idle state, i.e. D+ is pulled high and D- remains at ground level.

When a low speed compliant device is attached to the TPS2543-Q1, charging port D- line will be pulled high in its idle state (mouse/keyboard not activated). TPS2543-Q1 will monitor D- data line continuously. Since TPS2543-Q1 does not monitor D+ line it cannot detect the attachment of a FS device. When TPS2543-Q1 is in CDP/SDP mode and system is commanded to go to sleep state, the device CTL setting is also changed. Assuming it is changed to DCP/Auto, 011, having previously detected a low speed HID attachment the device will simply ignore the command to go to DCP/Auto mode and stay in CDP/SDP state to support wake on mouse function. When the USB low speed HID is activated (clicked) while system is in S3 (sleep) mode the high speed switch within the TPS2543-Q1 allows the transfer of signal from the LS HID device to the USB host. The USB host subsequently wakes the system and changes CTL setting of the TPS2543-Q1 back to CDP/SDP state. Activating (clicking) the low speed device makes the D- data line go back low momentarily, this triggers an internal timer within the TPS2543-Q1 to count down. If after ~64ms the CTL lines are still set at 011 (DCP/Auto) the device will immediately switch to DCP/Auto mode and disconnect the mouse from the host. To prevent this, the CTL setting must be made in less then 64 ms after HID device activation otherwise mouse/KB function will be lost.

Figure 33. Mouse Wake from Sleep Scope Plot

INSTRUMENTS

SLVSBW2 -MARCH 2013 www.ti.com

#### **Device Truth Table (TT)**

Device TT lists all valid bias combinations for the three control pins CTL1-3 and ILIM\_SEL pin and their corresponding charging mode. It is important to note that the TT *purposely* omits matching charging modes of the TPS2543-Q1 with global power states (S0-S5) as device is agnostic to system power states. The TPS2543-Q1 monitors its CTL inputs and will transition to whatever charging state it is commanded to go to (except when LS HID device is detected). For example if sleep charging is desired when system is in standby or hibernate state then user must set TPS2543-Q1 CTL pins to correspond to DCP\_Auto charging mode per below table. When system is put back to operation mode then set control pins to correspond to SDP or CDP mode and so on.

**Table 2. Truth Table**

| CTL1 | CTL2 | CTL3 | ILIM_SEL | MODE                | CURRENT<br>LIMIT<br>SETTING                 | STATUS OUTPUT (Active low)      | COMMENT                                                 |

|------|------|------|----------|---------------------|---------------------------------------------|---------------------------------|---------------------------------------------------------|

| 0    | 0    | 0    | 0        | Discharge           | NA                                          | OFF                             | OUT held low                                            |

| 0    | 0    | 0    | 1        | Discharge           | NA                                          | OFF                             | OOT field low                                           |

| 0    | 0    | 1    | 0        | DCP_Auto            | ILIM_HI                                     | OFF                             | Data Lines Disconnected                                 |

| 0    | 0    | 1    | 1        | DCP_Auto            | I <sub>OS_PW</sub> & ILIM_HI <sup>(1)</sup> | DCP load present <sup>(2)</sup> | Data Lines Disconnected and Load Detect Function Active |

| 0    | 1    | 0    | 0        | SDP1                | ILIM_LO                                     | OFF                             | Data Lines connected                                    |

| 0    | 1    | 0    | 1        | SDP1                | ILIM_HI                                     | OFF                             | - Data Lines connected                                  |

| 0    | 1    | 1    | 0        | DCP_Auto            | ILIM_HI                                     | OFF                             | Data Lines Disconnected                                 |

| 0    | 1    | 1    | 1        | DCP_Auto            | ILIM_HI                                     | DCP load present <sup>(3)</sup> | Data Lines Disconnected and Load Detect Function Active |

| 1    | 0    | 0    | 0        | DCP _Shorted        | ILIM_LO                                     | OFF                             | Device Forced to stay in DCP BC1.2 charging             |

| 1    | 0    | 0    | 1        | DCP_Shorted         | ILIM_HI                                     | OFF                             | mode                                                    |

| 1    | 0    | 1    | 0        | DCP / Divider1      | ILIM_LO                                     | OFF                             | Device Forced to stay in DCP Divider1                   |

| 1    | 0    | 1    | 1        | DCP / Divider1      | ILIM_HI                                     | OFF                             | Charging Mode                                           |

| 1    | 1    | 0    | 0        | SDP1                | ILIM_LO                                     | OFF                             |                                                         |

| 1    | 1    | 0    | 1        | SDP1                | ILIM_HI                                     | OFF                             | Data Lines Connected                                    |

| 1    | 1    | 1    | 0        | SDP2 <sup>(4)</sup> | ILIM_LO                                     | OFF                             |                                                         |

| 1    | 1    | 1    | 1        | CDP <sup>(4)</sup>  | ILIM_HI                                     | CDP load present <sup>(5)</sup> | Data Lines Connected and Load Detect Active             |

<sup>(1)</sup> TPS2543-Q1 : Current limit (I<sub>OS</sub>) is automatically switched between I<sub>OS\_PW</sub> and the value set by ILIM\_HI according to the Load Detect – Power Wake functionality.

Table 3 can be used as an aid to program the TPS2543-Q1 per system states however not restricted to below settings only.

Table 3. Control Pin Settings Matched to System Power States

| SYSTEM<br>GLOBAL<br>POWER<br>STATE | TPS2543-Q1 CHARGING MODE                                                                  | CTL1 | CTL2 | CTL3 | ILIM_SEL | CURRENT LIMIT<br>SETTING |

|------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|----------|--------------------------|

| S0                                 | SDP1                                                                                      | 1    | 1    | 0    | 1 or 0   | ILIM_HI / ILIM_LO        |

| S0                                 | SDP2, no discharge to / from CDP                                                          | 1    | 1    | 1    | 0        | ILIM_LO                  |

| S0                                 | CDP, load detection with ILIM_LO + 60mA thresholds or if a BC1.2 primary detection occurs | 1    | 1    | 1    | 1        | ILIM_HI                  |

| S4/S5                              | Auto mode, load detection with power wake thresholds                                      | 0    | 0    | 1    | 1        | ILIM_HI                  |

| S3/S4/S5                           | Auto mode, no load detection                                                              | 0    | 0    | 1    | 0        | ILIM_HI                  |

| S3                                 | Auto mode, keyboard/mouse wake up, load detection with ILIM_LO + 60 mA thresholds         | 0    | 1    | 1    | 1        | ILIM_HI                  |

| S3                                 | Auto mode, keyboard/mouse wake-up, no load detection                                      | 0    | 1    | 1    | 0        | ILIM_HI                  |

| S3                                 | SDP1, keyboard/mouse wake-up                                                              | 0    | 1    | 0    | 1 or 0   | ILIM_HI / ILIM_LO        |

<sup>(2)</sup> DCP Load present governed by the "Load Detection – Power Wake" limits.

<sup>(3)</sup> DCP Load present governed by the "Load Detection – Non Power Wake" limits.

<sup>(4)</sup> No OUT discharge when changing between 1111 and 1110.

<sup>(5)</sup> CDP Load present governed by the "Load Detection - Non Power Wake" limits and BC1.2 primary detection.

#### **Load Detect**

TPS2543-Q1 offers system designers unique power management strategy not available in the <u>industry</u> from similar devices. There are two power management schemes supported by the TPS2543-Q1 via the STATUS pin, they are:

- 1. Power Wake (PW)

- 2. Port Power Management (PPM)

Either feature may be implemented in a system depending on power savings goals for the system. In general Power Wake feature is used mainly in mobile systems like a notebook where it is imperative to save battery power when system is in deep sleep (S4/S5) state. On the other hand Port Power Management feature would be implemented where multiple charging ports are supported in the same system and system power rating is not capable of supporting high current charging on multiple ports *simultaneously*.

#### **Power Wake**

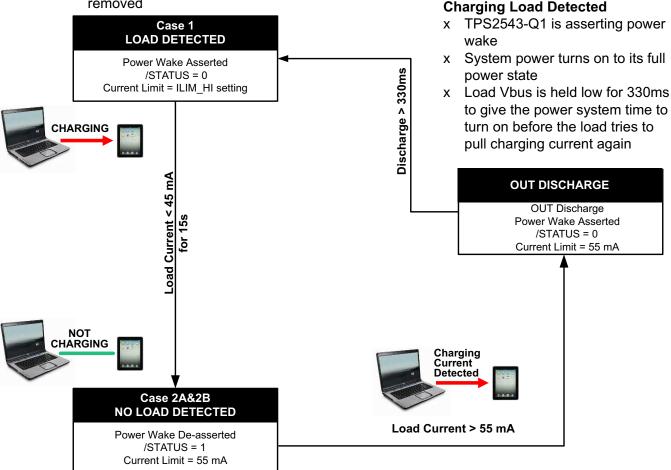

Goal of power wake feature is to save system power when system is in S4/S5 state. In S4/S5 state system is in deep sleep and typically running of the battery; so every "mW" in system power savings will translate to extending battery life. In this state the TPS2543-Q1 will monitor charging current at the OUT pin and provide a mechanism via the STATUS pin to switch out the high power DC-DC controller and switch in a low power LDO when charging current requirement is <45mA (typ). This would be the case when no peripheral device is connected at the charging port or if a device has attained its full battery charge and draws <45mA. Power wake flow chart and description is shown in Figure 34.

Submit Documentation Feedback

SLVSBW2 -MARCH 2013 www.ti.com

#### Load being Charged

- x TPS2543-Q1 is asserting power wake

- x System power is at its full capability

- x Load can charge at high current

- x TPS2543-Q1 monitors port to detect when charging load is done charging or removed

#### **Charging Load Not Detected.**

- x TPS2543-Q1 is not asserting power wake. System power is in a low power state to save energy.

- x TPS2543-Q1 monitors port to detect when charging load is attached and tries to charge

Figure 34. Power Wake Flow Chart

#### Implementing Power Wake in Notebook System

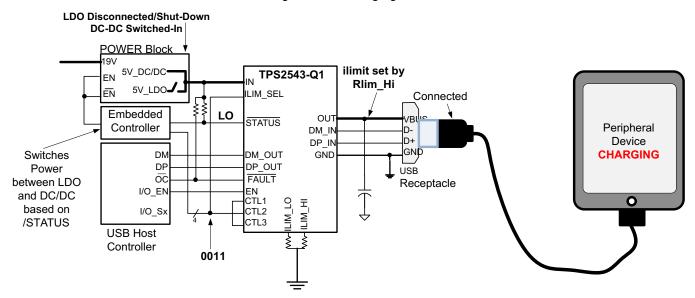

An implementation of power wake in notebook platforms with the TPS2543-Q1 is shown in Figure 35-37. Power wake function is used to select between a high power DC-DC converter and low power LDO (100mA) based on charging requirements. System power saving is achieved when under no charging conditions (the connected device is fully charged or no device is connected) the DC-DC converter is turned-off (to save power since it is less efficient in low power operating region) and the low power LDO supplies standby power to the charging port.

6 Submit Documentation Feedback

Power wake is activated in S4/S5 mode (0011 setting, see device truth table), TPS2543-Q1 is charging connected device as shown in Figure 35, STATUS is pulled LO (Case 1) which switches-out the LDO and switches-in the DC-DC converter to handle high current charging.

Figure 35. Case 1: System in S4/S5, Device Charging

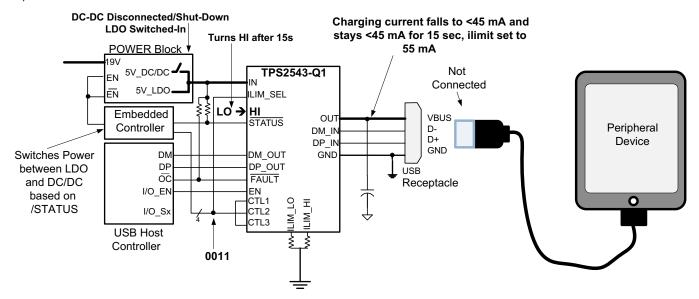

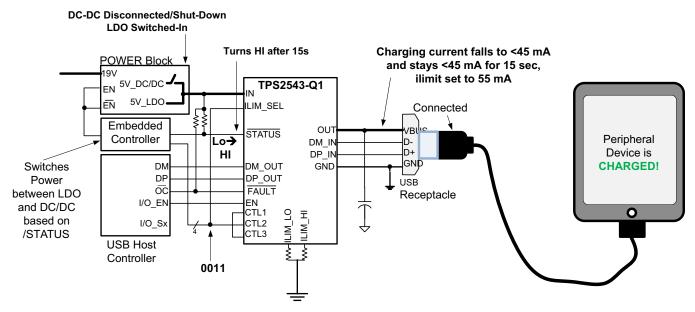

As shown in Case 2A and Case 2B, when connected device is fully charged or gets disconnected from the charging port, the charging current will fall. If charging current falls to <45mA and stays below this threshold for over 15s, TPS2543-Q1 automatically sets a 55mA internal current limit and STATUS is de-asserted (pulled HI). As shown in Case 2A and Case 2B. This results in DC-DC converter turning off and the LDO turning on. Current limit of 55 mA is set to prevent the low power LDO output voltage from collapsing in case there is a spike in current draw due to device attachment or other activity such as display panel LED turning ON in connected device.

Following Power Wake flow chart (Figure 34) when a device is attached and draws >55 mA of charging current the TPS2543-Q1 will hit its internal current limit. This will trigger the device to assert STATUS (LO) and turn on the DC-DC converter and turn off the LDO. TPS2543-Q1 will discharge OUT for >330ms (typ) to allow the main power supply to turn on. After the discharge the device will turn back on with current limit set by ILIM\_HI (Case 1)

Figure 36. Case 2A: System in S4/S5, No Device Attached

SLVSBW2 -MARCH 2013 www.ti.com

Figure 37. Case 2B: System in S4/S5, Attached Device Fully Charged

#### **Port Power Management (PPM)**

PPM is the intelligent and dynamic allocation of power. It is for systems that have multiple charging ports but cannot power them all simultaneously. Goal of this feature are:

- 1. Enhances user experience since user does not have to search for charging port

- 2. Power supply only has to be designed for a reasonable charging load

Initially all ports are allowed to <u>broadcast</u> high current charging, charging current limit is based on ILIM\_HI resistor setting. System monitors <u>STATUS</u> to see when high current loads are present. Once allowed number of ports assert <u>STATUS</u>, remaining ports are toggled to a non-charging port. Non-charging ports are SDP ports with current limit based on ILIM\_LO. TPS2543-Q1 allows for a system to toggle between charging and non-charging ports either with an OUT discharge or without an OUT discharge.

#### **Benefits of PPM**

- Delivers better user experience

- Prevents overloading of system's power supply

- · Allows for dynamic power limits based on system state

- Allows every port to potentially be a high power charging port

- · Allows for smaller power supply capacity since the loading is controlled

#### **PPM Details**

All ports are allowed to broadcast high current charging – CDP or DCP. Current limit is based on ILIM\_HI and <a href="mailto:system\_monitors">system\_monitors</a> STATUS pin to see when high current loads are present. Once allowed number of ports assert <a href="mailto:STATUS">STATUS</a>, remaining ports are toggled to a SDP non-charging port. SDP current limit is based on ILIM\_LO <a href="mailto:setting">setting</a>. SDP ports are automatically toggled back to CDP or DCP mode when a charging port de-asserts <a href="mailto:STATUS">STATUS</a>.

Based on CTL settings there is a provision for a port to toggle between charging and non-charging ports either with a Vbus discharge or without a Vbus discharge. For example when a port is in SDP2 mode (1110) and its ILIM\_SEL pin is toggled to 1 due to another port releasing its high current requirements. The SDP2 port will automatically revert to CDP mode (1111) without a discharge event. This is desirable if this port was connected to a media device where it was syncing data from the SDP2 port; a discharge event would mess-up the syncing activity on the port and cause user confusion.

STATUS trip point is based on the programmable ILIM\_LO current limit set point This does not mean STATUS is a current limit – the port itself is using the ILIM\_HI current limit. Since ILIM\_LO defines the current limit for a SDP port, it works well to use the ILIM\_LO value to define a high current load. STATUS asserts in CDP and DCP when load current is above ILIM\_LO+60mA for 200 ms. STATUS also asserts in CDP when an attached device does a BC1.2 primary detection. STATUS de-asserts in CDP and DCP when load current is below ILIM LO+10mA for 3s.

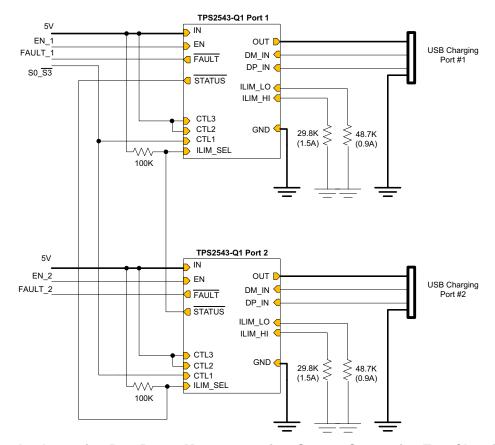

#### Implementing PPM in a System with Two Charging Ports

Figure 38 shows implementation of two charging ports, each with its own TPS2543-Q1. In this example 5V power supply for the two charging ports is rated at < 3A or <15W max. Both devices have  $R_{LIM}$  chosen to correspond to the low (0.9A) and high (1.5A) current limit setting for the port. In this implementation the system can support only one of the two ports at 1.5A charging current while the other port is set to SDP mode and  $I_{LIMIT}$  corresponding to 0.9A.

Figure 38. Implementing Port Power Management in a System Supporting Two Charging Ports

#### **Over-Current Protection**

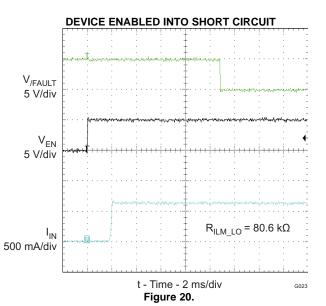

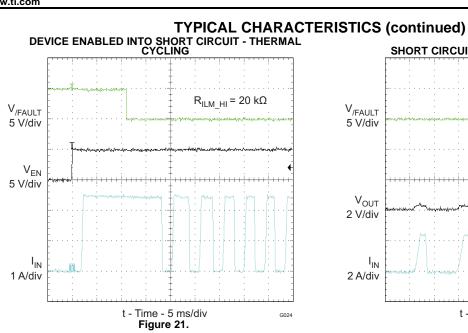

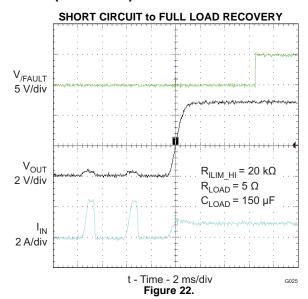

When an over-current condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Two possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before VIN has been applied. The TPS2543-Q1 senses the short and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for nominally one to two microseconds before the current-limit circuit can react. The device operates in constant-current mode after the current-limit circuit has responded. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting. The device will remain off until the junction temperature cools approximately 20°C and will then re-start. The device will continue to cycle on/off until the over-current condition is removed.

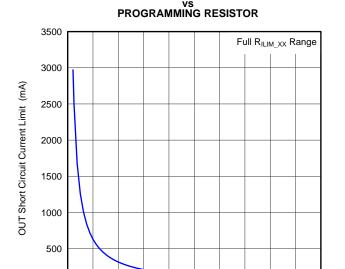

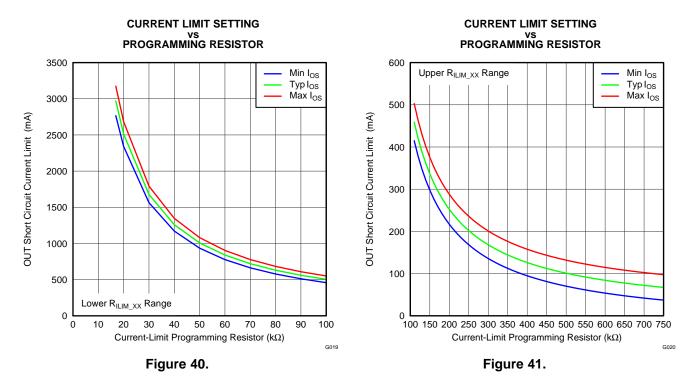

#### **Current-Limit Settings**

The TPS2543-Q1 has two independent current limit settings that are each programmed externally with a resistor. The ILIM\_HI setting is programmed with R<sub>ILIM\_HI</sub> connected between ILIM\_HI and GND. The ILIM\_LO setting is programmed with RILIM\_LO connected between ILIM\_LO and GND. Consult the Device Truth Table (Table 2) to see when each current limit is used. Both settings have the same relation between the current limit and the programming resistor.

R<sub>ILIM\_LO</sub> is optional and the ILIM\_LO pin may be left unconnected if the following conditions are met:

- 1. ILIM SEL is always set high

- 2. Load Detection Port Power Management is not used

- 3. Mouse / Keyboard wake function is not used

If conditions 1 and 2 are met but the mouse / keyboard wake function is also desired, it is recommended to use  $R_{ILIM\_LO}$  < 80.6 k $\Omega$ .

The following equation programs the typical current limit:

$$I_{OS_{typ}}(mA) = \frac{50,500}{(R_{ILIM_{XX}}(k\Omega) + 0.1)}$$

(1)

TYPICAL CURRENT LIMIT SETTING

$R_{ILIM\ XX}$  corresponds to either  $R_{ILIM\ HI}$  or  $R_{ILIM\ LO}$  as appropriate.

Figure 39.

Current-Limit Programming Resistor (kΩ)

240 320 400 480 560

80

SLVSBW2 -MARCH 2013 www.ti.com

Many applications require that the current limit meet specific tolerance limits. When designing to these tolerance limits, both the tolerance of the TPS2543-Q1 current limit and the tolerance of the external programming resistor must be taken into account. The following equations approximate the TPS2543-Q1 minimum / maximum current limits to within a few mA and are appropriate for design purposes. The equations do not constitute part of TI's published device specifications for purposes of Ti's product warranty. These equations assume an ideal - no variation - external programming resistor. To take resistor tolerance into account, first determine the minimum / maximum resistor values based on its tolerance specifications and use these values in the equations. Because of the inverse relation between the current limit and the programming resistor, use the maximum resistor value in the l<sub>OS min</sub> equation and the minimum resistor value in the l<sub>OS max</sub> equation.

$$I_{OS\_min}(mA) = \frac{45,661}{(R_{ILIM\_XX}(k\Omega) + 0.1)^{0.98422}} - 30$$

$$I_{OS\_max}(mA) = \frac{55,639}{(R_{ILIM\_XX}(k\Omega) + 0.1)^{1.0143}} + 30$$

(3)

The traces routing the R<sub>ILIM\_XX</sub> resistors should be a sufficiently low resistance as to not affect the current-limit accuracy. The ground connection for the R<sub>ILIM\_XX</sub> resistors is also very important. The resistors need to reference back to the TPS2543-Q1 GND pin. Follow normal board layout practices to ensure that current flow from other parts of the board does not impact the ground potential between the resistors and the TPS2543-Q1 GND pin.

#### **FAULT Response**

The FAULT open-drain output is asserted (active low) during an over-temperature or current limit condition. The output remains asserted until the fault condition is removed. The TPS2543-Q1 is designed to eliminate false FAULT reporting by using an internal deglitch circuit for current limit conditions without the need for external circuitry. This ensures that FAULT is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. Over-temperature conditions are not deglitched and assert the FAULT signal immediately.

#### **Undervoltage Lockout (UVLO)**

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted oscillations on the output due to input voltage drop from large current surges.

#### **Thermal Sense**

The TPS2543-Q1 protects itself with two independent thermal sensing circuits that monitor the operating temperature of the power distribution switch and disables operation if the temperature exceeds recommended operating conditions. The device operates in constant-current mode during an over-current condition, which increases the voltage drop across power switch. The power dissipation in the package is proportional to the voltage drop across the power switch, so the junction temperature rises during an over-current condition. The first thermal sensor turns off the power switch when the die temperature exceeds 135°C and the part is in current limit. The second thermal sensor turns off the power switch when the die temperature exceeds 155°C regardless of whether the power switch is in current limit. Hysteresis is built into both thermal sensors, and the switch turns on after the device has cooled by approximately 20°C. The switch continues to cycle off and on until the fault is removed. The open-drain false reporting output FAULT is asserted (active low) during an over-temperature shutdown condition.

11-Apr-2013

#### PACKAGING INFORMATION