TRF1112 TRF1212 SLWS175A-APRIL 2005-REVISED DECEMBER 2005

# Dual VCO/PLL Synthesizer With IF Down-Conversion

## **FEATURES**

- Low Phase Noise

- High Dynamic Range Image-Reject

Downconverter

- Selectable IF Filters

- Internal or External AGC Control With Peak Detector and Voltage Reference

- Analog Gain Control Range

- Direct Interface to A/D

- Dual VCO/PLL With On-Chip Resonator For Double Down-Conversion Architecture

## **KEY SPECIFICATIONS**

- S-Band LO Frequency Range:

TRF1112: 1700 to 2400 MHz

- TRF1212: 2400 MHz to 3550 MHz

- UHF LO Frequency Range: 325 MHz to 460 MHz

- Phase Noise is 0.5 RMS Typ 100 Hz to 1 MHz

- Rx Noise Figure of 5 dB, Typ

- UHF LO Tuning Step Size of 125 kHz With 18 MHz Reference

- Typical Gain of 90 dB, Including 15-dB Loss IF2 SAW Filter

- Input Third Order Intercept Point > 0 dBm

- Input 1-dB Compression Point > -10 dBm

- Gain Control Range of 90 dB Typ

## DESCRIPTION

The TRF1112 / TRF1212 are UHF-VHF down converters with integrated UHF and S-band frequency synthesizers for radio applications in the 2GHz to 4GHz range. The device integrates an image reject mixer, IF gain blocks, automatic gain control (AGC), and two complete phase locked loop (PLL) circuits including: VCOs, resonator circuit, varactors, dividers, and phase detectors.

The TRF1112 / TRF1212 are designed to function as part of Texas Instruments 2.5-GHz and 3.5-GHz complete radio chipsets, respectively. In the chipset, two chips function together to double-down convert RF frequencies to an IF frequency that is suitable for most baseband modem ADCs. The TRF1112 / TRF1212 performs the second down conversion from the first IF frequency (480 MHz typical) to a final IF frequency (20-50 MHz). The radio chipset features sufficient linearity, phase noise and dynamic range to work in single carrier or multi-carrier, line-of-sight or non-line-of-sight, IEEE standard 802.16, BWIF, or proprietary systems. Due to the modular nature of the chipset, it is ideal for use in systems that employ transmit or receive diversity.

## **TRF1112 / TRF1212 PIN OUT**

|                                                                                       |                                                                                                                                                            | LPCC-48 PACKAGE<br>(TOP VIEW)                                                                                                      |                                                                               |                                                                                                    |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                       |                                                                                                                                                            | EXTLO1N<br>EXTLO1P<br>VCCLO1<br>LO10P<br>LO10N<br>LO10N<br>LO1BPA<br>LO1BPB<br>IF2BIN<br>IF2BIP<br>IF2AIN<br>IF2AIP<br>IF2AIP      |                                                                               |                                                                                                    |

| CP2O<br>LD1<br>LF1<br>EN<br>FRBP<br>VCCD1<br>FR<br>VCCD2<br>CLK<br>DATA<br>LF2<br>LD2 | $ \begin{array}{c}     1 \\     1 \\     2 \\     3 \\     4 \\     5 \\     6 \\     7 \\     8 \\     9 \\     10 \\     11 \\     12 \\   \end{array} $ |                                                                                                                                    | 36 U 35 U 33 U 33 U 31 U 29 U 28 U 27 U 26 U 25 | AGCO<br>IFBPB<br>IF1IP<br>IF1IN<br>VCCA<br>VCCB<br>VERR<br>VREF<br>VFB<br>VCCC<br>IF2AOP<br>IF2AON |

| I                                                                                     |                                                                                                                                                            | CP20<br>LO2TUN<br>LO2BPB<br>VDET<br>AGCI<br>LO2BPA<br>AGCI<br>LO2BPA<br>VCCLO2<br>BBON<br>BBON<br>BBOP<br>VBGR<br>IF2BON<br>IF2BON |                                                                               |                                                                                                    |

## **BLOCK DIAGRAM**

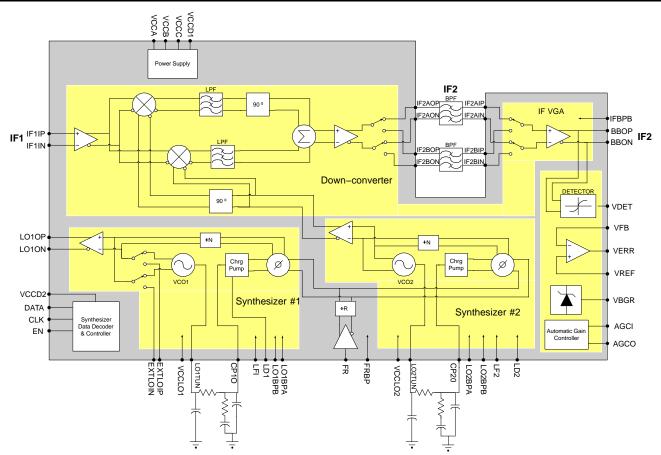

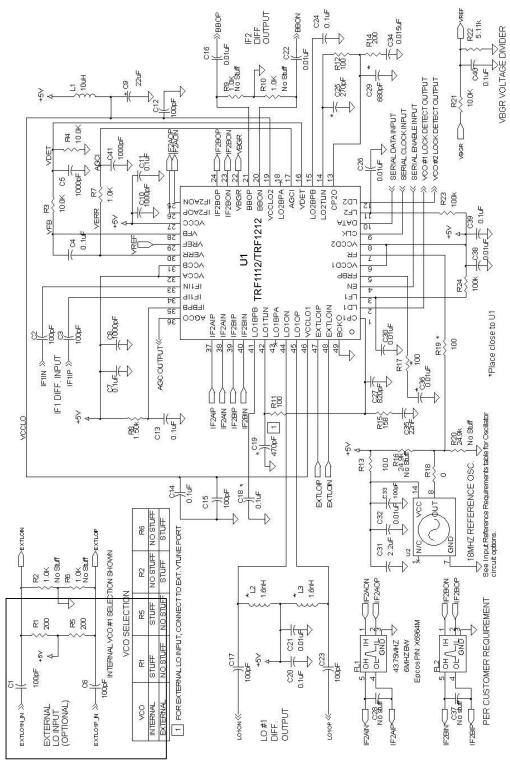

The detailed block diagram and the pin-out of the ASIC are shown in Figure 1 and the Terminal Functions table.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. TRF1112 TRF1212

SLWS175A-APRIL 2005-REVISED DECEMBER 2005

| TE  | RMINAL | I/O | TYPE    | DESCRIPTION                                                                                     |

|-----|--------|-----|---------|-------------------------------------------------------------------------------------------------|

| NO. | NAME   | 1/0 | ITPE    | DESCRIPTION                                                                                     |

| 1   | CP1O   | 0   | Analog  | Analog Synthesizer 1 Charge Pump Output                                                         |

| 2   | LD1    | 0   | Digital | Synthesizer 1 Lock Detect Output, High is locked                                                |

| 3   | LF1    | 0   | Analog  | Lock Detector Filter Capacitor for LO1, 0.01 $\mu$ F Typ. 100 k $\Omega$ pull-up <sup>(1)</sup> |

| 4   | EN     | I   | Digital | 3-wire bus Enable; Active High                                                                  |

| 5   | FRBP   | 0   | Analog  | Reference Frequency Bypass, Internally biased to 2.5 V.                                         |

| 6   | VCCD1  | Ι   | Power   | Digital Power Supply Voltage                                                                    |

| 7   | FR     | Ι   | Analog  | Reference Frequency Source Input, HCMOS input. (DC level = 2.5 V)                               |

| 8   | VCCD2  | I   | Power   | Digital Power Supply Voltage                                                                    |

| 9   | CLK    | I   | Digital | 3-wire bus Clock                                                                                |

| 10  | DATA   | Ι   | Digital | 3-wire bus Data                                                                                 |

| 11  | LF2    | 0   | Analog  | Lock Detector Filter Capacitor for LO2, 0.01 $\mu$ F typ 100 k $\Omega$ pull-up <sup>(1)</sup>  |

| 12  | LD2    | 0   | Analog  | Synthesizer 2 Lock Detect Output, High is locked                                                |

| 13  | CP2O   | 0   | Analog  | Synthesizer 2 Charge Pump Output                                                                |

| 14  | LO2TUN | Ι   | Analog  | Synthesizer 2 VCO Input tune port                                                               |

| 15  | LO2BPB | 0   | Analog  | Bypass cap for LO2, 0.1 $\mu$ F (min) DCV = 1 V                                                 |

| 16  | VDET   | 0   | Analog  | Peak Detector Output                                                                            |

#### **TERMINAL FUNCTIONS**

(1) Current leakage on the order of 10 μA through the capacitor or by any other means from either LF pin can cause false loss of lock signals. The two pull up resistors (R23 and R24) in Figure 20 reduce this sensitivity.

# **TERMINAL FUNCTIONS (continued)**

| TE  | RMINAL  |     | -      |                                                                                                       |

|-----|---------|-----|--------|-------------------------------------------------------------------------------------------------------|

| NO. | NAME    | I/O | TYPE   | DESCRIPTION                                                                                           |

| 17  | AGCI    | Ι   | Analog | AGC Voltage Input, 0-3 V                                                                              |

| 18  | LO2BPA  | 0   | Analog | Not connected for normal operation. DC bias nominal 1.8 V. Do not ground or connect to any other pin. |

| 19  | VCCLO2  | I   | Power  | VCC for LO2, Low Noise Supply                                                                         |

| 20  | BBON    | 0   | Analog | IF output (differential) negative, DC coupled, internally biased to 3 V typical                       |

| 21  | BBOP    | 0   | Analog | IF output (differential) positive, DC coupled, internally biased to 3 V typical                       |

| 22  | VBGR    | 0   | Analog | Band-Gap Reference Voltage, 1.17 V                                                                    |

| 23  | IF2BON  | 0   | Analog | IF2B output (differential) negative, DC coupled, internally biased to 4 V typical                     |

| 24  | IF2BOP  | 0   | Analog | IF2B output (differential) positive , DC coupled, internally biased to 4 V typical                    |

| 25  | IF2AON  | 0   | Analog | IF2A output (differential) negative, DC coupled, internally biased to 4 V typical                     |

| 26  | IF2AOP  | 0   | Analog | IF2A output (differential) positive, DC coupled, internally biased to 4 V typical                     |

| 27  | VCCC    | I   | Power  | Analog Power Supply Voltage                                                                           |

| 28  | VFB     | I   | Analog | Error Amplifier Feedback Input                                                                        |

| 29  | VREF    | I   | Analog | Reference Frequency Input                                                                             |

| 30  | VERR    | 0   | Analog | Error Amplifier Output, internal op amp output                                                        |

| 31  | VCCB    | I   | Power  | Analog Power Supply Voltage                                                                           |

| 32  | VCCA    | I   | Power  | Analog Power Supply Voltage                                                                           |

| 33  | IF1IN   | I   | Analog | IF1 input (differential) negative, DC coupled, Internally biased to 1.4 V typical                     |

| 34  | IF1IP   | I   | Analog | IF1 input (differential) positive, DC coupled, Internally biased to 1.4 V typical                     |

| 35  | IFBPB   | 0   | Analog | Bypass cap for IF amp, 0.1 $\mu$ F (min), DCV = 1 V                                                   |

| 36  | AGCO    | 0   | Analog | AGC Voltage Output Used to control Front end gain for extended dynamic range                          |

| 37  | IF2AIP  | I   | Analog | IF2A input (differential) positive, DC coupled, Internally biased to 3.0 V typical                    |

| 38  | IF2AIN  | I   | Analog | IF2A input (differential) negative, DC coupled, Internally biased to 3.0 V typical                    |

| 39  | IF2BIP  | I   | Analog | IF2B input (differential) positive, DC coupled, Internally biased to 3.0 V typical                    |

| 40  | IF2BIN  | I   | Analog | IF2B input (differential) negative, DC coupled, Internally biased to 3.0 V typical                    |

| 41  | LO1BPB  | 0   | Analog | Bypass cap for LO1 0.1 μF (min), DCV = 1 V                                                            |

| 42  | LO1TUN  | I   | Analog | Synthesizer1 VCO Tune port Input                                                                      |

| 43  | LO1BPA  | 0   | Analog | Not connected for normal operation. DC bias nominal 1.8 V. Do not ground or connect to any other pin. |

| 44  | LO10N   | 0   | Analog | LO1 output (differential) neg. Negative and positive VCC bias (+5 V) for LO buffer amp.               |

| 45  | LO10P   | 0   | Analog | LO1 output (differential) pos. Negative and positive VCC bias (+5 V) for LO buffer amp.               |

| 46  | VCCLO1  | Ι   | Power  | VCC for LO1, Low Noise Supply                                                                         |

| 47  | EXTLO1P | Ι   | Analog | External VCO input (differential) positive and logic level for VCO select.                            |

| 48  | EXTLO1N | Ι   | Analog | External VCO input (differential) negative and logic level for VCO select.                            |

| _   | BACK    | _   | -      | Back side of package has metal base that must be grounded for thermal and RF performance.             |

SLWS175A-APRIL 2005-REVISED DECEMBER 2005

### **ABSOLUTE MAXIMUM RATINGS**

|                      |                                                       | UNIT            |

|----------------------|-------------------------------------------------------|-----------------|

| V <sub>CC</sub>      | DC Supply Voltage                                     | 0.0 V to 5.5 V  |

| I <sub>CC</sub>      | DC Supply Current                                     | 270 mA          |

| Pin                  | RF Input Power                                        | 20 dBm          |

| TJ                   | Junction Temperature                                  | 150°C           |

| Pd                   | Power Dissipation                                     | 1.5 W           |

|                      | Digital Input Pins                                    | –0.3 to 5.5 V   |

|                      | Analog Input Pins                                     | TBD             |

| $\theta_{\text{JC}}$ | Thermal Resistance Junction-to-Ambient <sup>(1)</sup> | 25°C/W          |

| T <sub>stg</sub>     | Storage Temperature                                   | – 40°C to 105°C |

| T <sub>op</sub>      | Operating Temperature                                 | –40°C to 85°C   |

|                      | Lead Temperature, 40 Sec Max.                         | 260°C           |

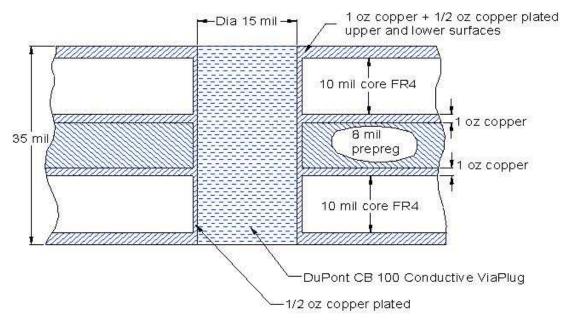

(1) Thermal resistance is junction to ambient assuming thermal pad with 16 thermal vias under package metal base see recommended PCB layout (see Figure 20.)

## DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 5 V, T = 25°C (unless otherwise noted)

|                 | PARAMETER         | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------|-------------------|-----------------|-----|-----|-----|------|

| V <sub>CC</sub> | DC supply voltage |                 | 4.8 |     | 5.2 | V    |

| I <sub>CC</sub> | DC supply current |                 |     | 200 |     | mA   |

## DOWNCONVERTER ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 5 V,  $T_{A}$  = 25°C, FIF = 480 MHz, IF2 SAW 43.75 MHz unless otherwise stated

|                     | PARAMETER                             | TEST CONDITIONS                                                                                              | MIN | TYP  | MAX | UNIT |

|---------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| f <sub>IF1</sub>    | IF1 input frequency                   |                                                                                                              | 400 | 480  | 500 | MHz  |

| G <sub>max</sub>    | Maximum gain                          | IF1IP/N to BBOP/N at V <sub>AGC</sub> I = 3 V                                                                | 90  | 95   | 100 | dB   |

| DR <sub>G</sub>     | Gain control range                    | IF1IP/N to BBOP/N at V <sub>AGCI</sub> = 0 through 3 V                                                       | 78  | 90   |     | dB   |

| $\Delta G_{max}$    | Gain flatness                         | IF1IP/N to IF2A/BOP/N or BBOP/N for any gain setting.<br>Measured in 6 MHz BW, excluding BPF gain variations |     | ±0.3 |     | dB   |

| IR                  | Image rejection                       | IF1IP/N to IF2A/BOP/N Measured into 1 k $\Omega$ differential load IF2 = 35–60 MHz                           | 30  | 35   |     | dBc  |

| NF                  | Noise figure                          | High Gain ( $V_{AGCI}$ = 2 V) IF1IP/N to BBOP/N at 100 $\Omega$ diff                                         |     | 4.7  |     | dB   |

| IP-1dB              | Input power at 1dB gain               | High Gain ( $V_{AGCI}$ = 2 V) IF1IP/N to BBOP/N at 100 $\Omega$ diff                                         |     | -75  |     | al D |

| IP-10B              | compression                           | Low Gain ( $V_{AGCI}$ = 0 V) IF1IP/N to BBOP/N at 100 $\Omega$ diff                                          |     | -10  |     | dBm  |

| IIP3                | lanut Ord and an intercent            | High Gain ( $V_{AGCI}$ = 2 V) IF1IP/N to BBOP/N at 100 $\Omega$ diff                                         |     | -65  |     | al D |

| IIP3                | Input 3 <sup>rd</sup> order intercept | Low Gain ( $V_{AGCI} = 0$ V) IF1IP/N to BBOP/N at 100 $\Omega$ diff                                          | -5  | 0    |     | dBm  |

| Z <sub>IF1</sub>    | IF1 input impedance                   | Differential mode                                                                                            |     | 100  |     | Ω    |

| RL <sub>IF1</sub>   | IF1 input return loss                 | Measured into 100 $\Omega$ differential load at IF1P/N input                                                 | -11 | -16  |     | dB   |

| f <sub>IF2</sub>    | IF2 frequency                         |                                                                                                              | 25  |      | 70  | MHz  |

| Z <sub>IF2O</sub>   | IF2A/BO output impedance              | Measured in differential mode At IF2A/BOP/N                                                                  |     | 50   |     | Ω    |

| ISO <sub>PP</sub>   | Port-to-port isolation                | Measured between IF2AOP/N to IF2BOP/N and IF2AIP/N to IF2BIP/N with the Filter Select set high or low.       | 30  |      |     | dB   |

| ISO <sub>OI</sub>   | Output-to-input port isolation        | Measured between IF2A/BOP/N and IF2A/BIP/N with the Filter Select set high or low.                           | 60  |      |     | dB   |

| Z <sub>F2I</sub>    | IF2A/BI input impedance               |                                                                                                              | 1   | 2    |     | kΩ   |

| V <sub>BB,OUT</sub> | Output signal level                   | Measured into a 1000 $\Omega$ differential load at BBOP/N at any gain with functional AGC                    | 1.2 |      |     | Vppd |

| IMD                 | In-band intermodulation               | Closed-loop AGC, $V_{BB,OUT} = 1.2$ V Any input power up to -20 dBm.                                         |     | -35  | -30 | dBc  |

## DOWNCONVERTER ELECTRICAL CHARACTERISTICS (continued)

$V_{CC}$  = 5 V,  $T_{A}$  = 25°C, FIF = 480 MHz, IF2 SAW 43.75 MHz unless otherwise stated

| OVER     | OVERALL DOWNCONVERTER SIGNAL CHARACTERISTICS |                                         |     |     |     |      |  |  |  |

|----------|----------------------------------------------|-----------------------------------------|-----|-----|-----|------|--|--|--|

|          | PARAMETER                                    | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |  |  |  |

| $Z_{BB}$ | Baseband section output<br>impedance         | Measured in differential mode at BBOP/N |     | 50  |     | Ω    |  |  |  |

## SYNTHESIZER #1 (S-BAND PLL) ELECTRICAL CHARACTERISTICS

| SYNTHES                               | SIZER #1 SIGNAL CHARACTERIS                        | STICS                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |            |

|---------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|

|                                       | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                           | MIN  | TYP  | MAX  | UNIT       |

| f <sub>Ref</sub>                      | Reference frequency                                | Reference frequency can vary. 18 MHz is used for<br>reference design Also see 1 Note that for source<br>peak-to-peak voltages of less than 4 V and dc component<br>other than 2.5-V degradation of the close-in phase noise<br>may occur. For oscillators with no dc component, a dc<br>voltage may be applied using a voltage divider (see the<br>schematic and the Input Reference Requirements table). |      | 18   |      | MHz        |

| f                                     | Output frequency range                             | TRF1112                                                                                                                                                                                                                                                                                                                                                                                                   | 1700 |      | 2400 | MHz        |

| f <sub>LO1</sub>                      | Output nequency range                              | TRF1212                                                                                                                                                                                                                                                                                                                                                                                                   | 2400 |      | 3550 |            |

| MC                                    | Tuning sensitivity                                 | TRF1112, For V <sub>LO1TUN</sub> ≥ 2 V                                                                                                                                                                                                                                                                                                                                                                    | 200  |      | 400  | MHz/V      |

| MS <sub>LO1</sub>                     | Turning sensitivity                                | TRF1212, For $V_{LO1TUN} \ge 2 V$                                                                                                                                                                                                                                                                                                                                                                         | 300  |      | 600  | IVII IZ/ V |

| $\Delta f_{LO1}$                      | Step size, nominal                                 | For 18-MHz reference input                                                                                                                                                                                                                                                                                                                                                                                |      | 1    |      | MHz        |

| P <sub>LO1</sub>                      | Power level                                        | Measured into a 100- $\Omega$ differential load at the LO1OP/N port, over temperature and frequency range                                                                                                                                                                                                                                                                                                 | -6   | -3   | 0    | dBm        |

| ∮FR VOC1                              | Free running VCO1 SSB phase noise at 100 kHz       | Measured into 100- $\Omega$ differential load at the LO1OP/N port                                                                                                                                                                                                                                                                                                                                         |      | -100 |      | dBc/Hz     |

| *                                     | Locked synthesizer 1 SSB phase noise at 10 kHz     | Measured into 100- $\Omega$ differential load at the LO1OP/N port                                                                                                                                                                                                                                                                                                                                         |      | -105 |      | dBc/Hz     |

| <sup>¢</sup> LD LO1                   | Locked Synthesizer 1 SSB<br>phase noise at 100 kHz | Locked with loop bandwidth set to 400 kHz nominal                                                                                                                                                                                                                                                                                                                                                         |      | -100 |      | UDC/NZ     |

| ¢ld lo1                               | Locked Synthesizer 1<br>Integrated RMS phase noise | 100 Hz to 1 MHz                                                                                                                                                                                                                                                                                                                                                                                           |      | 0.5  | 1    | deg        |

| R <sub>RS LO1</sub>                   | Reference Spur Rejection                           | Measured into a 100- $\Omega$ differential load at the LO1OP/N port                                                                                                                                                                                                                                                                                                                                       |      |      | -50  | dBc        |

| R <sub>FS LO1</sub>                   | Fractional Spur Rejection                          | Measured into a 100- $\Omega$ differential load at the LO1OP/N port                                                                                                                                                                                                                                                                                                                                       |      |      | -45  | dBc        |

| R <sub>N x LO1</sub> ,<br>N:<br>2,3,4 | Harmonic Rejection                                 | Measured into a 100- $\Omega$ differential load at the LO1OP/N port                                                                                                                                                                                                                                                                                                                                       |      | -20  |      | dBc        |

| RL <sub>O</sub>                       | Output Return Loss                                 | Measured into a 100- $\Omega$ differential load at the LO1OP/N port over all input power levels.                                                                                                                                                                                                                                                                                                          | -11  | -16  |      | dB         |

| Z <sub>O</sub>                        | Output Impedance                                   | Differential mode at LO1OP/N port                                                                                                                                                                                                                                                                                                                                                                         |      | 100  |      | Ω          |

| P <sub>extVCO</sub>                   | Ext VCO input                                      | Differential mode                                                                                                                                                                                                                                                                                                                                                                                         |      | -13  |      | dBm        |

| R <sub>LextVCO</sub>                  | Ext VCO Port Input Return Loss                     | Differential mode                                                                                                                                                                                                                                                                                                                                                                                         |      | -13  |      | dB         |

| Z <sub>I extVCO</sub>                 | Ext VCO port input impedance                       | Differential mode                                                                                                                                                                                                                                                                                                                                                                                         |      | 100  |      | Ω          |

## SYNTHESIZER #2 (UHF-BAND PLL) ELECTRICAL CHARACTERISTICS

| SYNTHESI         | ZER #2 SIGNAL CHARACTERISTICS                  |                 |     |      |     |        |

|------------------|------------------------------------------------|-----------------|-----|------|-----|--------|

|                  | PARAMETER                                      | TEST CONDITIONS | MIN | TYP  | MAX | UNIT   |

| f <sub>Ref</sub> | Reference Frequency                            | See Table 4     |     | 18   |     | MHz    |

| f <sub>LO2</sub> | Frequency                                      |                 | 325 |      | 460 | MHz    |

| ∲FR VCO2         | Free running VCO2 SSB Phase Noise at 100 kHz   |                 |     | -115 |     | dBc/Hz |

| ∮LD LO2          | Locked Synthesizer 2 SSB Phase Noise at 10 kHz |                 |     | -115 |     | dBc/Hz |

| ¢ld lo₂          | Locked Synthesizer 2 SSB Phase Noise at100 kHz |                 |     | -115 |     | dBc/Hz |

## SYNTHESIZER #2 (UHF-BAND PLL) ELECTRICAL CHARACTERISTICS (continued)

| SYNTHES             | IZER #2 SIGNAL CHARACTERISTICS                  |                               |     |     |     |       |

|---------------------|-------------------------------------------------|-------------------------------|-----|-----|-----|-------|

|                     | PARAMETER                                       | TEST CONDITIONS               | MIN | TYP | MAX | UNIT  |

| ¢ld lo₂             | Locked Synthesizer 2 Integrated RMS Phase noise | 100 Hz to 1MHz                |     |     | 0.2 | deg   |

| MS <sub>LO2</sub>   | Tuning Sensitivity                              | For V <sub>LO2TUN</sub> ≥ 2 V | 40  |     | 80  | MHz/V |

| $\Delta f_{LO2}$    | Step Size                                       | For 18-MHz reference input    |     |     | 125 | kHz   |

| R <sub>RS LO1</sub> | Reference Sideband Rejection                    |                               |     | -65 | -60 | dBc   |

| R <sub>FS LO1</sub> | Fractional Spurs Rejection                      |                               |     | -65 | -60 | dBc   |

## **INPUT REFERENCE REQUIREMENTS**

|                  | PARAMETER                                   | TEST CONDITIONS                      | MIN | TYP  | MAX  | UNIT   |

|------------------|---------------------------------------------|--------------------------------------|-----|------|------|--------|

| f <sub>Ref</sub> | Reference Frequency                         |                                      |     | 18   |      | MHz    |

|                  | Temperature Stability                       | Customer Requirement                 |     |      |      |        |

| $V_{FR}$         | Reference Source Input Level <sup>(1)</sup> | HCMOS Output                         | 4   | 4.5  | 5    | Vpp    |

|                  | Reference Input Symmetry                    | Waveform Duty Cycle                  | 40% |      | 60%  |        |

| $\tau_{FR}$      | Waveform Pulse Rise Time                    | 10% to 90% of max voltage transition |     | 1    | 4    | nsec   |

| $\phi_{FR}$      | SSB Phase Noise at 10 kHz                   |                                      |     | -153 | -150 | dBc/Hz |

(1) Note that for source peak-to-peak voltage of less than 4 V and dc component other than 2.5-V degradation of the close-in phase noise may occur. For oscillators with no dc component, a dc voltage may be applied using a voltage divider (see the schematic).

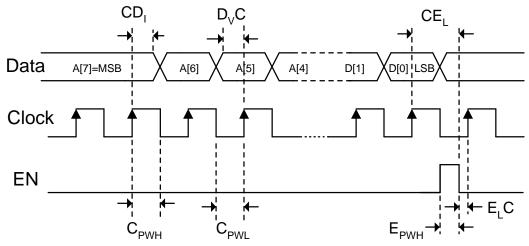

## AC TIMING, SERIAL BUS INTERFACE

| SERIAL INTERFACE TIMING CHARACTERISTICS (see Figure 9) |                        |                 |     |     |     |      |  |  |

|--------------------------------------------------------|------------------------|-----------------|-----|-----|-----|------|--|--|

|                                                        | PARAMETER              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |  |

| C <sub>DI</sub>                                        | Clock to Data Invalid  |                 | 10  |     |     | ns   |  |  |

| D <sub>V</sub> C                                       | Data Valid to Clock    |                 | 10  |     |     | ns   |  |  |

| C <sub>PWH</sub>                                       | Clock Pulse Width High |                 | 50  |     |     | ns   |  |  |

| C <sub>PWL</sub>                                       | Clock Pulse Width Low  |                 | 50  |     |     | ns   |  |  |

| CEL                                                    | Clock to Enable Low    |                 | 10  |     |     | ns   |  |  |

| $E_LC$                                                 | Enable Low to Clock    |                 | 10  |     |     | ns   |  |  |

| E <sub>PWH</sub>                                       | Enable Pulse Width     |                 | 10  |     |     | ns   |  |  |

## DIGITAL INTERFACE CHARACTERISTICS

|                 | PARAMETER                | TEST CONDITIONS   | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------|-------------------|-----|-----|-----|------|

| V <sub>IH</sub> | Input High Voltage       |                   | 2.1 |     | 5.0 | V    |

| V <sub>IL</sub> | Input Low Voltage        |                   | 0   |     | 0.8 | V    |

| I <sub>IH</sub> | Input High Current       |                   | 0   |     | 50  | μΑ   |

| IIL             | Input Low Current        |                   | 0   |     | -50 | μΑ   |

| CI              | Input Capacitance        |                   |     | 3   |     | pF   |

| V <sub>OH</sub> | Output Logic 1 Voltage   | 0 to 100-µA load  | 2.4 |     | 3.6 | V    |

| R <sub>OH</sub> | Output Logic 1 Impedance |                   |     | 18  |     | kΩ   |

| V <sub>OL</sub> | Output Low Voltage       | 0 to -100-µA load | 0   |     | 0.4 | V    |

# AUXILIARY, AGC, AND CONTROL FUNCTIONS

|                      | PARAMETER                   | TEST CONDITIONS                                                                                                                                               | MIN  | TYP  | MAX | UNIT |

|----------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| V <sub>VCOenbl</sub> | External VCO Enable Voltage | CMOS compatible Input. See the<br>Synthesizer #1 (S-Band PLL)<br>Characteristics table.                                                                       |      |      |     | V    |

| V <sub>LD1</sub>     | Lock Detect Voltage (PLL1)  | CMOS compatible Output (active high). See<br>the Synthesizer #1 (S-Band PLL)<br>Characteristics table.                                                        |      |      |     | V    |

| $V_{LD2}$            | Lock Detect Voltage (PLL2)  | CMOS compatible Output (active high). See<br>the Synthesizer #1 (S-Band PLL)<br>Characteristics table.                                                        |      |      |     | V    |

| V <sub>AGCI</sub>    | Gain Control Input          |                                                                                                                                                               | 0    |      | 3   | V    |

| V <sub>AGCO</sub>    | Gain Control Output         | When loaded with $10$ -k $\Omega$ load. Output impedance of AGCO is $3.75$ k $\Omega$ . Texas Instruments RF ASICs present a $10$ -k $\Omega$ load impedance. | 0    |      | 1.5 | V    |

| A <sub>AGC2</sub>    | VAGCO Accuracy              | V <sub>AGCO</sub> vs V <sub>AGCI</sub> characteristic                                                                                                         | ±100 |      |     | mV   |

| V <sub>DET</sub>     | Detector Output Voltage     |                                                                                                                                                               | TBD  |      |     | mV   |

| A <sub>VDET</sub>    | Detector Accuracy           |                                                                                                                                                               | TBD  |      |     | mV   |

| V <sub>BGR</sub>     | Band-Gap Reference Voltage  |                                                                                                                                                               | 1.17 |      |     | V    |

| t <sub>RBB</sub>     | AGC Time Constant           | Set by external loop filter                                                                                                                                   | TBD  |      |     | μs   |

| EXTLOIP              | On-chip VCO1 selection      | Logic level applied to EXTLOIP and                                                                                                                            |      | High |     |      |

| EXTLOIN              |                             | EXTLOIN pins to select the on-chip VCO                                                                                                                        |      | High |     |      |

| EXTLOIP              |                             | Logic Level applied to EXTLOIP and                                                                                                                            |      | Low  |     |      |

| EXTLOIN              | Off-chip VCO1 selection     | EXTLOIN pins to select the off-chip (external) VCO.                                                                                                           |      | Low  |     |      |

The V<sub>AGCO</sub> vs V<sub>AGCI</sub> is the voltage-transfer-function as defined by Table 1 when the AGCO is loaded with 10 k $\Omega$ . Note: The RFAGC pin on Texas Instruments RF downconverters (such as: TRF1111, TRF1115, or TRF1216) have an internal load of 10 k $\Omega$  and consequently the user should not add a separate 10-k $\Omega$  load resistor.

#### Table 1. AGCO Voltage vs AGCI Voltage

| VAGCI | V | 0.0 | 0.1 | 0.2  | 0.3  | 0.4 | 0.5 | 0.6 | >0.6 |

|-------|---|-----|-----|------|------|-----|-----|-----|------|

| VAGCO | V | 1.5 | 1.2 | 0.85 | 0.55 | 0.2 | 0.0 | 0.0 | 0.0  |

## **FREQUENCY PLAN**

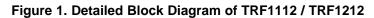

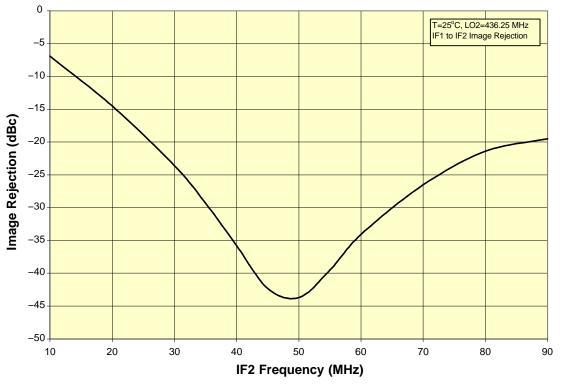

The TRF1112 / TRF1212 allow a variety of frequency plans. Figure 2 illustrates the allowable combinations of first and second IFs. However, due to the fact that the chips feature image-reject mixers, significant changes in the frequency plan can result in degradation of image rejection. This phenomenon is captured in Figure 3.

In order to maintain maximum image rejection and LO suppression, a recommended frequency plan is: RxIF1 = 480 MHz, RxIF2 = 43.75 MHz.

Figure 3. Image Rejection vs IF2

## **RECEIVE GAIN CONTROL**

The TRF1112 / TRF1212 offers two methods for gain control. Gain can be adjusted via an external analog signal (0-3 V) or by using the on-chip detector, voltage reference and operational amplifier.

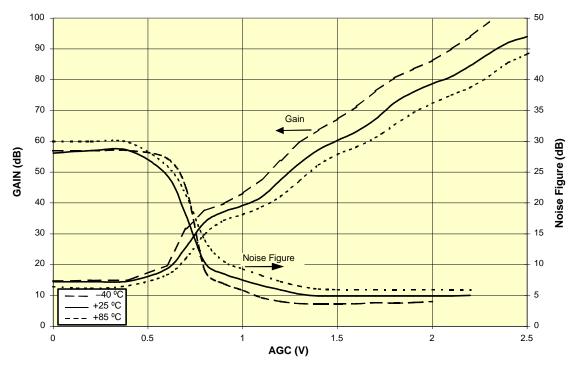

The gain-response curve is shown in Figure 4 and is designed to be monotonic for a 0-V to 3-V input analog voltage. This voltage control (AGCI) can be used to keep a constant peak-to-peak differential voltage output from

the TRF1112 / TRF1212 to the baseband processor's ADC over a large input signal dynamic range. The recommended TRF1112 / TRF1212 differential output level is 1.2 Vpp. The ASIC AGC output pin (AGCO) can be used to control the gain of a front-end downconverter for improved system dynamic range. In order to minimize the receiver's noise figure, the gain is changed in a stepped fashion. This means as the input signal level decreases, the gain shifts from the front-end stages to the back-end stages of the chip. This approach allows the noise figure to remain low until large input signals are present.

### Closed-Loop AGC

In order to achieve very fast signal acquisition in applications such as burst-mode transmission, Texas Instruments offers a receive gain control loop that requires no interaction from the demodulator. The internal loop operates by comparing the output of an internal peak detector to an internal voltage reference and adjusting the gain of the receive chain such that a constant voltage is achieved over a large input signal dynamic range. The internal AGC speed is set by an external AGC loop filter, the speed of which should be set low enough so that the AGC loop will not remove any carrier AM modulation.

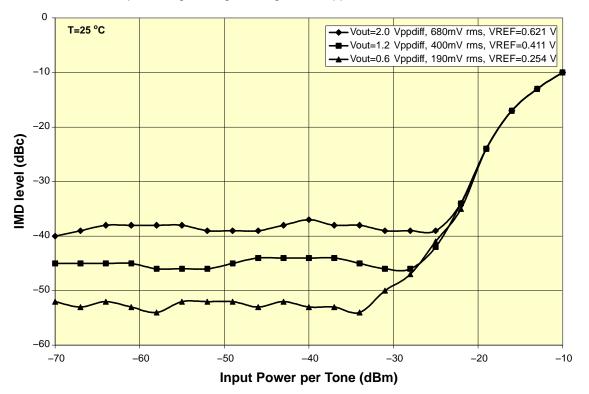

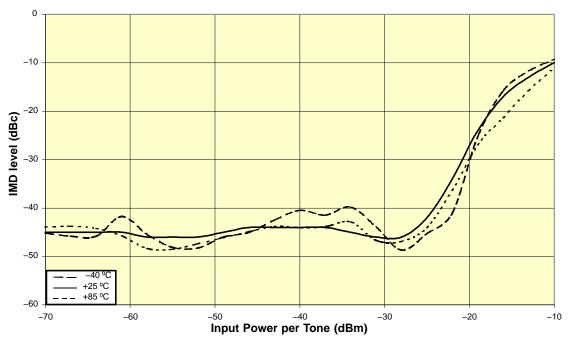

Careful attention to the ASIC architecture enables excellent 3<sup>rd</sup> order intermodulation distortion (IMD) performance over the entire AGC range as shown in Figure 4 and Figure 5. In these figures, VREF refers to the reference voltage setting on the VREF pin which is used to set the output voltage swing when configured for internal AGC. Vout is the output voltage swing at IF2 given in Vpp differential or rms.

Figure 4. IMD Level vs Input Power and AGC Output Setting (IF2 BPF Loss of 15 dB Included in Plot)

Figure 5. IMD Level vs Temperature at Output AGC Setting of 1.2-Vpp Differential (IF2 Filter Loss of 15 dB Included)

### External Analog Control

Receive signal gain control can also be accomplished through direct interaction with the modem. For example, the modem can look at several metrics on the incoming signal including voltage swing, SNR, and AGC error, then feedback an analog (0 V to 3 V) gain control signal to the Texas Instruments ASIC. Note that for applications requiring large channel bandwidths (e.g., 6 MHz) the maximum usable VAGCI should be limited to approximately 2 V to 2.5 V, otherwise the resulting gain produces excessive amounts of noise at the output.

Texas truments

www.ti.com

Figure 6. TRF1112 / TRF1212 Gain vs AGCI Voltage (IF2 BPF Loss of 15 dB Included)

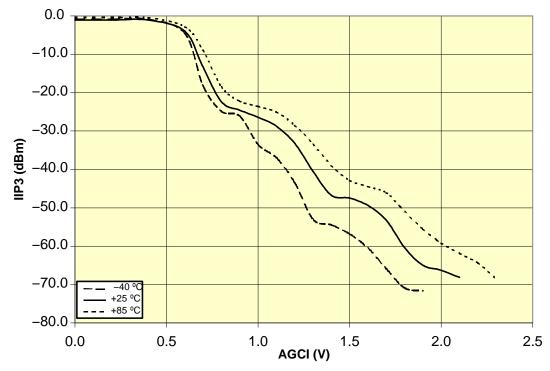

Figure 7 shows the input third-order intercept point (IIP3) vs  $V_{AGCI}$  for open loop AGC operation. As expected, the IIP3 decreases with increasing gain (increasing  $V_{AGCI}$ ). The input P-1dB behaves in a similar way.

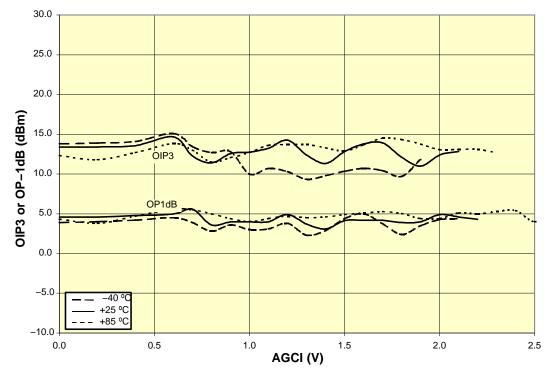

Figure 8 shows that the output P-1dB (OP-1dB) and output (OIP3) of the TRF1112 / TRF1212 is approximately constant vs the  $V_{AGCI}$  voltage.

Figure 8. OP-1dB and OIP3 vs AGCI Voltage and Temperature (IF2 BPF Loss of 15 dB Included)

## INTEGRATED SYNTHESIZERS

### **PLL Programming**

A UHF and S-band PLL are integrated in the TRF1112 / TRF1212. These two PLLs can be programmed via a 3-wire serial bus (CLK, DATA, and EN) from the baseband processor. The timing specs are given in the AC Timing table and detailed in Figure 9. Figure 10details the addresses and register values required to fully program the synthesizers.

NOTE: If left unconnected, the DATA, CLK and EN pins rest on logic High.

Figure 9. Serial Interface Timing Diagram

Data is written to the PLLs according to the following format:

IRF1112 TRF1212 SLWS175A-APRIL 2005-REVISED DECEMBER 2005

| MSB  |                                                   |      |      | Byt  | e 1  |      | LSB  | MSB   |       |       | Byte  | 2         |           |      | LSB  | MSB   |         |        | Byt  | e 3  |        |         | LSB  |

|------|---------------------------------------------------|------|------|------|------|------|------|-------|-------|-------|-------|-----------|-----------|------|------|-------|---------|--------|------|------|--------|---------|------|

|      |                                                   |      | Add  | ress |      |      |      |       |       |       |       |           |           |      | Data |       |         |        |      |      |        |         |      |

| A[7] | A[6]                                              | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | D[15] | D[14] | D[13] | D[12] | D[11]     | D[10]     | D[9] | D[8] | D[7]  | D[6]    | D[5]   | D[4] | D[3] | D[2]   | D[1]    | D[0] |

| 0    | 0                                                 | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0     |       | S     | ynth #1 N | l divider |      |      | Synth | #1 S co | ounter |      | Synt | h #1 F | divider |      |

| 0    | 0                                                 | 0    | 0    | 0    | 0    | 0    | 1    | 0     | 0     |       | S     | ynth #2 N | l divider |      |      | Synth | #2 S co | ounter |      | Synt | h #2 F | divider |      |

| 0    | 0                                                 | 0    | 0    | 0    | 1    | 0    | 0    | 0     | 0     | 0     | 0     | 0         | 0         | FS   | PS   | 0     | 0       | 0      | 0    | 0    | 0      | 0       | 0    |

|      | all other addresses reserved for future expansion |      |      |      |      |      |      |       |       |       |       |           |           |      |      |       |         |        |      |      |        |         |      |

| Figure 10  | . Serial | Interface   | Data | Format   |

|------------|----------|-------------|------|----------|

| i iguio io |          | millionauou | Dutu | I Olinat |

The first eight bits are the appropriate address for the instruction set and the remaining 16 bits are the instructions. The data is 24 bits long (3 bytes). Byte 1 is the address with A[7] being the MSB and A[0] being the LSB. Byte 2 and 3 program the IC with synthesizer information and PS (polarity select bit) information. D[15] is the MSB and D[8] the LSB. The PS bit selects which edge of the reference is used for frequency comparison. Improved spurious and phase noise is achieved by selected the edge with the fastest rise or fall time. If PS = 1, the rising edge is used as the reference. If PS = 0, the falling edge is used.

The filter select (FS) bit selects which receive filter path is enabled. If FS = 1, the *A* filter path is selected, if FS = 0 the *B* filter path is selected. This feature allows the user to control the receive signal bandwidth.

Each of the three lines in Figure 10 needs to be sent to the TRF1112 /TRF1212 to fully program the synthesizers, the FS bit, and the PS bit. Once the synthesizers and the FS/PS bits are fully programmed, the clock signal should be turned off to eliminate any clock-associated spurious signals

The UHF oscillator (LO2) frequency of oscillation is set by the following equation:

Fout = REFIN ×

$$\left[8 \times (N + 3) - S - \frac{F}{18}\right]/8$$

(1)

The S-band oscillator (LO1) frequency of oscillation is set by the following equation:

Fout = REFIN ×

$$\left[ 8 \times (N+3) - S - \frac{F}{18} \right]$$

(2)

where F has a range of 0 to 17. Both N and S have ranges that are limited more by the LO range than by their digital count.

Both synthesizers use a fractional architecture, which allows a high comparison frequency relative to the step size. The S-band PLL operates at a reference frequency of 18 MHz with a minimum phase accumulator frequency of 1 MHz. The UHF PLL operates at a 9-MHz reference with a minimum phase accumulator frequency of 0.5 MHz. The S-band PLL has a step size of 1 MHz and the UHF PLL has a step size of 125 kHz, when using an 18-MHz reference frequency. Different reference frequencies yield different step sizes, many of which are non-integer. If a different reference frequency is chosen, the step size is linearly related to the step size for 18 MHz.

Step size = step size<sub>18MHz</sub> x [REF FREQ/18 MHz]

In addition to normal reference spurious signals, fractional synthesizers have fractional spurs. The fractional spurs occur at an offset from the LO signal that is dependent on the difference between the LO frequency and integer multiples of the reference frequency. The spur locations can be found by the following process: divide the LO frequency by the reference frequency, take the remainder (fraction to the right of the whole number) and multiply by the reference frequency. This frequency is the difference between the actual LO frequency and an integer multiple of reference frequency. Fractional spurs will occur at this frequency and the reference frequency minus this frequency.

An example will best explain the process: if LO1 is set to 2206 MHz and an 18-MHz reference frequency is used, then 2206/18 is 122.55556. The difference between the LO1 and  $122 \times 18$  MHz is:

0.55556 x 18 MHz = 10 MHz

The fractional spurs will occur at this frequency offset (10 MHz) from LO1 and:

18 MHz–10 MHz or 8 MHz from LO1.

The fractional spurious level varies with the offset from the LO since these spurious signals are attenuated by the loop filter response. The larger the offset from the LO, the lower the spur level. In general, spurs at offsets greater than 3 or 4 MHz are below –75 dBc and are not a concern. The worst fractional spurs levels occur when they are located at 1 MHz offset from the LO1 frequency. (Note: the fractional spur is offset from the LO1 frequency by 1 MHz when the difference between the LO1 and an integer multiple of the reference frequency is 1 or 17 MHz.)

Although both synthesizers have fractional spurs, for most applications the spurious signals from the UHF (LO2) synthesizer can be ignored because these spurs are attenuated by frequency dividers that are placed after the LO2 generation. In some frequency plans it is possible to offset LO1 and LO2, in a complementary manner, to avoid worst-case fractional spurs (i.e., 1-MHz offsets) on LO1 synthesizer.

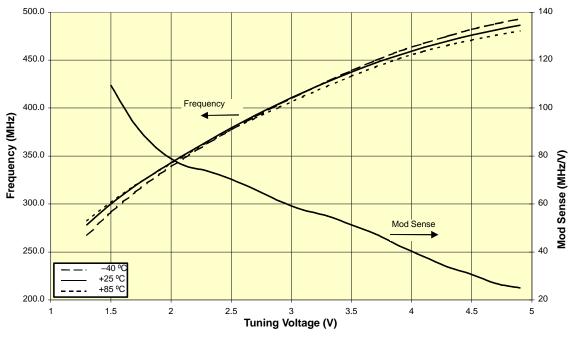

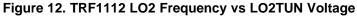

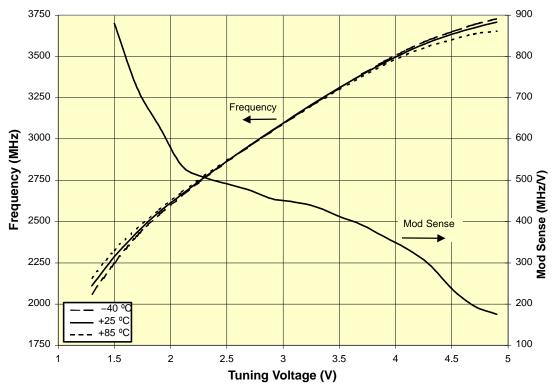

### **VCO Tuning Characteristics**

2500 700 2250 600 2000 Frequency 500 Frequency (MHz) 1750 400 Mod Sense (MHz/V) 1500 300 Mod Sense 1250 200 -40 +25 °C +85 °C 1000 100 1.5 2.5 2 3.5 4 4.5 5 3 1 Tuning Voltage (V)

The TRF1121 / TRF1221 internal VCOs have the following frequency vs tune voltage characteristics.

Figure 11. TRF1112 LO1 Frequency vs LO1TUN Voltage

Figure 14. TRF1212 LO2 Frequency vs LO2TUN Voltage

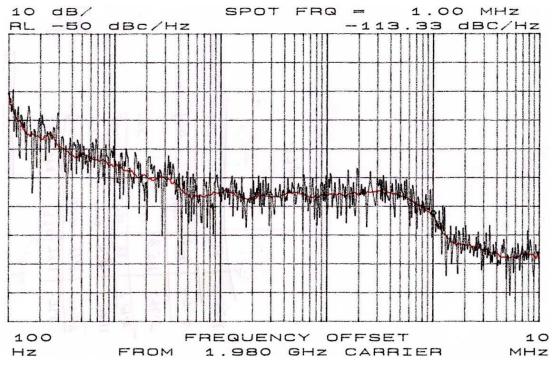

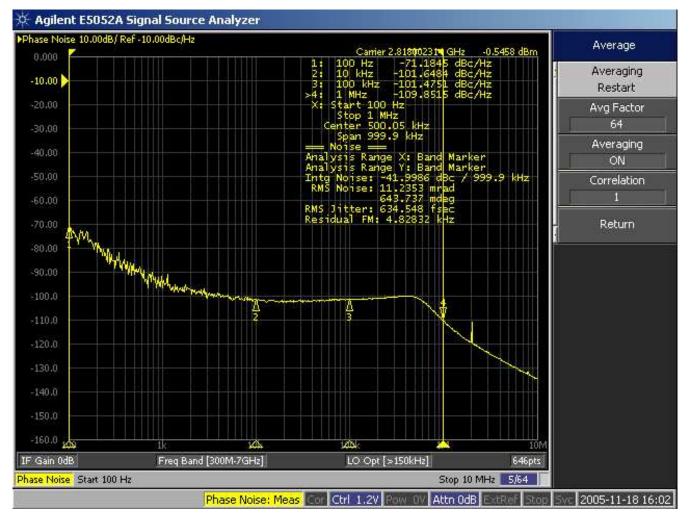

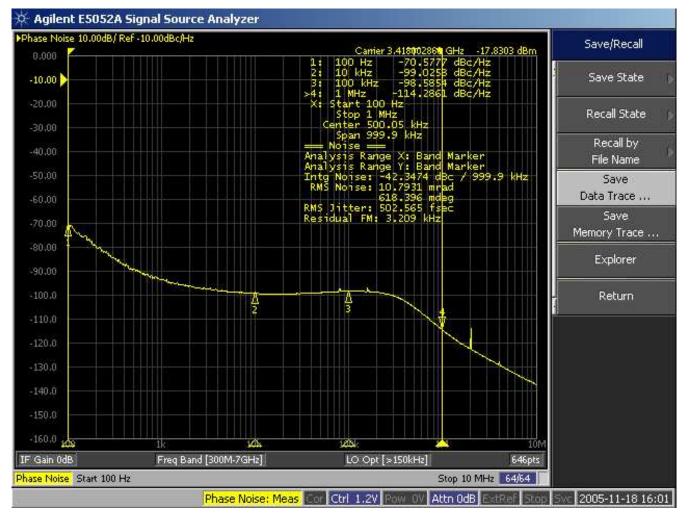

#### Phase Noise

The TRF1112 / TRF1212 achieve superior phase noise performance with on-chip resonators and varactors. They are designed to meet the phase noise requirements of both single carrier and multi-carrier systems. Due to chip architecture, the phase noise and spurious performance of the LO2 (UHF) PLL is about 15 dB better than the LO1 (S-band) PLL. The typical phase noise of the TRF1112 and TRF1212 S-Band PLL (LO1) with the PLL locked is shown in Figure 15 and Figure 16, respectively. The phase noise of the TRF1212 S-Band PLL at the min and max range are shown in Figure 17 and Figure 18 respectively. These plots were taken at room temperature and typical voltage conditions.

Figure 15. Phase Noise of TRF1112 Synthesizer #1 – Typical Performance is 0.4 RMS (100 Hz to 1 MHz)

Figure 16. Phase Noise of the TRF1212 Synthesizer #1 – Typical Performance is 0.6 RMS (100 Hz to 1 MHz)

TRF1112 TRF1212 SLWS175A-APRIL 2005-REVISED DECEMBER 2005

Figure 17. TRF1212 S-Band Synthesizer Phase Noise - 2818 MHz

Figure 18. TRF1212 S-Band Synthesizer Phase Noise - 3418 MHz

For applications demanding tighter phase noise performance than that offered by Texas Instruments internal VCOs, a provision exists for connection of an external VCO. Texas Instruments integrated PLL locks the external VCO to the reference frequency and the chip provides an external tuning voltage that drives the VCO.

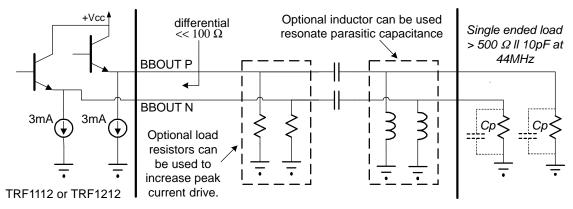

## **OUTPUT A/D INTERFACE**

The output of the baseband amplifier is designed to directly drive typical A/D inputs. The output IF2 buffer amplifiers are low impedance emitter followers as shown in Figure 19.

Figure 19. Output Interface for TRF1112 / TRF1212

The peak current drive of the output transistors is 3 mA. Assuming a 1.2-Vpp differential (0.6 V single ended) voltage swing, the minimum impedance the TRF1112 / TRF1212 drives without clipping is 0.6 V/3 mA = 200  $\Omega$ , single-ended. In practice the impedance must be higher to prevent distortion products from degrading BER of the receiver. This impedance must include the A/D input capacitance and any parasitic board capacitance. At 44 MHz, the TRF1112 / TRF1212 drives a differential impedance of 1000  $\Omega$  (single ended impedance of 500  $\Omega$ ) with up to a 10-pF capacitive load (293- $\Omega$  single-ended impedance) and maintain 38-dBc intermodulation products with 64 QAM modulation. Proper attention to layout and reduction of parasitic capacitance at this interface is critical to avoid linearity degradation. At higher IF frequencies parasitic capacitance is even more critical.

If parasitic capacitance is loading the output and degrading intermodulation performance there are two approaches to solve the problem. First a shunt inductor can be added to resonate the capacitance. The inductor value would be determined by:  $L = 1/\omega^2 Cp$ , where Cp is the parasitic capacitance and  $\omega$  is  $2\pi$  times the baseband receive IF frequency. Frequently this inductor can be part of the bias network for the ADC.

Second, the peak output current drive can be increased by adding a shunt resistor across the output of each baseband output. This resistor will essentially increase the quiescent current through the output transistor thus allowing a higher peak output current. The maximum **increase** in quiescent current is 3 mA resulting in a maximum allowable peak current of 6 mA. If load resistors are added, their resistance must be included to calculate total load impedance for the TRF1112 / TRF1212.

## **APPLICATION INFORMATION**

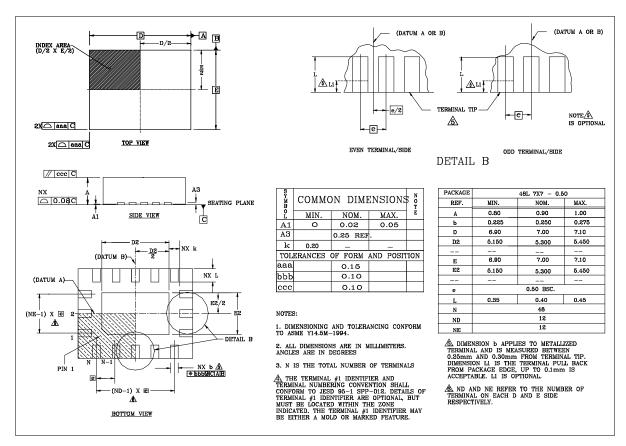

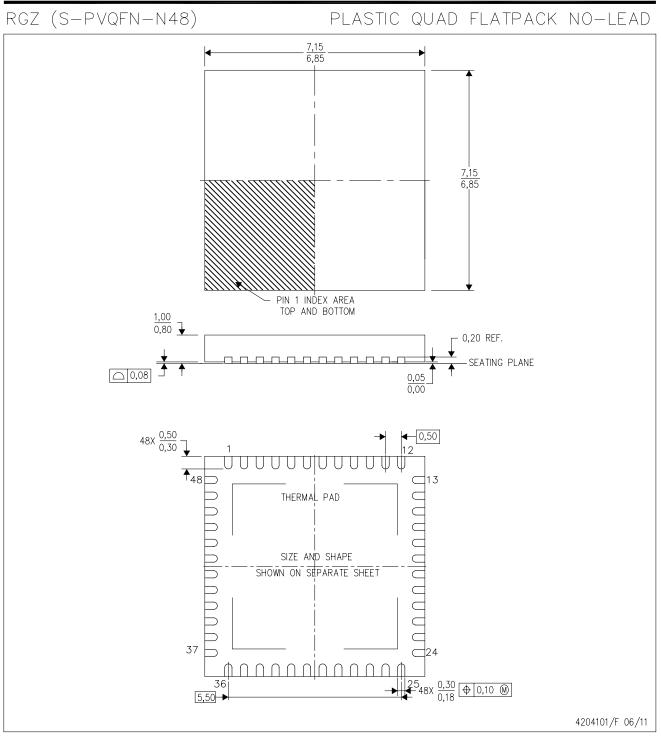

A typical application schematic is shown in Figure 20 and a mechanical drawing of the package outline (LPCC Quad 7 mm  $\times$  7 mm, 48-pin) is shown in Figure 21.

Figure 20. Recommended TRF1112/TRF1212 Application Schematic

## **APPLICATION INFORMATION (continued)**

Figure 21. Package Drawing

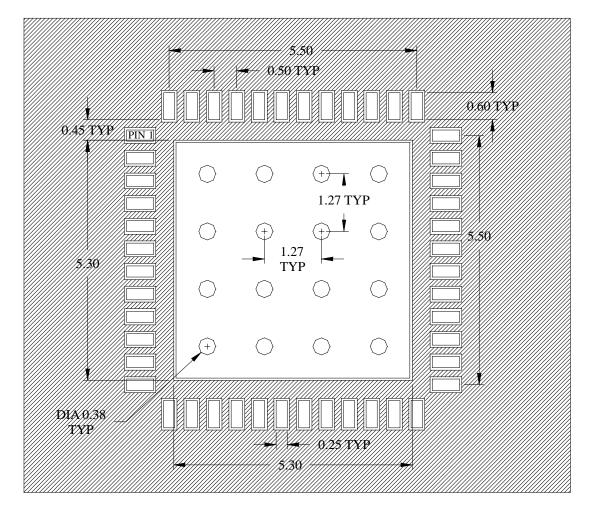

The recommended PCB Layout mask is shown in Figure 22, along with recommendations on the board material (see Table 2) and construction (see Figure 23).

| Board Material                | FR4                 |

|-------------------------------|---------------------|

| Board Material Core Thickness | 10 mil              |

| Copper Thickness (starting)   | 1 oz                |

| Prepreg Thickness             | 8 mil               |

| Recommended Number of Layers  | 4                   |

| Via Plating Thickness         | ½ 0Z                |

| Final Plate                   | White immersion tin |

| Final Board Thickness         | 33–37 mil           |

| Table 2 | PCB | Recommendations |

|---------|-----|-----------------|

|---------|-----|-----------------|

SOLDER MASK: NO SOLDERMASK UNDER CHIP, ON LEAD PADS OR ON GROUND CONNECTIONS.

16 VIA HOLES, EACH 0.38 mm.

DIMENSIONS in mm

Figure 22. Recommended Pad Layout

Figure 23. PCB Via Cross Section

24-Jan-2013

## PACKAGING INFORMATION

| Orderable Device | Status      | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan                          | Lead/Ball Finish | •                          | Op Temp (°C) |                    | Samples |

|------------------|-------------|--------------|--------------------|------|-------------|-----------------------------------|------------------|----------------------------|--------------|--------------------|---------|

| PTRF1212IRGZR    | (1)<br>NRND | VQFN         | RGZ                | 48   |             | (2)<br>Green (RoHS<br>& no Sb/Br) | CU SN            | (3)<br>Level-3-260C-168 HR | -40 to 85    | (4)<br>TRF<br>1212 |         |

| TRF1112IRGZR     | NRND        | VQFN         | RGZ                | 48   | 2500        | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1112        |         |

| TRF1112IRGZRG3   | NRND        | VQFN         | RGZ                | 48   | 2500        | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1112        |         |

| TRF1112IRGZT     | NRND        | VQFN         | RGZ                | 48   | 250         | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1112        |         |

| TRF1112IRGZTG3   | NRND        | VQFN         | RGZ                | 48   | 250         | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        |              | TRF<br>1112        |         |

| TRF1212IRGZR     | NRND        | VQFN         | RGZ                | 48   | 2500        | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1212        |         |

| TRF1212IRGZRG3   | NRND        | VQFN         | RGZ                | 48   | 2500        | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1212        |         |

| TRF1212IRGZT     | NRND        | VQFN         | RGZ                | 48   | 250         | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1212        |         |

| TRF1212IRGZTG3   | NRND        | VQFN         | RGZ                | 48   | 250         | Green (RoHS<br>& no Sb/Br)        | CU SN            | Level-3-260C-168 HR        | -40 to 85    | TRF<br>1212        |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

www.ti.com

24-Jan-2013

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

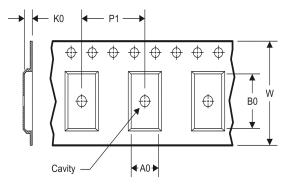

## TAPE AND REEL INFORMATION

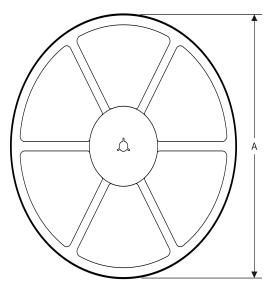

#### REEL DIMENSIONS

Texas Instruments

TAPE AND REEL INFORMATION

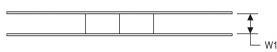

#### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

| All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TRF1112IRGZR               | VQFN            | RGZ                | 48 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

| TRF1112IRGZT               | VQFN            | RGZ                | 48 | 250  | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

| TRF1212IRGZR               | VQFN            | RGZ                | 48 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

| TRF1212IRGZT               | VQFN            | RGZ                | 48 | 250  | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

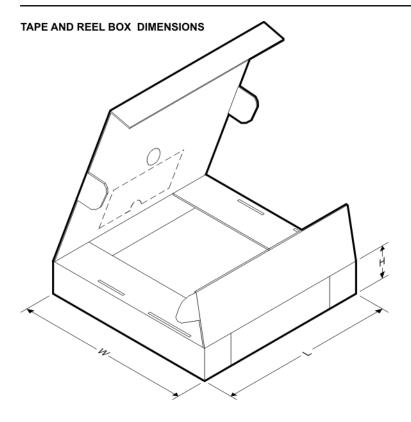

# PACKAGE MATERIALS INFORMATION

20-Jul-2012

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TRF1112IRGZR | VQFN         | RGZ             | 48   | 2500 | 336.6       | 336.6      | 28.6        |

| TRF1112IRGZT | VQFN         | RGZ             | 48   | 250  | 336.6       | 336.6      | 28.6        |

| TRF1212IRGZR | VQFN         | RGZ             | 48   | 2500 | 336.6       | 336.6      | 28.6        |

| TRF1212IRGZT | VQFN         | RGZ             | 48   | 250  | 336.6       | 336.6      | 28.6        |

# **MECHANICAL DATA**

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

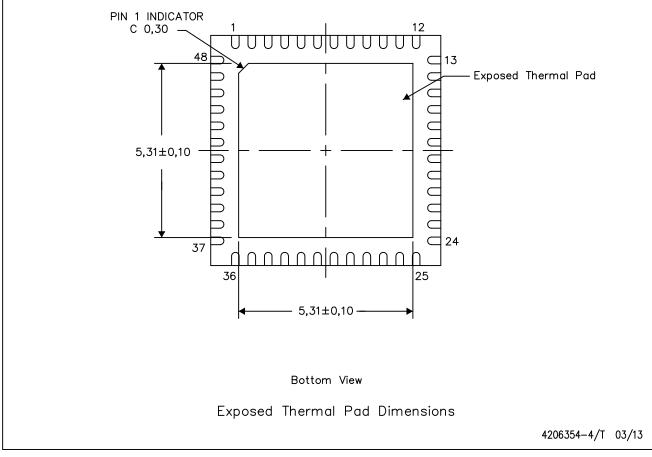

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

F. Falls within JEDEC MO-220.

# RGZ (S-PVQFN-N48) PLASTIC QUAD FLATPACK NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated