SLWS224C - AUGUST 2010 - REVISED MAY 2012

# Integrated IQ Modulator PLL/VCO

# FEATURES

- Fully Integrated PLL/VCO and IQ Modulator

- LO Frequency from 300MHz to 4.8GHz

- 76-dBc Single-Carrier WCDMA ACPR at –8dBm Channel Power

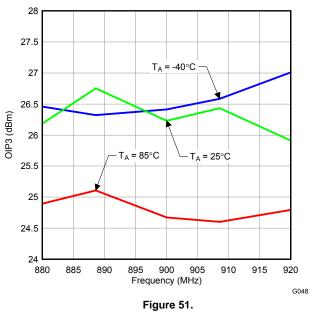

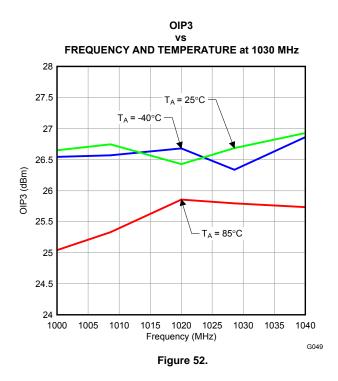

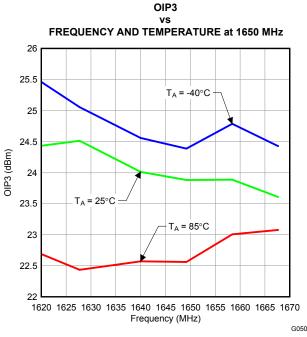

- OIP3 of 26 dBm

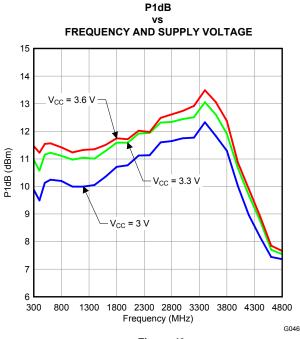

- P1dB of 11.5 dBm

- Integer/Fractional PLL

- Phase Noise –132 dBc/Hz (at 1MHz, f<sub>vCO</sub> of 2.3 GHz)

- Low Noise Floor: -160 dBm/Hz

- Input Reference Frequency Range: Up to 160MHz

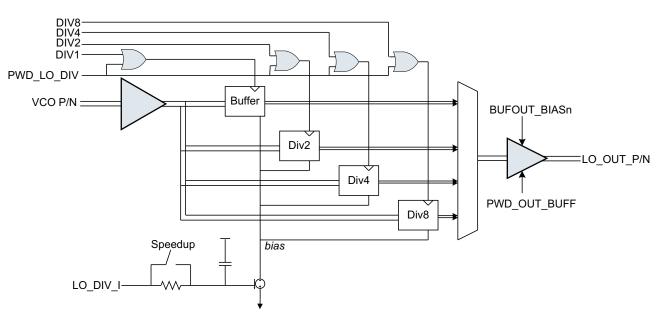

- VCO Frequency Divided by 1-2-4-8 Output

# **APPLICATIONS**

- Wireless Infrastructure

- CDMA: IS95, UMTS, CDMA2000, TD-SCDMA

- TDMA: GSM, IS-136, EDGE/UWC-136

- LTE

- Wireless Local Loop

- Point-to-Point Wireless Access

- Wireless MAN Wideband Transceivers

# DESCRIPTION

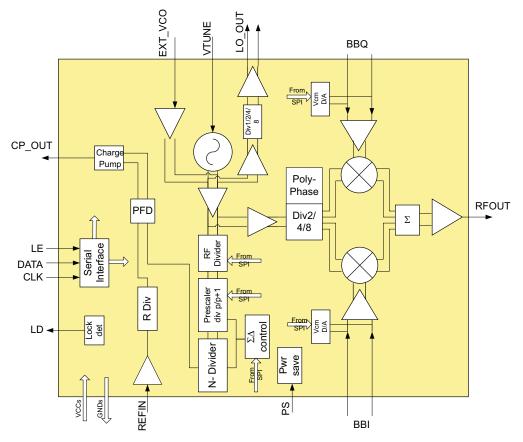

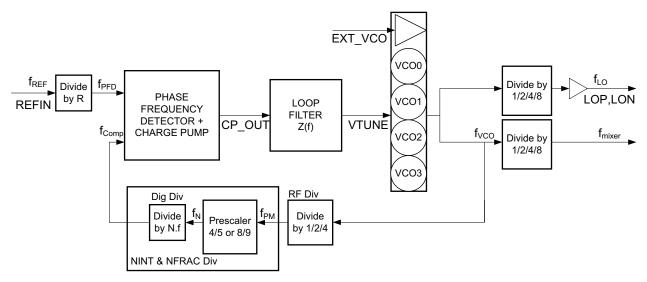

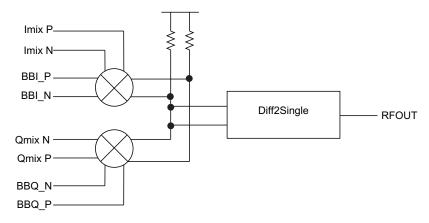

TRF372017 is a high performance direct up-conversion device, integrating a high linearity, low noise IQ modulator and an integer-fractional PLL/VCO. The VCO uses integrated frequency dividers to achieve a wide, continuous tuning range of 300MHz–4800MHz. The LO is available as an output with independent frequency dividers. The device also accepts input from an external LO or VCO. The modulator baseband inputs can be biased either internally or externally. Internal DC offset adjustment enables carrier cancellation. The device is controlled through a 3 wire serial programming interface (SPI). A control pin invokes power-save mode to reduce power consumption while keeping the VCO locked for fast startup.

### FREQUENCY RANGE OPERATION

| VCO Fr | equency | Div by 2 |      | Div by 4 |      | Div by 8 |      |

|--------|---------|----------|------|----------|------|----------|------|

| Fmin   | Fmax    | Fmin     | Fmax | Fmin     | Fmax | Fmin     | Fmax |

| 2400   | 4800    | 1200     | 2400 | 600      | 1200 | 300      | 600  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# TRF372017

### SLWS224C-AUGUST 2010-REVISED MAY 2012

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

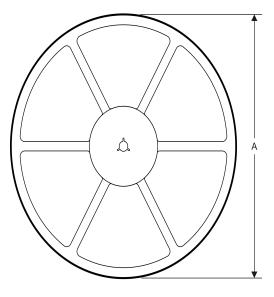

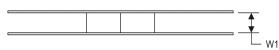

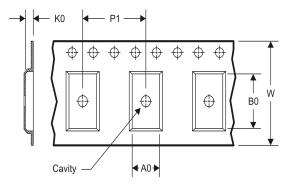

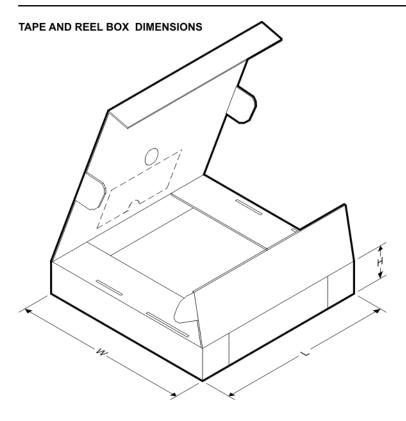

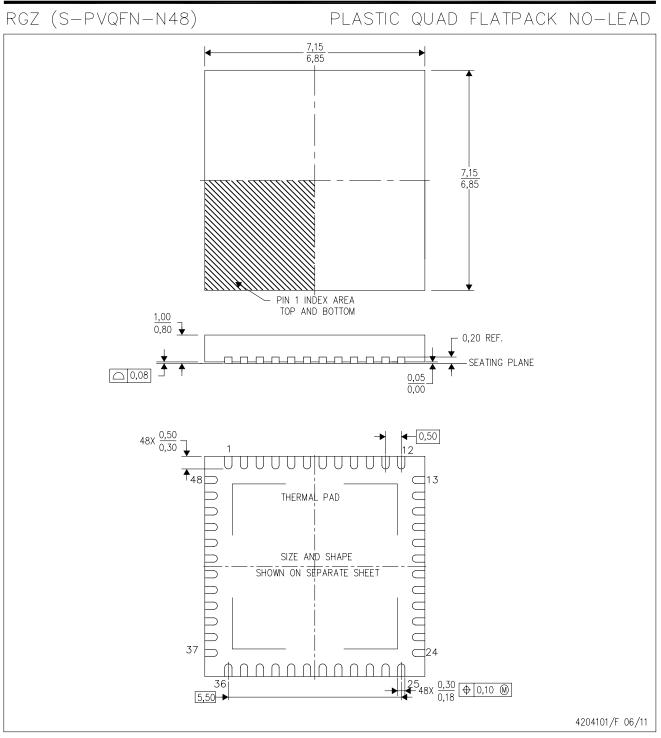

### AVAILABLE DEVICE OPTIONS

| PRODUCT        | PACKAGE<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>OPERATING<br>TEMPERATURE | PACKAGE<br>MARKING | MEDIA, QUANTITY     |

|----------------|-----------------|-----------------------|---------------------------------------|--------------------|---------------------|

| TRF372017IRGZT | QFN-48          | RGZ                   | –40°C to 85°C                         | TRF372017          | Tape and Reel, 250  |

| TRF372017IRGZR | QFN-48          | RGZ                   | –40°C to 85°C                         | TRF372017          | Tape and Reel, 2500 |

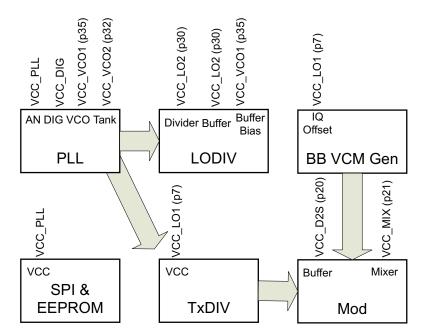

# FUNCTIONAL BLOCK DIAGRAM

Figure 1. TRF372017 Block Diagram

# TRF372017

SLWS224C - AUGUST 2010 - REVISED MAY 2012

www.ti.com

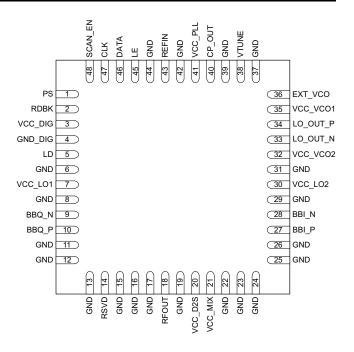

# PIN FUNCTIONS

| PIN      |    |      |                                                                        |

|----------|----|------|------------------------------------------------------------------------|

| NAME     | NO | TYPE | DESCRIPTION                                                            |

| PS       | 1  | I    | Power saving mode enable (Low = normal mode; High = power saving mode) |

| RDBK     | 2  | 0    | SPI internal registers readback output                                 |

| VCC_DIG  | 3  |      | 3.3V digital power supply                                              |

| GND_DIG  | 4  |      | Digital ground                                                         |

| LD       | 5  | 0    | PLL lock detect output                                                 |

| GND      | 6  |      | Ground                                                                 |

| VCC_LO1  | 7  |      | 3.3V Tx path local oscillator chain power supply                       |

| GND      | 8  |      | Ground                                                                 |

| BBQ_N    | 9  | I    | Base-band in-quadrature input: negative terminal                       |

| BBQ_P    | 10 | I    | Base-band in-quadrature input: positive terminal                       |

| GND      | 11 |      | Ground                                                                 |

| GND      | 12 |      | Ground                                                                 |

| GND      | 13 |      | Ground                                                                 |

| RSVD     | 14 |      | Reserved. Normally open.                                               |

| GND      | 15 |      | Ground                                                                 |

| GND      | 16 |      | Ground                                                                 |

| GND      | 17 |      | Ground                                                                 |

| RFOUT    | 18 | 0    | RF output                                                              |

| GND      | 19 |      | Ground                                                                 |

| VCC_D2S  | 20 |      | 5V modulator output buffer power supply                                |

| VCC_MIX  | 21 |      | 5V modulator power supply                                              |

| GND      | 22 |      | Ground                                                                 |

| GND      | 23 |      | Ground                                                                 |

| GND      | 24 |      | Ground                                                                 |

| GND      | 25 |      | Ground                                                                 |

| GND      | 26 |      | Ground                                                                 |

| BBI_P    | 27 | Ι    | Base-band in-phase input: positive terminal                            |

| BBI_N    | 28 | I    | Base-band in-phase input: negative terminal                            |

| GND      | 29 |      | Ground                                                                 |

| VCC_LO2  | 30 |      | 3.3V output local oscillator chain power supply                        |

| GND      | 31 |      | Ground                                                                 |

| VCC_VCO2 | 32 |      | 3.3 – 5.0V VCO power supply                                            |

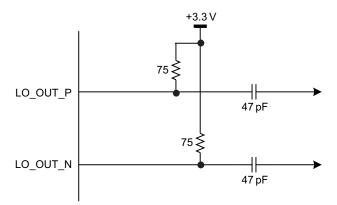

| LO_OUT_N | 33 | 0    | Local oscillator output: negative terminal                             |

| LO_OUT_P | 34 | 0    | Local oscillator output: positive terminal                             |

| VCC_VCO1 | 35 |      | 3.3V VCO power supply                                                  |

| EXT_VCO  | 36 | I    | External local oscillator input                                        |

| GND      | 37 |      | Ground                                                                 |

| VTUNE    | 38 | I    | VCO control voltage input                                              |

| GND      | 39 |      | Ground                                                                 |

| CP_OUT   | 40 | 0    | Charge pump output                                                     |

| VCC_PLL  | 41 |      | 3.3V PLL power supply                                                  |

| GND      | 42 |      | Ground                                                                 |

| REFIN    | 43 | I    | Reference clock input                                                  |

| GND      | 44 |      | Ground                                                                 |

| LE       | 45 | I    | SPI latch enable. Digital input                                        |

| DATA     | 46 | I    | SPI data input. Digital input                                          |

### PIN FUNCTIONS (continued)

| PIN     |    | TYPE | DESCRIPTION                                                  |  |

|---------|----|------|--------------------------------------------------------------|--|

| NAME    | NO | TTPE | DESCRIPTION                                                  |  |

| CLK     | 47 | I    | SPI clock input. Digital input                               |  |

| SCAN_EN | 48 | I    | Internal testing mode. Connect to ground in normal operation |  |

### THERMAL INFORMATION

|                  |                                              | TRF372017 |       |

|------------------|----------------------------------------------|-----------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | RGZ       | UNITS |

|                  |                                              | 48 PINS   |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 30        |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 10        |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 8         | °C/W  |

| ΨJT              | Junction-to-top characterization parameter   | 0.5       | °C/w  |

| ΨJB              | Junction-to-board characterization parameter | 7         |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.5       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1) (2)</sup>

|                                                     | VALUE                         | UNIT |

|-----------------------------------------------------|-------------------------------|------|

| Supply voltage range <sup>(3)</sup>                 | -0.3 to 5.5                   | V    |

| Digital I/O voltage range                           | –0.3 to V <sub>CC</sub> + 0.5 | V    |

| Operating virtual junction temperature range, $T_J$ | -40 to 150                    | °C   |

| Operating ambient temperature range, T <sub>A</sub> | -40 to 85                     | °C   |

| Storage temperature range, T <sub>stg</sub>         | -40 to 150                    | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) ESD rating not valid for RF sensitive pins.

(3) All voltage values are with respect to network ground terminal.

# **RECOMMENDED OPERATING CONDITIONS**

|                   |                                              | MIN | NOM | MAX | UNIT |

|-------------------|----------------------------------------------|-----|-----|-----|------|

| V <sub>CC5V</sub> | 5V Power supply voltage                      | 4.5 | 5.0 | 5.5 | V    |

| V <sub>CC3V</sub> | 3.3V Power supply voltage                    | 3.0 | 3.3 | 3.6 | V    |

| VCC_VCO2          | 3.3–5V Power supply voltage                  | 3.0 | 3.3 | 5.5 | V    |

| T <sub>A</sub>    | Operating ambient temperature range          | -40 |     | 85  | °C   |

| TJ                | Operating virtual junction temperature range | -40 |     | 125 | °C   |

#### www.ti.com

### ELECTRICAL CHARACTERISTICS

$V_{CC5V} = 5.0V$ ,  $V_{CC3V} = 3.3V$ ,  $VCC_VCO2 = 3.3V$ ,  $T_A = 25^{\circ}C$ , internal LO, internal VCM (unless otherwise noted)

|                  | PARAMETER                                      | TEST CONDITIONS                                               | MIN     | TYP  | MAX     | UNIT |  |

|------------------|------------------------------------------------|---------------------------------------------------------------|---------|------|---------|------|--|

| DC PA            | RAMETERS                                       |                                                               |         |      |         |      |  |

|                  | Total august august 10 an <sup>(1)</sup>       | 3.3V power supply, LO on                                      |         | 200  | 250     | mA   |  |

| I <sub>CC</sub>  | Total supply current, LO on <sup>(1)</sup>     | 5V power supply, LO on                                        |         | 117  | 148     | mA   |  |

|                  |                                                | VCC_DIG, LO on                                                |         | 3    | 5       | mA   |  |

|                  |                                                | VCC_LO1 and VCC_LO2                                           |         | 121  | 130     | mA   |  |

|                  |                                                | VCC_D2S                                                       |         | 43   | 60      | mA   |  |

|                  | Supply current, LO on <sup>(1)</sup>           | VCC_MIX                                                       |         | 74   | 90      | mA   |  |

|                  | Supply current, LO on the                      | VCC_VCO1                                                      |         | 20   | 28      | 1    |  |

|                  |                                                | VCC_VCO2                                                      |         | 17   | 20      | mA   |  |

|                  |                                                | LO_OUT_N and LO_OUT_P                                         |         | 17   | 28      | mA   |  |

|                  |                                                | VCC_PLL                                                       |         | 24   | 40      | mA   |  |

|                  | Tetel complex compared 1 O off(1)              | 3.3V power supply, LO off                                     |         | 165  | 204     |      |  |

|                  | Total supply current, LO off <sup>(1)</sup>    | 5V power supply, LO off                                       |         | 117  | 149     | mA   |  |

|                  | Tatal and the second DO as (1)                 | 3.3V power supply, PS on                                      |         | 65   | 94      | mA   |  |

|                  | Total supply current, PS on <sup>(1)</sup>     | 5V power supply, PS on                                        |         | 51   | 73      | mA   |  |

| BASEB            | BAND INPUTS                                    |                                                               | - L     |      | ¥       |      |  |

|                  |                                                | Externally generated                                          |         | 1.7  |         | V    |  |

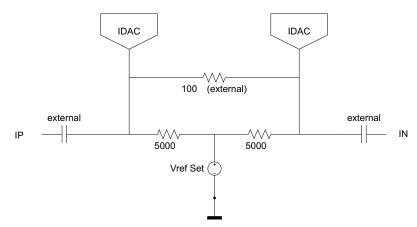

| V <sub>cm</sub>  | I and Q Input DC common voltage <sup>(2)</sup> | Set internally                                                | 1.6     | 1.7  | 1.85    | V    |  |

| BW               | 1dB Input frequency bandwidth                  |                                                               |         | 1000 |         | MHz  |  |

| 7                | Lengt Lenge de see                             | Resistance                                                    |         | 5    |         | kΩ   |  |

| ZI               | Input Impedance                                | Parallel Capacitance                                          |         | 3    |         | pF   |  |

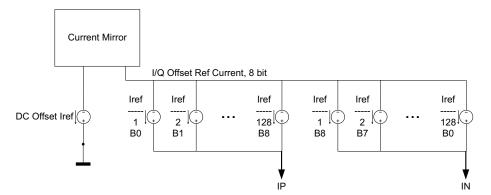

| BASEE            | BAND INPUT DC OFFSET CONTROL D/A               | (3)                                                           | *       |      | *       |      |  |

|                  | Number of bits                                 | Programmed via SPI                                            |         | 8    |         |      |  |

|                  | Programmable DC offset setting                 | BBI_P - BBI_N  or  BBQ_P - BBQ_N , 100-Ω<br>differential load |         |      | 0.02    | V    |  |

| DIGITA           | L INTERFACE                                    |                                                               |         |      |         |      |  |

| VIH              | High-level input voltage                       |                                                               | 2       | 3.3  |         | V    |  |

| V <sub>IL</sub>  | Low-level input voltage                        |                                                               | 0       |      | 0.8     | V    |  |

| V <sub>ОН</sub>  | High-level output voltage                      | Referenced to VCC_DIG                                         | 0.8xVcc |      |         | V    |  |

| V <sub>OL</sub>  | Low-level output voltage                       | Referenced to VCC_DIG                                         |         |      | 0.2xVcc | V    |  |

| REFER            | ENCE OSCILLATOR PARAMETERS                     |                                                               |         |      |         |      |  |

| F <sub>ref</sub> | Reference Frequency                            |                                                               |         |      | 160     | MHz  |  |

|                  | Reference input sensitivity                    |                                                               | 0.2     |      | 3.3     | Vp-p |  |

|                  | Deference input incredence                     | Parallel capacitance                                          |         | 5    |         | pF   |  |

|                  | Reference input impedance                      | Parallel resistance                                           | 3900    |      |         | Ω    |  |

| PFD CI           | HARGE PUMP                                     |                                                               |         |      | 1       |      |  |

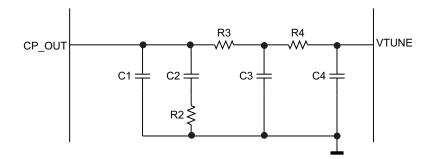

|                  | PFD frequency <sup>(4)</sup>                   |                                                               |         |      | 100     | MHz  |  |

| I <sub>CP</sub>  | Charge pump current                            | SPI programmable                                              |         | 1.94 |         | mA   |  |

(1) Maximum current is worst-case over voltage, temperature, and expected process variations.

(2) The TRF372017 can generate the input common voltage internally or can accept an external common mode voltage. The two modes are selectable via SPI

(3) When the internal input common mode voltage is selected, it is possible to apply some dc offset with the integrated D/A

(4) See Application Information for discussion on selection of PFD frequency.

# **TRF372017 ELECTRICAL CHARACTERISTICS**

$V_{CC5V} = 5.0V$ ,  $V_{CC3V} = 3.3V$ ,  $VCC_VCO2 = 3.3V$ ,  $T_A = 25^{\circ}C$ , internal LO, internal VCM (unless otherwise noted)

|      | PARAMETER                                | TEST CONDITIONS                                               | MIN  | TYP   | MAX  | UNIT   |

|------|------------------------------------------|---------------------------------------------------------------|------|-------|------|--------|

|      | JLATOR OUTPUT, F <sub>LO</sub> = 750 MHz | 2                                                             |      |       |      |        |

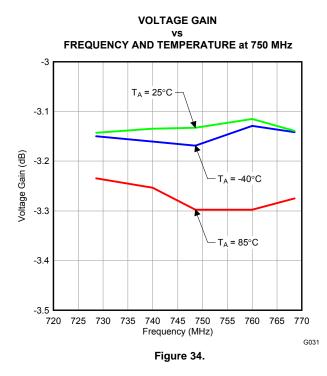

| G    | Voltage gain                             | Output rms voltage over se input I (or Q) rms voltage         | -4   | -3.2  | -2.4 | dB     |

| P1dB | Output compression point                 |                                                               |      | 11    |      | dBm    |

| IP3  | Output IP3                               | 2 input tones at 4.5 and 5.5MHz                               |      | 26    |      | dBm    |

| IP2  | Output IP2                               | 2 input tones at 4.5 and 5.5MHz                               |      | 56.5  |      | dBm    |

|      | Carrier feedthrough                      | Unadjusted                                                    |      | -43.5 |      | dBm    |

|      | Sideband suppression                     | Unadjusted                                                    |      | -46   |      | dBc    |

|      | Output return loss                       |                                                               |      | 10    |      | dB     |

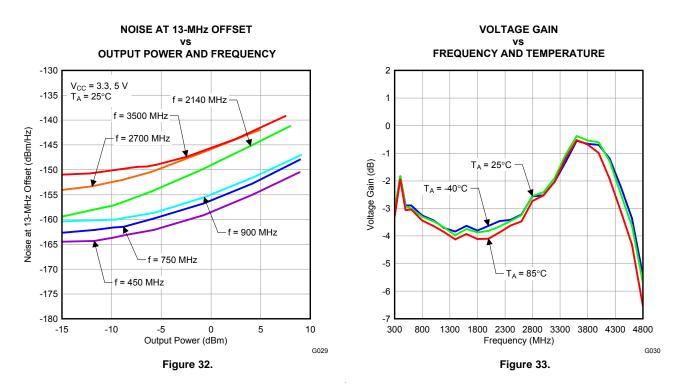

|      | Output noise                             | DC only to BB inputs; 13 MHz offset from LO; Pout = -10 dBm   |      | -162  |      | dBm/Hz |

|      | JLATOR OUTPUT, F <sub>LO</sub> = 900 MHz | 2                                                             |      |       |      |        |

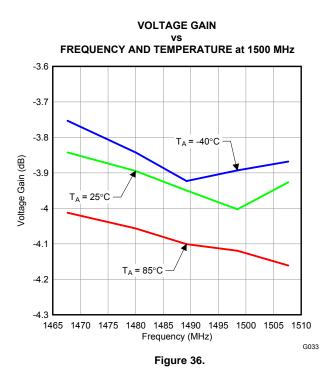

| G    | Voltage Gain                             | Output rms voltage over se input I (or Q) rms voltage         | -4   | -3.4  | -2.4 | dB     |

| P1dB | Output Compression Point                 |                                                               |      | 11    |      | dBm    |

| IP3  | Output IP3                               | 2 input tones at 4.5 and 5.5 MHz                              |      | 26.5  |      | dBm    |

| IP2  | Output IP2                               | 2 input tones at 4.5 and 5.5 MHz                              |      | 56.5  |      | dBm    |

|      | Carrier Feedthrough                      | Unadjusted                                                    |      | -43   |      | dBm    |

|      | Sideband suppression                     | Unadjusted                                                    |      | -45   |      | dBc    |

|      | Output Return Loss                       |                                                               |      | 10    |      | dB     |

|      | Output Noise                             | DC only to BB inputs; 13 MHz offset from LO; Pout = $-10$ dBm |      | -160  |      | dBm/Hz |

|      | JLATOR OUTPUT, F <sub>LO</sub> = 2150 MH | lz                                                            |      |       |      |        |

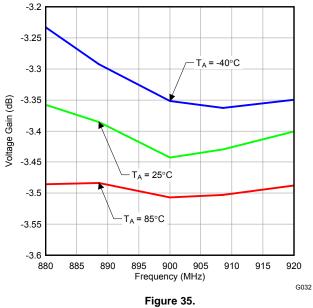

| G    | Voltage Gain                             | Output rms voltage over se input I (or Q) rms voltage         | -4.2 | -3.1  | -2   | dB     |

| P1dB | Output Compression Point                 |                                                               |      | 11.5  |      | dBm    |

| IP3  | Output IP3                               | 2 input tones at 4.5 and 5.5 MHz                              |      | 25    |      | dBm    |

| IP2  | Output IP2                               | 2 input tones at 4.5 and 5.5 MHz                              |      | 56    |      | dBm    |

|      | Carrier Feedthrough                      | Unadjusted                                                    |      | -40   |      | dBm    |

|      | Sideband suppression                     | Unadjusted                                                    |      | -32   |      | dBc    |

|      | Output Return Loss                       |                                                               |      | 10    |      | dB     |

|      | Output Noise                             | DC only to BB inputs; 13 MHz offset from LO; Pout = $-10$ dBm |      | -158  |      | dBm/Hz |

| ACPR | Adiagant channel newer ratio             | 1 WCDMA signal; Pout = -8 dBm                                 |      | -75   |      | dBc    |

| ACEN | Adjacent-channel power ratio             | 2 WCDMA signals; Pout = -11 dBm per carrier                   |      | -71   |      | dBc    |

|      | JLATOR OUTPUT, F <sub>LO</sub> = 2700 MH | lz                                                            |      |       |      |        |

| G    | Voltage gain                             | Output rms voltage over se input I (or Q) rms voltage         | -4.1 | -2.7  | -1.3 | dB     |

| P1dB | Output compression point                 |                                                               |      | 12    |      | dBm    |

| IP3  | Output IP3                               | 2 input tones at 4.5 and 5.5 MHz                              |      | 26.5  |      | dBm    |

| IP2  | Output IP2                               | 2 input tones at 4.5 and 5.5 MHz                              |      | 50    |      | dBm    |

|      | Carrier feedthrough                      | Unadjusted                                                    |      | -43   |      | dBm    |

|      | Sideband suppression                     | Unadjusted                                                    |      | -41   |      | dBc    |

|      | Output return loss                       |                                                               |      | 10    |      | dB     |

|      | Output noise                             | DC only to BB inputs; 13 MHz offset from LO; Pout = -10 dBm   |      | -153  |      | dBm/Hz |

SLWS224C - AUGUST 2010-REVISED MAY 2012

# **TRF372017 ELECTRICAL CHARACTERISTICS (continued)**

V<sub>CC5V</sub> = 5.0V, V<sub>CC3V</sub> = 3.3V, VCC\_VCO2 = 3.3V, T<sub>A</sub> = 25°C, internal LO, internal VCM (unless otherwise noted)

|                 | PARAMETER                      | TEST CONDITIONS                                        | MIN  | TYP    | MAX  | UNIT   |

|-----------------|--------------------------------|--------------------------------------------------------|------|--------|------|--------|

| LOCAL           | OSCILLATOR                     |                                                        |      |        |      |        |

|                 |                                | VCO range                                              | 2400 |        | 4800 |        |

| $F_{VCO}$       | <b>F</b>                       | Divide by 2                                            | 1200 |        | 2400 | N 41 I |

|                 | Frequency Range                | Divide by 4                                            | 600  |        | 1200 | MHz    |

|                 |                                | Divide by 8                                            | 300  | 300 60 | 600  |        |

|                 | Free running VCO               | 10kHz                                                  |      | -85    |      | dBc/Hz |

|                 | Phase Noise, Fout=2.3GHz       | 1MHz                                                   |      | -132   |      | dBc/Hz |

|                 |                                | 10MHz                                                  |      | -150   |      | dBc/Hz |

|                 |                                | 50MHz                                                  |      | -153   |      | dBc/Hz |

| P <sub>LO</sub> | LO Output power <sup>(1)</sup> | 100 $\Omega$ differential, external load; single-ended | -2.5 | 3      |      | dBm    |

(1) With VCO frequency at 4.6 GHz and LO in divide-by-2 mode at 2.3 GHz

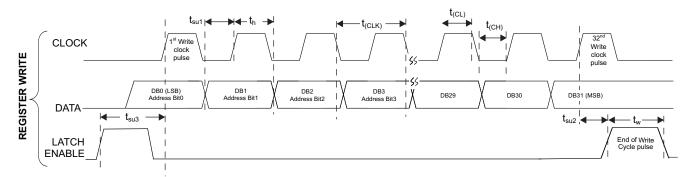

| Figure 2. | SPI Write | Timina | Diagram |

|-----------|-----------|--------|---------|

|           | •••••     |        |         |

|                    | PARAMETER                   | MIN | TYP | MAX | UNITS |

|--------------------|-----------------------------|-----|-----|-----|-------|

| t <sub>h</sub>     | Hold time, data to clock    | 20  |     |     | ns    |

| t <sub>SU1</sub>   | Setup time, data to clock   | 20  |     |     | ns    |

| T <sub>(CH)</sub>  | Clock low duration          | 20  |     |     | ns    |

| T <sub>(CL)</sub>  | Clock high duration         | 20  |     |     | ns    |

| t <sub>SU2</sub>   | Setup time, clock to enable | 20  |     |     | ns    |

| t <sub>(CLK)</sub> | Clock period                | 50  |     |     | ns    |

| t <sub>W</sub>     | Enable time                 | 50  |     |     | ns    |

| t <sub>SU3</sub>   | Setup time, latch to Data   | 70  |     |     | ns    |

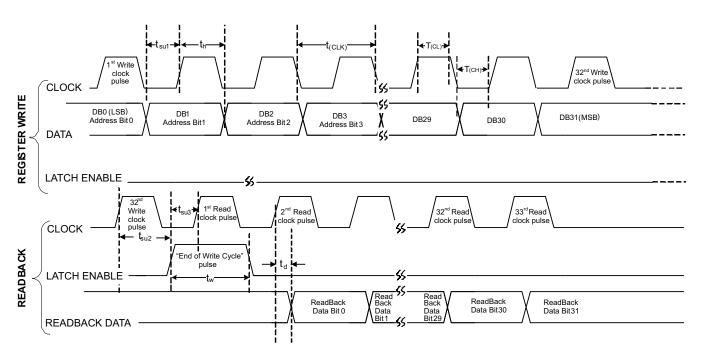

Figure 3. SPI Read-Back Timing Diagram

|                    | PARAMETER                                 | MIN | TYP | MAX | UNITS | COMMENTS            |

|--------------------|-------------------------------------------|-----|-----|-----|-------|---------------------|

| t <sub>h</sub>     | Hold time, data to clock                  | 20  |     |     | ns    |                     |

| t <sub>SU1</sub>   | Setup time, data to clock                 | 20  |     |     | ns    |                     |

| T <sub>(CH)</sub>  | Clock low duration                        | 20  |     |     | ns    |                     |

| T <sub>(CL)</sub>  | Clock High duration                       | 20  |     |     | ns    |                     |

| t <sub>SU2</sub>   | Setup time, clock to enable               | 20  |     |     | ns    |                     |

| t <sub>d</sub>     | Delay time, clock to readback data output | 10  |     |     | ns    |                     |

| t <sub>W</sub>     | Enable Time                               | 50  |     |     | ns    | Equals Clock period |

| t <sub>(CLK)</sub> | Clock period                              | 50  |     |     | ns    |                     |

#### Table 2. SPI Timing Read-Back Phase

www.ti.com

#### www.ti.com

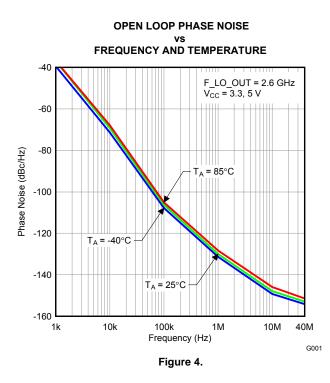

### **TYPICAL CHARACTERISTICS**

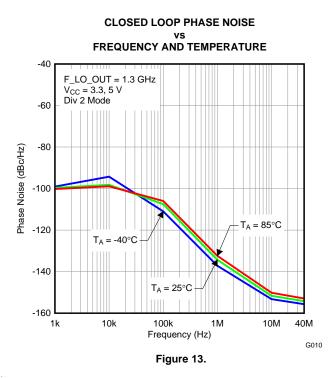

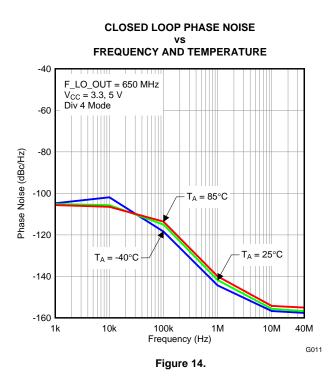

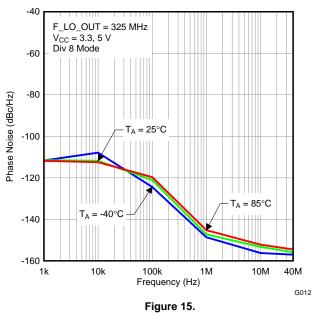

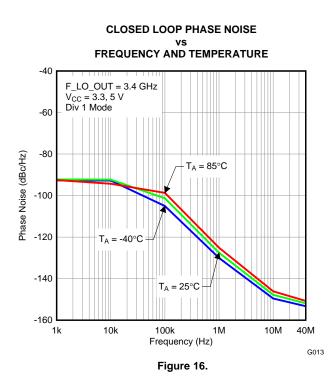

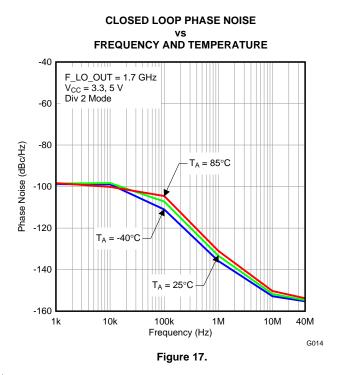

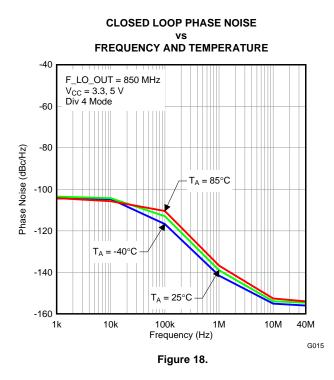

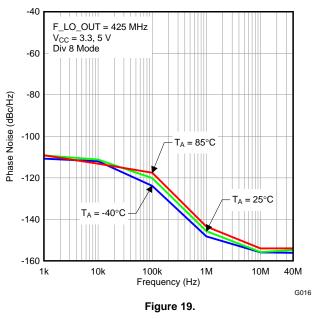

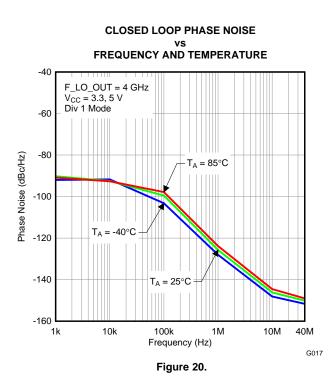

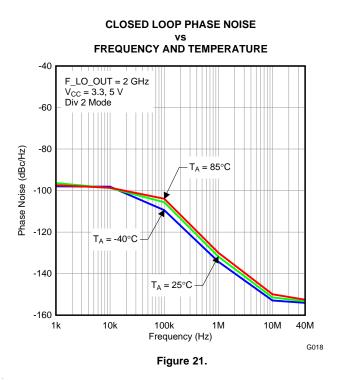

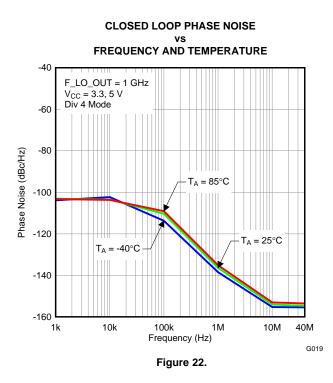

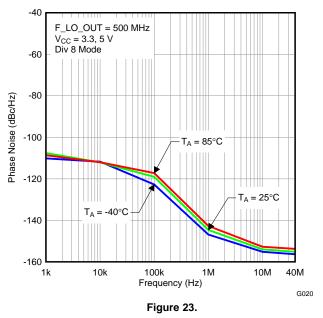

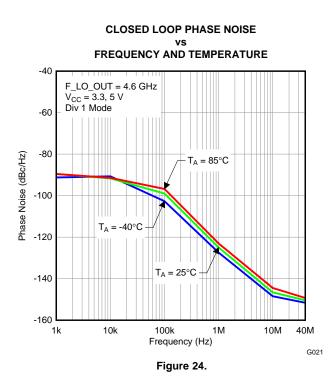

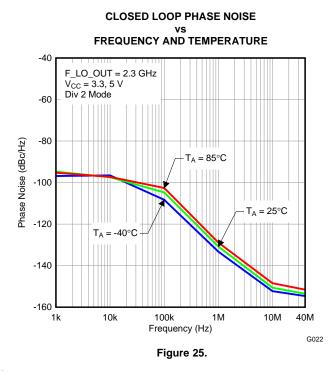

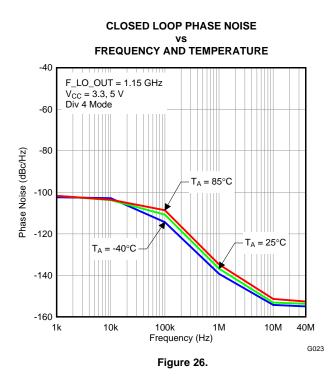

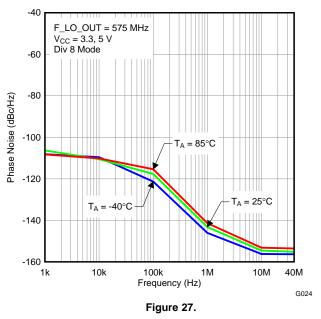

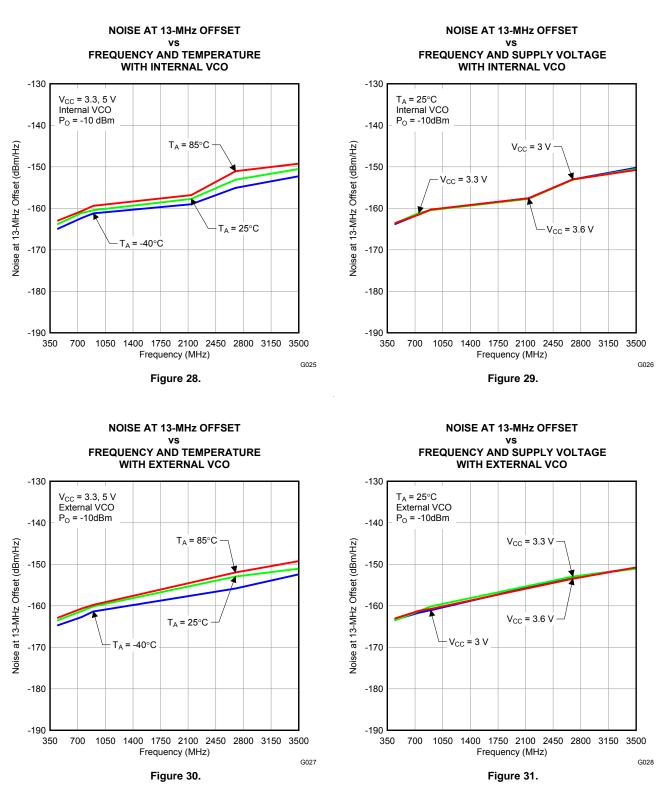

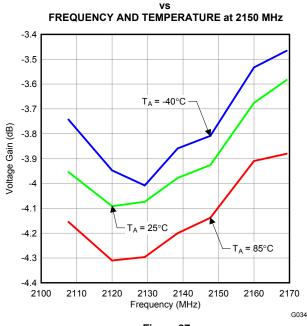

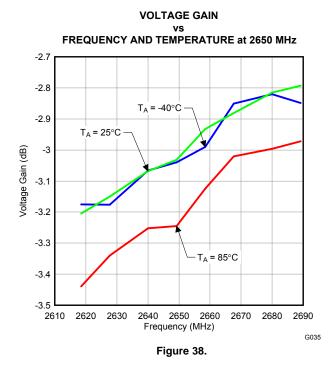

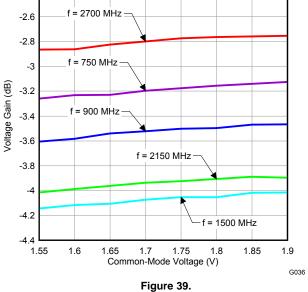

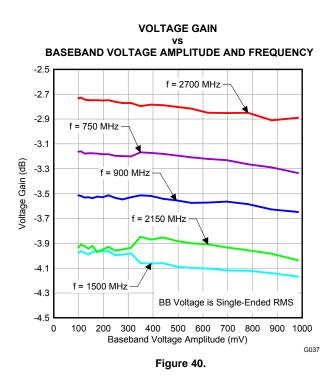

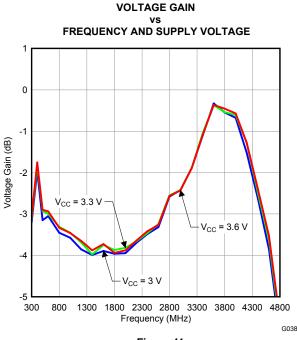

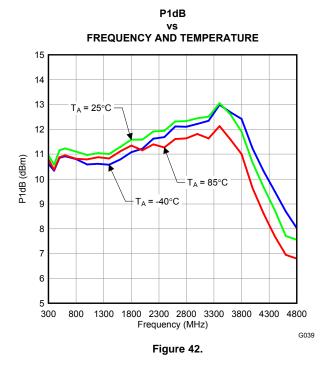

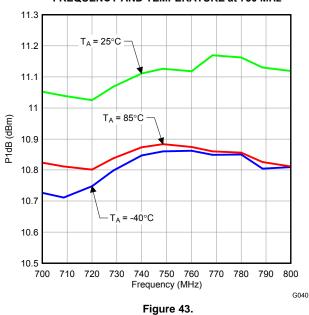

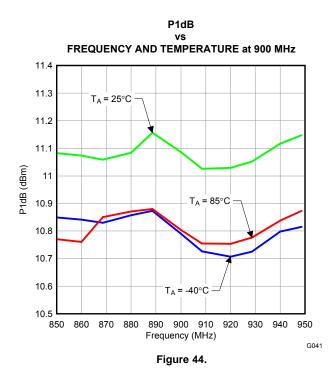

$V_{CM} = 1.7 \text{ V} \text{ (internal)}, V_{inBB} = 300 \text{ mVrms single-ended sine wave in quadrature, } V_{CC3V} = 3.3 \text{ V}, V_{CC5V} = 5 \text{ V}, f_{BB} = 4.5 \text{ MHz} \text{ and } 5.5 \text{ MHz}, \text{ internal LO, TA} = 25^{\circ}\text{C}; F_{PFD} = 1.6 \text{ MHz} \text{ (unless otherwise noted)}.$

**OPEN LOOP PHASE NOISE** vs FREQUENCY AND TEMPERATURE -40 F\_LO\_OUT = 3.35 GHz V<sub>CC</sub> = 3.3, 5 V -60 -80 Phase Noise (dBc/Hz) T<sub>A</sub> = 85°C -100 -120 T<sub>A</sub> = -40°C -140 T<sub>A</sub> = 25°C -160 1k 10k 100k 1M 10M 40M Frequency (Hz) G002 Figure 5.

www.ti.com

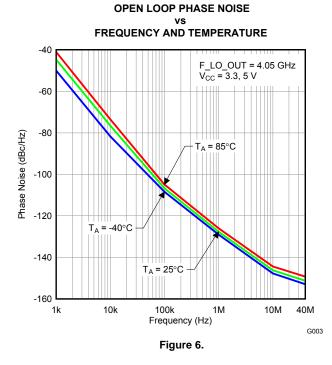

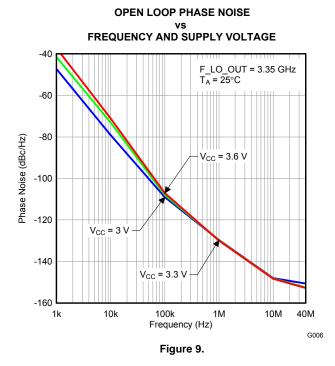

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

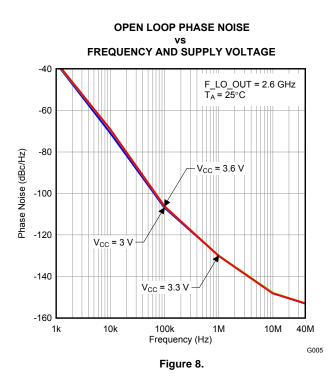

OPEN LOOP PHASE NOISE vs FREQUENCY AND SUPPLY VOLTAGE

www.ti.com

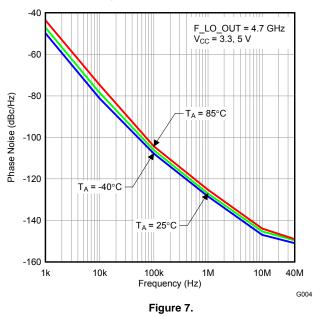

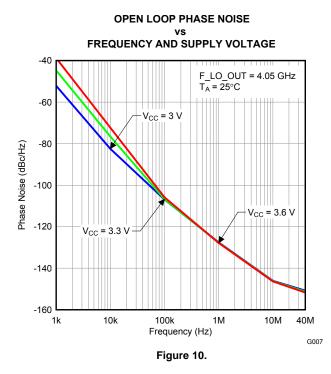

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

TEXAS INSTRUMENTS

www.ti.com

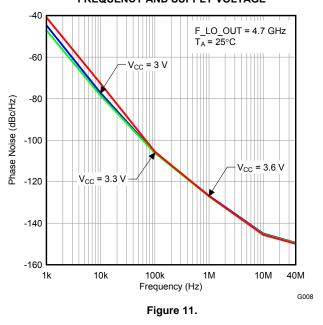

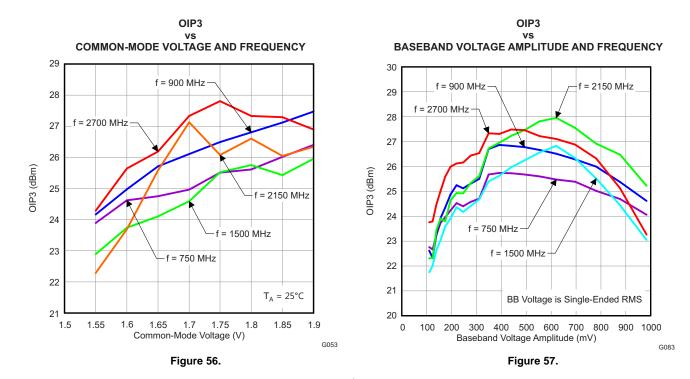

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

www.ti.com

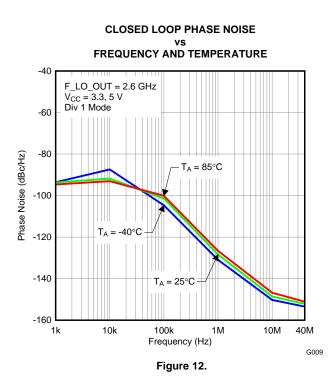

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

TEXAS INSTRUMENTS

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

www.ti.com

# TYPICAL CHARACTERISTICS (continued)

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

TEXAS INSTRUMENTS

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

VOLTAGE GAIN vs FREQUENCY AND TEMPERATURE at 900 MHz

www.ti.com

# TYPICAL CHARACTERISTICS (continued)

-2.4

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

**VOLTAGE GAIN**

VOLTAGE GAIN vs COMMON-MODE VOLTAGE AND FREQUENCY

TEXAS INSTRUMENTS

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

Figure 41.

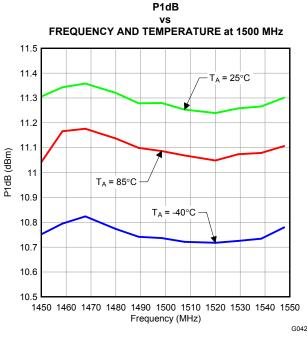

P1dB vs FREQUENCY AND TEMPERATURE at 750 MHz

# TRF372017

SLWS224C -AUGUST 2010-REVISED MAY 2012

#### www.ti.com

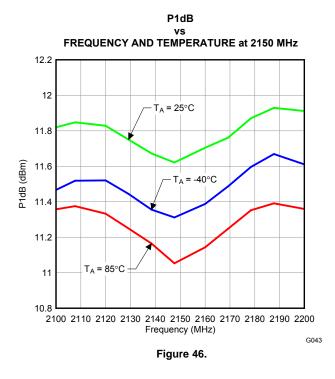

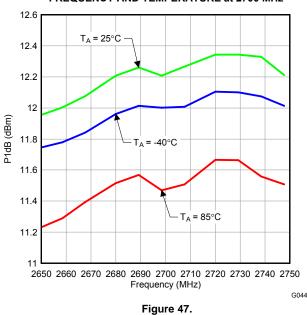

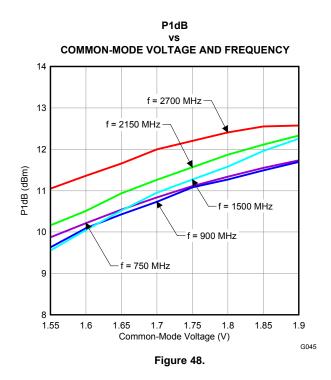

### **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

Figure 45.

P1dB vs FREQUENCY AND TEMPERATURE at 2700 MHz

EXAS ISTRUMENTS

SLWS224C-AUGUST 2010-REVISED MAY 2012

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

Figure 49.

vs FREQUENCY AND TEMPERATURE 34 32 T<sub>A</sub> = -40°C 30 T<sub>A</sub> = 25°C 28 26 OIP3 (dBm) 24 22 T<sub>A</sub> = 85°C 20 18 16 14 800 1300 1800 2300 2800 3300 3800 4300 4800 300 Frequency (MHz) G047 Figure 50.

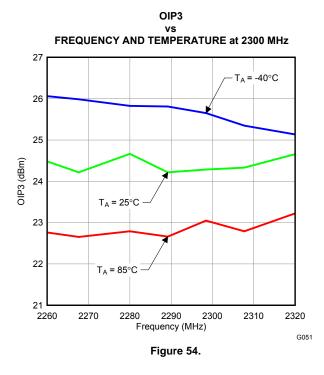

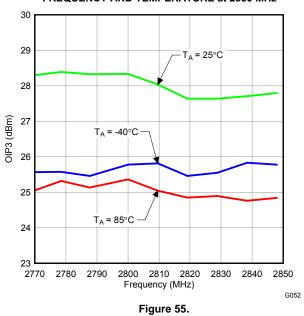

OIP3

OIP3 vs **TEMPERATURE AND FREQUENCY at 900 MHz**

www.ti.com

www.ti.com

# TYPICAL CHARACTERISTICS (continued)

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

Figure 53.

OIP3 vs FREQUENCY AND TEMPERATURE at 2850 MHz

Texas Instruments

SLWS224C - AUGUST 2010 - REVISED MAY 2012

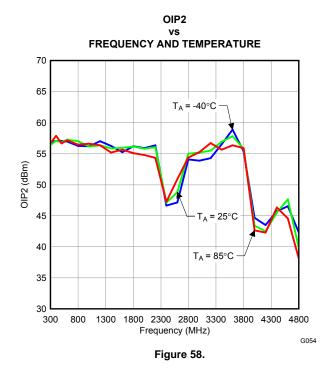

# TYPICAL CHARACTERISTICS (continued)

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

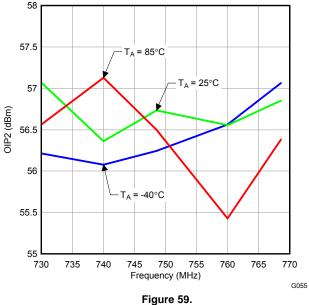

OIP2 vs FREQUENCY AND TEMPERATURE at 750 MHz

www.ti.com

www.ti.com

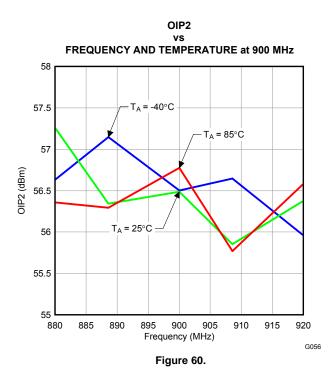

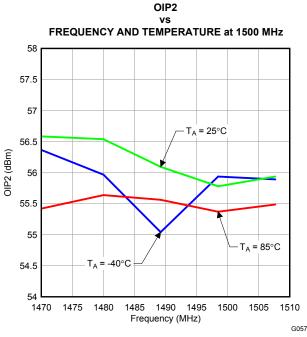

# TYPICAL CHARACTERISTICS (continued)

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

Figure 61.

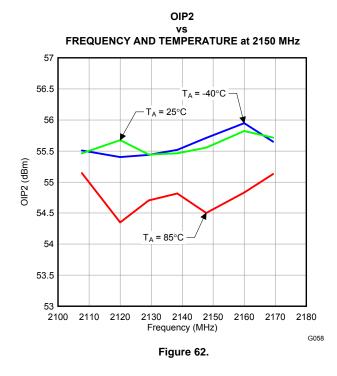

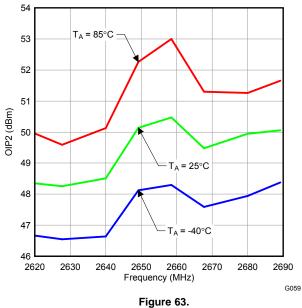

OIP2 vs FREQUENCY AND TEMPERATURE at 2650 MHz

TEXAS INSTRUMENTS

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM} = 1.7 \text{ V}$  (internal),  $V_{inBB} = 300 \text{ mVrms}$  single-ended sine wave in quadrature,  $V_{CC3V} = 3.3 \text{ V}$ ,  $V_{CC5V} = 5 \text{ V}$ ,  $f_{BB} = 4.5 \text{ MHz}$  and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD} = 1.6 \text{ MHz}$  (unless otherwise noted).

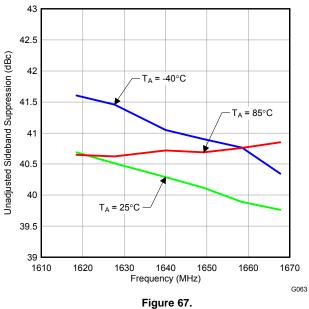

UNADJUSTED SIDEBAND SUPPRESSION vs FREQUENCY AND TEMPERATURE at 1650 MHz

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

-21

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

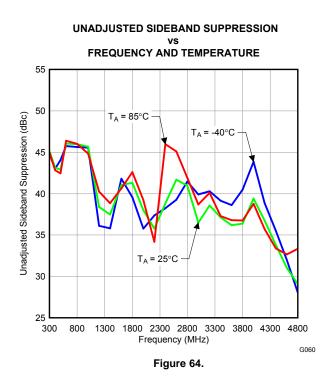

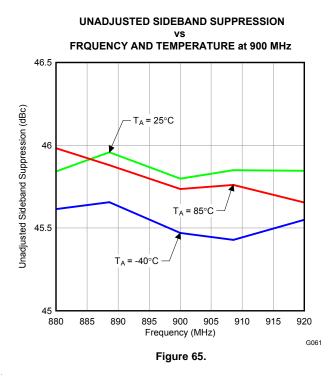

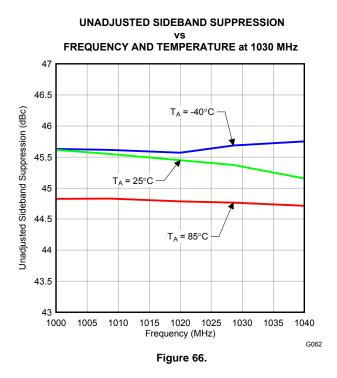

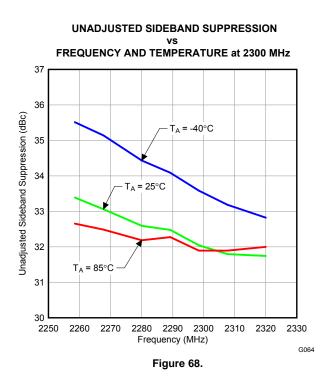

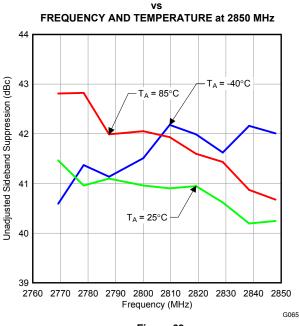

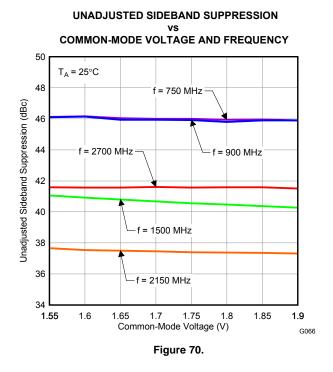

UNADJUSTED SIDEBAND SUPPRESSION

Figure 69.

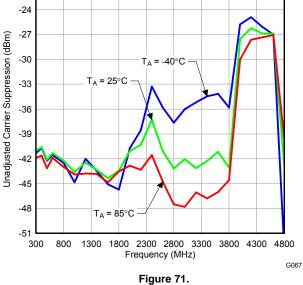

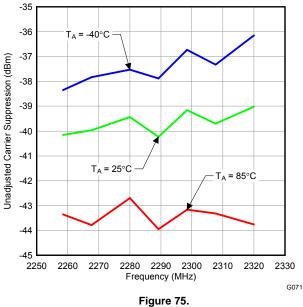

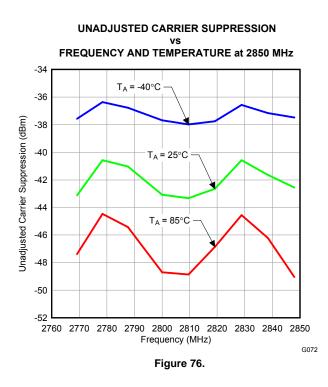

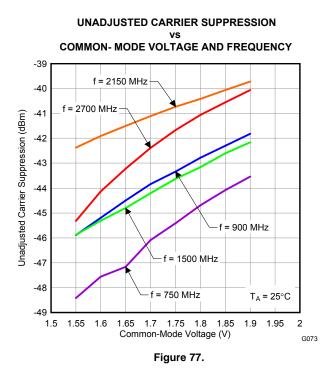

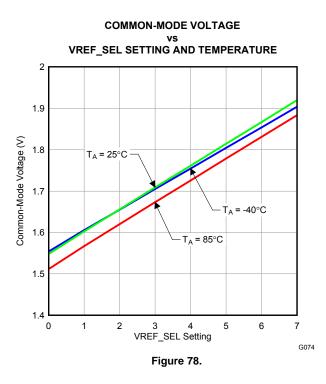

UNADJUSTED CARRIER SUPPRESSION vs FRQUENCY AND TEMPERATURE

www.ti.com

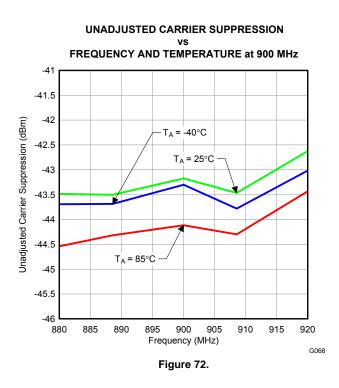

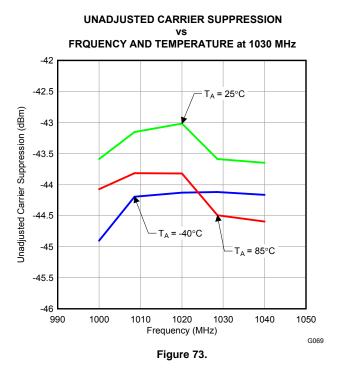

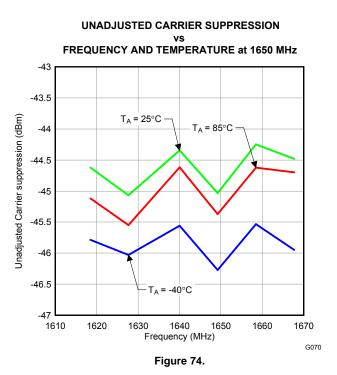

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

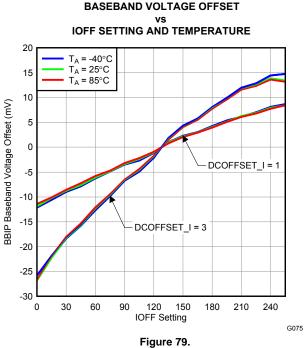

**BASEBAND VOLTAGE OFFSET**

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

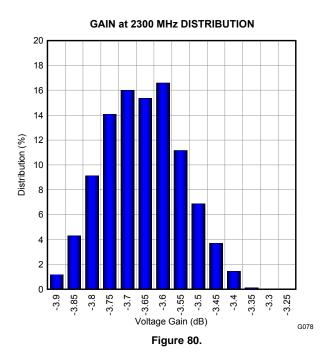

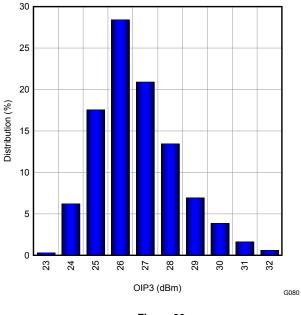

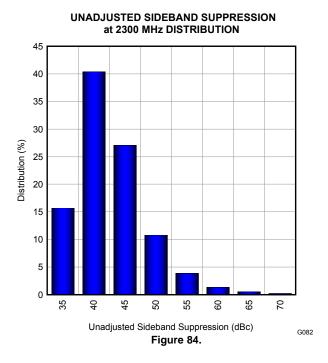

OIP3 at 2300 MHz DISTRIBUTION

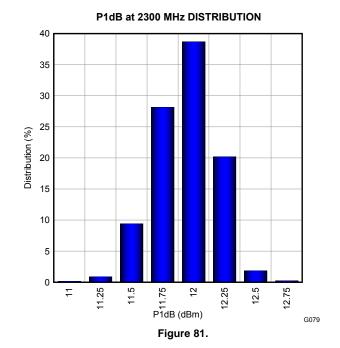

UNADJUSTED CARRIER SUPPRESSION at 2300 MHz DISTRIBUTION

# TRF372017

SLWS224C - AUGUST 2010-REVISED MAY 2012

#### www.ti.com

### **TYPICAL CHARACTERISTICS (continued)**

$V_{CM}$  = 1.7 V (internal),  $V_{inBB}$  = 300 mVrms single-ended sine wave in quadrature,  $V_{CC3V}$  = 3.3 V,  $V_{CC5V}$  = 5 V,  $f_{BB}$  = 4.5 MHz and 5.5 MHz, internal LO, TA = 25°C;  $F_{PFD}$  = 1.6 MHz (unless otherwise noted).

### SERIAL INTERFACE PROGRAMMING REGISTERS DEFINITION

The TRF372017 features a 3-wire serial programming interface (SPI) that controls an internal 32-bit shift register. There are a total of 3 signals that need to be applied: the clock (CLK, pin 47), the serial data (DATA, pin 46) and the latch enable (LE, pin 45). The TRF372017 has an additional pin (RDBK, pin 2) for read-back functionality. This pin is a digital pin and can be used to read-back values of different internal registers.

The DATA (DB0-DB31) is loaded LSB first and is read on the rising edge of the CLOCK. The LE is asynchronous to the CLOCK and at its rising edge the data in the shift register gets loaded onto the selected internal register. The 5 LSB of the Data field are the address bits to select the available internal registers.

# PLL SPI REGISTERS

|       | Register address |       |            |            |       | Reference Clock Divider                                     |      |      |     |       |       |       |       |       |       |

|-------|------------------|-------|------------|------------|-------|-------------------------------------------------------------|------|------|-----|-------|-------|-------|-------|-------|-------|

| Bit0  | Bit1             | Bit2  | Bit3       | Bit4       | Bit5  | Bit6                                                        | Bit7 | Bit8 | Bit | Bit10 | Bit11 | Bit12 | Bit13 | Bit14 | Bit15 |

|       | ••               | RSV   | REF<br>INV | VCO<br>NEG |       | Charge Pump Current CP VCO Cal CLK div/Mult<br>DOUBLE       |      |      |     |       | RSV   |       |       |       |       |

| Bit16 | Bit17            | Bit18 | Bit19      | Bit20      | Bit21 | Bit21 Bit22 Bit23 Bit24 Bit25 Bit26 Bit27 Bit28 Bit29 Bit30 |      |      |     |       | Bit31 |       |       |       |       |

| Register 1 | Name           | Reset Value | Description                                                                                                       |

|------------|----------------|-------------|-------------------------------------------------------------------------------------------------------------------|

| Bit0       | ADDR_0         | 1           | Register address bits                                                                                             |

| Bit1       | ADDR_1         | 0           |                                                                                                                   |

| Bit2       | ADDR_2         | 0           |                                                                                                                   |

| Bit3       | ADDR_3         | 1           |                                                                                                                   |

| Bit4       | ADDR_4         | 0           |                                                                                                                   |

| Bit5       | RDIV_0         | 1           | 13-bit Reference Divider value                                                                                    |

| Bit6       | RDIV_1         | 0           | │ (minimum value Rmin= 1, B[175] = [00 0000 0000 001];<br>│ maximum value Rmax=8191, B[175] = [11 1111 1111 111]; |

| Bit7       | RDIV_2         | 0           |                                                                                                                   |

| Bit8       | RDIV_3         | 0           |                                                                                                                   |

| Bit9       | RDIV_4         | 0           |                                                                                                                   |

| Bit10      | RDIV_5         | 0           |                                                                                                                   |

| Bit11      | RDIV_6         | 0           |                                                                                                                   |

| Bit12      | RDIV_7         | 0           |                                                                                                                   |

| Bit13      | RDIV_8         | 0           |                                                                                                                   |

| Bit14      | RDIV_9         | 0           |                                                                                                                   |

| Bit15      | RDIV_10        | 0           |                                                                                                                   |

| Bit16      | RDIV_11        | 0           |                                                                                                                   |

| Bit17      | RDIV_12        | 0           |                                                                                                                   |

| Bit18      | RSV            | 0           |                                                                                                                   |

| Bit19      | REF_INV        | 0           | Invert Reference Clock polarity; 1 = use falling edge                                                             |

| Bit20      | NEG_VCO        | 1           | VCO polarity control; 1= negative slope (negative K <sub>v</sub> )                                                |

| Bit21      | ICP_0          | 0           | Program Charge Pump dc current, ICP                                                                               |

| Bit22      | ICP_1          | 1           | 1.94mA, B[25.21] = [00 000]<br>0.47mA, B[25.21] = [11 111]                                                        |

| Bit23      | ICP_2          | 0           | 0.97mA, default value, , B[2521] = [01 010]                                                                       |

| Bit24      | ICP_3          | 1           |                                                                                                                   |

| Bit25      | ICP_4          | 0           |                                                                                                                   |

| Bit26      | ICPDOUBLE      | 0           | 1 = set ICP to double the current                                                                                 |

| Bit27      | CAL_CLK_SEL_0  | 0           | Multiplication or division factor to create VCO calibration clock from PFD frequency                              |

| Bit28      | CAL_CLK _SEL_1 | 0           |                                                                                                                   |

| Bit29      | CAL_CLK _SEL_2 | 0           |                                                                                                                   |

| Bit30      | CAL_CLK _SEL_3 | 1           |                                                                                                                   |

| Bit31      | RSV            | 0           |                                                                                                                   |

CAL\_CLK\_SEL[3..0]: Set the frequency divider value used to derive the VCO calibration clock from the phase detector frequency

| CAL_CLK_SEL | Scaling Factor |

|-------------|----------------|

| 1111        | 1/128          |

| 1110        | 1/64           |

| 1101        | 1/32           |

| 1100        | 1/16           |

| 1011        | 1/8            |

| 1010        | 1/4            |

| 1001        | 1/2            |

| 1000        | 1              |

| 0110        | 2              |

| 0101        | 4              |

| 0100        | 8              |

| 0011        | 16             |

| 0010        | 32             |

| 0001        | 64             |

| 0000        | 128            |

# ICP[4..0]: Set the charge pump current

| ICP[40] | Current (mA) |  |  |  |  |

|---------|--------------|--|--|--|--|

| 00 000  | 1.94         |  |  |  |  |

| 00 001  | 1.76         |  |  |  |  |

| 00 010  | 1.62         |  |  |  |  |

| 00 011  | 1.49         |  |  |  |  |

| 00 100  | 1.38         |  |  |  |  |

| 00 101  | 1.29         |  |  |  |  |

| 00 110  | 1.21         |  |  |  |  |

| 00 111  | 1.14         |  |  |  |  |

| 01 000  | 1.08         |  |  |  |  |

| 01 001  | 1.02         |  |  |  |  |

| 01 010  | 0.97         |  |  |  |  |

| 01 011  | 0.92         |  |  |  |  |

| 01 100  | 0.88         |  |  |  |  |

| 01 101  | 0.84         |  |  |  |  |

| 01 110  | 0.81         |  |  |  |  |

| 01 111  | 0.78         |  |  |  |  |

| 10 000  | 0.75         |  |  |  |  |

| 10 001  | 0.72         |  |  |  |  |

| 10 010  | 0.69         |  |  |  |  |

| 10 011  | 0.67         |  |  |  |  |

| 10 100  | 0.65         |  |  |  |  |

| 10 101  | 0.63         |  |  |  |  |

| 10 110  | 0.61         |  |  |  |  |

| 10 111  | 0.59         |  |  |  |  |

| 11 000  | 0.57         |  |  |  |  |

| 11 001  | 0.55         |  |  |  |  |

| 11 010  | 0.54         |  |  |  |  |

| 11 011  | 0.52         |  |  |  |  |

www.ti.com

| ICP[40] | Current (mA) |

|---------|--------------|

| 11 100  | 0.51         |

| 11 101  | 0.5          |

| 11 110  | 0.48         |

| 11 111  | 0.47         |

| Register address |       |       |       |       |                     | N-divider value |                     |       |       |       |        |                    |        |        |       |

|------------------|-------|-------|-------|-------|---------------------|-----------------|---------------------|-------|-------|-------|--------|--------------------|--------|--------|-------|

| Bit0             | Bit1  | Bit2  | Bit3  | Bit4  | Bit5                | Bit6            | Bit7                | Bit8  | Bit9  | Bit10 | Bit11  | Bit12              | Bit13  | Bit14  | Bit15 |

|                  |       |       |       |       | PLL divider setting |                 | Prescaler<br>Select | RSV   | RSV   | VCO   | select | FCO<br>sel<br>mode | Cal ac | curacy | CAL   |

| Bit16            | Bit17 | Bit18 | Bit19 | Bit20 | Bit21               | Bit22           | Bit23               | Bit24 | Bit25 | Bit26 | Bit27  | Bit28              | Bit29  | Bit30  | Bit31 |

| Register 2 | Name         | Reset Value | Description                                                                                         |

|------------|--------------|-------------|-----------------------------------------------------------------------------------------------------|

| Bit0       | ADDR_0       | 0           | Register address bits                                                                               |

| Bit1       | ADDR_1       | 1           |                                                                                                     |

| Bit2       | ADDR_2       | 0           |                                                                                                     |

| Bit3       | ADDR_3       | 1           |                                                                                                     |

| Bit4       | ADDR_4       | 0           |                                                                                                     |

| Bit5       | NINT_0       | 0           | PLL N-divider division setting                                                                      |

| Bit6       | NINT_1       | 0           |                                                                                                     |

| Bit7       | NINT_2       | 0           |                                                                                                     |

| Bit8       | NINT_3       | 0           |                                                                                                     |

| Bit9       | NINT_4       | 0           |                                                                                                     |

| Bit10      | NINT_5       | 0           |                                                                                                     |

| Bit11      | NINT_6       | 0           |                                                                                                     |

| Bit12      | NINT_7       | 1           |                                                                                                     |

| Bit13      | NINT_8       | 0           |                                                                                                     |

| Bit14      | NINT_9       | 0           |                                                                                                     |

| Bit15      | NINT_10      | 0           |                                                                                                     |

| Bit16      | NINT_11      | 0           |                                                                                                     |

| Bit17      | NINT_12      | 0           |                                                                                                     |

| Bit18      | NINT_13      | 0           |                                                                                                     |

| Bit19      | NINT_14      | 0           |                                                                                                     |

| Bit20      | NINT_15      | 0           |                                                                                                     |

| Bit21      | PLL_DIV_SEL0 | 1           | Select division ratio of divider in front of prescaler                                              |

| Bit22      | PLL_DIV_SEL1 | 0           |                                                                                                     |

| Bit23      | PRSC_SEL     | 1           | Set prescaler modulus (0 $\rightarrow$ 4/5; 1 $\rightarrow$ 8/9)                                    |

| Bit24      | RSV          | 0           |                                                                                                     |

| Bit25      | RSV          | 0           |                                                                                                     |

| Bit26      | VCO_SEL_0    | 0           | Selects between the four integrated VCO's<br>00 = lowest frequency VCO; 11 = highest frequency VCO  |

| Bit27      | VCO_SEL_1    | 1           |                                                                                                     |

| Bit28      | VCOSEL_MODE  | 0           | Single VCO auto-calibration mode (1 = active)                                                       |

| Bit29      | CAL_ACC_0    | 0           | Error count during the cap array calibration                                                        |

| Bit30      | CAL_ACC_1    | 0           | Recommended programming [00]                                                                        |

| Bit31      | EN_CAL       | 0           | Execute a VCO frequency auto-calibration. Set to 1 to initiate a calibration. Resets automatically. |

SLWS224C -AUGUST 2010-REVISED MAY 2012

*PLL\_DIV<1,0>:* Select division ratio of divider in front of prescaler

| PLL DIV | Frequency Divider |

|---------|-------------------|

| 00      | 1                 |

| 01      | 2                 |

| 10      | 4                 |

$VCOSEL_MODE<0>:$  when it is 1, the cap array calibration is run on the VCO selected through bits  $VCO_SEL<2,1>$

|       | Register address |       |       |       |       | Fractional N-divider value |       |       |       |       |       |       |       |       |       |

|-------|------------------|-------|-------|-------|-------|----------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit0  | Bit1             | Bit2  | Bit3  | Bit4  | Bit5  | Bit6                       | Bit7  | Bit8  | Bit9  | Bit10 | Bit11 | Bit12 | Bit13 | Bit14 | Bit15 |

|       |                  |       |       |       |       |                            |       |       | RSV   | RSV   |       |       |       |       |       |

| Bit16 | Bit17            | Bit18 | Bit19 | Bit20 | Bit21 | Bit22                      | Bit23 | Bit24 | Bit25 | Bit26 | Bit27 | Bit28 | Bit29 | Bit30 | Bit31 |

| Register 3 | Name      | Reset Value | Description                                  |

|------------|-----------|-------------|----------------------------------------------|

| Bit0       | ADDR_0    | 1           | Register address bits                        |

| Bit1       | ADDR_1    | 1           |                                              |

| Bit2       | ADDR_2    | 0           |                                              |

| Bit3       | ADDR_3    | 1           |                                              |

| Bit4       | ADDR_4    | 0           |                                              |

| Bit5       | NFRAC<0>  | 0           | Fractional PLL N divider value 0 to 0.99999. |

| Bit6       | NFRAC<1>  | 0           |                                              |

| Bit7       | NFRAC<2>  | 0           |                                              |

| Bit8       | NFRAC<3>  | 0           |                                              |

| Bit9       | NFRAC<4>  | 0           |                                              |

| Bit10      | NFRAC<5>  | 0           |                                              |

| Bit11      | NFRAC<6>  | 0           |                                              |

| Bit12      | NFRAC<7>  | 0           |                                              |

| Bit13      | NFRAC<8>  | 0           |                                              |

| Bit14      | NFRAC<9>  | 0           |                                              |

| Bit15      | NFRAC<10> | 0           |                                              |

| Bit16      | NFRAC<11> | 0           |                                              |

| Bit17      | NFRAC<12> | 0           |                                              |

| Bit18      | NFRAC<13> | 0           |                                              |

| Bit19      | NFRAC<14> | 0           |                                              |

| Bit20      | NFRAC<15> | 0           |                                              |

| Bit21      | NFRAC<16> | 0           |                                              |

| Bit22      | NFRAC<17> | 0           |                                              |

| Bit23      | NFRAC<18> | 0           |                                              |

| Bit24      | NFRAC<19> | 0           |                                              |

| Bit25      | NFRAC<20> | 0           |                                              |

| Bit26      | NFRAC<21> | 0           |                                              |

| Bit27      | NFRAC<22> | 0           |                                              |

| Bit28      | NFRAC<23> | 0           |                                              |

| Bit29      | NFRAC<24> | 0           |                                              |

| Bit30      | RSV       | 0           |                                              |

| Bit31      | RSV       | 0           |                                              |

www.ti.com

|              | Register address |       |                  |       | PD<br>PLL | Power Down PLL blocks |       |       |       |         |       |       |           | PD<br>VCM |                     |

|--------------|------------------|-------|------------------|-------|-----------|-----------------------|-------|-------|-------|---------|-------|-------|-----------|-----------|---------------------|

| Bit0         | Bit1             | Bit2  | Bit3             | Bit4  | Bit5      | Bit6                  | Bit7  | Bit8  | Bit9  | Bit10   | Bit11 | Bit12 | Bit13     | Bit14     | Bit15               |

| PD DC<br>off | EXT<br>VCO       |       | PLL Test Control |       |           |                       |       |       | ΣΔ    | Mode or | der   | ΣΔ Ν  | /lode con | trols     | EN<br>Fract<br>mode |

| Bit16        | Bit17            | Bit18 | Bit19            | Bit20 | Bit21     | Bit22                 | Bit23 | Bit24 | Bit25 | Bit26   | Bit27 | Bit28 | Bit29     | Bit30     | Bit31               |

| Register 4 | Name          | Reset Value | Description                                                                                                                                                      |  |  |  |  |  |

|------------|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit0       | ADDR_0        | 0           | Register address bits                                                                                                                                            |  |  |  |  |  |

| Bit1       | ADDR_1        | 0           |                                                                                                                                                                  |  |  |  |  |  |

| Bit2       | ADDR_2        | 1           |                                                                                                                                                                  |  |  |  |  |  |

| Bit3       | ADDR_3        | 1           |                                                                                                                                                                  |  |  |  |  |  |

| Bit4       | ADDR_4        | 0           |                                                                                                                                                                  |  |  |  |  |  |

| Bit5       | PWD_PLL       | 0           | Power down all PLL blocks (1 = off)                                                                                                                              |  |  |  |  |  |

| Bit6       | PWD_CP        | 0           | When 1, charge pump is off                                                                                                                                       |  |  |  |  |  |

| Bit7       | PWD_VCO       | 0           | When 1, VCO is off                                                                                                                                               |  |  |  |  |  |

| Bit8       | PWD_VCOMUX    | 0           | Power down the 4 VCO mux block (1 = Off)                                                                                                                         |  |  |  |  |  |

| Bit9       | PWD_DIV124    | 0           | Power down programmable RF divider in PLL feedback path (1 = off)                                                                                                |  |  |  |  |  |

| Bit10      | PWD_PRESC     | 0           | Power down programmable prescaler (1 = off)                                                                                                                      |  |  |  |  |  |

| Bit11      | RSV           | 0           |                                                                                                                                                                  |  |  |  |  |  |

| Bit12      | PWD_OUT_BUFF  | 1           | Power down LO output buffer $(1 = off)$ .                                                                                                                        |  |  |  |  |  |

| Bit13      | PWD_LO_DIV    | 1           | Power down frequency divider in LO output chain 1 (1 = off)                                                                                                      |  |  |  |  |  |

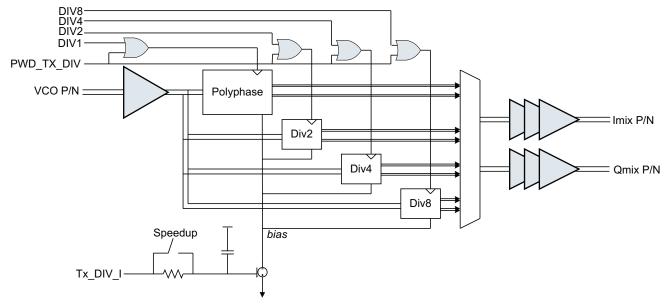

| Bit14      | PWD_TX_DIV    | 1           | Power down frequency divider in modulator chain (1 = off)                                                                                                        |  |  |  |  |  |

| Bit15      | PWD_BB_VCM    | 1           | Power down baseband input DC common block (1 = off)                                                                                                              |  |  |  |  |  |

| Bit16      | PWD_DC_OFF    | 1           | Power down baseband input DC offset control block (1 = off)                                                                                                      |  |  |  |  |  |

| Bit17      | EN_EXTVCO     | 0           | Enable external LO/VCO input buffer (1 = enabled)                                                                                                                |  |  |  |  |  |

| Bit18      | EN_ISOURCE    | 0           | Enable offset current at Charge Pump output (to be used in fractional mode only, 1 = on).                                                                        |  |  |  |  |  |

| Bit19      | LD_ANA_PREC_0 | 0           | Control precision of analog lock detector (1 1 = low; 0 0 = high). See LOCK DETEC                                                                                |  |  |  |  |  |

| Bit20      | LD_ANA_PREC_1 | 0           | section of Application Information for usage details.                                                                                                            |  |  |  |  |  |

| Bit21      | CP_TRISTATE_0 | 0           | Set the charge pump output in Tristate mode.                                                                                                                     |  |  |  |  |  |

| Bit22      | CP_TRISTATE_1 | 0           | Normal, B[2221] = [00]<br>Down, B[2221] = [01]<br>Up, B[2221] = [10]<br>Tristate, B[2221] = [11]                                                                 |  |  |  |  |  |

| Bit23      | SPEEDUP       | 0           | Speed up PLL and Tx blocks by bypassing bias stabilizer capacitors.                                                                                              |  |  |  |  |  |

| Bit24      | LD_DIG_PREC   | 0           | Lock detector precision (increases sampling time if set to 1)                                                                                                    |  |  |  |  |  |

| Bit25      | EN_DITH       | 1           | Enable $\Delta\Sigma$ modulator dither (1=on)                                                                                                                    |  |  |  |  |  |

| Bit26      | MOD_ORD_0     | 0           | $\Delta\Sigma$ modulator order (1 through 4). Not used in integer mode.                                                                                          |  |  |  |  |  |

| Bit27      | MOD_ORD_1     | 1           | 1 <sup>st</sup> order, B[2726] = [00]<br>2 <sup>nd</sup> order, B[2726] = [01]<br>3 <sup>rd</sup> order, B[2726] = [10]<br>4 <sup>th</sup> order, B[2726] = [11] |  |  |  |  |  |

| Bit28      | DITH_SEL      | 0           | Select dither mode for $\Delta\Sigma$ modulator (0 = const; 1 = pseudo-random)                                                                                   |  |  |  |  |  |

| Bit29      | DEL_SD_CLK_0  | 0           | ΔΣ modulator clock delay. Not used in integer mode.                                                                                                              |  |  |  |  |  |

| Bit30      | DEL_SD_CLK_1  | 1           | Min delay = 00<br>Max delay = 11                                                                                                                                 |  |  |  |  |  |

| Bit31      | EN_FRAC       | 0           | Enable fractional mode (1 = fractional enabled)                                                                                                                  |  |  |  |  |  |

#### SLWS224C - AUGUST 2010 - REVISED MAY 2012

|       | Register address        |       |       | VCO_R Trim        |       |       | PLL_R_Trim |       | VCO Current    |       |                     |       | VCOBUF BIAS |               |       |

|-------|-------------------------|-------|-------|-------------------|-------|-------|------------|-------|----------------|-------|---------------------|-------|-------------|---------------|-------|

| Bit0  | Bit1                    | Bit2  | Bit3  | Bit4              | Bit5  | Bit6  | Bit7       | Bit8  | Bit9           | Bit10 | Bit11               | Bit12 | Bit13       | Bit14         | Bit15 |

| VCOML | VCOMUX BIAS OUTBUF BIAS |       | R     | RSV BIAS V<br>SEL |       | VC    | CO CAL REF |       | VCOMUX<br>AMPL |       | VCO Bias<br>Voltage |       | RSV         | EN_LD<br>ISRC |       |

| Bit16 | Bit17                   | Bit18 | Bit19 | Bit20             | Bit21 | Bit22 | Bit23      | Bit24 | Bit25          | Bit26 | Bit27               | Bit28 | Bit29       | Bit30         | Bit31 |

| Register 5 | Name            | Reset Value | Description                                                                                                                                                       |  |  |  |  |  |  |  |

|------------|-----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Bit0       | ADDR_0          | 1           | Register address bits                                                                                                                                             |  |  |  |  |  |  |  |

| Bit1       | ADDR_1          | 0           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit2       | ADDR_2          | 1           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit3       | ADDR_3          | 1           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit4       | ADDR_4          | 0           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit5       | VCOBIAS_RTRIM_0 | 0           | VCO bias resistor trimming. Recommended programming [100].                                                                                                        |  |  |  |  |  |  |  |

| Bit6       | VCOBIAS_RTRIM_1 | 0           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit7       | VCOBIAS_RTRIM_2 | 1           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit8       | PLLBIAS_RTRIM_0 | 0           | PLL bias resistor trimming. Recommended programming [10].                                                                                                         |  |  |  |  |  |  |  |

| Bit9       | PLLBIAS_RTRIM_1 | 1           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit10      | VCO_BIAS_0      | 0           | ecommended programming<br>00 μA, B[1310] = [0101] with VCC_VCO2 = 3.3 V<br>00 μA, B[1310] = [1111] with VCC_VCO2 = 5.0 V                                          |  |  |  |  |  |  |  |

| Bit11      | VCO_BIAS_1      | 0           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit12      | VCO_BIAS_2      | 0           | Bias current varies directly with reference current                                                                                                               |  |  |  |  |  |  |  |

| Bit13      | VCO_BIAS_3      | 1           | Recommended programming<br>400 μA, B[1310] = [0101] with VCC_VCO2 = 3.3 V<br>600 μA, B[1310] = [1111] with VCC_VCO2 = 5.0 V                                       |  |  |  |  |  |  |  |

| Bit14      | VCOBUF_BIAS_0   | 0           | VCO buffer bias reference current.                                                                                                                                |  |  |  |  |  |  |  |

| Bit15      | VCOBUF_BIAS_1   | 1           | $300 \ \mu\text{A}, B[1514] = [00]$<br>$600 \ \mu\text{A}, B[1514] = [11]$<br>Bias current varies directly with reference current<br>Recommended programming [10] |  |  |  |  |  |  |  |

| Bit16      | VCOMUX_BIAS_0   | 0           | VCO's muxing buffer bias reference current.                                                                                                                       |  |  |  |  |  |  |  |

| Bit17      | VCOMUX_BIAS_1   | 1           | $300 \ \mu$ A, B[1716] = [00]<br>$600 \ \mu$ A, B[1716] = [11]<br>Bias current varies directly with reference current<br>Recommended programming [11]             |  |  |  |  |  |  |  |

| Bit18      | BUFOUT_BIAS_0   | 0           | PLL output buffer bias reference current.                                                                                                                         |  |  |  |  |  |  |  |

| Bit19      | BUFOUT_BIAS_1   | 1           | 300 μA, B[1918] = [00]<br>600 μA, B[1918] = [11]<br>Bias current varies directly with reference current                                                           |  |  |  |  |  |  |  |

| Bit20      | RSV             | 0           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit21      | RSV             | 1           |                                                                                                                                                                   |  |  |  |  |  |  |  |

| Bit22      | VCO_CAL_IB      | 0           | Select bias current type for VCO calibration circuitry<br>0 = PTAT; 1 = constant over temperature<br>Recommended programming [0]                                  |  |  |  |  |  |  |  |

| Bit23      | VCO_CAL_REF_0   | 0           | VCO calibration reference voltage trimming.                                                                                                                       |  |  |  |  |  |  |  |

| Bit24      | VCO_CAL_REF_1   | 0           | 0.9 V, B[2523] = [000]<br>1.4 V, B[2523] = [111]                                                                                                                  |  |  |  |  |  |  |  |

| Bit25      | VCO_CAL_REF_2   | 1           | Recommended programming [010]                                                                                                                                     |  |  |  |  |  |  |  |

| Bit26      | VCO_AMPL_CTRL_0 | 0           | Adjust the signal amplitude at the VCO mux input                                                                                                                  |  |  |  |  |  |  |  |

| Bit27      | VCO_AMPL_CTRL_1 | 1           | Recommended programming [11]                                                                                                                                      |  |  |  |  |  |  |  |

| Bit28      | VCO_VB_CTRL_0   | 0           | VCO core bias voltage control                                                                                                                                     |  |  |  |  |  |  |  |

| Bit29      | VCO_VB_CTRL _1  | 1           | 1.2 V, B[2928] = [00]<br>1.35 V, B[2928] = [01]<br>1.5 V, B[2928] = [10]<br>1.65 V, B[2928] = [11]<br>Recommended programming [00]                                |  |  |  |  |  |  |  |

| Bit30      | RSV             | 0           |                                                                                                                                                                   |  |  |  |  |  |  |  |

# TRF372017

www.ti.com

### SLWS224C-AUGUST 2010-REVISED MAY 2012

| Register 5 | Name          | Reset Value | Description                                                                                                                                                            |

|------------|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit31      | EN_LD_ISOURCE | 1           | Enable monitoring of LD to turn on Isource when in frac-n mode (EN_FRAC=1).<br>0 = ISource set by EN_ISOURCE.<br>1 = ISource set by LD.<br>Recommended programming [0] |

| Register address |              |       |       |       | BB DC OFFSET |       |           |       |           |       |            |       |            |       |       |

|------------------|--------------|-------|-------|-------|--------------|-------|-----------|-------|-----------|-------|------------|-------|------------|-------|-------|

| Bit0             | Bit1         | Bit2  | Bit3  | Bit4  | Bit5         | Bit6  | Bit7      | Bit8  | Bit9      | Bit10 | Bit11      | Bit12 | Bit13      | Bit14 | Bit15 |

|                  | BB DC OFFSET |       |       | V     | /REF SE      | L     | TXDIV SEL |       | LODIV SEL |       | TXDIV BIAS |       | LODIV BIAS |       |       |

| Bit16            | Bit17        | Bit18 | Bit19 | Bit20 | Bit21        | Bit22 | Bit23     | Bit24 | Bit25     | Bit26 | Bit27      | Bit28 | Bit29      | Bit30 | Bit31 |

| Register 6 | Name          | Reset Value | Description                                                                                                                                                                     |  |  |  |  |  |  |

|------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit0       | ADDR_0        | 0           | Register address bits                                                                                                                                                           |  |  |  |  |  |  |

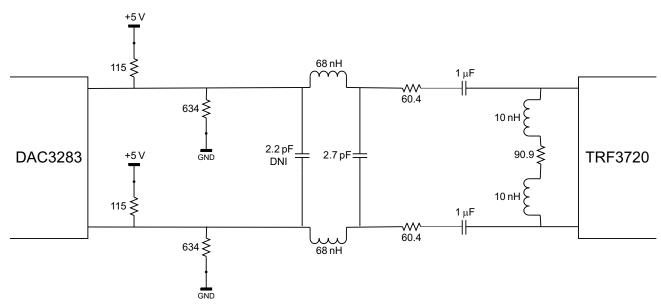

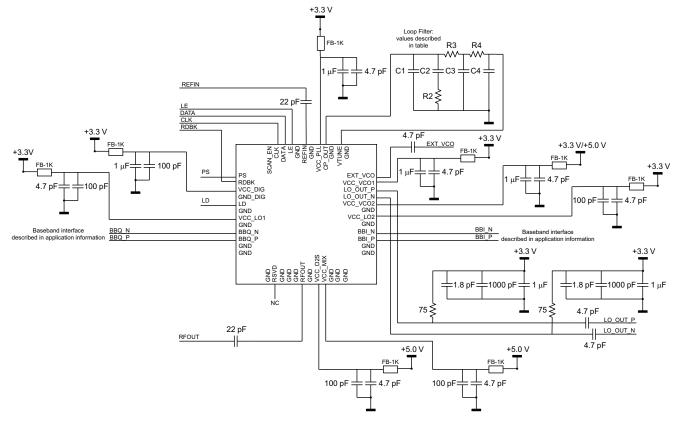

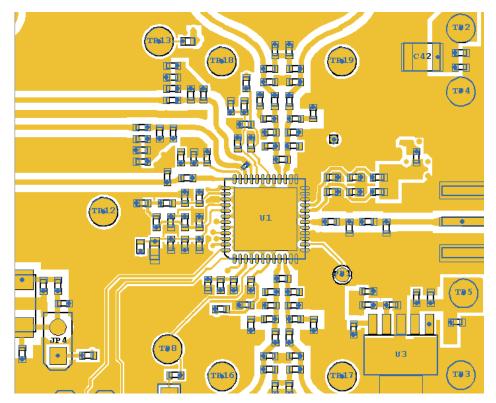

| Bit1       | ADDR_1        | 1           |                                                                                                                                                                                 |  |  |  |  |  |  |