# LM4560

LM4560 Advanced PCI Audio Accelerator

Literature Number: SNAS029

## LM4560

# **Advanced PCI Audio Accelerator**

# **General Description**

LM4560 is an advanced PCI audio accelerator providing full legacy compatibility, wavetable synthesis, DirectMusic, DirectSound, and DirectSound3D on a single chip for the high-performance, cost-sensitive consumer market. It supports Sound Blaster functionality and is fully PC98 compliant.

The LM4560 integrates a 64-voice wave table engine with per voice effect processing capability. It supports the upcoming Microsoft™ DirectMusic API and is fully compatible with DLS Level 1 (downloadable samples) specification. The LM4560 is optimized for Microsoft Windows™ 98 and Windows NT5.0 WDM streaming architecture with re-routable end-point support. The LM4560 includes DirectSound3D acceleration hardware for ITD (Interaural Time Difference), IID (Interaural Intensity Difference), Pan, Delay, and Doppler hardware

The LM4560 supports Sound Blaster Pro/16 DOS games while improving gaming audio quality. The LM4560 supports both the legacy analog gameport and a Digital Enhanced Game Port. When coupled with DirectInput™ driver, the Digital Enhanced Game Port can save up to 12% of the CPU overhead nominally required by a conventional analog game port. The LM4560 employs a high precision 26-bit digital mixer, providing an accurate 20-bit output and higher than 90 dB signal-to-noise ratio when used with high quality AC97 Rev 1.03 and Rev 2.0 codecs.

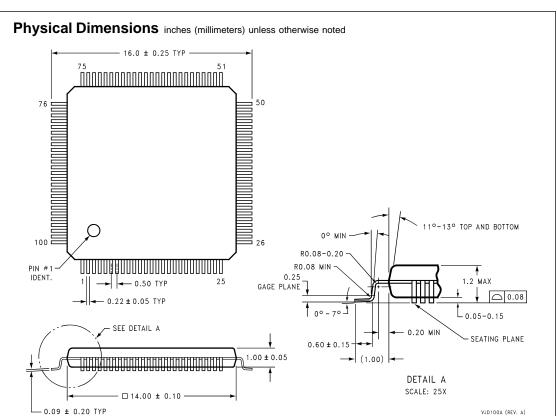

The LM4560 is designed with aggressive power management. It is PCI Bus Power Management Interface (PPMI 1.0)-compliant. The LM4560 supports multiple Rev 2.0 AC97 codecs, which are useful for notebook docking systems. With a low power, 3.3V process and a space conscious 100 TQFP package, the LM4560 is also well suited for Notebook systems

In summary, the LM4560 provides a balanced combination of features and performance to the end-user. By combining PCI bus mastering for DirectSound acceleration, Hardware Wave table synthesizer, Digital Enhanced Game Port and DirectSound 3D audio acceleration. It delivers high performance, high quality audio, high-end features with efficient power management in a space-efficient 100 TQFP package.

### **Features**

- PCI 2.1-compliant with Bus Mastering optimized for multiple stream operation

- On-chip per voice cache minimizes PCI bandwidth

- Up to 20X improvement over ISA DMA on PCI bus bandwidth utilization

#### **Advanced Wavetable Synthesizer**

- Wavetable synthesis with 64-voices polyphony, which supports all combinations of stereo/mono, 8-/16-bits, and signed/unsigned samples

- Per channel volume, pitch shift, left/right pan, tremolo, vibrato and envelope control (32 channels in hardware)

- Per channel effect process ing and effect volume control for reverb, chorus, and echo

- DLS1-compliant Downloadable Samples support

#### Legacy Compatibility

- Legacy game audio support with SoundBlaster Pro/16 compatibility on the PCI bus

- Legacy DMA support on PCI Bus with DDMA-enabled or standard (non-DDMA) PCI chipsets

- FM through realtime FM-to-wavetable conversion

- MPU-401 compatible UART for external or internal synthesis

- General MIDI/GS command interpretation for wavetable & effect synthesis

#### High Quality Audio and AC97 Support

- CD quality audio with higher than 90 dB signal-to-noise ratio using an external high quality AC97 codec

- AC97 support with full duplex, independent sample rate converter for audio recording and playback

- On-chip sample rate converter ensures all internal operation at 48 kHz

- High precision internal 26-bit digital mixer with 16- and 20-bit digital audio output

#### **Advanced Streaming Architecture**

- Microsoft WDM Streaming architecture compliant and "Re-routable endpoint" support

- Three stereo capture channels

- AC97 stereo recording channel through AC-link

#### DirectSound 3D

- 64-voices DirectSound channels

- 32-voices DirectSound3D accelerator with IID, ITD, and Doppler effects on 3D positional audio buffers

- DirectSound accelerator for volume, pan, and pitch shift control on streaming or static buffers

#### Telephony & Modem

- Full duplex speaker phone with AC97 2.0 audio-modem codec

- Fax-modem with host based software

#### Extras

- Fully Plug and Play PCI controller and software

- Digital Enhanced Game port enables an analog joystick to emulate digital joystick performance using the National Semiconductor-provided DirectInput driver. This eliminates up to 12% CPU overhead wasted on joystick polling.

TRI-STATE® is a registered trademark of National Semiconductor Corporation. Microsoft™ is a trademark of Microsoft Corporation. Windows® is a registered trademark of Microsoft Corporation. Directlnput™ is a trademark of Microsoft Corporation

### Features (Continued)

- DirectX timer for video/audio synchronization

- Forward pin-compatible with future PCI audio accelerators

- 100-pin TQFP package

- 3.3V operation

#### **Software Support**

■ Complete DirectX driver suite (DirectSound3D, DirectSound, DirectMusic, and DirectInput) for Windows 95 and Windows 98/NT 5.0

- Configuration installation, and diagnostics under real mode DOS, WindowsWindows 95, and Windows 98 DOS box

- Windows 3.1, 95, NT4.0, Windows 98/NT5.0 configuration, installation, and mixer program

- 1, 2, 4, or 8 Mbytes General MIDI (GM)/General Sound (GS) compliant sample Library

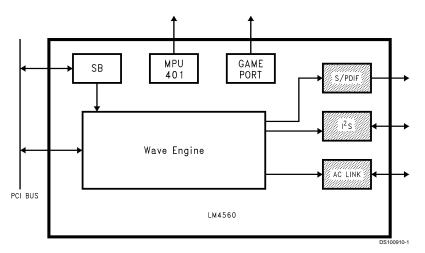

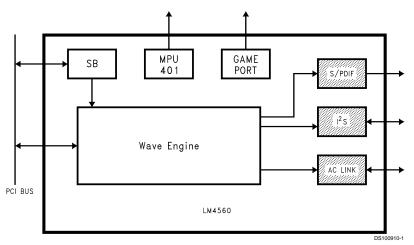

# **Block Diagram**

#### **Table of Contents**

- 1.0 Pin Description

- 1.1 Package Diagram

- 1.2 Pin Description

- 2.0 Functional Decription

- 2.1 Device Overview

- 3.0 Register Description

- 3.1 PCI Configuration Register Map

- 3.1.1 PCI Configuration Register Description

- 3.1.1.1 Device ID & Vendor ID

- 3.1.1.2 Status & Command

- 3.1.1.3 Class Code & Revision ID

- 3.1.1.5 Audio IO Base Register

- 3.1.1.6 Audio MEM Base Register

- 3.1.1.7 Subsystem ID & Subsystem vendor ID

- 3.1.1.8 PCIPM Capability List Pointer Register

- 3.1.1.9 Max\_Lat, Min\_Gnt, Interrupt Pin & Interrupt Line

- 3.1.1.10 DDMA Slave Configuration Register

- 3.1.1.11 Legacy audio/power management configuration

- 3.1.1.13 Power management capability register (PMC)

- 3.1.1.14 Power management control/status register (PMCSR) & PMCSR\_BSE & Data

- 3.2 Audio Processor Register Map

- 3.3 Audio Processor Register Access Mode

- 3.3.1 I/O Access Mode

- 3.3.2 Memory Access Mode

- 3.4 Audio Processor Register Description

- 3.4.1 DMA Registers

- 3.4.1.1 DMAR0 (Legacy DMA Playback Buffer Base Register Port1)

- 3.4.2 Legacy Sound Blaster/Adlib Registers

- 3.4.3 Legacy MPU-401 Registers

- 3.4.4 Legacy Gameport Register

- 3.4.5 Serial Interface Control Register

- 3.4.6 Misc and Status Register

- 3.4.7 OPL3 Channel Status Register

- 3.4.8 S/PDIF & GPIO Registers

- 3.4.9 Wave Engine Registers

- 3.4.9.31 F4h\_A (EBUF1) ( Bank A Only)

### 4.0 Functional Description

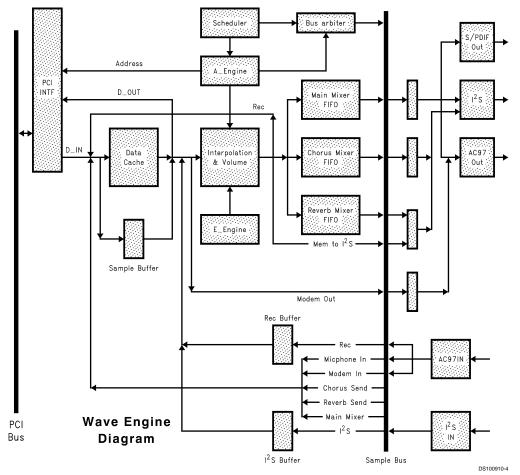

- 4.1 Wave Engine

- 4.1.1 Scheduler

- 4.1.2 Address Engine

- 4.1.3 Envelope Engine

- 4.1.4 Interpolation & Volume Adjustment

- 4.1.5 Digital Mixer

- 4.1.6 LFO

- 4.1.7 Recording

# Table of Contents (Continued)

- 4.1.8 PCI Buffer/Sample Cache

- 4.1.9 CODEC Buffer/Sample FIFO

- 4.1.10 Legacy Channel Playback/Recording

- 4.2 Legacy Audio

- 4.2.1 SB Engine:

- 4.3 Serial Interface

- 4.3.1 AC-97 Interface

- 4.3.2 I2S Interface

- 4.3.3 S/PDIF

- 4.4 Power Management

- 4.4.1 Power Management For D0-D3 States

- 4.4.2 D0-D3 State Transition Table

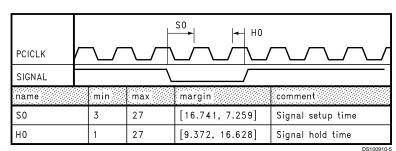

- 5.0 Signals and Timing

- 5.1.2 Timing

- 5.1.2.1 Slave read/write timing

- 6.0 Device Configuration

- 6.1 Overview

- 6.2 Configuration and GPIO Registers

## 7.0 Device Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Capacitance

- 7.3 Electrical Characteristics

- 7.4.1 Timing Table

- 7.4.2 PCI Signals

### **Physical Dimensions**

### List of Figures

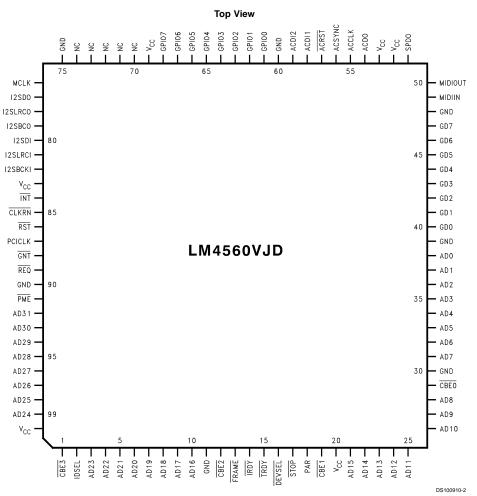

- Figure 1. 100-Pin TQFP Package

- Figure 2. LM4560 Block diagram

- Figure 3. Wave Engine Block Diagram

# 1.0 Pin Description

### 1.1 PACKAGE DIAGRAM

FIGURE 1. 100-Pin TQFP Package

# 1.0 Pin Description (Continued)

# 1.2 PIN DESCRIPTION

| Symbol          | Pin(s)   | Туре | Description                                |

|-----------------|----------|------|--------------------------------------------|

| V <sub>DD</sub> | 20, 39,  | IN   | 3.3V Power Supply                          |

|                 | 52, 53,  |      |                                            |

|                 | 69, 83,  |      |                                            |

|                 | 100      |      |                                            |

| V <sub>SS</sub> | 11, 30,  | IN   | Ground                                     |

| 00              | 48, 60,  |      |                                            |

|                 | 75, 90   |      |                                            |

| PCI BUS IN      | ITERFACI | SIGN | ALS (51)                                   |

| AD[31:0]        | 92-99.   | I/O  | PCI Address/Data Bus.                      |

|                 | 3–10,    |      | A time-multiplexed                         |

|                 | 21–28,   |      | address data bus.                          |

|                 | 31–38    |      |                                            |

| C/BE[3:0]       | 1, 12,   | I/O  | PCI Command/Byte                           |

| O/BE[0.0]       | 19, 29   | "    | Enable. Defines the type                   |

|                 | 10, 20   |      | of AD bus transaction                      |

|                 |          |      | type.                                      |

| FRAME           | 10       | I/O  |                                            |

| FRAIVIE         | 13       | 1/0  | Cycle Frame. A PCI                         |

|                 |          |      | transaction begins and ends with the FRAME |

|                 |          |      |                                            |

|                 |          |      | signal.                                    |

| IRDY            | 14       | I/O  | Initiator Ready. An active                 |

|                 |          |      | low indicates the cycle                    |

|                 |          |      | initiator is ready to send                 |

|                 |          |      | or receive data.                           |

| TRDY            | 15       | I/O  | Target Ready. An active                    |

|                 |          |      | low indicates that the                     |

|                 |          |      | target is read to complete                 |

|                 |          |      | the current transaction.                   |

| DEVSEL          | 16       | I/O  | Device Select. An active                   |

|                 |          |      | low indicates the target                   |

|                 |          |      | has decoded its address.                   |

| STOP            | 17       | I/O  | STOP. An active low                        |

|                 |          |      | indicates the target wants                 |

|                 |          |      | the initiator to stop data                 |

|                 |          |      | during the current data                    |

|                 |          |      | phase.                                     |

| PAR             | 18       | I/O  | Parity. Generates an                       |

|                 |          | ., 0 | even parity for the                        |

|                 |          |      | AD[31.0].                                  |

| RST             | 86       | IN   | Reset. A low active signal                 |

| KOT             | 00       | "    | which resets the PCI                       |

|                 |          |      | device.                                    |

| ĪNT             | - 0.4    | OUT  |                                            |

| IIN I           | 84       | 001  | Interrupt. An active low                   |

|                 |          |      | signals in interrupt to the                |

|                 | <u> </u> |      | CPU.                                       |

| PCICLK          | 87       | IN   | Clock. The clock that                      |

|                 |          |      | drives the PCI timing.                     |

| GNT             | 88       | IN   | Grant. An active low                       |

|                 |          |      | signals the master has                     |

|                 |          |      | access to the PCI bus.                     |

| REQ             | 89       | OUT  | Request. An active low                     |

|                 |          |      | indicates the master                       |

|                 | 1        | ĺ    | l                                          |

|                 |          |      | wants access to the PCI                    |

| Symbol     | Pin(s)   | Туре   | Description                                                                                                                                                 |

|------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI BUS IN |          |        | •                                                                                                                                                           |

| CLKRUN     | r        |        |                                                                                                                                                             |

| CLKRUN     | 85       | I/O    | clock Run. An active low signal used for power management on motherboards only. It is not assigned a pin on the PCI connector.                              |

| PME        | 91       | OUT    | Power Management Event. An active low signal used for power management for add in cards or motherboards. It is assigned a pin on the PCI connector.         |

| TC         | 78       | IN     | Terminal Count. This input is asserted by the DMA controller to indicate the end of a DMA transfer. The signal is only effective during a DMA access cycle. |

| IDSEL      | 2        | IN     | Initialization Device<br>Select. An active high<br>allows reads to the PCI<br>devices configuration<br>registers.                                           |

| MPU-401 IN | ITERFAC  | E SIGN | ALS (2)                                                                                                                                                     |

| MIDIOUT    | 50       | OUT    | MIDI Data Out. Sends midi data to the midi connector.                                                                                                       |

| MIDIIN     | 49       | IN     | MIDI Data In. Receives midi data from an optocoupler.                                                                                                       |

| AC97 CODI  | EC INTER | FACE S | SIGNALS (6)                                                                                                                                                 |

| ACRST      | 57       | OUT    | AC97 Master Reset. An active low which resets the internal circuitry of AC97 codecs.                                                                        |

| ACCLK      | 55       | IN     | AC97 Bit Clock. A<br>12.288 MHz clock from<br>the codec. This is used to<br>synchronize the data<br>streams to and from the<br>codecs.                      |

| ACSYNC     | 56       | I/O    | AC97 Sync. Used to start<br>the data frame used to<br>format the serial data to<br>and from the codecs.                                                     |

| ACDI1      | 58       | IN     | Primary CODEC Serial Data Input. This receives serial data in from the primary codec.                                                                       |

| ACDI2      | 59       | IN     | Secondary CODEC<br>Serial Data Input. This<br>receives serial data in<br>from the secondary<br>codec.                                                       |

## 1.0 Pin Description (Continued)

| Symbol                  | Pin(s)    | Туре   | Description              |  |

|-------------------------|-----------|--------|--------------------------|--|

| AC97 CODE               | C INTER   | FACE S | SIGNALS (6)              |  |

| ACDO                    | 54        | OUT    | AC97 serial data out.    |  |

|                         |           |        | This output sends serial |  |

|                         |           |        | data to codec(s).        |  |

| 12S INTERF              | ACE (7)   |        |                          |  |

| 12SBCKI                 | 82        | IN     | I2S Receiver Bit Clock   |  |

| 12SLRCKI                | 81        | IN     | I2S Receiver L/R Clock   |  |

| I2SDI                   | 80        | IN     | I2S Receiver Data        |  |

| I2SBCKO                 | 79        | OUT    | I2S Transmitter Bit      |  |

|                         |           |        | Clock                    |  |

| 12SLRCKO                | 78        | OUT    | I2S Transmitter L/R      |  |

|                         |           |        | Clock                    |  |

| I2SDO                   | 77        | OUT    | I2S Transmitter Data     |  |

| MCLK                    | 76        | OUT    | I2S Transmitter Master   |  |

|                         |           |        | Clock                    |  |

| S/PDIF TRANSMITTER (1)  |           |        |                          |  |

| SPDO                    | 51        | OUT    | S/PDIF transmitter       |  |

|                         |           |        | output                   |  |

| GAME POR                | T PINS (8 | 3)     |                          |  |

| GD[7:4]                 | 47:44     | IN     | Gameport data            |  |

| GD[3:0]                 | 43:40     | IN     | Gameport data            |  |

| GENERAL-PURPOSE I/O (8) |           |        |                          |  |

| GPIO[7:0]               | 68:61     | I/O    | General-purpose          |  |

|                         |           |        | input/output             |  |

| NO CONNE                | CTIONS (  | 5)     |                          |  |

| NC                      | 70:74     |        | No connections           |  |

|                         |           |        |                          |  |

## 2.0 Functional Description

#### 2.1 DEVICE OVERVIEW

- **2.1.1** The LM4560 is composed of several functional blocks. There is a PCI bus interface, a wave engine, I/O interfaces and legacy support hardware.

- 2.1.1.1 The PCI bus interface includes all the logic that talks to the PCI bus, handles the PCI bus cycles, reports PCI configuration block and PCI power management. The EEPROM interface for supporting the SubSystem and SubVendor ID fields for PCI card vendors is located here.

- 2.1.1.2 The wave engine supports all the logic necessary to synthesize wave table voices / instruments. The sample rate converter is used to pitch shift the samples and rate convert pcm streams. For example converting from 44.1 ksps CD audio to 48ksps DAT pcm. The wave engine is also used to play back WDM streams and for the legacy PC audio functions. There are three mixers in the wave engine, the main mixer, and mixers for chorus and reverb sends.

- **2.1.1.3** The I/O ports include the AC97 Rev 2.0 I/O, the I2S I/O, the SPDIF out, GPIOs, gameport and MPU401 midi I/O.

- **2.1.1.3.1** The AC97 port supports two AC97 codecs. The primary codec must be Rev 1.03, 2.0 or 2.1. The secondary codec must be Rev 2.0 or 2.1.

- 2.1.1.3.2 The I2S port supports data out at 48 KSPS only and inputs at rates from 8 to 48 KSPS. Output can come from I2S L/R Output Buffer or SURR L/R Output FIFO. The input data rate can be determined by reading the 13 lsbs of register 0xCC. The sample rate = (I2S\_DELTA)\*60. The

transmitter sends 20 bits stereo and the receiver receives 20 stereo. When the I2S data in receives more than 20 bits, the Isb's are truncated. If the receiver receives less than 20 bits, zeros are appended to the Isbs.

- **2.1.1.3.3** The SPDIF output only supports Mode 0 consumer 20 bit audio data that is sampled at 48 kHz. If the receiver needs fewer bits, then the lsbs will be truncated.

- **2.1.1.3.4** The GPIO pins are 5V tolerant programmable I/O pins. They can be programmed to either inputs or output via a register at offset 7Ch. On power up all the pins default to inputs.

If any of the GPIO pins are used for hardware control pins, the best programming procedure would be to leave the i/o pins as inputs, then set the output bits to highs or lows, then change the selected I/O pins to outputs. This will avoid the possibility of glitches on the output. Since the pins power up as inputs, they will be floating and so  $30~\mathrm{k}\Omega$  resistors are needed to put the pin into a know state on power up.

The inputs can be read from the same register 7Ch. The CPU must poll the 7Ch to see if any of the inputs have changed state.

**2.1.1.3.5** The Game port pins are 5V tolerant I/O pins and support the standard dual analog joysticks.

The enhanced mode works will all normal analog input joysticks. The CPU can read internal counters rather than measuring the time constants of each of the X, Y inputs with software timing loops.

**2.1.1.3.6** The LM4560 supports the standard MPU 401 uart mode midi interface.

# 3.0 Register Description

### 3.1 PCI CONFIGURATION REGISTER MAP

| Offset | +3h                        | +2h          | +1h                 | +0h             |  |

|--------|----------------------------|--------------|---------------------|-----------------|--|

| 00h    | Device ID                  |              | Vendor ID           |                 |  |

| 04h    | Sta                        | ntus         | Command             |                 |  |

| 08h    |                            | Class Code   |                     | Revision ID     |  |

| 0Ch    | BIST                       | Header Type  | Latency Timer       | Cache Line Size |  |

| 10h    | Audio IO B                 |              | ase Address         |                 |  |

| 14h    |                            | Audio Memory | Base Address        | Base Address    |  |

| 18–28h |                            | RS           | VD                  |                 |  |

| 2Ch    | Subsystem ID               |              | Subsystem Vendor ID |                 |  |

| 30h    | RSVD                       |              |                     |                 |  |

| 34h    | RSVD                       |              |                     | Cap_Ptr         |  |

| 38h    | RS                         |              | VD                  |                 |  |

| 3Ch    | MAX_LAT                    | MIN_GNT      | Interrupt Pin       | Interrupt Line  |  |

| 40h    | DDMA Slave CFG             |              |                     |                 |  |

| 44h    | PM_Timer                   | PM_CFG       | LEGACY_DMA          | LEGACY_IOBASE   |  |

| 48h    | RSVD                       |              | INT_VEC             | INTA_SNOOP_ENA  |  |

| DCh    | PMC                        |              | PM_Next_Ptr         | PM_Cap_ID       |  |

| E0h    | Power Value Data PMCSR_BSE |              | PMG                 | CSR             |  |

#### 3.1.1 PCI Configuration Register Description

## 3.1.1.1 Device ID & Vendor ID

PCI Configuration

Address: 00h-03h

Default: 001B100Bh

Description: read/write, can be written only when

CFG46h[6]=1

Bit 31–16 device ID: default 001Bh Bit 15–0 vendor ID: default 100Bh

#### 3.1.1.2 Status & Command:

PCI Configuration

Address: 04h-07h

Default: 02900000h

Description: Bit 2-0: R/W

Bit 28: TA Received target abort. Write 1 to clear.

Bit 29: MA Received master abort. Write 1 to clear.

Bit 20: PM PCI Power Management support, hardwired to 1

Bit 23, 25: hardwired to 1 The rest bits: hardwired to 0

### 3.1.1.3 Class Code & Revision ID:

PCI Configuration

Address: 08h-0Bh

Default: 04010001h

Description: read only

Bit 7-0: 01 revision ID

Bit 31–24: 04 Base class: Multimedia Bit 23–16: 01 Sub-class: Audio device

Bit 15-8: 00 Interface

#### 3.1.1.4 BIST, Header Type, Latency Timer & Cache Line

Size:

PCI Configuration

Address: 0Ch-0Fh

Default: 00000000h

Description:

Bit 15–12: R/W

The rest bits: hardwired to 0

### 3.1.1.5 Audio IO Base Register:

PCI Configuration

Address: 10h-13h

Default: 00000001h

Description:

Bit 31–8: R/W Audio IO base Bit 7–1: Hardwire to 0 Bit 0: Hardwire to 1

#### 3.1.1.6 Audio MEM Base Register:

PCI Configuration

Address: 14h-17h

Default: 00000000h

Description:

Bit 31-12: R/W Audio MEM base

Bit 11-0: Hardwire to 0

# 3.1.1.7 Subsystem ID & Subsystem vendor ID:

PCI Configuration

Address: 2Ch-2Fh

Default: 001B100Bh

Description: read only

Bit 31–16: subsystem ID: default 001Bh Bit 15–0: subsystem vendor ID: default 100Bh

#### 3.1.1.8 PCIPM Capability List Pointer Register:

PCI Configuration

Address: 34h–37h

Default: 000000DCh

Description: Read Only

#### 3.1.1.9 Max\_Lat, Min\_Gnt, Interrupt Pin & Interrupt

Line:

PCI Configuration

Address: 3Ch-3Fh

Default: 18020100h

Description:

Bit 7-0: INT line R/W

Bit 15–8: INT pin hardwired to 01 Bit 23–16: Min\_Gnt hardwired to 02 Bit 31–24: Max\_Gnt hardwired to 18

#### 3.1.1.10 DDMA Slave Configuration Register

PCI Configuration Address: 40h-43h

Type: Read/Write Default: 00000000h

Bit 0: DDMA Slave Channel Access Enable Control

0 disabled 1 enabled

When disabled, the DDMABase is not usefull and the PCM sample playback control registers cannot be accessed through DDMA Slave channel method.

When enabled, LM4560 can behave like a DDMA Slave channel device. DDMA Master will transfer the legacy DMA controller channel specific information to the related DDMA Slave channel control register when software trying to program the legacy DMA controller register.

Bit 2..1 Legacy DMA Transfer Size Control, Read Only as 00 00 8 bit transfer, legacy

Bit 3 Non Legacy Extended Addressing Control (Fully 32 bit Addressing)

0 disabled 1 enabled

Bit 31..4 DDMABase

# 3.1.1.11 Legacy audio/ power management configuration:

PCI Configuration

Address: 44h–47h

Type: Read/Write

Default: E2000000h

bit 0:

0: SBBase = 0220h-022Fh 1: SBBase = 0240h-024Fh

legacy I/O decoding 44h

bit 1

0: SBBase disable

bit 2

0: ADLIBBase = 0388h-038Bh

1: ADLIBBase = 038Ch-038Fh

bit 3

0: ADLIBBase disable 1: ADLIBBase enable

bit 4

0: GAMEBase = 0200h-0207h 1: GAMEBase = 0208h-020Fh

bit 5

0: GAMEBase disable

1: GAMEBase enable

bit 6

0: MPU401Base = 0330h-0333h 1: MPU401Base = 0300h-0303h

bit 7

0: MPU401Base disable1: MPU401Base enablelegacy DMA decoding 45h

bit 0

0: DMA channel 1 trapping1: DMA channel 0 trapping

bit 1

0: DMA trapping

disable 1: DMA trapping enable

bit 2

0: DMA status handle mode A (slave only)

1: DMA status handle mode B (bus master)

bit 3

0: DMA status retry OK

1: DMA status retry error

If bit 3 is set, bus interface will not respond to IO8 operation any more unless the status retry error bit is cleared by writing 1 to this bit.

bit 4 DMAREG\_RD\_EN\_

0: Response to DMAREG(00h-03h, 83h/87h) Read when CFG45[1] is 1;

1: Never response to DMAREG(00h-03h, 83h/87h) Read.

bits 5-7 reserved

when DMA trapping is enable, chip will decode the following

I/O port

DMA channel 1 trapping

read 2,3 write snoop 2,3 write snoop 8–Fh write snoop 83h

### DMA channel 0 trapping

read 0,1 write snoop 0,1 write snoop 8–Fh write snoop 87h

when DMA trapping is enable, the chip will handle DMA status read (I/O read port 8) depending on the DMA status mode bit.

DMA status handle mode A:

LM4560 will decode I/O read port 8 if StatusRDY is active,

otherwise, it will ignore the cycle. DMA status handle mode B:

When StatusRDY is not active, the chip will retry DMA status reads if it is not the current active bus master. Whenever chip retry the DMA status read from other bus master, it will also generate a bus request for the DMA status read. When the DMA status read cycle generated by chip is terminated normally, the chip will write the status data by asserting the StatusWR signal.

If chip retries a DMA status read from other bus master 3 times without getting the bus ownership or proper data, it will set the status error bit high which will terminate the pending DMA status read request internally and ignore the all DMA status read cycle by the other bus master.

When audio engine receives the StatusWR signal, it will assert the StatusRDY signal and allow the chip to decode I/O read port 8 normally. The audio engine will de-assert the StatusRDY after each DMA status read.

Note: All I/O decoding is 16 bits, write snooping happens only once even with multiple write retry cycles. Write snooping means chip will decode the cycle to the audio engine without generating the DEVSEL signal or TRDY on the PCI bus.

#### Power Management Configuration (PM\_CFG) 46h

Bit 0 (DCC\_EN) Dynamic Clock Control Enable

0: Disable

1: Enable. CLKRUN scheme will be enabled.

Bit 1 (DC\_PM\_EN\_) Digital Controller Power Management Enable

0: Enable When enabled, Audio\_clk can be shut off or turn on according to PM\_ST.

1: Disable

Bit 2 (DC\_RST) Digital Controller Software Reset

0: normal

1: Reset Digital Controller

Bit 3 (AC\_PM\_EN\_) Analog CODEC Power Management Enable

0: Enable

If enabled, AC97 bit clock can be shut off according to PM ST  $\,$

1 Disable

Bit 4 (WAKE\_EN1) Primary CODEC Wake-up Enable Read/Write. Powered with Vaux. Cleared when H/W reset or S/W reset.

0: disable

1: enable

When CODEC\_PD = 1, BCLK keeps low, a rising edge of ACDI1 will set WAVE\_EV to high

Bit 5 (WAKE\_EN2) Secondary CODEC Wake-up Enable Read/Write. Powered with Vaux. Cleared when H/W reset or S/W reset.

0: disable

1: enable

When CODEC\_PD = 1, BCLK keeps low, a rising edge of ACDI2 will set WAVE\_EV to high

Bit 6 (ID\_WR\_EN) Chip IDs write enable

0: Vendor ID, Device ID, Subsystem vendor ID & Subsystem ID are read only

1: Vendor ID, Device ID, Subsystem vendor ID & Subsystem ID are writeable.

Bit 7 (TIMER\_PME\_EN) Inactivity Timer assert PME enable

0: Disable

1: Enable

If enabled, when the Inactivity Timer is expired,  $\overline{\text{PME}}$  will be asserted.

#### **Inactivity Timer Expiration Control 47h**

bit 0-7 Inactivity timer expiration base (in seconds)

Each time when audio engine enters into D2 state, the Inactivity timer will load the base count from this register and start counting at 1s clock rate. When the MSB of the counter goes from high to low timer has expired. When not in the D2 state, the timer is reset.

#### 3.1.1.12 INT Acknowledge Snoop Register:

### **PCI Configuration**

Address: 48h–4Bh

Default: 00000000h

Description: Read/Write

Bit 0 (INTA\_SNOOP\_ENA) Interrupt Acknowledge Snooping

Enable bit.

0: Disable

1: Enable

Bit 15-7 (INT\_VEC) Interrupt Vector to be matched.

All other bits are reserved.

# 3.1.1.13 Power Management Capability Register (PMC): PCI Configuration

Address: DCh-DFh

Default: 66010001h

Description: Read Only

Bit 7-0 (PM\_Cap\_ID) Power management capability identi-

fier, read only as 01h.

Bit 15-8 (PM\_Next\_Ptr) Next data structure item list pointer in the PCI header, read only as 00h

in the FCI fleader, fead only as our

Bit 31–16 (PM\_CAP) Power management capability register, read only as E611h.

ter, read only as Eorm.

Bit 31–27 (PME\_Support)  $\overline{\text{PME}}$  supported PM\_ST, read only as 01100b, indicates that  $\overline{\text{PME}}$  can be asserted in D2, D3

not.

Bit 26 (D2\_Support) Read only as 1, indicates D2 supported.

Bit 25 (D1\_Support) Read only as 1, indicates D1 supported.

Bit 24-22 Reserved. Read only as 000b.

Bit 21 (DSI) Device Specific Initialization. Read only as 0.

Bit 20 (Vaux) Auxiliary Power Source. Read only as 0.

Bit 19 (PME\_clk) PME clock. Read only as 0, indicates that no PCI clock is required to generate  $\overline{\text{PME}}$ .

Bit 18–16 (Version) Read only as 001b, indicates PPMI v1.0 compliance

# 3.1.1.14 Power management control/status register (PMCSR) & PMCSR\_BSE & Data:

#### **PCI** Configuration

Address: E0h–E3h

Default: 00000000h

Description: Read/Write

Bit 31-24 (Data) Read only as 00h.

Bit 23-16 (PMCSR\_BSE) Read only as 00h.

Bit 15-0 (PMCSR) Power Management Control/Status Reg-

Bit 15 (PME\_Status) Read/Write-Clear.

0: (Default) Normal (PME is controlled by bit[8] PME\_En)

1: PME can be asserted independent of bit[8] (PME\_En). Writing 0 to this bit has no effect.

Writing 1 to this bit will clear this bit, and also cause chip to stop asserting  $\overline{\text{PME}}.$

Bit 14-13 (Data\_Scale) Read only as 00b.

Bit 12-9 (Data\_Select) Read only as 0000b.

Bit 8 (PME\_En) Read/Write.

0: (Default) PME is disabled to be asserted.

1: PME is enabled to be asserted.

Bit 7–2 Reserved. Read only as 000000b.

Bit 1-0 (PM\_ST) Power State. Read/Write.

Read will return current Power State, write will set to new state.

00 D0

01 D1

10 D2

11 D3 hot

| IO Offset | +3h               | +2h       | +1h             | +0h    |

|-----------|-------------------|-----------|-----------------|--------|

| 00h       | DMAR3             | DMAR2     | DMAR1           | DMAR0  |

| 04h       | DMAR7             | DMAR6     | DMAR5           | DMAR4  |

| 08h       | DMAR11            | DMAR10    | DMAR9           | DMAR8  |

| 0Ch       | DMAR15            | DMAR14    | DMAR13          | DMAR12 |

| 10h       | SBR3/SBR1         | SBR2      | SBR1/SBR3       | SBR0   |

| 14h       | RSVD              | SBR6      | SBR5            | SBR4   |

| 18h       | RSVD              | SBR7      | RSVD            | RSVD   |

| 1Ch       | SBR10             | SBR9      | RSVD            | SBR8   |

| 20h       | MPUR3             | MPUR2     | MPUR1           | MPUR0  |

| 24h-2Ch   | RSVD              |           |                 |        |

| 30h       | RSVD              | RSVD      | GAMER1          | GAMER  |

| 34h       | GAMER2            |           |                 |        |

| 38h       | GAMER3            |           |                 |        |

| 3Ch       | RSVD              |           |                 |        |

| 40h       | ACWR              |           |                 |        |

| 44h       | ACRD              |           |                 |        |

| 48h       | SCTRL             |           |                 |        |

| 4Ch       | ACGPIO            |           |                 |        |

| 50h       | ASR0              |           |                 |        |

| 54h       | RSVD              | ASR2      | RSVD            | ASR1   |

| 58h       | ASR3              |           | 1               |        |

| 5Ch       | ASR6              | ASR5      | RSVD            | ASR4   |

| 60h       | AOPLSR0           |           |                 |        |

| 70h       | SPDIF_CS          |           |                 |        |

| 74h       | RSVD              |           |                 |        |

| 78h       | SubSystem ID      |           | SubVendor ID    |        |

| 7Ch       | PCI ID read       | GPcontrol | GPO             | GPI    |

| 80h       | START_A           |           | 1               |        |

| 84h       | STOP_A            |           |                 |        |

| 88h       | DLY               |           |                 |        |

| 8Ch       | SIGN_CSO          |           |                 |        |

| 90h       | CSPF_A            |           |                 |        |

| 94h       | CEBC              |           |                 |        |

| 98h       | AIN_A             |           |                 |        |

| 9Ch       | EINT              |           |                 |        |

| A0h       | GC                | GC        |                 | CIR    |

| A4h       | AINTEN_A          |           | I.              |        |

| A8h       | MUSICVOL          |           |                 |        |

| ACh       | SBDELTA/SBDELTA R |           | WAVEVOL<br>RSVD |        |

| B0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IO Offset | +3h         | +2h                     | +1h                           | +0h          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-------------------------|-------------------------------|--------------|

| B8h         STOP_B           BCh         CSPF_B           C0h         SBDMAL           C4h         SCE2R           RSVD         SBDD           SBCTRL           C3H         STIMER           CCh         LFO_CTRL_B         LFO_CT_B         RSVD + I²S_DELTA           D0h         ST_TARGET         D4h         RSVD           D8h         AINT_B         AINT_B         D0ch         AINTEN_B           Bank A: Channel Register           ARAM_A (CIR<32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B0h       | MISCINT     |                         |                               |              |

| BCh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B4h       | START_B     |                         |                               |              |

| C0h         SBDMAL         SBDMAC           C4h         SCE2R         RSVD         SBDD         SBCTRL           C8H         STIMER         CCh         LFO_CTRL_B         LFO_CT_B         RSVD + I²S_DELTA           D0h         ST_TARGET         D0h         RSVD           D8h         AINT_B         DCh         AINTEN_B           Bank A: Channel Register         ARAM_A (CIR<32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | B8h       | STOP_B      |                         |                               |              |

| C4h         SCE2R         RSVD         SBDD         SBCTRL           C8H         STIMER         CCh         LFO_CTRL_B         LFO_CT_B         RSVD + i²S_DELTA           D0h         ST_TARGET         D4h         RSVD           D8h         AINT_B         DCh         AINTEN_B           Bank A: Channel Register           ARAM_A (CIR<32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BCh       | CSPF_B      |                         |                               |              |

| C8H         STIMER           CCh         LFO_CTRL_B         LFO_CT_B         RSVD + I²S_DELTA           D0h         ST_TARGET         D4h         RSVD           D8h         AINT_B         AINTEN_B           Bank A: Channel Register           ARAM_A (CIR<32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C0h       | SBDMAL      |                         | SBDMAC                        |              |

| CCh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C4h       | SCE2R       | RSVD                    | SBDD                          | SBCTRL       |

| D0h         ST_TARGET           D4h         RSVD           D8h         AINT_B           DCh         AINTEN_B           Bank A: Channel Register           ARAM_A (CIR<32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C8H       | STIMER      |                         |                               |              |

| D4h         RSVD           D8h         AINT_B           DCh         AINTEN_B           Bank A: Channel Register           ARAM_A (CIR<32)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CCh       | LFO_CTRL_B  | LFO_CT_B                | RSVD + I <sup>2</sup> S_DELTA |              |

| D8h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D0h       | ST_TARGET   |                         |                               |              |

| Bank A: Channel Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D4h       | RSVD        |                         |                               |              |

| Bank A: Channel Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D8h       | AINT_B      |                         |                               |              |

| ### ARAM_A (CIR<32)  ### CONTR + LBA  ### ESO  ### ECH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DCh       | AINTEN_B    |                         |                               |              |

| E0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |             | Bank A: Channel Registe | er                            |              |

| E4h         CPTR + LBA           E8h         ESO           ECh         LFO_CTRL         LFO_CT         FMC+RVOL[6:1]         RVOL[0]+CVOL           F0h         GVSEL + PAN         VOL         CTRL + Ec(11:8)         Ec(7:0)           F4h         EBUF1         EBUF2         ECTRL + Ec(11:8)         ECTRL + Ec(11:8) <t< td=""><td></td><td></td><td>ARAM_A (CIR&lt;32)</td><td></td><td></td></t<> |           |             | ARAM_A (CIR<32)         |                               |              |

| E8h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E0h       | CSO         |                         | FMS+ALPHA(11:8)               | ALPHA(7:0)   |

| ECh         LFO_CTRL         LFO_CT         FMC+RVOL[6:1]         RVOL[0]+CVOL           F0h         GVSEL + PAN         VOL         CTRL + Ec(11:8)         Ec(7:0)           F4h         EBUF1           F8h         EBUF2           FCh         RSVD           Bank B: Channel Register           ARAM_B (CIR>=32)           E0h         CSO         FMS+ALPHA(11:8)         ALPHA(7:0)           E4h         CPTR + LBA         E8h         ESO         DELTA           ECh         ATTRIBUTE         FMC+RVOL[6:1]         RVOL[0]+CVOL           ERAM_B (CIR>=32)         F0h         GVSEL + PAN         LFO_INIT(Bank A)         CTRL + VOL(11:8)         VOL(7:0)           F4h         RSVD           F8h         RSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | E4h       | CPTR + LBA  |                         |                               |              |

| F0h         GVSEL + PAN         VOL         CTRL + Ec(11:8)         Ec(7:0)           F4h         EBUF1         F8h         EBUF2           FCh         RSVD         Bank B: Channel Register           ARAM_B (CIR>=32)           E0h         CSO         FMS+ALPHA(11:8)         ALPHA(7:0)           E4h         CPTR + LBA         E8h         ESO         DELTA           ECh         ATTRIBUTE         FMC+RVOL[6:1]         RVOL[0]+CVOL           ERAM_B (CIR>=32)         F0h         GVSEL + PAN         LFO_INIT(Bank A)         CTRL + VOL(11:8)         VOL(7:0)           F4h         RSVD           F8h         RSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E8h       | ESO         |                         | DELTA                         |              |

| F4h         EBUF1           F8h         EBUF2           FCh           RSVD           Bank B: Channel Register           ARAM_B (CIR>=32)           E0h         CSO         FMS+ALPHA(11:8)         ALPHA(7:0)           E4h         CPTR + LBA         DELTA           E8h         ESO         DELTA           ECh         ATTRIBUTE         FMC+RVOL[6:1]         RVOL[0]+CVOL           ERAM_B (CIR>=32)           F0h         GVSEL + PAN         LFO_INIT(Bank A)         CTRL + VOL(11:8)         VOL(7:0)           F4h         RSVD           F8h         RSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ECh       | LFO_CTRL    | LFO_CT                  | FMC+RVOL[6:1]                 | RVOL[0]+CVOL |

| F8h         EBUF2           FCh         RSVD           Bank B: Channel Register           ARAM_B (CIR>=32)           E0h         CSO         FMS+ALPHA(11:8)         ALPHA(7:0)           E4h         CPTR + LBA         DELTA           E8h         ESO         DELTA           ECh         ATTRIBUTE         FMC+RVOL[6:1]         RVOL[0]+CVOL           ERAM_B (CIR>=32)           F0h         GVSEL + PAN         LFO_INIT(Bank A)         CTRL + VOL(11:8)         VOL(7:0)           F4h         RSVD           F8h         RSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | F0h       | GVSEL + PAN | VOL                     | CTRL + Ec(11:8)               | Ec(7:0)      |

| ### RSVD    Bank B: Channel Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | F4h       | EBUF1       |                         |                               |              |

| Bank B: Channel Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | F8h       | EBUF2       |                         |                               |              |

| ARAM_B (CIR>=32)  E0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FCh       | RSVD        |                         |                               |              |

| E0h         CSO         FMS+ALPHA(11:8)         ALPHA(7:0)           E4h         CPTR + LBA         BEBH         ESO         DELTA           ECh         ATTRIBUTE         FMC+RVOL[6:1]         RVOL[0]+CVOL           ERAM_B (CIR>=32)           F0h         GVSEL + PAN         LFO_INIT(Bank A)         CTRL + VOL(11:8)         VOL(7:0)           F4h         RSVD           F8h         RSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |             | Bank B: Channel Registe | er                            |              |

| E4h         CPTR + LBA           E8h         ESO           ECh         ATTRIBUTE           FMC+RVOL[6:1]         RVOL[0]+CVOL           ERAM_B (CIR>=32)           F0h         GVSEL + PAN         LFO_INIT(Bank A)         CTRL + VOL(11:8)         VOL(7:0)           F4h         RSVD           F8h         RSVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |             | ARAM_B (CIR>=32)        |                               |              |