LMX2323 PLLatinum 2.0 GHz Frequency Synthesizer for RF Personal

**Communications**

Literature Number: SNAS057C

October 2000

# LMX2323 PLLatinum<sup>™</sup> 2.0 GHz Frequency Synthesizer for RF Personal Communications

# **General Description**

The LMX2323 is a high performance frequency synthesizer with integrated 32/33 dual modulus prescaler designed for RF operation up to 2.0 GHz. Using a proprietary digital phase locked loop technique, the LMX2323's linear phase detector characteristics can generate very stable, low noise control signals for UHF and VHF voltage controlled oscillators.

Serial data is transferred into the LMX2323 via a three-line MICROWIRE<sup>™</sup> interface (Data, LE, Clock). Supply voltage range is from 2.7V to 5.5V. The LMX2323 features very low curent consumption, typically 3.5mA at 3V. The charge pump provides 4 mA output current.

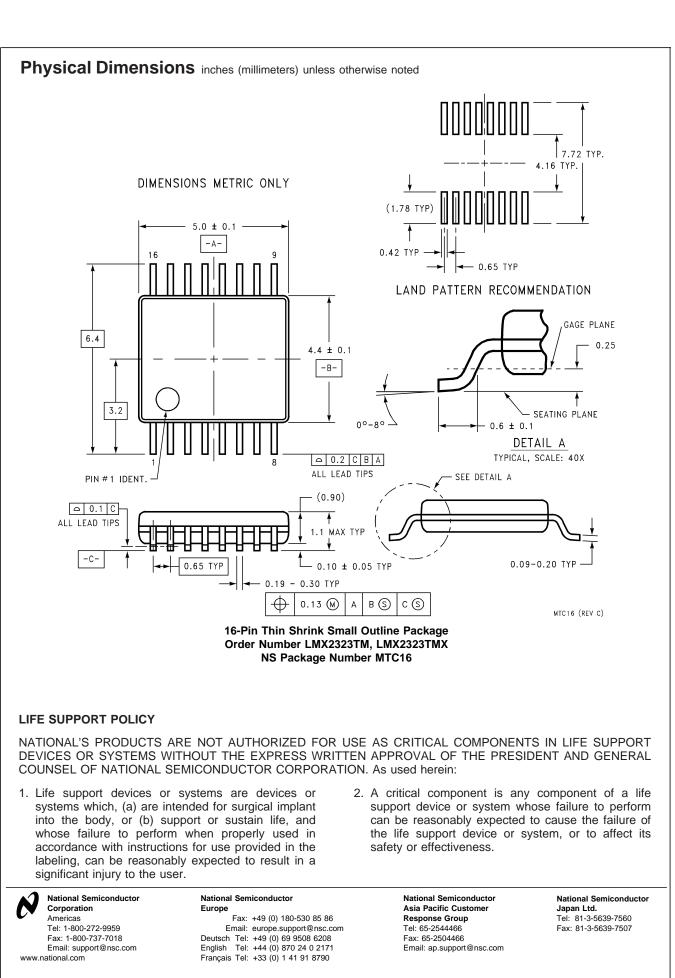

The LMX2323 is manufactured using National's ABiC V BiCMOS process and is packaged in a 16-pin TSSOP.

### Features

- RF operation up to 2.0 GHz

- 2.7V to 5.5V operation

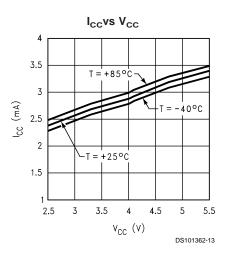

- Low current consumption: Icc = 3.5mA (typ) at Vcc=3.0V

- Digital Lock Detect

- Dual modulus prescaler: 32/33

- Internal balanced, low leakage charge pump

# **Applications**

- Cellular telephone systems (GSM, NADC, CDMA, PDC, PHS)

- Personal wireless communications (DCS-1800, DECT, CT-1+)

- Wireless local area networks (WLANs)

- DCS/PCS infrastructure equipment

- Other wireless communication systems

TRI-STATE® is a registered trademark of National Semiconductor Corporation. MICROWIRE™ and PLLatinum™ are trademarks of National Semiconductor Corporation

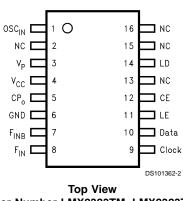

# **Connection Diagram**

#### Order Number LMX2323TM, LMX2323TMX See NS Package Number MTC16

# **Pin Descriptions**

| Pin No.          | Pin<br>Name       | I/O | Description                                                                                                                                                                                                                                              |

|------------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | OSC <sub>IN</sub> | I   | Oscillator input. A CMOS inverting gate input. The input has a $V_{CC}/2$ input threshold and can be driven from an external CMOS or TTL logic gate.                                                                                                     |

| 3                | V <sub>P</sub>    | _   | Power supply for charge pump. Must be $\geq V_{CC}$ .                                                                                                                                                                                                    |

| 4                | V <sub>cc</sub>   | _   | Power supply voltage input. Input may range from 2.7V to 5.5V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane.                                                                        |

| 5                | CPo               | 0   | Internal charge pump output. For connection to a loop filter for driving the voltage control input of an external oscillator.                                                                                                                            |

| 6                | GND               |     | Ground.                                                                                                                                                                                                                                                  |

| 7                | f <sub>INB</sub>  | Ι   | RF prescaler complimentary input. In single-ended mode, a bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane. The LMX2323 can be driven differentially when a bypass capacitor is omitted. |

| 8                | f <sub>IN</sub>   | I   | RF prescaler input. Small signal input from the voltage controlled oscillator.                                                                                                                                                                           |

| 9                | Clock             | I   | High impedance CMOS Clock input. Data is clocked in on the rising edge, into the various counters and registers.                                                                                                                                         |

| 10               | Data              | I   | Binary serial data input. Data entered MSB first. LSB is control bit. High impedance CMOS input.                                                                                                                                                         |

| 11               | LE                | I   | Load Enable input. When Load Enable transitions HIGH, data is loaded into either the N or R register (control bit dependent). See timing diagram.                                                                                                        |

| 12               | CE                | I   | PLL Enable. A LOW on CE powers down the device asynchronously and TRI-STATE®s the charge pump output.                                                                                                                                                    |

| 14               | LD                | 0   | Lock detect output. This pin can be programmed to provide R counter output, N counter output, digital lock detect (CMOS logic) or analog lock detect (open drain).                                                                                       |

| 2, 13,<br>15, 16 | NC                |     | No Connect.                                                                                                                                                                                                                                              |

# Absolute Maximum Ratings (Note 1)

| –0.3V to 6.5V<br>V <sub>CC</sub> to 6.5V |

|------------------------------------------|

|                                          |

| –0.3V to V <sub>CC</sub> + 0.5V          |

| –65°C to +150°C                          |

| ) +260°C                                 |

| 2 kV                                     |

|                                          |

## Recommended Operating Conditions (Note 1)

| Power Supply Voltage (V <sub>CC</sub> )             | 2.7V to 5.5V          |

|-----------------------------------------------------|-----------------------|

| Power Supply for Charge pump ( $V_P$ )              | $V_{CC}$ to 5.5V      |

| Operating Temperature (T <sub>A</sub> )             | –40°C to +85°C        |

| Note 1: Absolute Maximum Ratings indicate limits be | evond which damage to |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Conditions indicate conditions for which the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

**Note 2:** This device is a high performance RF integrated circuit and is ESD sensitive. Handling and assembly of this device should be done on ESD protected workstations.

## **Electrical Characteristics**

$V_{CC}$  = 3.0V,  $V_{P}$  = 3.0V; -40°C <  $T_{A}$  < 85°C except as specified.

| Symbol                                              | Parameter                                                           | Conditions                                                                   | Min                  | Тур  | Max                  | Units           |

|-----------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|------|----------------------|-----------------|

| GENERAL                                             |                                                                     |                                                                              |                      |      | •                    |                 |

| I <sub>cc</sub>                                     | Power Supply Current                                                | $V_{\rm CC} = 3.0 V$                                                         |                      | 3.5  |                      | mA              |

| I <sub>cc</sub>                                     | _                                                                   | V <sub>CC</sub> = 2.7V to 5.5V                                               |                      |      | 7.0                  | mA              |

| I <sub>CC</sub> -PWDN                               | _                                                                   | V <sub>CC</sub> = 5.5V (Note 3)                                              |                      | 10   | 20                   | μA              |

| f <sub>IN</sub>                                     | RF Operating Frequency                                              |                                                                              | 0.1                  |      | 2.0                  | GHz             |

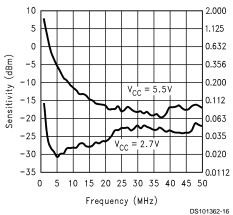

| f <sub>osc</sub>                                    | Oscillator Frequency                                                |                                                                              | 5                    |      | 40                   | MHz             |

| fφ                                                  | Phase Detector Frequency                                            |                                                                              |                      |      | 10                   | MHz             |

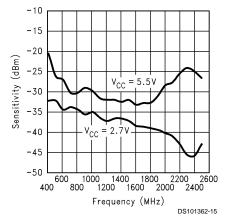

| Pf <sub>IN</sub>                                    | RF Input Sensitivity                                                | 2.7V≤Vcc≤ 3.0V                                                               | -15                  |      | 0                    | dBm             |

|                                                     |                                                                     | 3.0 <vcc≤5.0v< td=""><td>-10</td><td></td><td>0</td><td>dBm</td></vcc≤5.0v<> | -10                  |      | 0                    | dBm             |

| Vosc                                                | Oscillator Sensitivity                                              |                                                                              | 0.4                  | 0.8  | V <sub>CC</sub> -0.3 | V <sub>PP</sub> |

|                                                     | Phase Noise (Note 4)                                                | $f_{IN}$ = 900 MHz, $V_{OSC} \ge 0.8 V_{PP}$                                 |                      | -86  |                      |                 |

|                                                     |                                                                     | $f_{IN}$ = 900 MHz, $V_{OSC} \ge 0.4 V_{PP}$                                 |                      | -82  | (Niete 6)            |                 |

|                                                     |                                                                     | $f_{IN}$ = 1800 MHz, $V_{OSC} \ge 0.8 V_{PP}$                                |                      | -82  | (Note 6)             | dBc/Hz          |

|                                                     |                                                                     | $f_{IN}$ = 1800 MHz, $V_{OSC} \ge 0.4 V_{PP}$                                |                      | -80  | 1                    |                 |

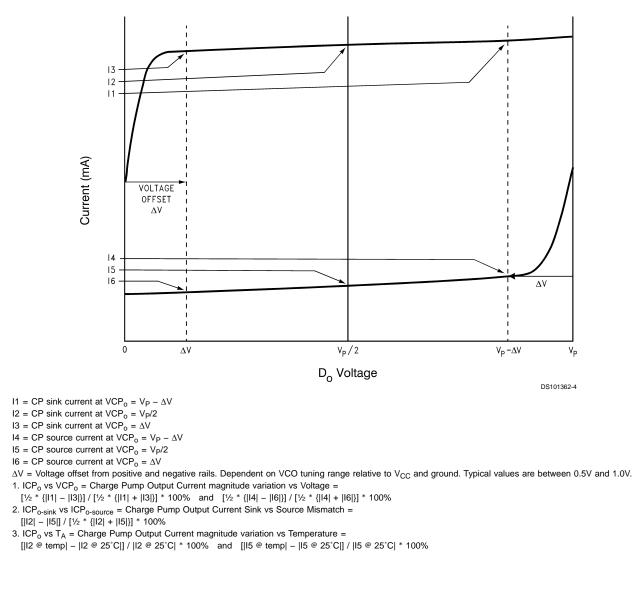

| CHARGE PL                                           | JMP                                                                 |                                                                              |                      |      | •                    |                 |

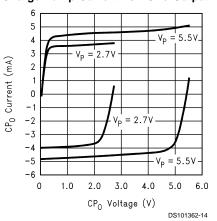

| I <sub>CPo-source</sub>                             | Charge Pump Output Current                                          | $V_{CPo} = V_P/2$                                                            |                      | -4.3 |                      | mA              |

| I <sub>CPo-sink</sub>                               |                                                                     | $V_{CPo} = V_P/2$                                                            |                      | 4.3  |                      | mA              |

| I <sub>CPo-Tri</sub>                                | Charge Pump TRI-STATE<br>Current                                    | $0.5 \le V_{CPo} \le V_{P} - 0.5$                                            | -2.5                 |      | 2.5                  | nA              |

| I <sub>CPo</sub> vs<br>V <sub>CPo</sub>             | Charge Pump Output Current<br>Magnitude Variation vs Voltage        | $0.5 \le V_{CPo} \le V_P - 0.5$<br>$T_A = 25^{\circ}C$                       |                      | 10   |                      | %               |

| I <sub>CPo-sink</sub> VS<br>I <sub>CPo-source</sub> | Charge Pump Output Current<br>Sink vs Source Mismatch               | $V_{CPo} = V_P/2$<br>$T_A = 25^{\circ}C$                                     |                      | 5    |                      | %               |

| I <sub>CPo</sub> vs T                               | Charge Pump Output Current<br>Magnitude Variation vs<br>Temperature | $V_{CPo} = V_P/2$                                                            |                      | 8    |                      | %               |

| DIGITAL INT                                         | ERFACE (DATA, CLK,LE, CE)                                           |                                                                              |                      |      | •                    |                 |

| V <sub>OH</sub>                                     | High-Level Output Voltage                                           | I <sub>OH</sub> = -500 μA                                                    | V <sub>CC</sub> -0.4 |      |                      | V               |

| V <sub>OL</sub>                                     | Low-Level Output Voltage                                            | I <sub>OL</sub> = -500 μA                                                    |                      |      | 0.4                  | V               |

| V <sub>IH</sub>                                     | High-Level Input Voltage<br>(Note 5)                                |                                                                              | 0.8Vcc               |      |                      | V               |

| V <sub>IL</sub>                                     | Low-Level Input Voltage (Note 5)                                    |                                                                              |                      |      | 0.2Vcc               | V               |

| I <sub>IH</sub>                                     | High-Level Input Current (Clock,<br>Data, Load Enable)              | $V_{IH} = V_{CC} = 5.5V$                                                     | -1.0                 |      | 1.0                  | μA              |

| I <sub>IL</sub>                                     | Low-Level Input Current (Clock,<br>Data, Load Enable)               | $V_{IL} = 0, V_{CC} = 5.5V$                                                  | -1.0                 |      | 1.0                  | μA              |

| I <sub>IH</sub>                                     | Oscillator Input Current                                            | $V_{IH} = V_{CC} = 5.5V$                                                     |                      |      | 100                  | μA              |

| IIL                                                 | Oscillator Input Current                                            | $V_{IL} = 0, V_{CC} = 5.5V$                                                  | -100                 |      |                      | μA              |

### Electrical Characteristics (Continued)

$V_{CC} = 3.0V$ ,  $V_{P} = 3.0V$ ;  $-40^{\circ}C < T_{A} < 85^{\circ}C$  except as specified.

| Symbol           | Parameter                   | Conditions            | Min | Тур | Max | Units |

|------------------|-----------------------------|-----------------------|-----|-----|-----|-------|

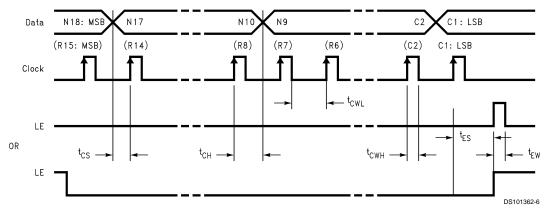

| MICROWIRE        | TIMING                      |                       |     |     |     |       |

| t <sub>cs</sub>  | Data to Clock Set Up Time   | See Data Input Timing | 50  |     |     | ns    |

| t <sub>CH</sub>  | Data to Clock Hold Time     | See Data Input Timing | 10  |     |     | ns    |

| t <sub>CWH</sub> | Clock Pulse Width High      | See Data Input Timing | 50  |     |     | ns    |

| t <sub>CWL</sub> | Clock Pulse Width Low       | See Data Input Timing | 50  |     |     | ns    |

| t <sub>ES</sub>  | Clock to Enable Set Up Time | See Data Input Timing | 50  |     |     | ns    |

| t <sub>EW</sub>  | Enable Pulse Width          | See Data Input Timing | 50  |     |     | ns    |

Note 3: This I<sub>CC</sub>-PWDN represents CLK, DATA, LE and CE being tied to either higher than 0.8 V<sub>CC</sub> or lower than 0.2 V<sub>CC</sub>.

Note 4: Phase noise is measured 1 kHz off from the carrier frequency. Comparison frequency is 200 kHz. OSCIN frequency is 13 MHz.

Note 5: Except f<sub>IN</sub> and OSC<sub>IN</sub>.

Note 6: Typical values are determined from measurements on the reference evaluation boards. A 3 dB (3 sigma) degradation is estimated from statistical distribution in manufacturing. Units will NOT be tested in production.

## **Charge Pump Current Specification Definitions**

# **Typical Performance Characteristics**

**RF Input Sensitivity vs Frequency**

Charge Pump Current vs VCPo Output

Oscillator Input Sensitivity

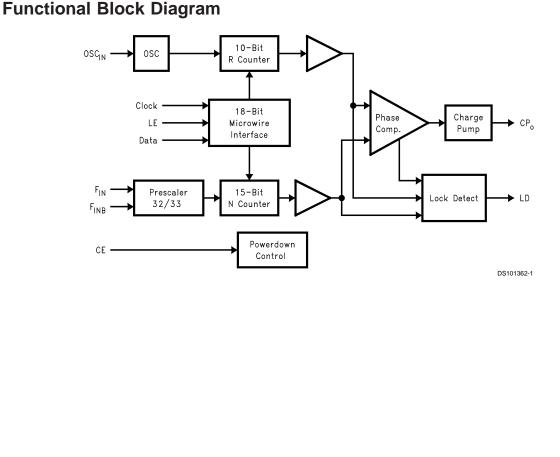

# **1.0 Functional Description**

The basic phase-lock-loop (PLL) configuration consists of a high-stability crystal reference oscillator, a frequency synthesizer such as the National Semiconductor LMX2323, a voltage controlled oscillator (VCO), and a passive loop filter. The frequency synthesizer includes a phase detector, current mode charge pump, as well as programmable reference [R] and feedback [N] frequency dividers. The VCO frequency is established by dividing the crystal reference signal down via the R counter to obtain a frequency that sets the comparison frequency. This reference signal, fr, is then presented to the input of a phase/frequency detector and compared with another signal, fp, the feedback signal, which was obtained by dividing the VCO frequency down by way of the N counter. The phase/frequency detector's current source outputs pump charge into the loop filter, which then converts the charge into the VCO's control voltage. The phase/frequency comparator's function is to adjust the voltage presented to the VCO until the feedback signal's frequency (and phase) match that of the reference signal. When this "phase-locked" condition exists, the RF VCO's frequency will be N times that of the comparison frequency, where N is the divider ratio.

#### 1.1 OSCILLATOR

The reference oscillator frequency for the PLL is provided by an external reference TCXO through the  $OSC_{IN}$  pin.  $OSC_{IN}$  block can operate to 40 MHz. The inputs have a  $V_{CC}/2$  input threshold and can be driven from an external CMOS or TTL logic gate.

#### **1.2 REFERENCE DIVIDER (R COUNTER)**

The R Counter is clocked through the oscillator block. The maximum input frequency is 40 MHz and the maximum output frequency is 10 MHz. The R Counter is a 10-bit CMOS binary counter with a divide range from 2 to 1,023. See programming description 2.2.1.

#### 1.3 PROGRAMMABLE DIVIDER (N COUNTER)

The N counter is clocked by the small signal  $f_{IN}$  input. The LMX2323 RF N counter is a 15-bit integer divider. The N counter is configured as a 5-bit A Counter and a 10-bit B Counter, offering a continuous integer divide range from 992 to 32,767. The LMX2323 is capable of operating from 100 MHz to 2.0 GHz with a 32/33 prescaler.

#### 1.3.1 Prescaler

The RF inputs to the prescaler consist of the  $f_{\rm IN}$  and  $f_{\rm INB}$  pins which are the complimentary inputs of a differential pair amplifier. The differential  $f_{\rm IN}$  configuration can operate to 2 GHz. The input buffer drives the N counter's ECL D-type flip-flops in a dual modulus configuration. The LMX2323 has a 32/33 prescaler ratio. The prescaler clocks the subsequent CMOS flip-flop chain comprising the fully programmable A and B counters.

#### 1.4 PHASE/FREQUENCY DETECTOR

The phase/frequency detector is driven from the N and R counter outputs. The maximum frequency at the phase detector inputs is 10 MHz. The phase detector outputs control the charge pumps. The polarity of the pump-up or pump-down control is programmed using PD\_POL, depending on whether RF VCO characteristics are positive or negative (see programming description 2.2.2). The phase detector also receives a feedback signal from the charge pump, in order to eliminate dead zone.

#### **1.5 CHARGE PUMP**

The phase detector's current source output pumps charge into an external loop filter, which then converts the charge into the VCO's control voltage. The charge pumps steer the charge pump output,  $CP_o$ , to  $V_P$  (pump-up) or Ground (pump-down). When locked,  $CP_o$  is primarily in a TRI-STATE mode with small corrections. The RF charge pump output current magnitude is set to 4.0 mA. The charge pump output can also be used to output divider signals as detailed in section 2.2.3.

#### **1.6 MICROWIRE SERIAL INTERFACE**

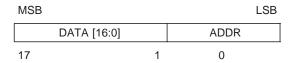

The programmable functions are accessed through the MICROWIRE serial interface. The interface is made of three functions: clock, data and latch enable (LE). Serial data for the various counters is clocked in from data on the rising edge of clock, into the 18-bit shift register. Data is entered MSB first. The last bit decodes the internal register address. On the rising edge of LE, data stored in the shift register is loaded into one of the two appropriate latches (selected by address bits). A complete programming description is included in the following sections.

#### **1.7 LOCK DETECT OUTPUT**

A digital filtered lock detect function is included through an internal digital filter to produce a CMOS logic output available on the LD output pin if selected. The lock detect output is high when the error between the phase detector inputs is less than 15 ns for five consecutive comparison cycles. The lock detect output is more than 30 ns for one comparison cycle. An open drain, analog lock detect status generated from the phase detector is also available on the LD output pin, if selected. The analog lock detect output goes high when the charge pump is inactive. It goes low when the charge pump is active during a comparison cycle. When the PLL is in power down mode, the LD output is always high.

#### **1.8 POWER CONTROL**

The PLL can be power controlled in two ways. The first method is by setting the CE pin LOW. This asynchronously powers down the PLL and TRI-STATEs the charge pump output, regardless of the PWDN bit status. The second method is by programming through MICROWIRE, while keeping the CE HIGH. Programming the PWDN bit in the N register HIGH (CE = HIGH) will disable the N counter and de-bias the f<sub>IN</sub> input (to a high impedance state). The R counter functionality also becomes disabled. The reference oscillator block powers down when the power down bit is asserted. The  $\ensuremath{\mathsf{OSC}_{\mathsf{IN}}}$  pin reverts to a high impedance state when this condition exists. Power down forces the charge pump and phase comparator logic to a TRI-STATE condition. A power down counter reset function resets both N and R counters. Upon powering up the N counter resumes counting in "close" alignment with the R counter (the maximum error is one prescaler cycle). The MICROWIRE control register remains active and capable of loading and latching in data during all of the power down modes.

# 2.0 Programming Description

#### 2.1 MICROWIRE INTERFACE

The MICROWIRE interface is comprised of an 18-bit shift register, a R register and a N register. The shift register consists of a 17-bit DATA field and a 1-bit address (ADDR) field as shown below. When Latch Enable transitions HIGH, data stored in the shift register is loaded into either the R or N register depending on the ADDR bit as described in Table 2.1.1. The data is loaded MSB first. The DATA field assignment for the R and N registers are shown in Table 2.1.2 below.

#### 2.1.1 Address Bit Truth Table

When LE is transitioned high, data is transferred from the 18-bit shift register into either the 14-bit R register, or the 17-bit N register depending upon the state of the ADDR bit.

| ADDR | DATA Location |

|------|---------------|

| 0    | N register    |

| 1    | R register    |

#### 2.1.2 Register Content Truth Table

|            | MSE                      | MSB SHIFT REGISTER BIT LOCATION |    |                      |    |    |    |    |   |   |   |   |       |      |   | I | LSB |   |

|------------|--------------------------|---------------------------------|----|----------------------|----|----|----|----|---|---|---|---|-------|------|---|---|-----|---|

|            | 17                       | 16                              | 15 | 14                   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 6 5 4 |      | 3 | 2 | 1   | 0 |

| N Register | NB_CNTR NA_CNTR CTL_WORD |                                 |    |                      |    |    |    |    |   |   |   |   |       | VORD | 0 |   |     |   |

| R Register | Х                        | Х                               | L  | LD_OUT PD_POL CP_TRI |    |    |    |    |   |   |   |   | R_CN  | TR   |   |   |     | 1 |

#### 2.2 R REGISTER

If the Address Bit (ADDR) is 1, when LE is transitioned high data is transferred from the 18-bit shift register into the 14-bit R register. The R register contains a latch which sets the PLL 10-bit R counter divide ratio. The divide ratio is programmed using the bits R\_CNTR as shown in 2.2.1 10-Bit Programmable Reference Divider Ratio (R Counter). The ratio must be  $\geq$  2. The PD\_POL and CP\_TRI bits control the phase detector polarity and charge pump TRI-STATE respectively, as shown in 2.2.2 R[11], R[12] Truth Table. X denotes a don't care condition.

| First | First Bit SHIFT REGISTER BIT LOCATION Last Bit |    |        |    |                                  |    |    |   |   |   |   |   |   |   | st Bit |   |   |

|-------|------------------------------------------------|----|--------|----|----------------------------------|----|----|---|---|---|---|---|---|---|--------|---|---|

| 17    | 16                                             | 15 | 14     | 13 | 12                               | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2      | 1 | 0 |

| Х     | Х                                              |    | LD_OUT |    | D_OUT PD_POL CP_TRI R_CNTR [9:0] |    |    |   |   |   |   |   |   | 1 |        |   |   |

#### 2.2.1 10-Bit Programmable Reference Divider Ratio (R Counter)

|              | R_CNTR |   |   |   |   |   |   |   |   |   |  |  |  |  |  |

|--------------|--------|---|---|---|---|---|---|---|---|---|--|--|--|--|--|

| Divide Ratio | 9      | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

| 2            | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |  |  |  |  |  |

| 3            | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |  |  |  |  |  |

| •            | •      | • | • | • | • | • | • | • | • | • |  |  |  |  |  |

| 1,023        | 1      | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |  |  |

Note: Divide ratio: 2 to 1,023 (Divide ratios less than 2 are prohibited).

$\ensuremath{\mathsf{R\_CNTR}}\xspace - \ensuremath{\mathsf{These}}\xspace$  bits select the divide ratio of the programmable reference dividers.

#### 2.2.2 R[11], R[12] Truth Table

| Bit    | Location | Function                | 0                | 1         |

|--------|----------|-------------------------|------------------|-----------|

| CP_TRI | R[11]    | Charge Pump TRI-STATE   | Normal Operation | TRI-STATE |

| PD_POL | R[12]    | Phase Detector Polarity | Negative         | Positive  |

Note: Depending upon VCO characteristics, R[12] should be set accordingly. When VCO characteristics are positive, R[12] should be set HIGH. When VCO characteristics are negative, R[12] should be set LOW.

# 2.0 Programming Description (Continued)

#### 2.2.3 LD\_OUT Truth Table (R[13]-[15])

| LD Pin Output       | R[15] | R[14] | R[13] |

|---------------------|-------|-------|-------|

| Digital Lock Detect | 0     | 0     | 0     |

| Analog Lock Detect  | 0     | 0     | 1     |

| R Divider Output    | 0     | 1     | 0     |

| N Divider Output    | 0     | 1     | 1     |

| Test Mode           | 1     | 0     | 0     |

Note: Do not use Test mode in normal operation. Test mode is for factory testing purpose only. It allows direct testing of the digital lock detect by using the CLK and Data as the R and N counter outputs.

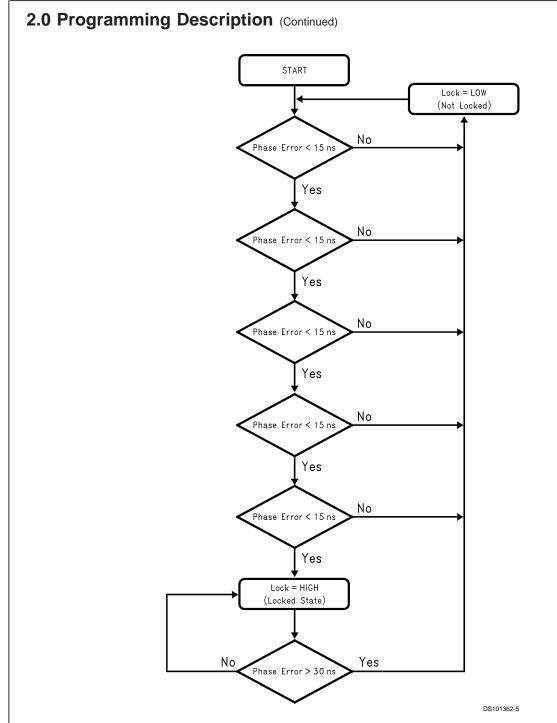

The Lock Detect Digital Filter compares the phase difference of the inputs from the phase detector to a RC generated delay of approximately 15 ns. To enter the locked state (LD = High), the phase error must be less than the 15 ns RC delay for 5 consecutive reference cycles. Once in lock, the RC delay is changed to approximately 30 ns. To exit the locked state, the phase error must be greater than the 30 ns RC delay. When the PLL is in power down mode, LD is forced to High state. A flow chart of the digital filter is shown as below:

#### 2.3 N REGISTER

If the address bit is LOW (ADDR = 0), when LE is transitioned high, data is transferred from the 18-bit shift register into the 17-bit N register. The N register consists of the 5-bit swallow counter (A counter), the 10-bit programmable counter (B counter) and the control word. Serial data format is shown below in *2.3.1 5-Bit Swallow Counter Divide Ratio (A Counter)* and *2.3.2 10-Bit Programmable Counter Divide Ratio (B Counter)*. The pulse swallow function which determines the divide ratio is described in section *2.3.3 Pulse Swallow Function*.

| First         | First Bit SHIFT REGISTER BIT LOCATION |    |    |    |    |    |    |   |   |                     |   |   |   |   |   | Last      | t Bit |

|---------------|---------------------------------------|----|----|----|----|----|----|---|---|---------------------|---|---|---|---|---|-----------|-------|

| 17            | 16                                    | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7                   | 6 | 5 | 2 | 1 | 0 |           |       |

| NB_CNTR [9:0] |                                       |    |    |    |    |    |    |   |   | NA_CNTR [4:0] CTL_W |   |   |   |   |   | DRD [1:0] | 0     |

|               |                                       |    |    |    |    |    |    |   |   |                     |   |   |   |   |   |           |       |

|               |                                       |    |    |    |    |    |    |   |   |                     |   |   |   |   |   |           |       |

## 2.0 Programming Description (Continued)

#### 2.3.1 5-Bit Swallow Counter Divide Ratio (A Counter)

| Swallow Count | NA_CNTR |   |   |   |   |

|---------------|---------|---|---|---|---|

| (A)           | 4       | 3 | 2 | 1 | 0 |

| 0             | 0       | 0 | 0 | 0 | 0 |

| 1             | 0       | 0 | 0 | 0 | 1 |

| •             | •       | • | • | ٠ | • |

| 31            | 1       | 1 | 1 | 1 | 1 |

**Notes:** Swallow Counter Value: 0 to 31 NB\_CNTR  $\geq$  NA\_CNTR

#### 2.3.2 10-Bit Programmable Counter Divide Ratio (B Counter)

| NB_CNTR      |   |   |   |   |   |   |   |   |   |   |

|--------------|---|---|---|---|---|---|---|---|---|---|

| Divide Ratio | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 3            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| ٠            | • | ٠ | • | • | • | • | • | • | • | ٠ |

| 1023         | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Notes: Divide ratio: 3 to 1,023 (Divide ratios less than 3 are prohibited). NB\_CNTR  $\geq$  NA\_CNTR

#### 2.3.3 Pulse Swallow Function

The N divider counts such that it divides the VCO RF frequency by (P+1) A times, and then divides by P (B - A) times. The B value (NB\_CNTR) must be  $\geq$  3. The continuous divider ratio is from 992 to 32,767. Divider ratios less than 992 are achievable as long as the binary counter value is greater than the swallow counter value (NB\_CNTR  $\geq$  NA\_CNTR).

$f_{VCO} = N \times (f_{OSC}/R)$

$\mathsf{N}=(\mathsf{P} \times \mathsf{B})+\mathsf{A}$

f<sub>VCO</sub>: Output frequency of external voltage controlled oscillator (VCO)

f<sub>OSC</sub>: Output frequency of the external reference frequency oscillator

- R: Preset divide ratio of binary 10-bit programmable reference counter (2 to 1023)

- N: Preset divide ratio of main 15-bit programmable integer N counter (992 to 32,767)

- B: Preset divide ratio of binary 10-bit programmable B counter (3 to 1023)

- A: Preset value of binary 5-bit swallow A counter ( $0 \le A \le 31, A \le B$ )

- P: Preset modulus of dual modulus prescaler (P = 32)

#### 2.3.4 CTL\_WORD

| MSB     | LSB  |

|---------|------|

| N2      | N1   |

| CNT_RST | PWDN |

#### 2.3.4.1 Reserve Word Truth Table

| CE | CNT DET | PWDN | Function               |

|----|---------|------|------------------------|

| CE | CNT_RST | FWDN | Function               |

| 1  | 0       | 0    | Normal Operation       |

| 1  | 0       | 1    | Synchronous Powerdown  |

| 1  | 1       | 0    | Counter Reset          |

| 1  | 1       | 1    | Asynchronous Powerdown |

| 0  | X       | Х    | Asynchronous Powerdown |

Notes: X denotes don't care.

1. The **Counter Reset** bit when activated allows the reset of both N and R counters. Upon powering up the N counter resumes counting in "close" alignment with the R counter. (The maximum error is one prescaler cycle).

# 2.0 Programming Description (Continued)

Both synchronous and asynchronous power down modes are available with the LMX2323 to be able to adapt to different types of applications. The MICROWIRE control register remains active and capable of loading and latching in data during all of the powerdown modes.

#### Synchronous Power down Mode

The PLL loops can be synchronously powered down by setting the counter reset mode bit to LOW (N[2] = 0) and its power down mode bit to HIGH (N[1] = 1). The power down function is gated by the charge pump. Once the power down mode and counter reset mode bits are loaded, the part will go into power down mode upon the completion of a charge pump pulse event.

#### Asynchronous Power down Mode

The PLL loops can be asynchronously powered down by setting the counter reset mode bit to HIGH (N[2] = 1) and its power down mode bit to HIGH (N[1] = 1). The power down function is NOT gated by the charge pump. Once the power down and counter reset mode bits are loaded, the part will go into power down mode immediately.

The R and N counters are disabled and held at load point during the synchronous and asynchronous power down modes. This will allow a smooth acquisition of the RF signal when the PLL is programmed to power up. Upon powering up, both R and N counters will start at the 'zero' state, and the relationship between R and N will not be random.

# Serial Data Input Timing

Notes: Parenthesis data indicates programmable reference divider data.

Data shifted into register on clock rising edge.

Data is shifted in MSB first.

Test Conditions: The Serial Data Input Timing is tested using a symmetrical waveform around  $V_{CC}/2$ . The test waveform has an edge rate of 0.6 V/ns with amplitudes of 2.2V @  $V_{CC}$  = 2.7V and 2.6V @  $V_{CC}$  = 5.5V.

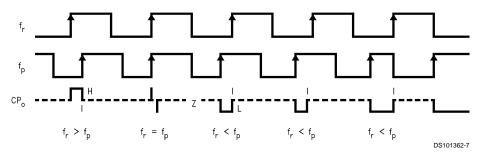

# Phase Comparator and Internal Charge Pump Characteristics

**Notes:** Phase difference detection range:  $-2\pi$  to  $+2\pi$

The minimum width pump up and pump down current pulses occur at the CPo pin when the loop is locked. PD\_POL = 1

f<sub>r</sub>: Phase comparator input from the R divider

fp: Phase comparator input from the N divider

CPo: Charge pump output

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | a O a Al a a m                |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated