LMX2335L, LMX2336L

SNAS112D - JUNE 1999-REVISED MARCH 2013

www.ti.com

# LMX2335L 1.1 GHz/1.1 GHz LMX2336L 2.0 GHz/1.1GHz

# PLLatinum™ Low Power Dual Frequency Synthesizer for RF Personal Communications

Check for Samples: LMX2335L, LMX2336L

#### **FEATURES**

- Ultra Low Current Consumption

- 2.7V to 5.5V Operation

- Selectable Synchronous and Asynchronous Powerdown Mode:

- $I_{CC} = 1 \mu A (Typ)$

- Dual Modulus Prescaler: 64/65 or 128/129

- Selectable Charge Pump TRI-STATE Mode

- Selectable Charge Pump Current Levels

- Selectable Fastlock Mode

- Upgrade and Compatible to LMX2335/36

- Small-Outline, Plastic, Surface Mount TSSOP Package

- LMX2336 Available in LGA Package

#### **APPLICATIONS**

- Cellular Telephone Systems (AMPS, ETACS, RCR-27)

- Cordless Telephone Systems

- (DECT, ISM, PHS, CT-1+)

- Personal Communication Systems

- (DCS-1800, PCN-1900)

- Dual Mode PCS Phones

- Cable TV Tuners (CATV)

- Other Wireless Communication Systems

#### DESCRIPTION

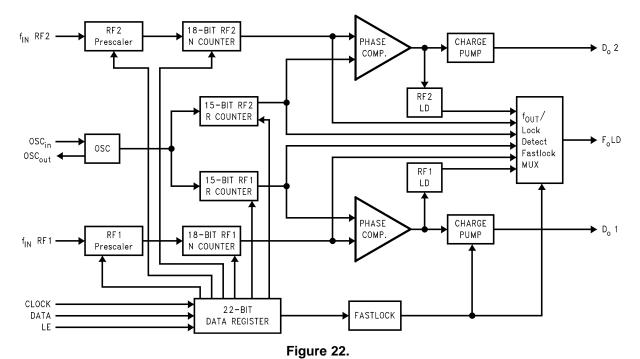

The LMX2335L and LMX2336L are monolithic, integrated dual frequency synthesizers, including two high frequency prescalers, and are designed for applications requiring two RF phase-lock loops. They are fabricated using TI's 0.5µ ABiC V silicon BiCMOS process.

The LMX2335L/36L contains two dual modulus prescalers. A 64/65 or a 128/129 prescaler can be selected for each RF synthesizer. A second reference divider chain is included in the IC for improved system noise. The LMX2335L/36L combined with a high quality reference oscillator, two loop filters, and two external voltage controlled oscillators generates very stable low noise RF local oscillator signals.

Serial data is transferred into the LMX2335L/36L via a three wire interface (Data, Enable, Clock). Supply voltage can range from 2.7V to 5.5V. The LMX2335L/36L feature very low current consumption; LMX2335L 4.0 mA at 5V, LMX2336L 5.5 mA at 5V. The LMX2335L is available in SO, TSSOP and LGA 16-pin surface mount plastic packages. The LMX2336L is available in a TSSOP 20-pin and LGA 24-pin surface mount plastic package.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PLLatinum is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

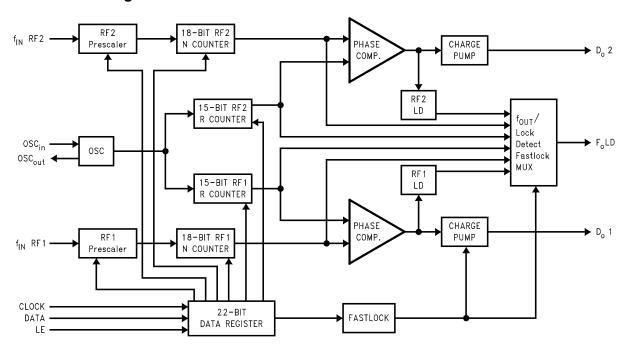

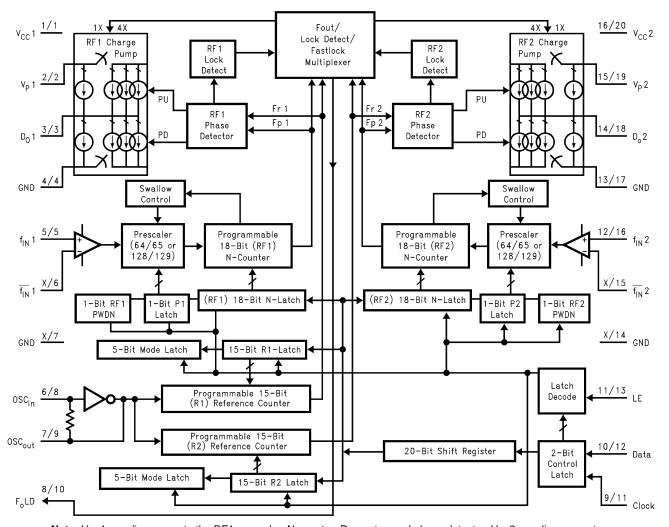

### **Functional Block Diagram**

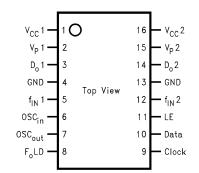

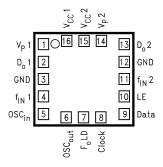

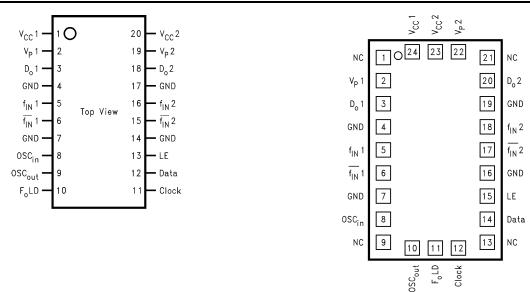

## **Connection Diagram**

Figure 1. LMX2335L (Top View) See Package Number D0016A and PW0016A

Figure 2. LMX2335L (Top View) See Package Number NPG0016A

www.ti.com

SNAS112D - JUNE 1999-REVISED MARCH 2013

Figure 3. LMX2336L (Top View) See Package Number PW0020A

Figure 4. LMX2336L (Top View) See Package Number NPH0024A

#### **PIN DESCRIPTIONS**

| Pin No. | Pin No.  | Pin No. | Pin No.  | Pin                | I/O | Description                                                                                                                                                                                                                                                |

|---------|----------|---------|----------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2336LPW | 2336LNPH | 2335LPW | 2335LNPG | Name               |     | Description                                                                                                                                                                                                                                                |

| 1       | 24       | 1       | 16       | V <sub>CC</sub> 1  |     | Power supply voltage input for RF1 analog and RF1 digital circuits. Input may range from 2.7V to 5.5V. $V_{CC}1$ must equal $V_{CC}2$ . Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane. |

| 2       | 2        | 2       | 1        | V <sub>p</sub> 1   |     | Power supply for RF1 charge pump. Must be ≥ V <sub>CC</sub> .                                                                                                                                                                                              |

| 3       | 3        | 3       | 2        | D <sub>o</sub> 1   | 0   | RF1 charge pump output. For connection to a loop filter for driving the input of an external VCO.                                                                                                                                                          |

| 4       | 4        | 4       | 3        | GND                |     | LMX2335L: Ground for RF1 analog and RF1 digital circuits.<br>LMX2336L: Ground for RF digital circuits.                                                                                                                                                     |

| 5       | 5        | 5       | 4        | f <sub>IN</sub> 1  | I   | RF1 prescaler input. Small signal input from the VCO.                                                                                                                                                                                                      |

| 6       | 6        | X       | Х        | /f <sub>IN</sub> 1 | I   | RF1 prescaler complementary input. A bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane. Capacitor is optional with loss of some sensitivity.                                                |

| 7       | 7        | Х       | Х        | GND                |     | Ground for RF1 analog circuitry.                                                                                                                                                                                                                           |

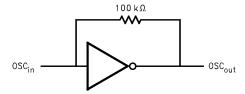

| 8       | 8        | 6       | 5        | OSC <sub>in</sub>  | I   | Oscillator input. The input has a $V_{\rm CC}/2$ input threshold and can be driven from an external CMOS or TTL logic gate.                                                                                                                                |

| 9       | 10       | 7       | 6        | OSC <sub>out</sub> | 0   | Oscillator output.                                                                                                                                                                                                                                         |

| 10      | 11       | 8       | 7        | F <sub>o</sub> LD  | 0   | Multiplexed output of the programmable or reference dividers, lock detect signals and Fastlock mode. CMOS output (see <i>Table 1</i> ).                                                                                                                    |

| 11      | 12       | 9       | 8        | Clock              | I   | High impedance CMOS Clock input. Data for the various latches is clocked in on the rising edge, into the 20-bit shift register.                                                                                                                            |

| 12      | 14       | 10      | 9        | Data               | I   | Binary serial data input. Data entered MSB first. The last two bits are the control bits. High impedance CMOS input.                                                                                                                                       |

| 13      | 15       | 11      | 10       | LE                 | I   | Load enable high impedance CMOS input. When LE goes HIGH, data stored in the shift registers is loaded into one of the 4 appropriate latches (control bit dependent).                                                                                      |

| 14      | 16       | Х       | Х        | GND                |     | Ground for RF2 analog circuitry.                                                                                                                                                                                                                           |

| 15      | 17       | Х       | Х        | /f <sub>IN</sub> 2 | I   | RF2 prescaler complementary input. A bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane. Capacitor is optional with loss of some sensitivity.                                                |

| 16      | 18       | 12      | 11       | f <sub>IN</sub> 2  | 1   | RF2 prescaler input. Small signal input from the VCO.                                                                                                                                                                                                      |

Copyright © 1999–2013, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

SNAS112D - JUNE 1999-REVISED MARCH 2013

www.ti.com

# PIN DESCRIPTIONS (continued)

| Pin No. | Pin No.      | Pin No. | Pin No.  | Pin               | I/O | Description                                                                                                                                                                                                                                                                                                              |  |  |

|---------|--------------|---------|----------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2336LPW | 2336LNPH     | 2335LPW | 2335LNPG | Name              |     | Description                                                                                                                                                                                                                                                                                                              |  |  |

| 17      | 19           | 13      | 12       | GND               |     | LMX2335L: Ground for RF2 analog, RF2 digital, MICROWIRE, F <sub>o</sub> LD and Oscillator circuits. LMX2336L: Ground for IF digital, MICROWIRE, F <sub>o</sub> LD and oscillator circuits.                                                                                                                               |  |  |

| 18      | 20           | 14      | 13       | D <sub>0</sub> 2  | 0   | RF2 charge pump output. For connection to a loop filter for driving the input of an external VCO.                                                                                                                                                                                                                        |  |  |

| 19      | 22           | 15      | 14       | V <sub>p</sub> 2  |     | Power supply for RF2 charge pump. Must be ≥ V <sub>CC</sub> .                                                                                                                                                                                                                                                            |  |  |

| 20      | 23           | 16      | 15       | V <sub>CC</sub> 2 |     | Power supply voltage input for RF2 analog, RF2 digital, MICROWIRE, $F_{\text{o}}\text{LD}$ and oscillator circuits. Input may range from 2.7V to 5.5V. $V_{\text{CC}}2$ must equal $V_{\text{CC}}1$ . Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane. |  |  |

| Х       | 1, 9, 13, 21 | Х       | Х        | NC                |     | No connect.                                                                                                                                                                                                                                                                                                              |  |  |

Submit Documentation Feedback

Copyright © 1999–2013, Texas Instruments Incorporated

### **Block Diagram**

**INSTRUMENTS**

**Note:**  $V_{CC}1$  supplies power to the RF1 prescaler, N-counter, R-counter, and phase detector.  $V_{CC}2$  supplies power to the RF2 prescaler, N-counter, phase detector, R-counter along with the OSC<sub>in</sub> buffer, MICROWIRE, and F<sub>o</sub>LD.  $V_{CC}1$  and  $V_{CC}2$  are clamped to each other by diodes and must be run at the same voltage level.

**Note:**  $V_P1$  and  $V_P2$  can be run separately as long as  $V_P \ge V_{CC}$ .

Note: Pin #  $\rightarrow$  8/10  $\leftarrow$  LMX2336L Pin #

Pin Name  $\rightarrow$  F<sub>o</sub>LD

X signifies a function not bonded out to a pin

Figure 5. LMX2335L

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings (1)(2)(3)

| Power Supply Voltage                               |                                |

|----------------------------------------------------|--------------------------------|

| V <sub>CC</sub>                                    | -0.3V to +6.5V                 |

| V <sub>P</sub>                                     | -0.3V to +6.5V                 |

| Voltage on Any Pin with GND = 0V (V <sub>I</sub> ) | -0.3V to V <sub>CC</sub> +0.3V |

| Storage Temperature Range (T <sub>S</sub> )        | -65°C to +150°C                |

| Lead Temperature (solder 4 sec.) (T <sub>L</sub> ) | +260°C                         |

- (1) This device is a high performance RF integrated circuit with an ESD rating <2 keV and is ESD sensitive. Handling and assembly of this device should only be done at ESD protected work stations.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

## **Recommended Operating Conditions**

| Power Supply Voltage                    |                          |

|-----------------------------------------|--------------------------|

| V <sub>CC</sub>                         | 2.7V to 5.5V             |

| V <sub>P</sub>                          | V <sub>CC</sub> to +5.5V |

| Operating Temperature (T <sub>A</sub> ) | −40°C to +85°C           |

#### **Electrical Characteristics**

$V_{CC} = 5.0V$ ,  $V_P = 5.0V$ ;  $T_A = 25$ °C, except as specified

|                      | _                       |                         |                                           |                     | 11  |                     |          |

|----------------------|-------------------------|-------------------------|-------------------------------------------|---------------------|-----|---------------------|----------|

| Symbol               | Par                     | ameter                  | Conditions                                | Min                 | Тур | Max                 | Units    |

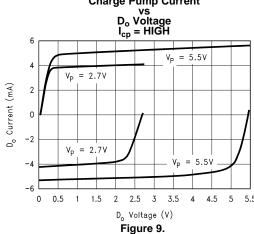

| I <sub>CC</sub>      | Power Supply Current    | LMX2335L RF1 and RF2    | V <sub>CC</sub> = 2.7V to 5.5V            |                     | 4.0 | 5.2                 | mA       |

| I <sub>CC</sub>      |                         | LMX2335L RF1 only       |                                           |                     | 2.0 | 2.6                 | mA       |

| Icc                  |                         | LMX2336L RF1 and<br>RF2 |                                           |                     | 5.5 | 7                   | mA       |

|                      |                         | LMX2336L RF1 only       |                                           |                     | 3.3 | 4.3                 | mA       |

| f <sub>IN</sub> 1    | Operating               | LMX2335L                |                                           | 0.100               |     | 1.1                 | GHz      |

| f <sub>IN</sub> 2    | Frequency               |                         |                                           | 0.050               |     | 1.1                 | GHz      |

| f <sub>IN</sub> 1    |                         | LMX2336L                |                                           | 0.200               |     | 2.0                 | GHz      |

| f <sub>IN</sub> 2    |                         |                         |                                           | 0.050               |     | 1.1                 | GHz      |

| I <sub>CC-PWDN</sub> | Powerdown Current       | LMX2335L/2336L          | $V_{CC} = 5.5V$                           |                     | 1   | 10                  | μΑ       |

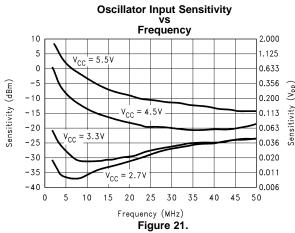

| fosc                 | Oscillator Frequency    |                         | With resonator load on OSC <sub>out</sub> | 5                   |     | 20                  | MHz      |

| fosc                 |                         |                         | No load on OSC <sub>out</sub>             | 5                   |     | 40                  | MHz      |

| $f_{\phi}$           | Maximum Phase Dete      | ctor Frequency          |                                           |                     | 10  |                     | MHz      |

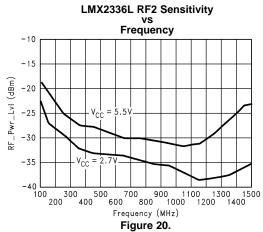

| Pf <sub>IN</sub>     | RF Input Sensitivity    |                         | $V_{CC} = 3.0V, f > 100 \text{ MHz}$      | -15                 |     | 0                   | dBm      |

| Pf <sub>IN</sub>     |                         |                         | $V_{CC} = 5.0V, f > 100 MHz$              | -10                 |     | 0                   |          |

| Vosc                 | Oscillator Sensitivity  |                         | OSC <sub>in</sub>                         | 0.5                 |     |                     | $V_{PP}$ |

| V <sub>IH</sub>      | High-Level Input Volta  | ige                     | (1)                                       | 0.8 V <sub>CC</sub> |     |                     | V        |

| V <sub>IL</sub>      | Low-Level Input Volta   | ge                      | (1)                                       |                     |     | 0.2 V <sub>CC</sub> | V        |

| I <sub>IH</sub>      | High-Level Input Curre  | ent                     | $V_{IH} = V_{CC} = 5.5V^{(1)}$            | -1.0                |     | 1.0                 | μΑ       |

| I <sub>IL</sub>      | Low-Level Input Curre   | ent                     | $V_{IL} = 0V, V_{CC} = 5.5V^{(1)}$        | -1.0                |     | 1.0                 | μΑ       |

| I <sub>IH</sub>      | Oscillator Input Currer | nt                      | $V_{IH} = V_{CC} = 5.5V$                  |                     |     | 100                 | μΑ       |

| I <sub>IL</sub>      | Oscillator Input Currer | nt                      | $V_{IL} = 0V, V_{CC} = 5.5V$              | -100                |     |                     | μΑ       |

(1) Clock, Data and LE does not include f<sub>IN</sub>1, f<sub>IN</sub>2 and OSC<sub>in</sub>.

www.ti.com

SNAS112D - JUNE 1999-REVISED MARCH 2013

# **Electrical Characteristics (continued)**

$V_{CC} = 5.0V$ ,  $V_P = 5.0V$ ;  $T_A = 25$ °C, except as specified

| Cumbal                                            | Parameter                           | Conditions                                              |                       | Value |     |       |  |

|---------------------------------------------------|-------------------------------------|---------------------------------------------------------|-----------------------|-------|-----|-------|--|

| Symbol                                            | Parameter                           | Conditions                                              | Min                   | Тур   | Max | Units |  |

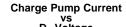

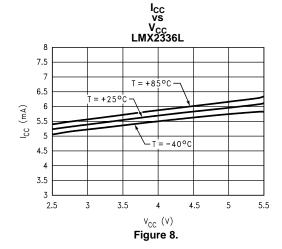

| I <sub>Do-SOURCE</sub>                            | Charge Pump Output Current          | $V_{Do} = V_P/2, I_{CPo} = LOW^{(2)}$                   |                       | -1.25 |     | mA    |  |

| I <sub>Do-SINK</sub>                              |                                     | $V_{Do} = V_P/2, I_{CPo} = LOW$                         |                       | 1.25  |     | mA    |  |

| I <sub>Do-SOURCE</sub>                            |                                     | $V_{Do} = V_P/2, I_{CPo} = HIGH^{(2)}$                  |                       | -5.00 |     | mA    |  |

| I <sub>Do-SINK</sub>                              |                                     | $V_{Do} = V_P/2, I_{CPo} = HIGH^{(2)}$                  |                       | 5.00  |     | mA    |  |

| I <sub>Do-TRI</sub>                               | Charge Pump                         | $0.5V \le V_{Do} \le V_{CC} - 0.5V$                     | -5.0                  |       | 5.0 | nA    |  |

|                                                   | TRI-STATE Current                   | T <sub>A</sub> = 25°C                                   |                       |       |     |       |  |

| I <sub>Do-SINK</sub> vs<br>I <sub>Do-SOURCE</sub> | Charge Pump Sink vs Source Mismatch | $V_{Do} = V_{P}/2$<br>$T_{A} = 25^{\circ}C^{(3)}$       |                       | 3     |     | %     |  |

| I <sub>Do</sub> vs V <sub>Do</sub>                | Charge Pump Current Vs Voltage      | $0.5 \le V_{DO} \le V_{p} - 0.5V$ $T_{A} = 25^{\circ}C$ |                       | 10    |     | %     |  |

| I <sub>Do</sub> vs T <sub>A</sub>                 | Charge Pump Current vs Temperature  | $V_{Do} = V_P/2$<br>-40°C≤ $T_A \le 85$ °C (3)          |                       | 10    |     | %     |  |

| $V_{OH}$                                          | High-Level Output Voltage           | I <sub>OH</sub> = -500 μA                               | V <sub>CC</sub> - 0.4 |       |     | V     |  |

| $V_{OL}$                                          | Low-Level Output Voltage            | $I_{OL} = 500 \ \mu A$                                  |                       |       | 0.4 | V     |  |

| t <sub>CS</sub>                                   | Data to Clock Set Up Time           | See SERIAL DATA INPUT TIMING                            | 50                    |       |     | ns    |  |

| t <sub>CH</sub>                                   | Data to Clock Hold Time             | See SERIAL DATA INPUT<br>TIMING                         | 10                    |       |     | ns    |  |

| t <sub>CWH</sub>                                  | Clock Pulse Width High              | See SERIAL DATA INPUT<br>TIMING                         | 50                    |       |     | ns    |  |

| t <sub>CWL</sub>                                  | Clock Pulse Width Low               | See SERIAL DATA INPUT<br>TIMING                         | 50                    |       |     | ns    |  |

| t <sub>ES</sub>                                   | Clock to Load Enable Set Up Time    | See SERIAL DATA INPUT<br>TIMING                         | 50                    |       |     | ns    |  |

| t <sub>EW</sub>                                   | Load Enable Pulse Width             | See SERIAL DATA INPUT                                   | 50                    |       |     | ns    |  |

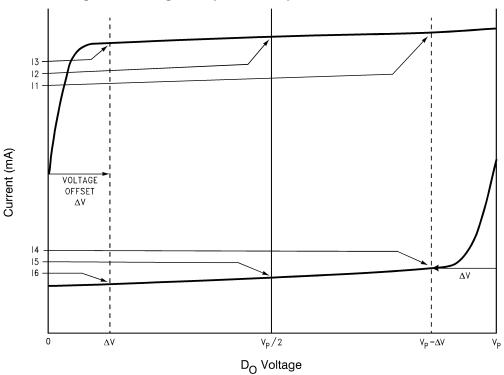

See Table 1 for  $I_{CPo}$  description. See Figure 6

Figure 6. Charge Pump Current Specification Definitions

I1 = CP sink current at  $V_{Do} = V_P - \Delta V$

I2 = CP sink current at  $V_{D0} = V_P/2$

I3 = CP sink current at  $V_{Do} = \Delta V$

I4 = CP source current at  $V_{Do} = V_P - \Delta V$

I5 = CP source current at  $V_{Do} = V_P/2$

I6 = CP source current at  $V_{Do} = \Delta V$

V = Voltage offset from positive and negative rails. Dependent on VCO tuning range relative to V<sub>CC</sub> and ground. Typical values are between 0.5V and 1.0V.

- 1. I<sub>Do</sub> vs V<sub>Do</sub> = Charge Pump Output Current magnitude variation vs Voltage =  $[\frac{1}{2} * {||1| - ||3|}]/[\frac{1}{2} * {||1| + ||3|}] * 100\%$  and  $[\frac{1}{2} * {||4| - ||6|}]/[\frac{1}{2} * {||4| + ||6|}] * 100\%$

- 2. I<sub>Do-sink</sub> vs I<sub>Do-source</sub> = Charge Pump Output Current Sink vs Source Mismatch =

- $[||2| ||5|]/[½ * {||2| + ||5|}] * 100\%$ 3.  $I_{Do}$  vs  $T_A$  = Charge Pump Output Current magnitude variation vs Temperature = [||2 @ temp| ||2 @ 25°C|]/||2 @ 25°C| \* 100% and [||5 @ temp| ||5 @ 25°C|]/||5 @ 25°C| \* 100%

Instruments

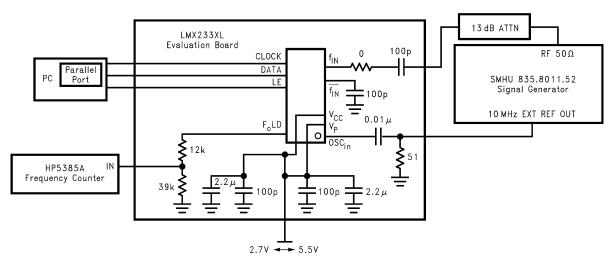

# **RF Sensitivity Test Block Diagram**

N = 10,000R = 50P = 64

Sensitivity limit is reached when the error of the divided RF output,  $F_0LD$ , is  $\geq 1$  Hz.

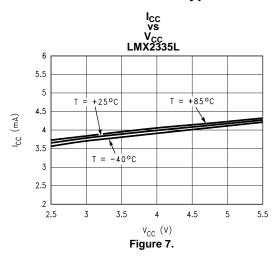

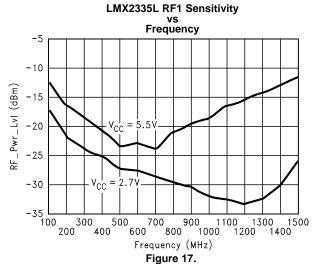

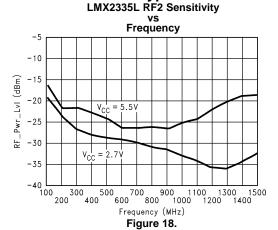

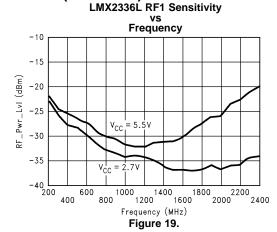

# **Typical Performance Characteristics**

### **Typical Performance Characteristics (continued)**

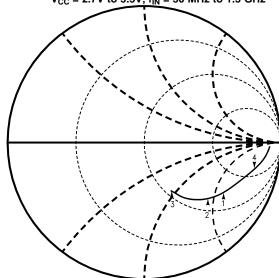

LMX2335L Input Impedance (for TSSOP package)  $V_{CC} = 2.7V$  to 5.5V,  $f_{\rm IN} = 50$  MHz to 1.5 GHz

Marker 1 = 1 GHz, Real = 94, Imaginary = -118 Marker 2 = 1.2 GHz, Real = 72, Imaginary = -88

Marker 3 = 1.5 GHz, Real = 53, Imaginary = -45

Marker 4 = 500 MHz, Real = 201, Imaginary = -224 Figure 11.

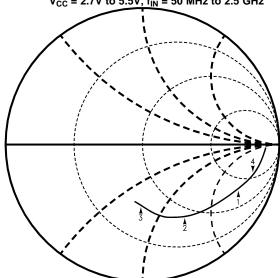

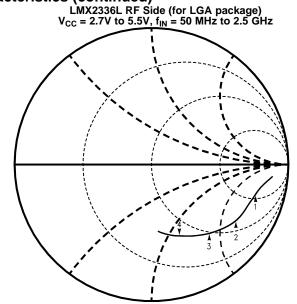

LMX2336L Input Impedance (for TSSOP package)  $V_{CC}$  = 2.7V to 5.5V,  $f_{IN}$  = 50 MHz to 2.5 GHz

Marker 1 = 1 GHz, Real = 97, Imaginary = −146

Marker 2 = 1.89 GHz, Real = 43, Imaginary = -67

Marker 3 = 2.5 GHz, Real = 30, Imaginary = -33

Marker 4 = 500 MHz, Real = 189, Imaginary = -233 Figure 12.

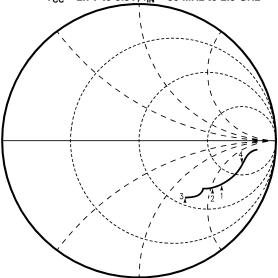

# LMX2335L Input Impedance (for TSSOP package) $V_{CC}$ = 2.7V to 5.5V, $f_{IN}$ = 50 MHz to 2.5 GHz

Marker 1 = 1 GHz, Real = 111, Imaginary = -129

Marker 2 = 1.2 GHz, Real = 87, Imaginary = -102

Marker 3 = 1.5 GHz, Real = 61, Imaginary = -70

Marker 4 = 500 MHz, Real = 232, Imaginary = -203

Figure 13.

NSTRUMENTS

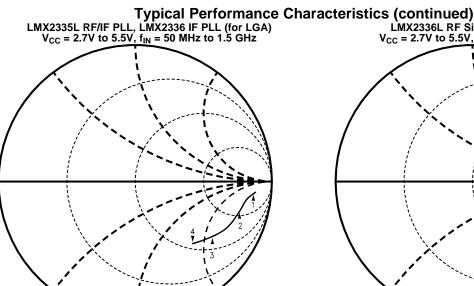

Marker 1 = 100 MHz, 446 -j279 ohm Marker 2 = 500 MHz, 178 -j210 ohm Marker 3 = 1500 MHz, 84 -j132 ohm Marker 4 = 2000 MHz, 54 −j84 ohm Figure 14.

Marker 1 = 0.5 GHz, 169 −j206 ohm Marker 2 = 1.0 GHz, 78 -j133 ohm Marker 3 = 1.5 GHz, 50 - j88 ohm Marker 4 = 2.0. GHz, 38 −j60 ohm Figure 15.

# Typical Performance Characteristics (continued) L RF2 Sensitivity LMX2336L RF1 Sensitivity

#### **FUNCTIONAL DESCRIPTION**

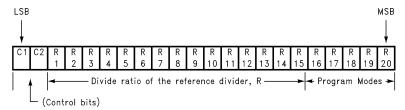

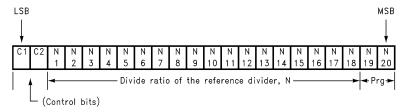

Figure 22 below shows the 22-bit data register, two 15-bit R Counters and two 18-bit N Counters (intermediate latches are not shown). The data stream is clocked (on the rising edge of Clock) into the DATA register, MSB first. The data stored in the shift register is loaded into one of the 4 appropriate latches on the rising edge of LE. The last two bits are the Control Bits. The DATA is transferred into the counters as follows:

| Contr | ol Bits | DATA Location |  |  |  |

|-------|---------|---------------|--|--|--|

| C1    | C2      |               |  |  |  |

| 0     | 0       | RF2 R Counter |  |  |  |

| 0     | 1       | RF1 R Counter |  |  |  |

| 1     | 0       | RF2 N Counter |  |  |  |

| 1     | 1       | RF1 N Counter |  |  |  |

# PROGRAMMABLE REFERENCE DIVIDERS (RF1 AND RF2 R COUNTERS)

If the Control Bits are 00 or 01 (00 for RF2 and 01 for RF1) data is transferred from the 22-bit shift register into a latch which sets the 15-bit R Counter. Serial data format is shown below.

www.ti.com

# 15-BIT PROGRAMMABLE REFERENCE DIVIDER RATIO (R COUNTER)(1)

| Divide | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R | R |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| Ratio  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 3      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| •      | •  | •  | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • |

| 32767  | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### (1) Notes:

Divide ratios less than 3 are prohibited.

Divide ratio: 3 to 32767

R1 to R15: These bits select the divide ratio of the programmable reference divider.

Data is shifted in MSB first.

## PROGRAMMABLE DIVIDER (N COUNTER)

Each N counter consists of the 7-bit swallow counter (A counter) and the 11-bit programmable counter (B counter). If the Control Bits are 10 or 11 (10 for RF2 counter and 11 for RF1 counter) data is transferred from the 20-bit shift register into a 7-bit latch (which sets the Swallow (A) Counter) and an 11-bit latch (which sets the 11-bit programmable (B) Counter), MSB first. Serial data format is shown below.

# 7-BIT SWALLOW COUNTER DIVIDE RATIO (A COUNTER)(1)

| Divide<br>Ratio<br>A | N<br>7 | N<br>6 | N<br>5 | N<br>4 | N<br>3 | N<br>2 | N<br>1 |

|----------------------|--------|--------|--------|--------|--------|--------|--------|

| 0                    | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 1                    | 0      | 0      | 0      | 0      | 0      | 0      | 1      |

| •                    | •      | •      | •      | •      | •      | •      | •      |

| 127                  | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

#### (1) Notes:

Divide ratio: 0 to 127

B ≥ A

A < P

# 11-BIT PROGRAMMABLE COUNTER DIVIDE RATIO (B COUNTER)(1)

| Divide<br>Ratio<br>B | N<br>18 | N<br>17 | N<br>16 | N<br>15 | N<br>14 | N<br>13 | N<br>12 | N<br>11 | N<br>10 | N<br>9 | N<br>8 |

|----------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------|--------|

| 3                    | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1      | 1      |

| 4                    | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0      | 0      |

| •                    | •       | •       | •       | •       | •       | •       | •       | •       | •       | •      | •      |

| 2047                 | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1      | 1      |

#### (1) **Note**:

Divide ratio: 3 to 2047 (Divide ratios less than 3 are prohibited)

$B \ge A$

www.ti.com

SNAS112D - JUNE 1999-REVISED MARCH 2013

#### **PULSE SWALLOW FUNCTION**

$f_{VCO} = [(P \times B) + A] \times f_{OSC}/R$

**f**<sub>VCO</sub>: Output frequency of external voltage controlled oscillator (VCO)

**B:** Preset divide ratio of binary 11-bit programmable counter (3 to 2047)

A: Preset divide ratio of binary 7-bit swallow counter

$$(0 \le A \le P; A \le B)$$

fosc: Output frequency of the external reference frequency oscillator

R: Preset divide ratio of binary 15-bit programmable reference counter (3 to 32767)

P: Preset modulus of dual modulus prescaler (P = 64 or 128)

#### PROGRAMMABLE MODES

Several modes of operation can be programmed with bits R16–R20 including the phase detector polarity, charge pump tristate and the output of the  $F_oLD$  pin. The prescaler and power down modes are selected with bits N19 and N20. The programmable modes are shown in Table 1. Truth table for the programmable modes and  $F_oLD$  output are shown in Table 2 and Table 3.

**Table 1. Programmable Modes**

| C1 | C2 | R16                         | R17                  | R18                          | R19    | R20                |

|----|----|-----------------------------|----------------------|------------------------------|--------|--------------------|

| 0  | 0  | RF2 Phase Detector Polarity | RF2 I <sub>CPo</sub> | RF2 D <sub>o</sub> TRI-STATE | RF2 LD | RF2 F <sub>o</sub> |

| 0  | 1  | RF1 Phase Detector Polarity | RF1 I <sub>CPo</sub> | RF1 D <sub>o</sub> TRI-STATE | RF1 LD | RF1 F <sub>o</sub> |

| C1 | C2 | N19       | N20  |

|----|----|-----------|------|

| 1  | 0  | RF2       | Pwdn |

|    |    | Prescaler | RF2  |

| 1  | 1  | RF1       | Pwdn |

|    |    | Prescaler | RF1  |

**Table 2. Mode Select Truth Table**

|   | Phase Detector Polarity | D <sub>o</sub> TRI-STATE <sup>(2)</sup> | I <sub>CPo</sub> (3) | RF1 Prescaler | RF2 Prescaler | Pwdn <sup>(2)</sup> |

|---|-------------------------|-----------------------------------------|----------------------|---------------|---------------|---------------------|

| 0 | Negative                | Normal Operation                        | LOW                  | 64/65         | 64/65         | pwrd up             |

| 1 | Positive                | TRI-STATE                               | HIGH                 | 128/129       | 128/129       | pwrd dn             |

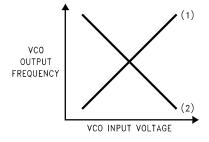

- (1) PHASE DETECTOR POLARITY, Depending upon VCO characteristics, R16 bit should be set accordingly: (see Figure 23) When VCO characteristics are positive like (1), R16 should be set HIGH; When VCO characteristics are negative like (2), R16 should be se LOW.

- (2) Refer to POWERDOWN OPERATION.

- (3) The  $I_{CPo}$  LOW current state =  $1/4 \times I_{CPo}$  HIGH current.

Figure 23. VCO Characteristics

Copyright © 1999–2013, Texas Instruments Incorporated

# Table 3. The F<sub>o</sub>LD Output Truth Table<sup>(1)</sup>

| RF1 R[19] | RF2 R[19] | RF1 R[20]             | RF2 R[20]             | F₀LD                            |

|-----------|-----------|-----------------------|-----------------------|---------------------------------|

| (RF1 LD)  | (RF2 LD)  | (RF1 F <sub>O</sub> ) | (RF2 F <sub>O</sub> ) | Output State                    |

| 0         | 0         | 0                     | 0                     | Disabled <sup>(2)</sup>         |

| 0         | 1         | 0                     | 0                     | RF2 Lock Detect (3)             |

| 1         | 0         | 0                     | 0                     | RF1 Lock Detect (3)             |

| 1         | 1         | 0                     | 0                     | RF1/RF2 Lock Detect (3)         |

| Х         | 0         | 0                     | 1                     | RF2 Reference Divider Output    |

| Х         | 0         | 1                     | 0                     | RF1 Reference Divider Output    |

| X         | 1         | 0                     | 1                     | RF2 Programmable Divider Output |

| Х         | 1         | 1                     | 0                     | RF1 Programmable Divider Output |

| 0         | 0         | 1                     | 1                     | Fastlock (4)                    |

| 0         | 1         | 1                     | 1                     | RF2 Counter Reset (5)           |

| 1         | 0         | 1                     | 1                     | RF1 Counter Reset (5)           |

| 1         | 1         | 1                     | 1                     | RF1 and RF2 Counter Reset (5)   |

- (1) X—don't care condition

- (2) When the F<sub>o</sub>LD output is disabled it is actively pulled to a low logic state.

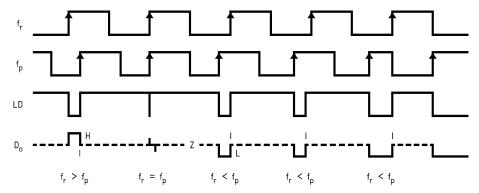

- (3) Lock detect output provided to indicate when the VCO frequency is in "lock". When the loop is locked and a lock detect mode is selected, the pins output is HIGH, with narrow pulses LOW. In the RF1/RF2 lock detect mode a locked condition is indicated when RF2 and RF1 are both locked.

- (4) The Fastlock mode utilized the F<sub>o</sub>LD output pin to switch a second loop filter damping resistor to ground during fastlock operation. Activation of Fastlock occurs whenever the RF loop's Icpo magnitude bit #17 is selected HIGH (while the #19 and #20 mode bits are set for Fastlock).

- (5) The RF2 counter reset mode resets RF2 PLL's R and N counters and brings RF2 charge pump output to a TRI-STATE condition. The RF1 counter reset mode resets RF1 PLL's R and N counters and brings RF1 charge pump output to a TRI-STATE condition. The RF1 and RF2 counter reset mode resets all counters and brings both charge pump output to a TRI-STATE condition. Upon removal of the Reset bits the N counter resumes counting in "close" alignment with the R counter. (The maximum error is one prescaler cycle).

#### **POWERDOWN OPERATION**

Synchronous and asynchronous powerdown modes are both available by microwire selection. Synchronously powerdown occurs if the respective loop's R18 bit (Do TRI-STATE) is LOW when its N20 bit (Pwdn) becomes HI. Asynchronous powerdown occurs if the loop's R18 bit is HI when its N20 bit becomes HI.

In the synchronous powerdown mode, the powerdown function is gated by the charge pump to prevent unwanted frequency jumps. Once the powerdown program bit N20 is loaded, the part will go into powerdown mode when the charge pump reaches a TRI-STATE condition.

In the asynchronous powerdown mode, the device powers down immediately after the LE pin latches in a HI condition on the powerdown bit N20.

Activation of either the IF or RF PLL powerdown conditions in either synchronous or asynchronous modes forces the respective loop's R & N dividers to their load state condition and debiasing of it's respective Fin input to a high impedance state. The oscillator circuitry function does not become disabled until both IF and RF powerdown bits are activated. The MICROWIRE control register remains active and capable of loading and latching data during all of the powerdown modes.

The device returns to an actively powered up condition in either synchronous ar asynchronous modes immediately upon LE latching LOW data into bit N20.

Table 4. Powerdown Mode Select Table

| R18 | N20 | Powerdown Status                          |  |  |

|-----|-----|-------------------------------------------|--|--|

| 0   | 0   | PLL Active                                |  |  |

| 1   | 0   | PLL Active (Charge Pump Output TRI-STATE) |  |  |

| 0   | 1   | Synchronous Powerdown Initiated           |  |  |

| 1   | 1   | Asynchronous Powerdown Initiated          |  |  |

www.ti.com

SNAS112D - JUNE 1999-REVISED MARCH 2013

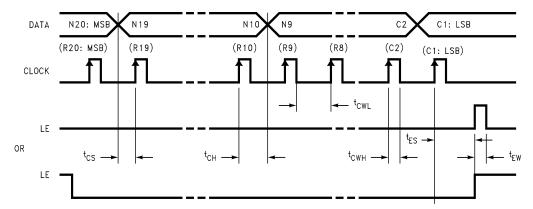

#### **SERIAL DATA INPUT TIMING**

Parenthesis data indicates programmable reference divider data.

Data shifted into register on clock rising edge.

Data is shifted in MSB first.

t<sub>CS</sub> = Data to Clock Set Up Time

t<sub>CH</sub> = Data to Clock Hold Time

t<sub>CWH</sub> = Clock Pulse Width High

t<sub>CWL</sub> = Clock Pulse Width Low

t<sub>ES</sub> = Clock to Load Enable Set Up Time

t<sub>EW</sub> = Load Enable Pulse Width

**Test Conditions:** The Serial Data Input Timing is tested using a symmetrical waveform around  $V_{CC}/2$ . The test waveform has an edge rate of 0.6V/ns with amplitudes of 2.2V @  $V_{CC}$  = 2.7V and 2.6V @  $V_{CC}$  = 5.5V.

#### PHASE COMPARATOR AND INTERNAL CHARGE PUMP CHARACTERISTICS

**Notes:** Phase difference detection range:  $-2\pi$  to  $+2\pi$

The minimum width pump up and pump down current pulses occur at the Do pin when the loop is locked.

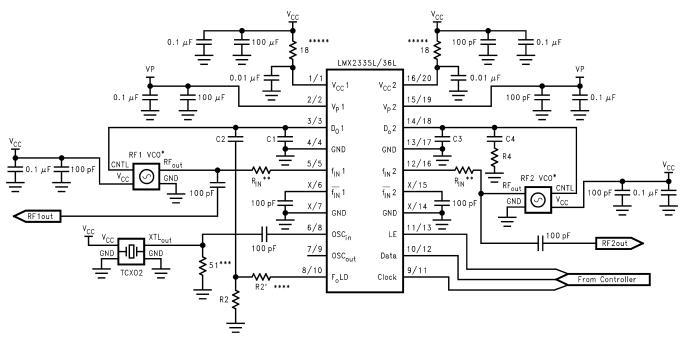

### **Typical Application Example**

#### **Operational Notes:**

- VCO is assumed AC coupled.

- \*\*  $R_{IN}$  increases impedance so that VCO output power is provided to the load rather than the PLL. Typical values are 10Ω to 200Ω depending on the VCO power level.  $f_{IN}$  RF impedance ranges from 40Ω to 100Ω.  $f_{IN}$  IF impedances are higher.

- \*\*\* 50Ω termination is often used on test boards to allow use of external reference oscillator. For most typical products a CMOS clock is used and no terminating resistor is required. OSC<sub>in</sub>may be AC or DC coupled. AC coupling is recommended because the input circuit provides its own bias. (See Figure 24).

- \*\*\*\* R2 configured F<sub>o</sub>LD for use in FastLock mode.

- \*\*\*\*\* Adding RC filters to the V<sub>CC</sub> lines is recommended to reduce loop-to-loop noise coupling.

#### **Application Hints:**

Proper use of grounds and bypass capacitors is essential to achieve a high level of performance. Crosstalk between pins can be reduced by careful board

layout.

This is an electrostatic sensitive device. It should be handled only at static free work stations.

Figure 24.

### **Application Information**

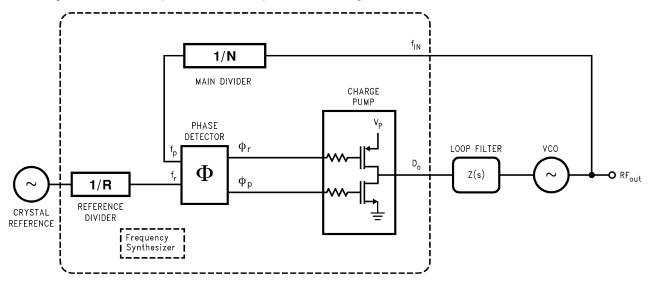

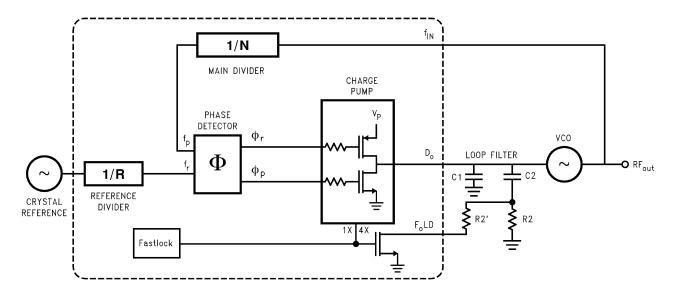

A block diagram of the basic phase locked loop is shown in Figure 25.

Figure 25. Conventional PLL Architecture

#### **LOOP GAIN EQUATIONS**

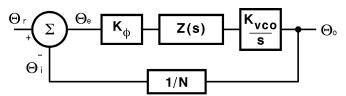

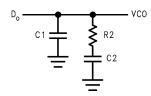

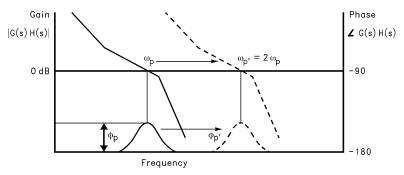

A linear control system model of the phase feedback for a PLL in the locked state is shown in Figure 26. The open loop gain is the product of the phase comparator gain  $(K_{\phi})$ , the VCO gain  $(K_{VCO}/s)$ , and the loop filter gain Z(s) divided by the gain of the feedback counter modulus (N). The passive loop filter configuration used is displayed in Figure 27, WHILE the complex impedance of the filter is given in equation 2.

Figure 26. PLL Linear Model

Figure 27. Passive Loop Filter

$$\begin{array}{ll} \begin{array}{lll} \text{Open} \\ \text{Loop} & = & \text{H(s)} \, \text{G(s)} \, = \frac{\Theta i}{\Theta e} = \frac{\text{K}_{\varphi} \text{Z(s)} \, \text{K}_{\text{VCO}}}{\text{Ns}} \end{array} \tag{1}$$

$$Z(s) = \frac{s(C2 \cdot R2) + 1}{S^2 (C1 \cdot C2 \cdot R2) + sC1 + sC2}$$

(2)

The time constants which determine the pole and zero frequencies of the filter transfer function can be defined as

$$T1 = R2 \cdot \frac{C1 \cdot C2}{C1 + C2}$$

$$T2 = R2 \cdot C2$$

(3)

Copyright © 1999–2013, Texas Instruments Incorporated

The 3rd order PLL Open Loop Gain can be calculated in terms of frequency,  $\omega$ , the filter time contants T1 and T2, and the design constants K $\phi$ , K<sub>VCO</sub>, and N.

$$G(s) \bullet H(s) \mid_{S = j \bullet w} = \frac{-K_{\Phi} \bullet K_{VCO}(1 + jw \bullet T2)}{w^2 C 1 \bullet N(1 + jw \bullet T1)} \bullet \frac{T1}{T2}$$

$$(4)$$

From Equation 3 we can see that the phase term will be dependent on the single pole and zero such that the phase margin is determined in Equation 1.

$$\varphi(\omega) = \tan^{-1}(\omega \cdot T2) - \tan^{-1}(\omega \cdot T1) + 180^{\circ}C$$

(5)

A plot of the magnitude and phase of G(s) H(s) for a stable loop, is shown in Equation 4 with a solid trace. The parameter  $\phi_p$  shows the amount of phase margin that exists at the point the gain drops below zero (the cutoff frequency wp of the loop). In a critically damped system, the amount of phase margin would be approximately 45 degrees.

If we were now to redefine the cut off frequency, wp', as double the frequency which gave us our original loop bandwidth, wp, the loop response time would be approximately halved. Because the filter attenuation at the comparison frequency also diminishes, the spurs would have increased by approximately 6 dB. In the proposed Fastlock scheme, the higher spur levels and wider loop filter conditions would exist only during the initial lock-on phase—just long enough to reap the benefits of locking faster. The objective would be to open up the loop bandwidth but not introduce any additional complications or compromises related to our original design criteria. We would ideally like to momentarily shift the curve Figure 28 over to a different cutoff frequency, illustrated by dotted line, without affecting the relative open loop gain and phase relationships. To maintain the same gain/phase relationship at twice the original cutoff frequency, other terms in the gain and phase equations 4 and 5 will have to compensate by the corresponding "1/w" or "1/w2" factor. Examination of equations 3 and 5 indicates the damping resistor variable R2 could be chosen to compensate with "w" terms for the phase margin. This implies that another resistor of equal value to R2 will need to be switched in parallel with R2 during the initial lock period. We must also insure that the magnitude of the open loop gain, H(s)G(s) is equal to zero at wp' = 2 wp.  $K_{VCO}$ ,  $K\phi$ , N, or the net product of these terms can be changed by a factor of 4, to counteract with  $w^2$  term present in the denominator of equation 3. The Kφ term was chosen to complete the transformation because it can readily be switched between 1X and 4X values. This is accomplished by increasing the charge pump output current from 1 mA in the standard mode to 4 mA in Fastlock.

#### **FASTLOCK CIRCUIT IMPLEMENTATION**

A diagram of the Fastlock scheme as implemented in Texas Instruments LMX2335L/36L PLL is shown in Figure 29. When a new frequency is loaded, and the RF1  $I_{CPo}$  bit is set high, the charge pump circuit receives an input to deliver 4 times the normal current per unit phase error while an open drain NMOS on chip device switches in a second R2 resistor element to ground. The user calculates the loop filter component values for the normal steady state considerations. The device configuration ensures that as long as a second identical damping resistor is wired in appropriately, the loop will lock faster without any additional stability considerations to account for. Once locked on the correct frequency, the user can return the PLL to standard low noise operation by sending a MICROWIRE instruction with the RF1  $I_{CPo}$  bit set low. This transition does not affect the charge on the loop filter capacitors and is enacted synchronous with the charge pump output. This creates a nearly seamless change between Fastlock and standard mode.

Figure 28. Open Loop Response Bode Plot

20

Figure 29. Fastlock PLL Architecture

# LMX2335L, LMX2336L

| SNAS112D - | JUNE | 1999- | REVISED | MARCH | 2013 |

|------------|------|-------|---------|-------|------|

www.ti.com

# **REVISION HISTORY**

| Changes from Revision C (March 2013) to Revision D |                                                    |  |            |

|----------------------------------------------------|----------------------------------------------------|--|------------|

| •                                                  | Changed layout of National Data Sheet to TI format |  | <b>2</b> 1 |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>