www.ti.com

SNAS187C - FEBRUARY 2003-REVISED MARCH 2013

# PLLatinum™ Dual High Frequency Synthesizer for RF Personal Communications LMX2430 3.0 GHz/0.8 GHz, LMX2433 3.6 GHz/1.7 GHz, LMX2434 5.0 GHz/2.5 GHz

Check for Samples: LMX2430, LMX2433, LMX2434

#### **FEATURES**

- Low Current Consumption

- 2.25V to 2.75V Operation

- Selectable Synchronous or Asynchronous Powerdown Mode

- Selectable Dual Modulus Prescaler:

LMX2430 RF: 8/9 or 16/17

LMX2433 RF: 8/9 or 16/17

LMX2434 RF: 16/17 or 32/33

LMX243x IF: 8/9 or 16/17

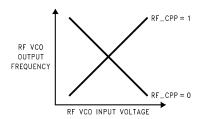

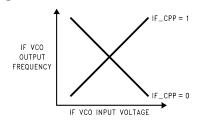

Programmable Charge Pump Current Levels

- RF and IF: 1 or 4 mA

- Fastlock Technology with Integrated Timeout Counters

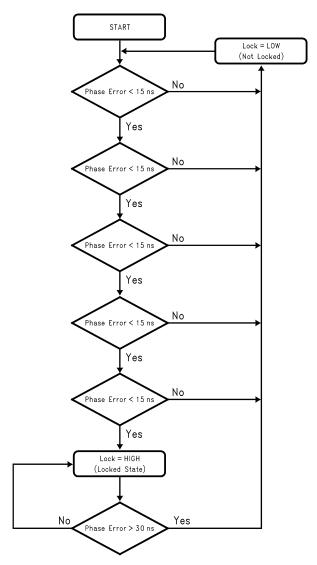

- Digital Filtered Lock Detect Output

- Analog Lock Detect Output (supports both Push-Pull and Open Drain configurations)

- 1.8V MICROWIRE Logic Interface

- Available in 20-Pin TSSOP and 20-Pin ULGA

#### **APPLICATIONS**

- Mobile Handsets

- (GSM, GPRS, W-CDMA, CDMA, PCS, AMPS, PDC, DCS)

- Cordless Handsets

- (DECT, DCT)

- Wireless Data

- Cable TV Tuners

#### DESCRIPTION

The LMX243x devices are high performance frequency synthesizers with integrated dual modulus prescalers. The LMX243x devices are designed for use as RF and IF local oscillators for dual conversion radio transceivers.

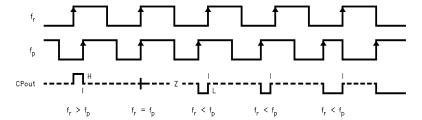

A 32/33 or a 16/17 prescale ratio can be selected for the 5.0 GHz LMX2434 RF synthesizer. An 8/9 or a 16/17 prescale ratio can be selected for both the LMX2430 and LMX2433 RF synthesizers. The IF circuitry contains an 8/9 or a 16/17 prescaler. Using a proprietary digital phase locked loop technique, the LMX243x devices generate very stable, low noise control signals for RF and IF voltage controlled oscillators. Both the RF and IF synthesizers include a two-level programmable charge pump. Both the RF and IF synthesizers have dedicated Fastlock circuitry with integrated timeout counters. Furthermore, only a single word write is required to power up and tune the synthesizers to a new frequency.

Serial data is transferred to the devices via a threewire interface (DATA, LE, CLK). A low voltage logic interface allows direct connection to 1.8V devices. Supply voltages from 2.25V to 2.75V are supported. The LMX243x family features low current consumption:

LMX2430 (3.0 GHz/ 0.8 GHz)—2.8 mA/ 1.4 mA, LMX2433 (3.6 GHz/ 1.7 GHz) —3.2 mA/ 2.0 mA, LMX2434 (5.0 GHz/ 2.5 GHz)—4.6 mA/ 2.4 mA at 2.50V.

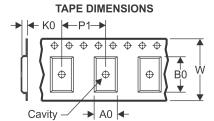

The LMX243x devices are available in 20-Pin TSSOP and 20-Pin ULGA surface mount plastic packages.

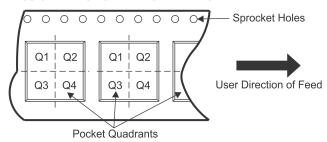

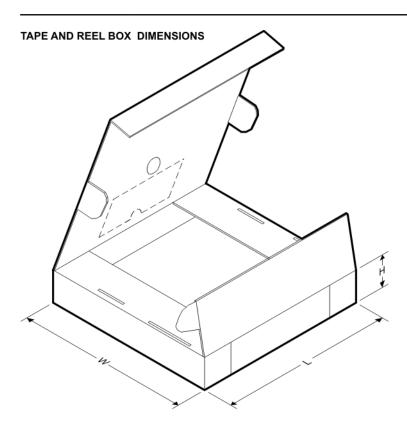

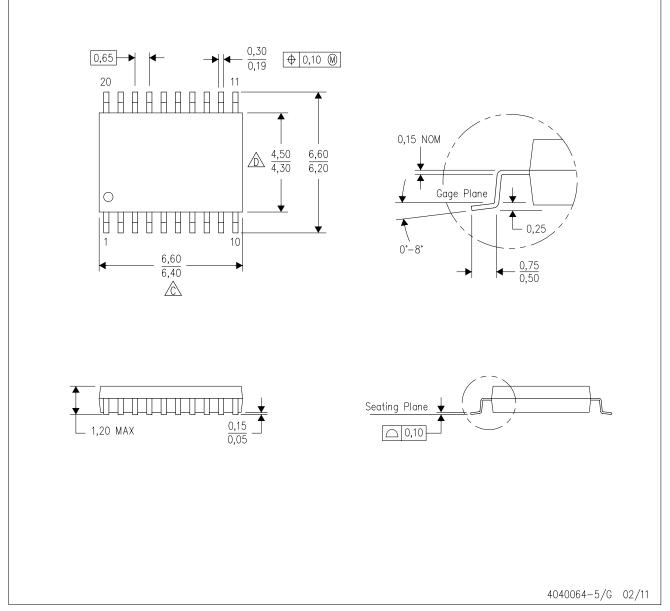

Figure 1. Thin Shrink Small Outline Package (PW0020A)

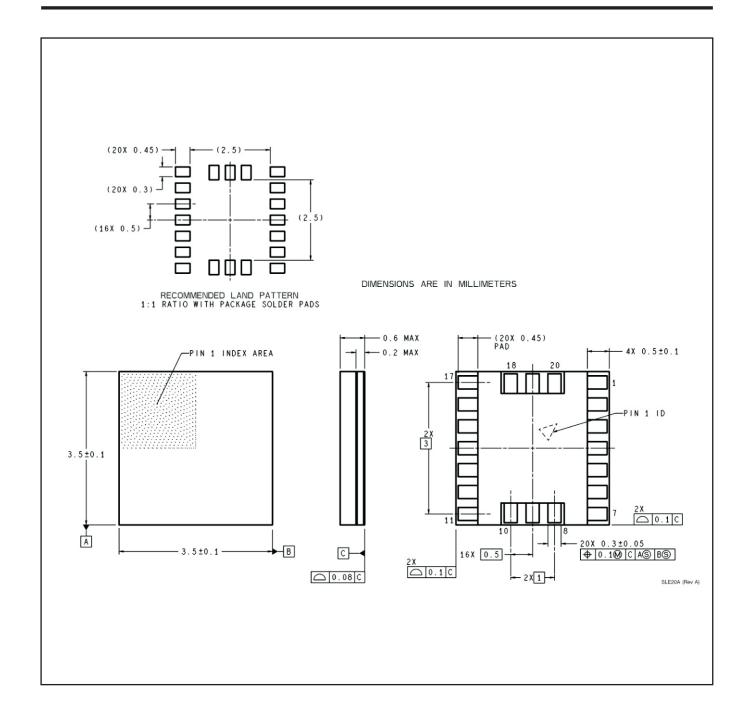

Figure 2. Ultra Thin Chip Scale Package (NPE0020A)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PLLatinum is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

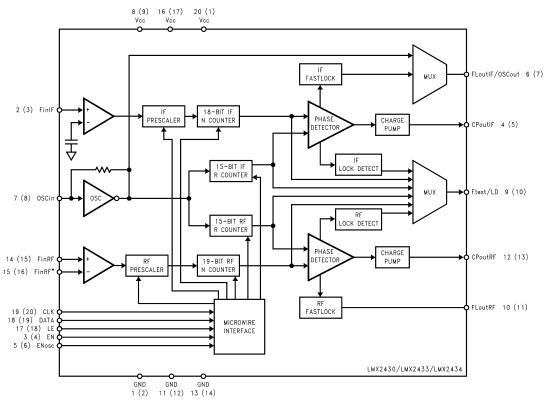

### **Functional Block Diagram**

Note:1 (2) refers to Pin #1 of the 20-Pin ULGA and Pin #2 of the 20-Pin TSSOP

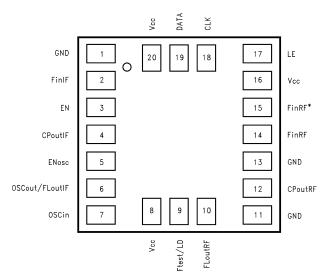

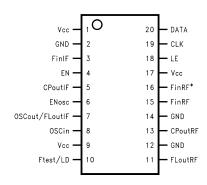

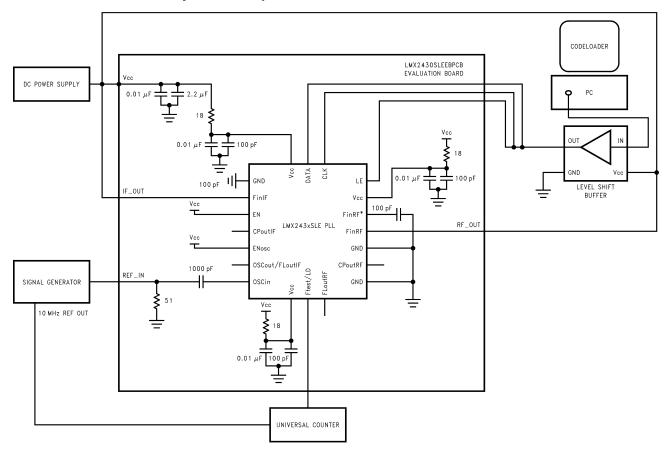

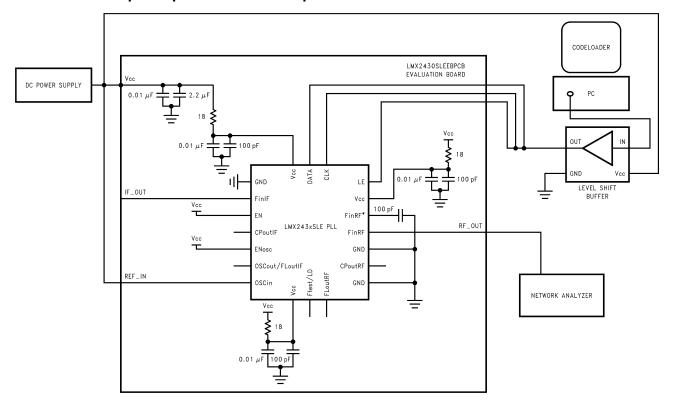

### **Connection Diagrams**

Figure 3. Ultra Thin Chip Scale Package (NPE) (Top View)

Figure 4. Thin Shrink Small Outline Package (PW) (Top View)

#### **Pin Descriptions**

| Pin No.<br>ULGA | Pin No.<br>TSSOP | Pin Name           | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | 2                | GND                | _   | Ground for the IF PLL analog and digital circuits, MICROWIRE <sup>TM</sup> , Ftest/LD and oscillator circuits.                                                                                                                                                                                                                                                                                                                                       |

| 2               | 3                | FinIF              | I   | IF PLL prescaler input. Small signal input from the VCO.                                                                                                                                                                                                                                                                                                                                                                                             |

| 3               | 4                | EN                 | I   | Chip Enable input. High Impedance CMOS input. When this pin is set HIGH, the RF and IF PLLs are powered up. Powerdown is then controlled through the MICROWIRE. When this pin is set LOW, the device is asynchronously powered down and the charge pump output is forced to a high impedance state (TRI-STATE).                                                                                                                                      |

| 4               | 5                | CPoutIF            | 0   | IF PLL charge pump output. The output is connected to the external loop filter, which drives the input of the IF VCO.                                                                                                                                                                                                                                                                                                                                |

| 5               | 6                | ENosc              | I   | Oscillator Enable input. High impedance CMOS input. When this pin is set HIGH, the oscillator buffer is always powered up, independent of the state of the EN pin. When this pin is set LOW, the OSCout/ FLoutIF pin functions as an IF Fastlock output, which connects a resistor in parallel to R2 of the external loop filter.                                                                                                                    |

| 6               | 7                | OSCout/<br>FLoutIF | 0   | Oscillator output/ IF PLL Fastlock output. The output configuration is dependent on the state of the ENosc pin. When ENosc is set LOW, the pin functions as an IF Fastlock output, which connects a resistor in parallel to R2 of the external loop filter. This configuration also functions as a general purpose CMOS TRI-STATE output. When ENosc is set HIGH, the pin functions as an oscillator output so that an external crystal can be used. |

| 7               | 8                | OSCin              | I   | Reference oscillator input. The input has an approximate Vcc/2 threshold and is driven by an external AC coupled source.                                                                                                                                                                                                                                                                                                                             |

| 8               | 9                | Vcc                | _   | Power supply bias for the RF PLL digital circuits and oscillator circuits. Vcc may range from 2.25V to 2.75V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane.                                                                                                                                                                                                                     |

| 9               | 10               | Ftest/LD           | 0   | Programmable multiplexed output. Functions as a general purpose CMOS TRI-<br>STATE output, N and R divider output, RF/ IF PLL push-pull analog lock detect<br>output, RF/ IF PLL open-drain analog lock detect output, or RF/ IF PLL digital filtered<br>lock detect output.                                                                                                                                                                         |

| 10              | 11               | FLoutRF            | 0   | RF PLL Fastlock output. This pin connects a resistor in parallel to R2 of the external loop filter. This pin can also function as a general purpose CMOS TRI-STATE output.                                                                                                                                                                                                                                                                           |

| 11              | 12               | GND                | _   | Ground for the RF PLL digital circuits.                                                                                                                                                                                                                                                                                                                                                                                                              |

Copyright © 2003–2013, Texas Instruments Incorporated

#### Pin Descriptions (continued)

| Pin No.<br>ULGA | Pin No.<br>TSSOP | Pin Name | I/O | Description                                                                                                                                                                                                                                          |

|-----------------|------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12              | 13               | CPoutRF  | 0   | RF PLL charge pump output. The output is connected to the external loop filter, which drives the input of the RF VCO.                                                                                                                                |

| 13              | 14               | GND      | _   | Ground for the RF PLL analog circuits.                                                                                                                                                                                                               |

| 14              | 15               | FinRF    | I   | RF PLL prescaler input. Small signal input from the VCO.                                                                                                                                                                                             |

| 15              | 16               | FinRF*   | I   | RF PLL prescaler complementary input. For single ended operation, this pin should be AC grounded through a 100 pF capacitor. The LMX243x can be driven differentially when the AC coupled capacitor is omitted.                                      |

| 16              | 17               | Vcc      | _   | Power supply bias for the RF PLL analog circuits. Vcc may range from 2.25V to 2.75V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane.                                              |

| 17              | 18               | LE       | I   | MICROWIRE Latch Enable input. High impedance CMOS input. When LE transitions HIGH, DATA stored in the shift register is loaded into one of 6 internal control registers.                                                                             |

| 18              | 19               | CLK      | I   | MICROWIRE Clock input. High impedance CMOS input. DATA is clocked into the 24-bit shift register on the rising edge of CLK.                                                                                                                          |

| 19              | 20               | DATA     | I   | MICROWIRE Data input. High impedance CMOS input. Binary serial data. The MSB of DATA is shifted in first. The two last bits are the control bits.                                                                                                    |

| 20              | 1                | Vcc      | _   | Power supply bias for the IF PLL analog and digital circuits, MICROWIRE, and Ftest/LD circuits. Vcc may range from 2.25V to 2.75V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **Absolute Maximum Ratings**(1)(2)(3)(4)

| - 1.5 - 5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - |                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Power Supply Voltage<br>Vcc to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -0.3V to +3.25V   |

| Voltage on any pin to GND ( $V_I$ ) $V_I$ must be $< +3.25V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3V to Vcc+0.3V |

| Storage Temperature Range (T <sub>S</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | −65°C to +150°C   |

| Lead Temperature (solder 4 s) (T <sub>L</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +260°C            |

- (1) This device is a high performance RF integrated circuit with an ESD rating <2 kV and is ESD sensitive. Handling and assembly of this device should only be done at ESD protected work stations.

- (2) GND = 0V

- (3) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, refer to the Electrical Characteristics section. The ensured specifications apply only for the conditions listed.

- (4) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

## Recommended Operating Conditions<sup>(1)</sup>

| Power Supply Voltage<br>Vcc to GND      | +2.25V to +2.75V |

|-----------------------------------------|------------------|

| Operating Temperature (T <sub>A</sub> ) | −40°C to +85°C   |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications and test conditions, refer to the Electrical Characteristics section. The ensured specifications apply only for the conditions listed.

#### **Electrical Characteristics**

Vcc = EN = 2.5V,  $-40^{\circ}C \le T_A \le +85^{\circ}C$ , unless otherwise specified

| Symbol                                        | Parama                                                                                 | tor                          | Conditions                                                    | Value |      |        | Units  |

|-----------------------------------------------|----------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------|-------|------|--------|--------|

| Зушьог                                        | Parameter                                                                              |                              | Conditions                                                    | Min   | Тур  | Max    | Ullits |

| I <sub>CC</sub> PARAM                         | ETERS                                                                                  |                              |                                                               | ·     |      | ·      | •      |

|                                               | Power Supply Current,                                                                  | LMX2430                      | CLK, DATA and LE = 0V                                         |       | 2.8  | 3.6    | mA     |

|                                               | LMX2433                                                                                | OSCin = GND<br>RF PD Bit = 0 |                                                               | 3.2   | 4.4  | mA     |        |

|                                               | Cymnosizor                                                                             | LMX2434                      | IF_PD Bit = 1<br>RF_P Bit = 0                                 |       | 4.6  | 6.2    | mA     |

| Icc <sub>IF</sub>                             | Power Supply Current,                                                                  | LMX2430                      | CLK, DATA and LE = 0V                                         |       | 1.4  | 2.0    | mA     |

|                                               | IF<br>Synthesizer                                                                      | LMX2433                      | OSCin = GND<br>RF_PD Bit = 1                                  |       | 2.0  | 2.8    | mA     |

|                                               | Cyminosizor                                                                            | LMX2434                      | IF_PD Bit = 0<br>IF_P Bit = 0                                 |       | 2.4  | 3.5    | mA     |

| Icc <sub>PD</sub>                             | Powerdown Current                                                                      |                              | EN, ENosc, CLK, DATA and LE = 0V                              |       |      | 10     | μA     |

| RF SYNTHE                                     | ESIZER PARAMETERS                                                                      |                              |                                                               |       |      |        |        |

| f <sub>FinRF</sub> RF Op                      | RF Operating                                                                           | LMX2430                      | RF_P Bit = 0                                                  | 250   |      | 2500   | MHz    |

|                                               | Frequency                                                                              |                              | RF_P Bit = 1                                                  | 250   |      | 3000   | MHz    |

|                                               |                                                                                        | LMX2433                      | RF_P Bit = 0                                                  | 500   |      | 3000   | MHz    |

|                                               |                                                                                        |                              | RF_P Bit = 1                                                  | 500   |      | 3600   | MHz    |

|                                               |                                                                                        | LMX2434                      | RF_P Bit = 0 or 1                                             | 1000  |      | 5000   | MHz    |

| N <sub>RF</sub> N Divider Range               | N Divider Range                                                                        |                              | $P = 8/9^{(1)}$                                               | 24    |      | 262151 |        |

|                                               |                                                                                        |                              | P = 16/17 <sup>(1)</sup>                                      | 48    |      | 524287 |        |

|                                               |                                                                                        |                              | P = 32/33 <sup>(1)</sup>                                      | 96    |      | 524287 |        |

| R <sub>RF</sub>                               | RF R Divider Range                                                                     |                              |                                                               | 3     |      | 32767  |        |

| f <sub>COMPRF</sub>                           | RF Phase Detector Free                                                                 | quency                       |                                                               |       |      | 10     | MHz    |

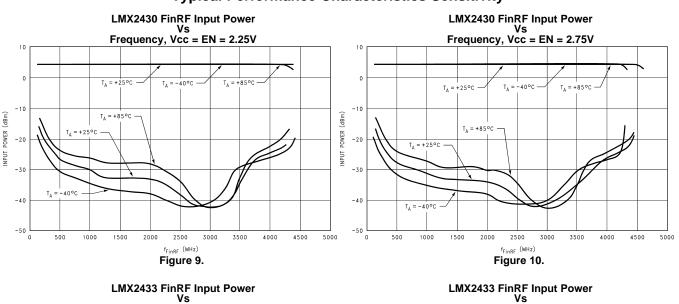

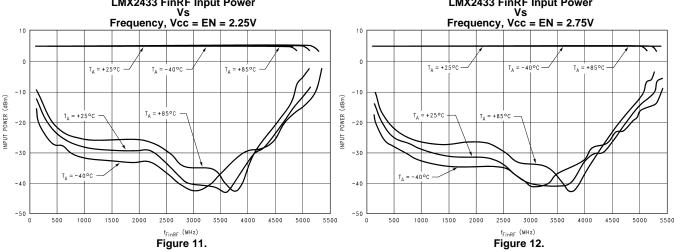

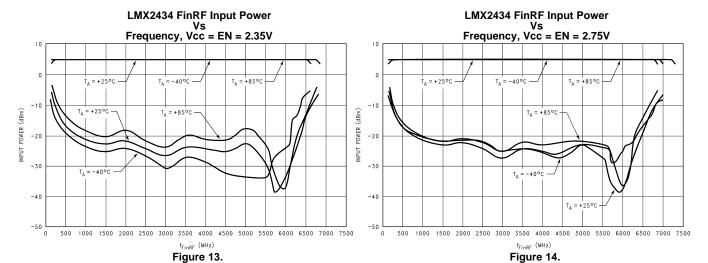

| PFinRF                                        | RF Input Sensitivity                                                                   |                              | LMX2430/33<br>2.25V ≤ Vcc ≤ 2.75V <sup>(2)</sup>              | -15   |      | 0      | dBm    |

|                                               |                                                                                        |                              | LMX2434<br>2.35V ≤ Vcc ≤ 2.75V <sup>(2)</sup>                 | -12   |      | 0      | dBm    |

| I <sub>CPoutRF</sub><br>Source                | RF Charge Pump Outpo                                                                   | ut Source Current            | $V_{CPoutRF} = Vcc/2$<br>RF_CPG Bit = $0^{(3)}$               |       | -1.0 |        | mA     |

|                                               |                                                                                        |                              | V <sub>CPoutRF</sub> = Vcc/2<br>RF_CPG Bit = 1 <sup>(3)</sup> |       | -4.0 |        | mA     |

| I <sub>CPoutRF</sub><br>Sink                  | RF Charge Pump Outpo                                                                   | ut Sink Current              | V <sub>CPoutRF</sub> = Vcc/2<br>RF_CPG Bit = 0 <sup>(3)</sup> |       | 1.0  |        | mA     |

|                                               |                                                                                        |                              | V <sub>CPoutRF</sub> = Vcc/2<br>RF_CPG Bit = 1 <sup>(3)</sup> |       | 4.0  |        | mA     |

| I <sub>CPoutRF</sub><br>TRI                   | RF Charge Pump Output TRI-STATE Current                                                |                              | $0.5V \le V_{CPoutRF} \le Vcc - 0.5V^{(3)}$                   | -2.5  |      | 2.5    | nA     |

| I <sub>CPoutRF</sub><br>%MIS                  | RF Charge Pump Output Sink Current Vs<br>Charge Pump Output Source Current<br>Mismatch |                              | V <sub>CPoutRF</sub> = Vcc/2 <sup>(4)</sup>                   |       | 3    | 10     | %      |

| I <sub>CPoutRF</sub><br>%V <sub>CPoutRF</sub> | RF Charge Pump Output Current Magnitude Variation Vs Charge Pump Output Voltage        |                              | $0.5V \le V_{CPoutRF} \le Vcc - 0.5V^{(4)}$                   |       | 5    | 15     | %      |

| I <sub>CPoutRF</sub><br>%T <sub>A</sub>       | RF Charge Pump Outpo<br>Magnitude Variation Vs                                         |                              | V <sub>CPoutRF</sub> = Vcc/2 <sup>(4)</sup>                   |       | 2    |        | %      |

<sup>(1)</sup> Some of the values in this range are illegal divide ratios (B < A). To obtain continuous legal division, the Minimum Divide Ratio must be calculated. Use N ≥ P \* (P-1), where P is the value of the prescaler selected.

Refer to the LMX243x FinRF Sensitivity Test Setup section

Refer to the LMX243x Charge Pump Test Setup section

Refer to the Charge Pump Current Specification Definitions for details on how these measurements are made.

## **Electrical Characteristics (continued)**

Vcc = EN = 2.5V,  $-40^{\circ}C \le T_{\wedge} \le +85^{\circ}C$ , unless otherwise specified

| Symbol                                        | Parame                                                                                 | ter               | Conditions                                                    |                       | Value |        |          |

|-----------------------------------------------|----------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------|-----------------------|-------|--------|----------|

| Cymbol                                        | 1 draine                                                                               |                   | Conditions                                                    | Min                   | Тур   | Max    | Units    |

| IF SYNTHES                                    | SIZER PARAMETERS                                                                       |                   |                                                               |                       |       |        |          |

| f <sub>FinIF</sub>                            | IF Operating                                                                           | LMX2430           | IF_P Bit = 0 or 1                                             | 100                   |       | 800    | MHz      |

|                                               | Frequency                                                                              | LMX2433           | IF_P Bit = 0 or 1                                             | 250                   |       | 1700   | MHz      |

|                                               |                                                                                        | LMX2434           | IF_P Bit = 0 or 1                                             | 500                   |       | 2500   | MHz      |

| N <sub>IF</sub>                               | IF N Divider Range                                                                     |                   | $P = 8/9^{(5)}$                                               | 24                    |       | 131079 |          |

|                                               |                                                                                        |                   | P = 16/17 <sup>(5)</sup>                                      | 48                    |       | 262143 |          |

| R <sub>IF</sub>                               | IF R Divider Range                                                                     | 1                 |                                                               | 3                     |       | 32767  |          |

| f <sub>COMPIF</sub>                           | IF Phase Detector Free                                                                 | luency            |                                                               |                       |       | 10     | MHz      |

| p <sub>FinIF</sub>                            | IF Input Sensitivity                                                                   |                   | 2.25V ≤ Vcc ≤ 2.75V <sup>(6)</sup>                            | -15                   |       | 0      | dBm      |

| I <sub>CPoutIF</sub><br>Source                | IF Charge Pump Outpu                                                                   | t Source Current  | V <sub>CPoutIF</sub> = Vcc/2<br>IF_CPG Bit = 0 <sup>(7)</sup> |                       | -1.0  |        | mA       |

|                                               |                                                                                        |                   | V <sub>CPoutIF</sub> = Vcc/2<br>IF_CPG Bit = 1 <sup>(7)</sup> |                       | -4.0  |        | mA       |

| I <sub>CPoutIF</sub><br>Sink                  | IF Charge Pump Outpu                                                                   | t Sink Current    | V <sub>CPoutIF</sub> = Vcc/2<br>IF_CPG Bit = 0 <sup>(7)</sup> |                       | 1.0   |        | mA       |

|                                               |                                                                                        |                   | V <sub>CPoutIF</sub> = Vcc/2<br>IF_CPG Bit = 1 <sup>(7)</sup> |                       | 4.0   |        | mA       |

| I <sub>CPoutIF</sub><br>TRI                   | IF Charge Pump Output TRI-STATE Current                                                |                   | $0.5V \le V_{CPoutlF} \le Vcc - 0.5V^{(7)}$                   | -2.5                  |       | 2.5    | nA       |

| I <sub>CPoutIF</sub><br>%MIS                  | IF Charge Pump Output Sink Current Vs<br>Charge Pump Output Source Current<br>Mismatch |                   | V <sub>CPoutIF</sub> = Vcc/2 <sup>(8)</sup>                   |                       | 3     | 10     | %        |

| I <sub>CPoutIF</sub><br>%V <sub>CPoutIF</sub> | IF Charge Pump Output Current<br>Magnitude Variation Vs Charge Pump<br>Output Voltage  |                   | $0.5V \le V_{CPoutlF} \le Vcc - 0.5V^{(8)}$                   |                       | 5     | 15     | %        |

| I <sub>CPoutIF</sub><br>%T <sub>A</sub>       | IF Charge Pump Outpu<br>Magnitude Variation Vs                                         |                   | V <sub>CPoutIF</sub> = Vcc/2 <sup>(8)</sup>                   |                       | 2     |        | %        |

| OSCILLATO                                     | R PARAMETERS                                                                           |                   |                                                               |                       |       | 1      |          |

| f <sub>OSCin</sub>                            | Oscillator Operating Fre                                                               | equency           |                                                               | 1                     |       | 256    | MHz      |

| V <sub>OSCin</sub>                            | Oscillator Sensitivity                                                                 |                   | See <sup>(9)</sup>                                            | 0.5                   |       | Vcc    | $V_{PP}$ |

| I <sub>OSCin</sub>                            | Oscillator Input Current                                                               |                   | V <sub>OSCin</sub> = Vcc                                      |                       |       | 100    | μA       |

|                                               | ·                                                                                      |                   | V <sub>OSCin</sub> = 0V                                       | -100                  |       |        | μA       |

| DIGITAL INT                                   | TERFACE (DATA, CLK, L                                                                  | E, EN, ENosc, Fte | est/LD, FLoutRF, OSCout/ FLoutIF)                             |                       |       |        |          |

| V <sub>IH</sub>                               | High-Level Input Voltage                                                               | ie                |                                                               | 1.6                   |       |        | V        |

| V <sub>IL</sub>                               | Low-Level Input Voltage                                                                | e                 |                                                               |                       |       | 0.4    | V        |

| I <sub>IH</sub>                               | High-Level Input Currer                                                                |                   | V <sub>IH</sub> = Vcc                                         |                       |       | 1.0    | μA       |

| I <sub>IL</sub>                               | Low-Level Input Current                                                                |                   | $V_{IL} = 0V$                                                 | -1.0                  |       | 1      | μA       |

| V <sub>OH</sub>                               | High-Level Output Volta                                                                |                   | I <sub>OH</sub> = -500 μA                                     | V <sub>CC</sub> - 0.4 |       |        | V        |

| V <sub>OL</sub>                               | Low-Level Output Volta                                                                 |                   | I <sub>OL</sub> = 500 μA                                      | - 55                  |       | 0.4    | V        |

|                                               | INTERFACE                                                                              |                   | 1 1                                                           |                       |       | 1      | 1        |

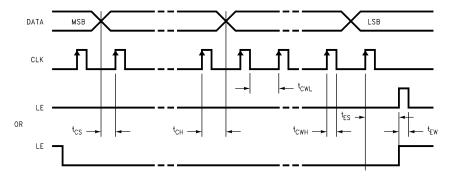

| t <sub>CS</sub>                               | DATA to CLK Set Up T                                                                   | ime               | See <sup>(10)</sup>                                           | 50                    |       |        | ns       |

| t <sub>CH</sub>                               | DATA to CLK Hold Tim                                                                   |                   | See <sup>(10)</sup>                                           | 10                    |       | 1      | ns       |

| <b>U</b> 11                                   | 1                                                                                      |                   | 1                                                             | -                     |       | 1      | 1        |

<sup>(5)</sup> Some of the values in this range are illegal divide ratios (B < A). To obtain continuous legal division, the Minimum Divide Ratio must be calculated. Use  $N \ge P * (P-1)$ , where P is the value of the prescaler selected. Refer to the LMX243x FinRF Sensitivity Test Setup section

Refer to the LMX243x Charge Pump Test Setup section

Refer to the Charge Pump Current Specification Definitions for details on how these measurements are made.

Refer to the LMX243x OSCin Sensitivity Test Setup section

<sup>(10)</sup> Refer to the LMX243x Serial Data Input Timing figure

## **Electrical Characteristics (continued)**

Vcc = EN = 2.5V,  $-40^{\circ}C \le T_A \le +85^{\circ}C$ , unless otherwise specified

| Symbol               | Parameter                                                          |                 | Conditions                                                                                                                                                                                                                                                                                                                                | Value |        |     | Units      |

|----------------------|--------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-----|------------|

| Symbol               | Farame                                                             | .ei             | Conditions                                                                                                                                                                                                                                                                                                                                | Min   | Тур    | Max | Units      |

| t <sub>CWL</sub>     | CLK Pulse Width LOW                                                |                 | See <sup>(10)</sup>                                                                                                                                                                                                                                                                                                                       | 50    |        |     | ns         |

| t <sub>ES</sub>      | CLK to LE Set Up Time                                              |                 | See <sup>(10)</sup>                                                                                                                                                                                                                                                                                                                       | 50    |        |     | ns         |

| t <sub>EW</sub>      | LE Pulse Width                                                     |                 | See <sup>(10)</sup>                                                                                                                                                                                                                                                                                                                       | 50    |        |     | ns         |

| PHASE NO             | ISE CHARACTERISTICS                                                |                 |                                                                                                                                                                                                                                                                                                                                           |       |        |     | •          |

| L <sub>NRF</sub> (f) | RF Synthesizer Normali<br>Contribution (11)                        | zed Phase Noise | TCXO Reference Source<br>RF_CPG Bit = 1<br>IF_PD Bit = 1                                                                                                                                                                                                                                                                                  |       | -219.0 |     | dBc/<br>Hz |

| L <sub>NIF</sub> (f) | IF Synthesizer Normalized Phase Noise Contribution <sup>(11)</sup> |                 | TCXO Reference Source<br>IF_CPG Bit = 1<br>RF_PD Bit = 1                                                                                                                                                                                                                                                                                  |       | -214.0 |     | dBc/<br>Hz |

| L <sub>RF</sub> (f)  | RF Synthesizer Single<br>Side Band Phase<br>Noise Measured         | LMX2430         | $\begin{split} f_{FinRF} &= 2750 \text{ MHz} \\ f &= 10 \text{ kHz offset} \\ f_{COMPRF} &= 1 \text{ MHz} \\ \text{Loop Bandwidth} &= 100 \text{ kHz} \\ N_{RF} &= 2750 \\ f_{OSCin} &= 10 \text{ MHz} \\ v_{OSCin} &= 1 \text{ Vpp} \\ RF\_CPG \text{ Bit} &= 1 \\ IF\_PD \text{ Bit} &= 1 \\ T_A &= +25^{\circ}C^{(12)} \end{split}$    |       | -90.30 |     | dBc/<br>Hz |

|                      |                                                                    | LMX2433         | $\begin{split} &f_{FinRF} = 3200 \text{ MHz} \\ &f = 10 \text{ kHz offset} \\ &f_{COMPRF} = 1 \text{ MHz} \\ &Loop \text{ Bandwidth} = 100 \text{ kHz} \\ &N_{RF} = 3200 \\ &f_{OSCin} = 10 \text{ MHz} \\ &V_{OSCin} = 1 \text{ Vpp} \\ &RF\_CPG \text{ Bit} = 1 \\ &IF\_PD \text{ Bit} = 1 \\ &T_A = +25^{\circ}C^{(12)} \end{split}$   |       | -88.90 |     | dBc/<br>Hz |

|                      |                                                                    | LMX2434         | $\begin{split} f_{FinRF} &= 4700 \text{ MHz} \\ f &= 10 \text{ kHz offset} \\ f_{COMPRF} &= 1 \text{ MHz} \\ \text{Loop Bandwidth} &= 100 \text{ kHz} \\ N_{RF} &= 4700 \\ f_{OSCin} &= 10 \text{ MHz} \\ v_{OSCin} &= 1 \text{ V}_{PP} \\ RF\_CPG \text{ Bit} &= 1 \\ IF\_PD \text{ Bit} &= 1 \\ T_A &= +25^{\circ}C^{(12)} \end{split}$ |       | -85.60 |     | dBc/<br>Hz |

<sup>(11)</sup> Normalized Phase Noise Contribution is defined as: L<sub>N</sub>(f) = L(f) − 20 log (N) − 10 log (f<sub>COMP</sub>), where L(f) is defined as the single side band phase noise measured at an offset frequency, f, in a 1 Hz bandwidth. The offset frequency, f, must be chosen sufficiently smaller than the PLL's loop bandwidth, yet large enough to avoid substantial phase noise contribution from the reference source. N is the value selected for the feedback divider and f<sub>COMP</sub> is the RF/IF phase/ frequency detector comparison frequency.

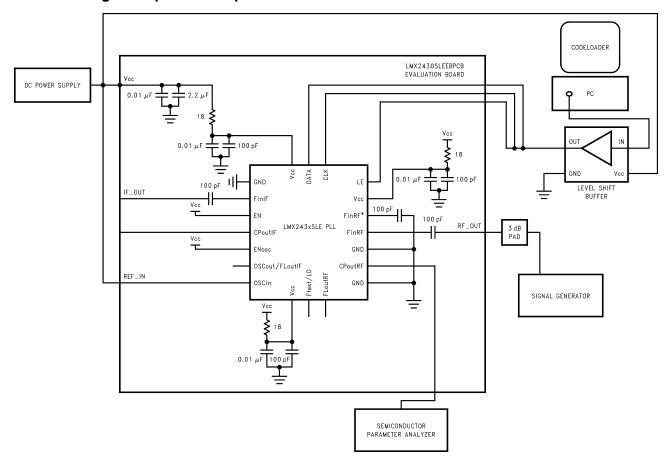

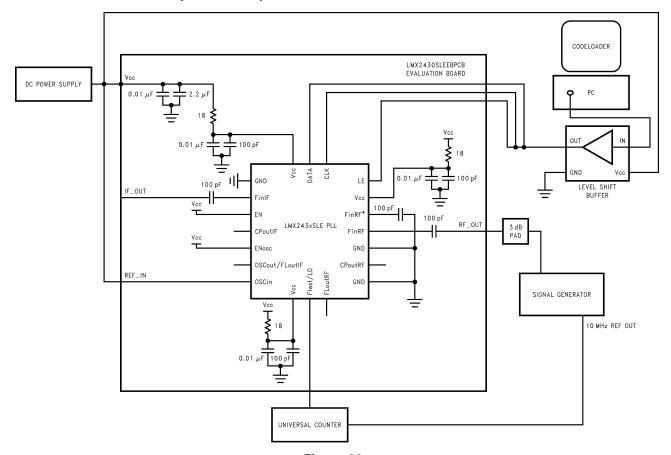

<sup>(12)</sup> The synthesizer phase noise is measured with the LMX2430PW/LMX2430NPE Evaluation boards and the HP8566B Spectrum Analyzer.

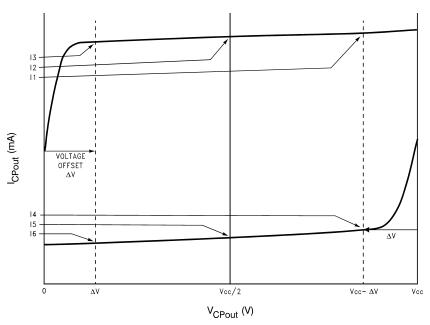

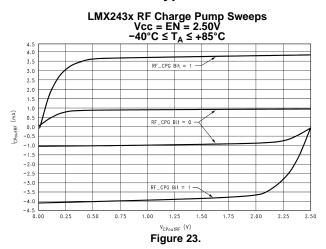

## **Charge Pump Current Specification Definitions**

I1 = Charge Pump Sink Current at  $V_{CPout} = Vcc - \Delta V$

I2 = Charge Pump Sink Current at  $V_{CPout} = Vcc//2$

I3 = Charge Pump Sink Current at  $V_{CPout} = \Delta V$

I4 = Charge Pump Source Current at  $V_{CPout} = Vcc - \Delta V$

$^{\circ}$  I5 = Charge Pump Source Current at  $V_{CPout} = Vcc/2$

I6 = Charge Pump Source Current at  $V_{CPout} = \Delta V$

$\Delta V$  = Voltage offset from the positive and negative rails. Dependent on the VCO tuning range relative to Vcc and GND. Typical values are between 0.5V and 1.0V.

$V_{CPout}$  refers to either  $V_{CPoutRF}$  or  $V_{CPoutIF}$

I<sub>CPout</sub> refers to either I<sub>CPoutRF</sub> or I<sub>CPoutIF</sub>

Figure 5.

$$I_{CPout} \ Vs \ V_{CPout} = \frac{(|11| - |13|)}{(|11| + |13|)} \times 100\%$$

$$= \frac{(|14| - |16|)}{(|14| + |16|)} \times 100\%$$

Figure 6. Charge Pump Output Current Magnitude Variation Vs Charge Pump Output Voltage

$$I_{CPout}$$

Sink Vs  $I_{CPout}$  Source =  $\frac{||2| - ||5|}{\frac{1}{2}(||2| + ||5|)} \times 100\%$

Figure 7. Charge Pump Output Sink Current Vs Charge Pump Output Source Current Mismatch

$$I_{CPout} Vs T_{A} = \frac{|I_{2}| \Big|_{T_{A}} - |I_{2}| \Big|_{T_{A} = 25^{\circ}C}}{|I_{2}| \Big|_{T_{A} = 25^{\circ}C}} \times 100\%$$

$$= \frac{|I_{5}| \Big|_{T_{A}} - |I_{5}| \Big|_{T_{A} = 25^{\circ}C}}{|I_{5}| \Big|_{T_{A} = 25^{\circ}C}} \times 100\%$$

Figure 8. Charge Pump Output Current Magnitude Variation Vs Temperature

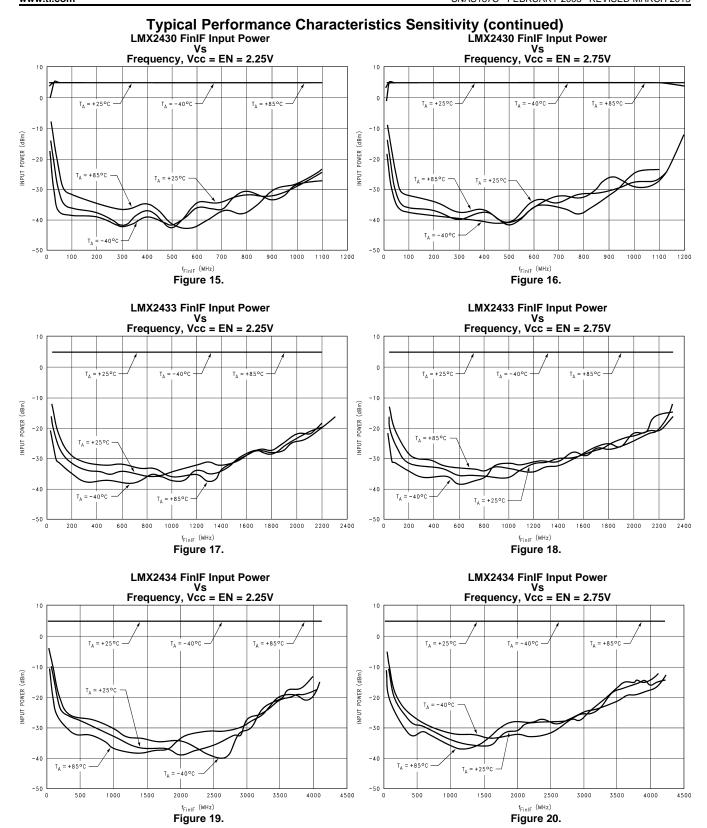

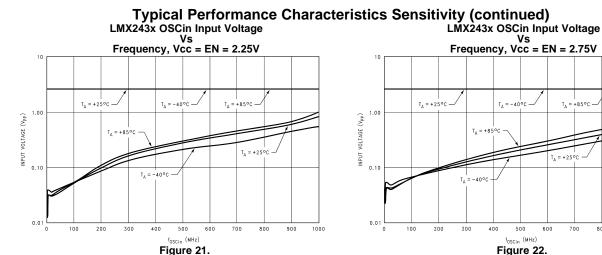

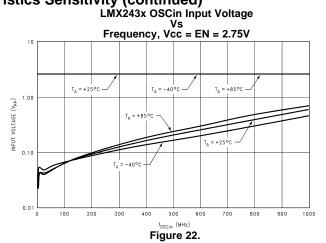

## **Typical Performance Characteristics Sensitivity**

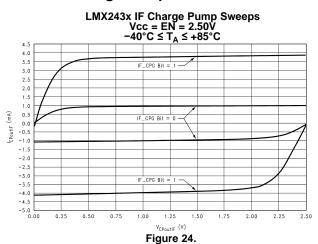

### **Typical Performance Characteristics Charge Pump**

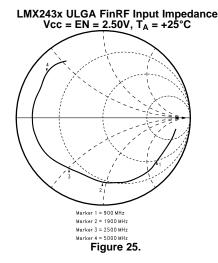

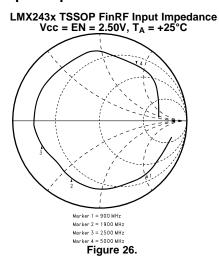

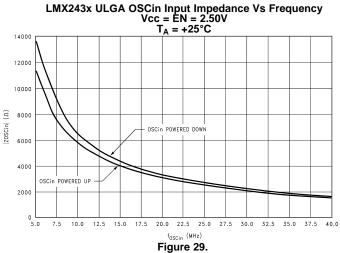

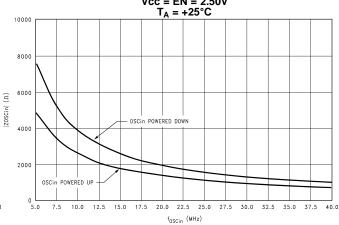

#### Typical Performance Characteristics Input Impedance

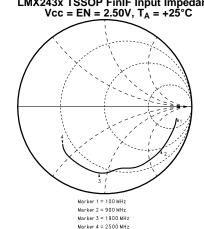

## Typical Performance Characteristics Input Impedance (continued) LMX243x ULGA FinIF Input Impedance Vcc = EN = 2.50V, $T_A$ = +25°C LMX243x TSSOP FinIF Input Impedance Vcc = EN = 2.50V, $T_A$ = +25°C

Marker 1 = 100 MHz

Marker 4 = 2500 MHz Figure 27.

Marker 2 = 900 MHz Marker 3 = 1900 MHz

Figure 28.

LMX233xU TSSOP OSCin Input Impedance Vs Frequency Vcc = EN = 2.50V  $T_A = +25^{\circ}C$

Figure 30.

## LMX243x ULGA FinRF Input Impedance Table (1)

| f <sub>FinRF</sub><br>(MHz) | ΙΓΙ  | Angle (Γ)<br>(°) | Re {ZFinRF}<br>(Ω) | Im {ZFinRF}<br>(Ω) | ZFinRF <br>(Ω) |

|-----------------------------|------|------------------|--------------------|--------------------|----------------|

| 100                         | 0.86 | -8.63            | 334.27             | -339.55            | 476.48         |

| 200                         | 0.86 | -10.72           | 265.44             | -313.48            | 410.77         |

| 300                         | 0.85 | -13.48           | 202.09             | -281.42            | 346.46         |

| 400                         | 0.84 | -17.01           | 150.76             | -245.31            | 287.93         |

| 500                         | 0.83 | -21.05           | 112.18             | -212.85            | 240.60         |

| 600                         | 0.82 | -25.32           | 85.96              | -185.41            | 204.37         |

| 700                         | 0.82 | -29.78           | 67.32              | -162.49            | 175.88         |

| 800                         | 0.81 | -34.35           | 54.27              | -143.15            | 153.09         |

| 900                         | 0.80 | -39.02           | 44.76              | -127.07            | 134.72         |

| 1000                        | 0.80 | -43.83           | 37.32              | -113.62            | 119.59         |

| 1100                        | 0.79 | -48.76           | 31.65              | -102.07            | 106.86         |

| 1200                        | 0.79 | -53.90           | 27.30              | -91.89             | 95.86          |

| 1300                        | 0.78 | -59.07           | 23.84              | -82.83             | 86.19          |

| 1400                        | 0.78 | -64.41           | 21.34              | -74.84             | 77.82          |

| 1500                        | 0.77 | -70.04           | 19.20              | -67.56             | 70.24          |

| 1600                        | 0.76 | -75.84           | 17.46              | -60.88             | 63.33          |

| 1700                        | 0.75 | -82.06           | 16.27              | -54.72             | 57.09          |

| 1800                        | 0.73 | -88.56           | 15.36              | -48.89             | 51.25          |

| 1900                        | 0.72 | -95.19           | 14.90              | -43.34             | 45.83          |

| 2000                        | 0.70 | -101.45          | 14.32              | -38.66             | 41.23          |

| 2100                        | 0.68 | -107.85          | 14.10              | -34.26             | 37.05          |

| 2200                        | 0.67 | -114.12          | 13.81              | -30.35             | 33.34          |

| 2300                        | 0.66 | -120.12          | 13.27              | -27.09             | 30.17          |

| 2400                        | 0.66 | -126.01          | 12.50              | -24.00             | 27.06          |

| 2500                        | 0.67 | -131.82          | 11.68              | -21.22             | 24.22          |

| 2600                        | 0.69 | -137.96          | 10.55              | -18.24             | 21.07          |

| 2700                        | 0.71 | -144.21          | 9.53               | -15.58             | 18.26          |

| 2800                        | 0.72 | -150.25          | 8.55               | -12.92             | 15.49          |

| 2900                        | 0.74 | -156.23          | 7.75               | -10.25             | 12.85          |

| 3000                        | 0.75 | -161.92          | 7.22               | -7.77              | 10.61          |

| 3100                        | 0.76 | -167.18          | 6.87               | -5.48              | 8.79           |

| 3200                        | 0.77 | -172.05          | 6.63               | -3.42              | 7.46           |

| 3300                        | 0.77 | -177.55          | 6.40               | -1.49              | 6.57           |

| 3400                        | 0.78 | 179.16           | 6.18               | 0.35               | 6.19           |

| 3500                        | 0.79 | 174.92           | 5.99               | 2.18               | 6.37           |

| 3600                        | 0.79 | 170.77           | 5.85               | 3.99               | 7.08           |

| 3700                        | 0.80 | 166.54           | 5.74               | 5.80               | 8.16           |

| 3800                        | 0.80 | 162.52           | 5.73               | 7.56               | 9.49           |

| 3900                        | 0.80 | 158.74           | 5.73               | 9.22               | 10.86          |

| 4000                        | 0.80 | 155.06           | 5.68               | 10.84              | 12.24          |

| 4100                        | 0.80 | 151.49           | 5.69               | 12.38              | 13.62          |

| 4200                        | 0.80 | 148.28           | 5.70               | 13.78              | 14.91          |

| 4300                        | 0.80 | 146.02           | 5.73               | 14.88              | 15.95          |

| 4400                        | 0.80 | 144.12           | 5.60               | 15.84              | 16.80          |

| 4500                        | 0.82 | 142.31           | 5.41               | 16.66              | 17.52          |

<sup>(1)</sup> Vcc = EN = 2.50V,  $T_A = +25$ °C

www.ti.com

SNAS187C - FEBRUARY 2003 - REVISED MARCH 2013

| f <sub>FinRF</sub><br>(MHz) | ΙΓΙ  | Angle (Γ)<br>(°) | Re {ZFinRF}<br>(Ω) | Im {ZFinRF}<br>(Ω) | ZFinRF <br>(Ω) |

|-----------------------------|------|------------------|--------------------|--------------------|----------------|

| 4600                        | 0.83 | 140.78           | 5.29               | 17.42              | 18.21          |

| 4700                        | 0.83 | 139.65           | 5.14               | 17.95              | 18.67          |

| 4800                        | 0.84 | 138.75           | 4.99               | 18.38              | 19.05          |

| 4900                        | 0.84 | 137.79           | 4.84               | 18.85              | 19.46          |

| 5000                        | 0.84 | 136.82           | 4.92               | 19.79              | 20.39          |

| 5100                        | 0.84 | 135.77           | 4.88               | 18.89              | 19.51          |

| 5200                        | 0.84 | 134.64           | 4.99               | 20.44              | 21.04          |

| 5300                        | 0.84 | 133.33           | 5.11               | 21.16              | 21.77          |

| 5400                        | 0.84 | 131.68           | 5.25               | 21.96              | 22.58          |

| 5500                        | 0.83 | 129.77           | 5.43               | 23.01              | 23.64          |

| 5600                        | 0.83 | 127.55           | 5.70               | 24.16              | 24.82          |

| 5700                        | 0.82 | 125.41           | 6.03               | 25.33              | 26.04          |

| 5800                        | 0.82 | 123.35           | 6.42               | 26.41              | 27.18          |

| 5900                        | 0.81 | 121.68           | 6.75               | 27.30              | 28.12          |

| 6000                        | 0.80 | 120.42           | 7.11               | 28.00              | 28.89          |

## Table 1. LMX243x TSSOP FinRF Input Impedance Table (1)

| f <sub>FinRF</sub><br>(MHz) | ļΓļ  | Angle (Γ)<br>(°) | Re {ZFinRF}<br>(Ω) | Im {ZFinRF}<br>(Ω) | ZFinRF <br>(Ω) |

|-----------------------------|------|------------------|--------------------|--------------------|----------------|

| 100                         | 0.86 | -12.47           | 214.61             | -314.33            | 380.61         |

| 200                         | 0.85 | -15.35           | 166.75             | -270.14            | 317.46         |

| 300                         | 0.84 | -19.41           | 122.76             | -228.38            | 259.28         |

| 400                         | 0.83 | -24.22           | 89.48              | -193.48            | 213.17         |

| 500                         | 0.82 | -28.97           | 67.73              | -167.98            | 181.12         |

| 600                         | 0.82 | -33.65           | 52.07              | -148.64            | 157.50         |

| 700                         | 0.82 | -38.37           | 41.64              | -131.88            | 138.30         |

| 800                         | 0.82 | -43.22           | 34.60              | -117.36            | 122.35         |

| 900                         | 0.81 | -48.37           | 29.69              | -104.33            | 108.47         |

| 1000                        | 0.80 | -53.84           | 25.88              | -92.74             | 96.28          |

| 1100                        | 0.79 | -59.80           | 22.78              | -82.21             | 85.31          |

| 1200                        | 0.78 | -66.29           | 20.17              | -72.67             | 75.42          |

| 1300                        | 0.77 | -73.30           | 17.88              | -64.06             | 66.51          |

| 1400                        | 0.76 | -80.74           | 15.93              | -56.21             | 58.42          |

| 1500                        | 0.75 | -88.27           | 14.50              | -49.36             | 51.45          |

| 1600                        | 0.74 | -95.87           | 13.27              | -43.30             | 45.29          |

| 1700                        | 0.73 | -103.41          | 12.42              | -37.96             | 39.94          |

| 1800                        | 0.72 | -110.77          | 11.67              | -33.20             | 35.19          |

| 1900                        | 0.71 | -118.23          | 11.20              | -28.78             | 30.88          |

| 2000                        | 0.70 | -125.46          | 11.25              | -24.74             | 27.18          |

| 2100                        | 0.68 | -131.35          | 11.37              | -21.60             | 24.41          |

| 2200                        | 0.68 | -137.19          | 10.94              | -18.79             | 21.74          |

| 2300                        | 0.68 | -143.41          | 10.37              | -15.88             | 18.97          |

| 2400                        | 0.69 | -149.45          | 9.70               | -13.18             | 16.36          |

| 2500                        | 0.71 | -156.15          | 8.62               | -10.26             | 13.40          |

| 2600                        | 0.73 | -163.87          | 7.79               | -6.92              | 10.42          |

| 2700                        | 0.74 | -171.33          | 7.47               | -3.71              | 8.34           |

| 2800                        | 0.75 | -178.24          | 7.30               | 0.76               | 7.34           |

| 2900                        | 0.75 | 174.91           | 7.24               | 2.18               | 7.56           |

| 3000                        | 0.75 | 168.09           | 7.33               | 5.12               | 8.94           |

| 3100                        | 0.74 | 161.11           | 7.53               | 8.14               | 11.09          |

| 3200                        | 0.74 | 153.92           | 7.83               | 11.30              | 13.75          |

| 3300                        | 0.74 | 146.42           | 8.19               | 14.72              | 16.85          |

| 3400                        | 0.74 | 138.67           | 8.59               | 18.36              | 20.27          |

| 3500                        | 0.74 | 130.89           | 8.97               | 22.22              | 23.96          |

| 3600                        | 0.75 | 123.33           | 9.30               | 26.23              | 27.83          |

| 3700                        | 0.76 | 116.17           | 9.54               | 30.32              | 31.79          |

| 3800                        | 0.77 | 109.55           | 9.74               | 34.42              | 35.77          |

| 3900                        | 0.78 | 103.54           | 9.91               | 38.43              | 39.69          |

| 4000                        | 0.79 | 98.25            | 10.20              | 42.23              | 43.44          |

| 4100                        | 0.79 | 93.38            | 10.71              | 45.97              | 47.20          |

| 4200                        | 0.79 | 88.86            | 11.70              | 49.59              | 50.95          |

| 4300                        | 0.78 | 85.10            | 13.43              | 52.63              | 54.32          |

| 4400                        | 0.77 | 82.09            | 14.79              | 55.23              | 57.18          |

| 4500                        | 0.77 | 78.59            | 16.13              | 58.48              | 60.66          |

| 4600                        | 0.76 | 74.73            | 17.90              | 62.30              | 64.82          |

<sup>(1)</sup> Vcc = EN = 2.50V,  $T_A = +25$ °C

## Table 1. LMX243x TSSOP FinRF Input Impedance Table<sup>(1)</sup> (continued)

| f <sub>FinRF</sub><br>(MHz) | ΙΓΙ  | Angle (Γ)<br>(°) | Re {ZFinRF}<br>(Ω) | Im {ZFinRF}<br>(Ω) | ZFinRF <br>(Ω) |

|-----------------------------|------|------------------|--------------------|--------------------|----------------|

| 4700                        | 0.76 | 70.66            | 19.89              | 66.66              | 69.56          |

| 4800                        | 0.75 | 66.05            | 22.50              | 72.05              | 75.48          |

| 4900                        | 0.75 | 61.68            | 25.37              | 77.73              | 81.77          |

| 5000                        | 0.75 | 57.35            | 28.56              | 84.19              | 88.90          |

| 5100                        | 0.76 | 53.11            | 31.70              | 91.39              | 96.73          |

| 5200                        | 0.77 | 48.79            | 34.78              | 100.34             | 106.20         |

| 5300                        | 0.78 | 43.56            | 40.56              | 112.59             | 119.67         |

| 5400                        | 0.78 | 38.11            | 52.53              | 125.62             | 136.16         |

| 5500                        | 0.76 | 32.89            | 71.05              | 135.74             | 153.21         |

| 5600                        | 0.73 | 27.85            | 95.57              | 142.32             | 171.43         |

| 5700                        | 0.71 | 21.89            | 133.18             | 141.32             | 194.19         |

| 5800                        | 0.68 | 15.38            | 177.08             | 116.75             | 212.10         |

| 5900                        | 0.65 | 9.47             | 207.23             | 77.49              | 221.24         |

| 6000                        | 0.64 | 4.15             | 222.92             | 35.24              | 225.69         |

## Table 2. LMX243x ULGA FinIF Input Impedance Table (1)

| f <sub>FinIF</sub><br>(MHz) | ΙΓΙ  | Angle (Γ)<br>(°) | Re {ZFinIF}<br>(Ω) | lm {ZFinIF}<br>(Ω) | ZFinIF <br>(Ω) |

|-----------------------------|------|------------------|--------------------|--------------------|----------------|

| 100                         | 0.87 | -6.19            | 446.34             | -341.41            | 561.94         |

| 200                         | 0.86 | -8.10            | 353.77             | -328.44            | 482.73         |

| 300                         | 0.85 | -10.98           | 257.50             | -300.77            | 395.94         |

| 400                         | 0.84 | -14.21           | 188.33             | -268.39            | 327.87         |

| 500                         | 0.83 | -17.67           | 141.63             | -235.88            | 275.13         |

| 600                         | 0.83 | -21.32           | 109.44             | -206.86            | 234.03         |

| 700                         | 0.82 | -25.13           | 86.57              | -182.41            | 201.91         |

| 800                         | 0.81 | -29.04           | 70.47              | -161.46            | 176.17         |

| 900                         | 0.80 | -32.99           | 58.90              | -144.27            | 155.83         |

| 1000                        | 0.79 | -36.73           | 50.96              | -130.45            | 140.05         |

| 1100                        | 0.79 | -40.28           | 44.21              | -120.14            | 128.02         |

| 1200                        | 0.79 | -44.11           | 37.38              | -111.08            | 117.20         |

| 1300                        | 0.79 | -48.38           | 31.82              | -101.96            | 106.81         |

| 1400                        | 0.79 | -52.91           | 27.95              | -93.09             | 97.20          |

| 1500                        | 0.78 | -57.26           | 25.34              | -85.47             | 89.15          |

| 1600                        | 0.77 | -61.56           | 23.28              | -78.74             | 82.11          |

| 1700                        | 0.77 | -66.01           | 20.98              | -72.74             | 75.71          |

| 1800                        | 0.77 | -71.39           | 18.40              | -66.32             | 68.83          |

| 1900                        | 0.77 | -77.74           | 15.22              | -59.40             | 61.32          |

| 2000                        | 0.76 | -84.72           | 15.02              | -52.48             | 54.59          |

| 2100                        | 0.73 | -92.59           | 14.39              | -46.17             | 48.36          |

| 2200                        | 0.71 | -100.18          | 14.07              | -40.46             | 42.84          |

| 2300                        | 0.69 | -107.33          | 13.94              | -35.79             | 38.41          |

| 2400                        | 0.68 | -114.48          | 13.37              | -31.55             | 34.27          |

| 2500                        | 0.68 | -118.42          | 12.71              | -28.62             | 31.32          |

<sup>(1)</sup> Vcc = EN = 2.50V,  $T_A = +25$ °C

## Table 3. LMX243x TSSOP FinIF Input Impedance Table (1)

| f <sub>FinIF</sub><br>(MHz) | ΙΓΙ  | Angle (Γ)<br>(°) | Re {ZFinIF}<br>(Ω) | Im {ZFinIF}<br>(Ω) | ZFinIF <br>(Ω) |

|-----------------------------|------|------------------|--------------------|--------------------|----------------|

| 100                         | 0.87 | -7.11            | 400.44             | -348.14            | 530.62         |

| 200                         | 0.86 | -9.92            | 288.69             | -318.81            | 430.10         |

| 300                         | 0.85 | -13.64           | 198.42             | -281.45            | 344.36         |

| 400                         | 0.84 | -17.47           | 141.73             | -246.13            | 284.02         |

| 500                         | 0.84 | -21.42           | 105.75             | -214.58            | 239.22         |

| 600                         | 0.83 | -25.39           | 82.00              | -188.43            | 205.50         |

| 700                         | 0.83 | -29.46           | 65.48              | -166.34            | 178.76         |

| 800                         | 0.82 | -33.67           | 53.78              | -147.46            | 156.96         |

| 900                         | 0.81 | -37.99           | 45.17              | -131.83            | 139.35         |

| 1000                        | 0.80 | -42.47           | 38.82              | -117.87            | 124.10         |

| 1100                        | 0.79 | -46.96           | 33.93              | -106.36            | 111.64         |

| 1200                        | 0.79 | -51.67           | 29.53              | -96.20             | 100.63         |

| 1300                        | 0.78 | -57.02           | 25.26              | -86.47             | 90.08          |

| 1400                        | 0.77 | -63.11           | 22.15              | -76.93             | 80.06          |

| 1500                        | 0.76 | -69.26           | 20.49              | -68.42             | 71.42          |

| 1600                        | 0.74 | -74.82           | 19.54              | -61.59             | 64.62          |

| 1700                        | 0.74 | -79.79           | 17.70              | -56.35             | 59.06          |

| 1800                        | 0.74 | -86.55           | 15.09              | -50.74             | 52.94          |

| 1900                        | 0.74 | -94.37           | 13.38              | -44.56             | 46.53          |

| 2000                        | 0.73 | -101.95          | 12.62              | -38.87             | 40.87          |

| 2100                        | 0.72 | -108.92          | 12.21              | -34.18             | 36.30          |

| 2200                        | 0.71 | -115.63          | 11.65              | -30.11             | 32.29          |

| 2300                        | 0.71 | -123.23          | 11.13              | -25.97             | 28.25          |

| 2400                        | 0.69 | -131.44          | 11.08              | 11.08 -21.74       |                |

| 2500                        | 0.67 | -138.35          | 11.54              | -18.31             | 21.64          |

<sup>(1)</sup> Vcc = EN = 2.50V,  $T_A = +25$ °C

## Table 4. LMX243x ULGA OSCin Input Impedance Table (1)