# LMK04828 Ultra Low-Noise JESD204B Compliant Clock Jitter Cleaner with Dual Loop PLLs

Check for Samples: LMK04828B

### 1 INTRODUCTION

### 1.1 Features

- JEDEC JESD204B Support

- Ultra-Low RMS Jitter and Performance

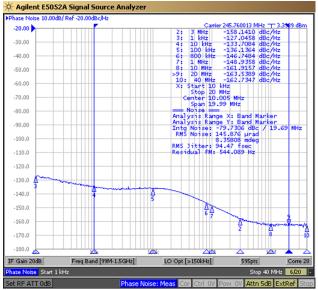

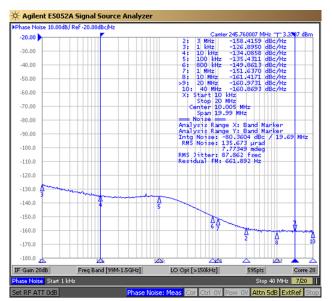

- 88 fs RMS jitter (12 kHz to 20 MHz)

- 91 fs RMS jitter (100 Hz to 20 MHz)

- -162.5 dBc/Hz noise floor at 245.76 MHz

- Up to 14 Differential Device Clocks from PLL2

- Up to 7 SYSREF Clocks

- Maximum clock output frequency 3.1 GHz

- LVPECL, LVDS, HSDS, LCPECL programmable outputs from PLL2

- Up to 1 buffered VCXO/Crystal output from PLL1

- LVPECL, LVDS, 2xLVCMOS programmable

- Dual Loop PLLatinum™ PLL Architecture

- PI 1

- Up to 3 redundant input clocks

- Automatic and manual switch-over modes

- Hitless switching and LOS

- Integrated Low-Noise Crystal Oscillator Circuit

- Holdover mode when input clocks are lost

- PI 12

- Normalized [1 Hz] PLL noise floor of -227 dBc/Hz

- Phase detector rate up to 155 MHz

- OSCin frequency-doubler

- Two Integrated Low-Noise VCOs

- 50% duty cycle output divides, 1 to 32 (even and odd)

- Precision digital delay, dynamically adjustable

- · 25 ps step analog delay

- Multi-mode: Dual PLL, single PLL, and clock distribution in 0 delay option

- Industrial Temperature Range: -40 to 85°C

- 3.15 V to 3.45 V operation

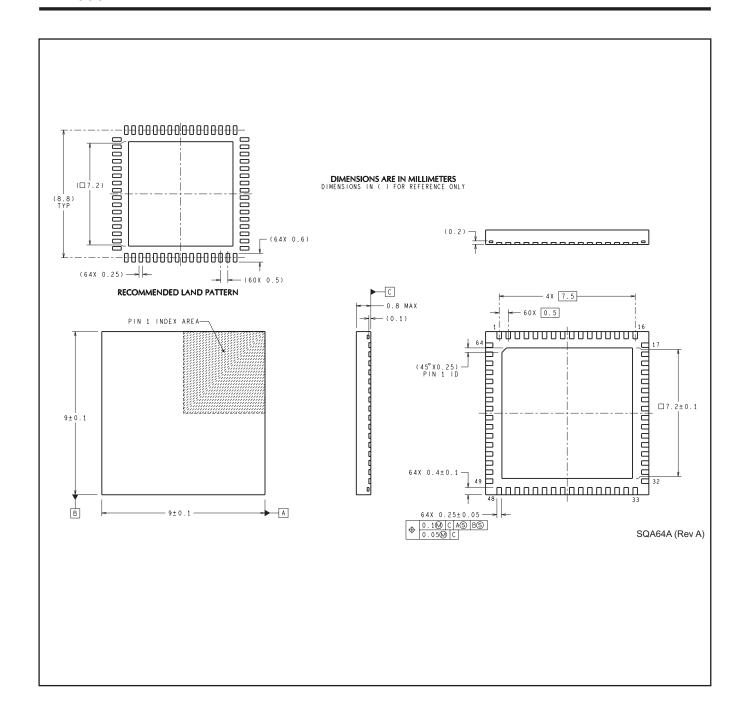

- Package: 64-pin QFN (9.0 x 9.0 x 0.8 mm)

| Device   | VCO0 Frequency   | VCO1 Frequency   |

|----------|------------------|------------------|

| LMK04828 | 2370 to 2600 MHz | 2945 to 3005 MHz |

### 1.2 Applications

- Wireless Infrastructure

- Data Converter Clocking

- Networking, SONET/SDH, DSLAM

- Medical / Video / Military / Aerospace

- Test and Measurement

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

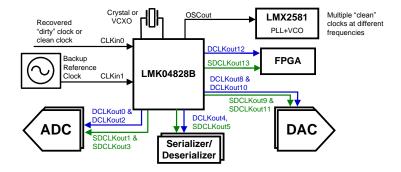

### 1.3 Description

The LMK04820 family is the industry's highest performance clock conditioner with JEDEC JESD204B support.

The 14 clock outputs from PLL2 can be configured to drive seven JESD204B converters or other logic devices using device and SYSREF clocks. SYSREF can be provided using both DC and AC coupling. Not limited to JESD204B applications, each of the 14 outputs can individually be configured as a high performance outputs for traditional clocking systems.

The high performance combined with features like the ability to trade off between power or performance, dual VCOs, dynamic digital delay, holdover, glitchless analog delay make the LMK04828 family ideal for providing flexible high performance clocking trees.

### 1.4 Device Configuration Information

| NSID         | Reference<br>Inputs <sup>(1)</sup> | OSCout (Buffered OSCin<br>Clock) LVDS/ LVPECL/<br>LVCMOS (1) | PLL2 Programmable<br>LVDS/LVPECL/HSDS<br>Outputs | VCO0 Frequency   | VCO1 Frequency   |

|--------------|------------------------------------|--------------------------------------------------------------|--------------------------------------------------|------------------|------------------|

| LMK04828BISQ | Up to 3                            | Up to 1                                                      | 14                                               | 2370 to 2600 MHz | 2945 to 3005 MHz |

<sup>(1)</sup> OSCout may also be third clock input, CLKin2.

#### 1.5 **Functional Block Diagrams and Operating Modes**

The LMK04820 Family is a flexible device that can be configured for many different use cases. The following simplified block diagrams help show the user the different use cases of the device.

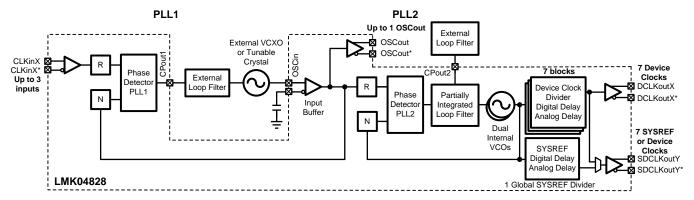

### 1.5.1 **DUAL PLL**

Figure 1-1 illustrates the typical use case of the LMK04820 family in dual loop mode. In dual loop mode the reference to PLL1 from CLKin0, CLKin1, or CLKin2. An external VCXO or tunable crystal will be used to provide feedback for the first PLL and a reference to the second PLL. This first PLL cleans the jitter with the VCXO or low cost tunable crystal by using a narrow loop bandwidth. The VCXO or tunable crystal output may be buffered through the OSCout port. The VCXO or tunable crystal is used as the reference to PLL2 and may be doubled using the frequency doubler. The internal VCO drives up to seven divide/delay blocks which drive up to 14 clock outputs.

Hitless switching and holdover functionality are optionally available when the input reference clock is lost. Holdover works by fixing the tuning voltage of PLL1 to the VCXO or tunable crystal.

It is also possible to use an external VCO in place of PLL2's internal VCO. In this case one less CLKin is available as a reference.

Figure 1-1. Simplified Functional Block Diagram for Dual Loop Mode

Table 1-1. Dual Loop Mode Register Configuration

| Field          | Register<br>Address | Function                                        | Value  | Selected Value                        |

|----------------|---------------------|-------------------------------------------------|--------|---------------------------------------|

| PLL1_NCLK_MUX  | 0x13F               | Selects the input to the PLL1 N divider         | 0      | OSCin                                 |

| PLL2_NCLK_MUX  | 0x13F               | Selects the input to the PLL2 N divider         | 1      | PLL2_P                                |

| FB_MUX_EN      | 0x13F               | Enables the Feedback Mux                        | 0      | Disabled                              |

| FB_MUX         | 0x13F               | Selects the output of the Feedback Mux          | Х      | Don't care because FB_MUX is disabled |

| OSCin_PD       | 0x140               | Powers down the OSCin port                      | 0      | Powered up                            |

| CLKin0_OUT_MUX | 0x147               | Selects where the output of CLKin0 is directed. | 2      | PLL1                                  |

| CLKin1_OUT_MUX | 0x147               | Selects where the output of CLKin1 is directed. | 2      | PLL1                                  |

| VCO_MUX        | 0x138               | Selects the VCO 0, 1 or an external VCO         | 0 or 1 | VCO 0 or VCO 1                        |

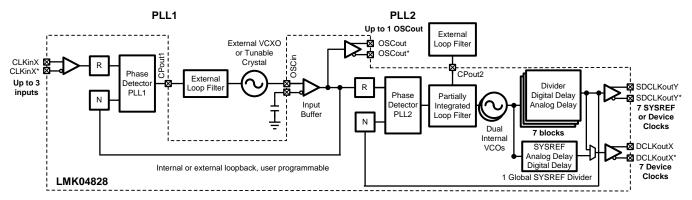

### 1.5.2 0-DELAY DUAL PLL

Figure 1-2 illustrates the use case of cascaded 0-delay dual loop mode. This configuration differs from duel loop mode Figure 1-1 in that the feedback for PLL2 is driven by a clock output instead of the VCO output. Figure 1-3 illustrates the use case of nested 0-delay dual loop mode. This configuration is similar to the duel PLL in Section 1.5.1 except that the feedback to the first PLL is driven by a clock output. This causes the clock outputs to have deterministic phase relationship with the clock input. Since all the clock outputs can be synchronized together, all the clock outputs can share the same deterministic phase relationship with the clock input signal. The feedback to PLL1 can be connected internally as shown using CLKout6, CLKout8, SYSREF, or externally using FBCLKin (CLKin1).

It is also possible to use an external VCO in place of PLL2's internal VCO; but one less CLKin is available as a reference and external 0-delay feedback is not available.

Figure 1-2. Simplified Functional Block Diagram for Cascaded 0-delay Dual Loop Mode

Table 1-2. Cascaded 0-delay Dual Loop Mode Register Configuration

| Field          | Register<br>Address | Function                                        | Value      | Selected Value                            |

|----------------|---------------------|-------------------------------------------------|------------|-------------------------------------------|

| PLL1_NCLK_MUX  | 0x13F               | Selects the input to the PLL1 N divider.        | 0          | OSCin                                     |

| PLL2_NCLK_MUX  | 0x13F               | Selects the input to the PLL2 N divider         | 1          | Feedback Mux                              |

| FB_MUX_EN      | 0x13F               | Enables the Feedback Mux.                       | 1          | Feedback Mux Enabled                      |

| FB_MUX         | 0x13F               | Selects the output of the Feedback Mux.         | 0, 1, or 2 | Select between DCLKout6, DCLKout8, SYSREF |

| OSCin_PD       | 0x140               | Powers down the OSCin port.                     | 0          | Powered up                                |

| CLKin0_OUT_MUX | 0x147               | Selects where the output of CLKin0 is directed. | 0          | PLL1                                      |

| CLKin1_OUT_MUX | 0x147               | Selects where the output of CLKin1 is directed. | 0 or 2     | Fin or PLL1                               |

| VCO_MUX        | 0x138               | Selects the VCO 0, 1 or an external VCO         | 0 or 1     | VCO 0 or VCO 1                            |

Figure 1-3. Simplified Functional Block Diagram for Nested 0-delay Dual Loop Mode

Table 1-3 illustrates nested 0-delay mode. This is the same as cascaded except the clock out feedback is to PLL1. The CLKin and CLKout have the same deterministic phase relationship but the VCXO's phase will not be deterministic to the CLKin or CLKouts.

Table 1-3. Nested 0-delay Dual Loop Mode Register Configuration

| Field Register<br>Address |       | Function                                        | Value      | Selected Value                               |  |  |

|---------------------------|-------|-------------------------------------------------|------------|----------------------------------------------|--|--|

| PLL1_NCLK_MUX             | 0x13F | Selects the input to the PLL1 N divider.        | 1          | Feedback Mux                                 |  |  |

| PLL2_NCLK_MUX             | 0x13F | Selects the input to the PLL2 N divider         | 0          | PLL2 P                                       |  |  |

| FB_MUX_EN                 | 0x13F | Enables the Feedback Mux.                       | 1          | Enabled                                      |  |  |

| FB_MUX                    | 0x13F | Selects the output of the Feedback Mux.         | 0, 1, or 2 | Select between DCLKout6,<br>DCLKout8, SYSREF |  |  |

| OSCin_PD                  | 0x140 | Powers down the OSCin port.                     | 0          | Powered up                                   |  |  |

| CLKin0_OUT_MUX            | 0x147 | Selects where the output of CLKin0 is directed. | 2          | PLL1                                         |  |  |

| CLKin1_OUT_MUX            | 0x147 | Selects where the output of CLKin1 is directed. | 0 or 2     | Fin or PLL1                                  |  |  |

| VCO_MUX                   | 0x138 | Selects the VCO 0, 1 or an external VCO         | 0 or 1     | VCO 0 or VCO 1                               |  |  |

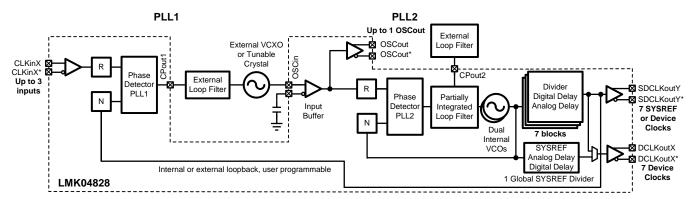

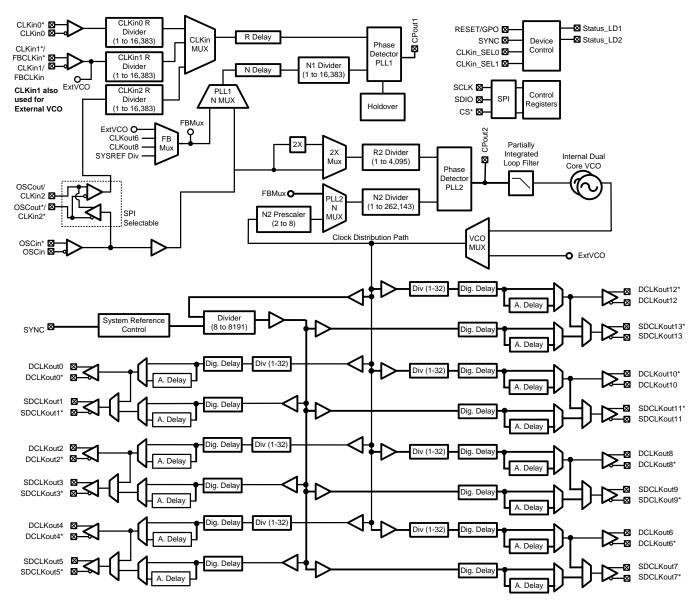

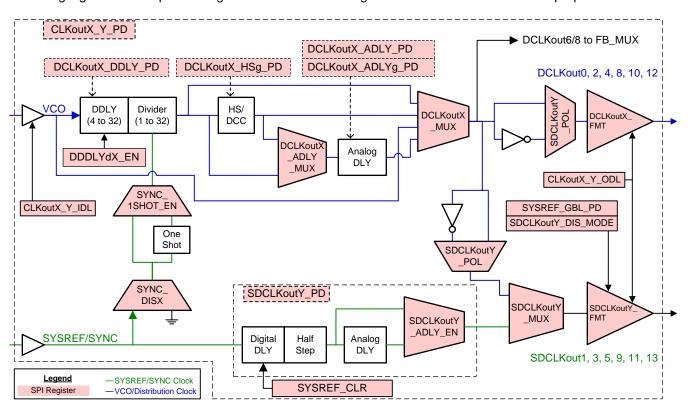

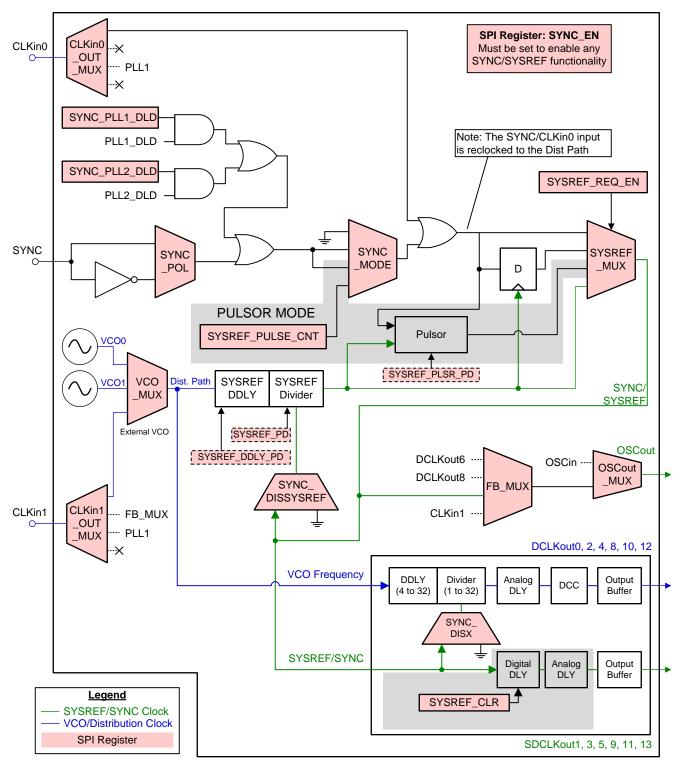

### 1.5.3 DETAILED LMK04820 FAMILY BLOCK DIAGRAM

Figure 1-4 illustrates the complete LMK04820 family block diagram.

Figure 1-4. Detailed LMK04820 Family Block Diagram

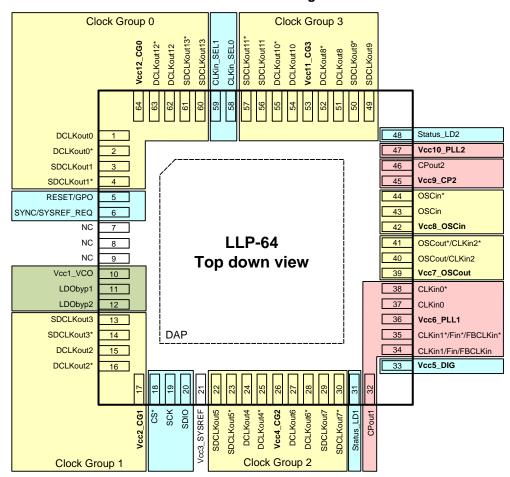

#### **Connection Diagram** 1.6

### 64-Pin QFN Package

Table 1-4. Pin Descriptions (1)

| Pin Number | Name(s)                  | I/O | Туре         | Description                                                                                      |

|------------|--------------------------|-----|--------------|--------------------------------------------------------------------------------------------------|

| 1, 2       | DCLKout0,<br>DCLKout0*   | 0   | Programmable | Device clock output 0.                                                                           |

| 3, 4       | SDCLKout1,<br>SDCLKout1* | 0   | Programmable | SYSREF / Device clock output 1                                                                   |

| 5          | RESET/GPO                | I/O | CMOS         | Device reset input or GPO                                                                        |

| 6          | SYNC/SYSREF_R<br>EQ      | I/O | CMOS         | Synchronization input or programmable status pin or SYSREF_REQ for requesting continuous SYSREF. |

| 7, 8, 9    | NC                       |     |              | No Connection. These pins must be left floating.                                                 |

| 10         | Vcc1_VCO                 |     | PWR          | Power supply for VCO LDO.                                                                        |

| 11         | LDObyp1                  |     | ANLG         | LDO Bypass, bypassed to ground with 10 µF capacitor.                                             |

| 12         | LDObyp2                  |     | ANLG         | LDO Bypass, bypassed to ground with a 0.1 µF capacitor.                                          |

| 13, 14     | SDCLKout3,<br>SDCLKout3* | 0   | Programmable | SYSREF / Device Clock output 3.                                                                  |

| 15, 16     | DCLKout2,<br>DCLKout2*   | 0   | Programmable | Device clock output 2.                                                                           |

| 17         | Vcc2_CG1                 |     | PWR          | Power supply for clock outputs 2 and 3.                                                          |

| 18         | CS*                      | I   | CMOS         | Chip Select                                                                                      |

| 19         | SCK                      | Ī   | CMOS         | SPI Clock                                                                                        |

Submit Documentation Feedback Product Folder Links: LMK04828B

<sup>(1)</sup> See Section 7.2 section for recommended connections.

### Table 1-4. Pin Descriptions (1) (continued)

| Table 1-4. Fin Descriptions \(\gamma\) (continued) |                            |     |              |                                                                  |  |  |  |

|----------------------------------------------------|----------------------------|-----|--------------|------------------------------------------------------------------|--|--|--|

| Pin Number                                         | Name(s)                    | I/O | Туре         | Description                                                      |  |  |  |

| 20                                                 | SDIO                       | I/O | CMOS         | SPI Data                                                         |  |  |  |

| 21                                                 | Vcc3_SYSREF                |     | PWR          | Power supply for SYSREF divider and SYNC.                        |  |  |  |

| 22, 23                                             | SDCLKout5,<br>SDCKLout5*   | 0   | Programmable | SYSREF / Device clock output 5.                                  |  |  |  |

| 24, 25                                             | DCLKout4,<br>DCLKout4*     | 0   | Programmable | Device clock output 4.                                           |  |  |  |

| 26                                                 | Vcc4_CG2                   |     | PWR          | Power supply for clock outputs 4, 5, 6 and 7.                    |  |  |  |

| 27, 28                                             | DCLKout6,<br>DCLKout6*     | 0   | Programmable | Device clock output 6.                                           |  |  |  |

| 29, 30                                             | SDCLKout7,<br>SDCLKout7*   | 0   | Programmable | SYSREF / Device clock output 7.                                  |  |  |  |

| 31                                                 | Status_LD1                 | I/O | Programmable | Programmable status pin.                                         |  |  |  |

| 32                                                 | CPout1                     | 0   | ANLG         | Charge pump 1 output.                                            |  |  |  |

| 33                                                 | Vcc5_DIG                   |     | PWR          | Power supply for the digital circuitry.                          |  |  |  |

|                                                    | CLKin1, CLKin1*            | I   | ANLG         | Reference Clock Input Port for PLL1.                             |  |  |  |

| 34, 35                                             | FBCLKin,<br>FBCLKin*       | I   | ANLG         | Feedback input for external clock feedback input (0-delay mode). |  |  |  |

|                                                    | Fin, Fin*                  | I   | ANLG         | External VCO Input (External VCO mode).                          |  |  |  |

| 36                                                 | Vcc6_PLL1                  |     | PWR          | Power supply for PLL1, charge pump 1.                            |  |  |  |

| 37, 38                                             | CLKin0, CLKin0*            | I   | ANLG         | Reference Clock Input Port 0 for PLL1.                           |  |  |  |

| 39                                                 | Vcc7_OSCout                |     | PWR          | Power supply for OSCout port.                                    |  |  |  |

| 40,41                                              | OSCout, OSCout*            | 0   | Programmable | Buffered output of OSCin port.                                   |  |  |  |

| 42                                                 | Vcc8_OSCin                 |     | PWR          | Power supply for OSCin                                           |  |  |  |

| 43, 44                                             | OSCin, OSCin*              | I   | ANLG         | Feedback to PLL1, Reference input to PLL2. AC coupled.           |  |  |  |

| 45                                                 | Vcc9_CP2                   |     | PWR          | Power supply for PLL2 Charge Pump.                               |  |  |  |

| 46                                                 | CPout2                     | 0   | ANLG         | Charge pump 2 output.                                            |  |  |  |

| 47                                                 | Vcc10_PLL2                 |     | PWR          | Power supply for PLL2.                                           |  |  |  |

| 48                                                 | Status_LD2                 | I/O | Programmable | Programmable status pin.                                         |  |  |  |

| 49, 50                                             | SDCLKout9,<br>SDCLKout9*   | 0   | Programmable | SYSREF / Device clock 9                                          |  |  |  |

| 51, 52                                             | DCLKout8,<br>DCLKout8*     | 0   | Programmable | Device clock output 8.                                           |  |  |  |

| 53                                                 | Vcc11_CG3                  |     | PWR          | Power supply for clock outputs 8, 9, 10, and 11.                 |  |  |  |

| 54, 55                                             | DCLKout10,<br>DCLKout10*   | 0   | Programmable | Device clock output 10.                                          |  |  |  |

| 56, 57                                             | SDCLKout11,<br>SDCLKout11* | 0   | Programmable | SYSREF / Device clock output 11.                                 |  |  |  |

| 58                                                 | CLKin_SEL0                 | I/O | Programmable | Programmable status pin.                                         |  |  |  |

| 59                                                 | CLKin_SEL1                 | I/O | Programmable | Programmable status pin.                                         |  |  |  |

| 60, 61                                             | SDCLKout13,<br>SDCLKout13* | 0   | Programmable | SYSREF / Device clock output 13.                                 |  |  |  |

| 62, 63                                             | DCLKout12,<br>DCLKout12*   | 0   | Programmable | Device clock output 12.                                          |  |  |  |

| 64                                                 | Vcc12_CG0                  |     | PWR          | Power supply for clock outputs 0, 1, 12, and 13.                 |  |  |  |

| DAP                                                | DAP                        |     | GND          | DIE ATTACH PAD, connect to GND.                                  |  |  |  |

| 1 | INTR | RODUCTION                                     | 1                 | 4.7  | Internal VCOs                          | 24 |

|---|------|-----------------------------------------------|-------------------|------|----------------------------------------|----|

|   | 1.1  | Features                                      | <u>1</u>          | 4.8  | External VCO Mode                      | 24 |

|   | 1.2  | Applications                                  | <u>1</u>          | 4.9  | Clock Distribution                     | 24 |

|   | 1.3  | Description                                   | 2                 | 4.10 | 0-Delay                                | 26 |

|   | 1.4  | Device Configuration Information              | 2                 | 4.11 | Status Pins                            | 26 |

|   | 1.5  | Functional Block Diagrams and Operating Modes | <u>3</u> 5        | FUN  | ICTIONAL DESCRIPTIONS                  | 27 |

|   | 1.6  | Connection Diagram                            | <u>7</u>          | 5.1  | Modes Of Operation                     | 27 |

| 2 | ELE  | CTRICAL SPECIFICATIONS                        | 10                | 5.2  | SYNC/SYSREF                            | 27 |

|   | 2.1  | Absolute Maximum Ratings                      | 10                | 5.3  | JEDEC JESD204B                         | 30 |

|   | 2.2  | Package Thermal Resistance                    | 10                | 5.4  | Digital Delay                          | 32 |

|   | 2.3  | Recommended Operating Conditions              | 10                | 5.5  | SYSREF to Device Clock Alignment       | 36 |

|   | 2.4  | Electrical Characteristics                    | 11                | 5.6  | Input Clock Switching                  | 37 |

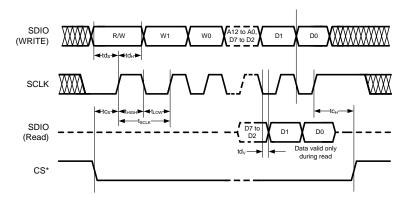

|   | 2.5  | SPI Timing Diagram                            | 20                | 5.7  | Digital Lock Detect                    | 38 |

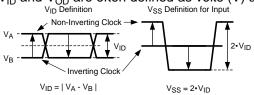

|   | 2.6  | Differential Voltage Measurement Terminology  | 21                | 5.8  | Holdover                               | 39 |

| 3 | TYPI | CAL PERFORMANCE CHARACTERISTICS               | <mark>22</mark> 6 | GEN  | IERAL PROGRAMMING INFORMATION          | 41 |

|   | 3.1  | Clock Output AC Characteristics               | 22                | 6.1  | Recommended Programming Sequence       | 41 |

| 4 | FEA  | TURES                                         | 23                | 6.2  | Register Map                           | 42 |

|   | 4.1  | Jitter Cleaning                               | 23                | 6.3  | Device Register Descriptions           | 46 |

|   | 4.2  | JEDEC JESD204B Support                        | <u>23</u> 7       | APP  | PLICATION INFORMATION                  | 85 |

|   | 4.3  | Three PLL1 Redundant Reference Inputs         |                   | 7.1  | Digital Lock Detect Frequency Accuracy | 85 |

|   |      | (CLKin0/CLKin0*, CLKin1/CLKin1*, and          | 22                | 7.2  | Pin Connection Recommendations         | 85 |

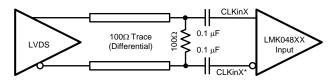

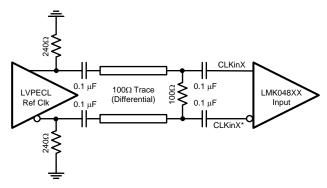

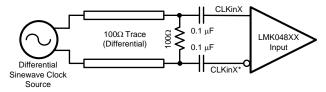

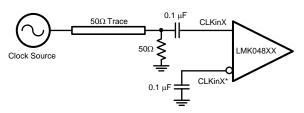

|   | 4.4  | CLKin2/CLKin2*)                               |                   | 7.3  | Driving CLKin AND OSCin Inputs         | 86 |

|   | 4.4  | VCXO/Crystal Buffered Output                  |                   | 7.4  | Power Supply                           | 88 |

|   | 4.5  | Frequency Holdover                            |                   | 7.5  | Thermal Management                     | 89 |

|   | 4.6  | PLL2 Integrated Loop Filter Poles             | <u> 24</u>        |      |                                        |    |

### 2 ELECTRICAL SPECIFICATIONS

### 2.1 Absolute Maximum Ratings (1) (2) (3)

| Parameter                                                                        | Symbol           | Ratings                         | Units |

|----------------------------------------------------------------------------------|------------------|---------------------------------|-------|

| Supply Voltage (4)                                                               | V <sub>CC</sub>  | -0.3 to 3.6                     | V     |

| Input Voltage                                                                    | V <sub>IN</sub>  | -0.3 to (V <sub>CC</sub> + 0.3) | V     |

| Storage Temperature Range                                                        | T <sub>STG</sub> | -65 to 150                      | °C    |

| Lead Temperature (solder 4 seconds)                                              | T <sub>L</sub>   | +260                            | °C    |

| Junction Temperature                                                             | $T_J$            | 150                             | °C    |

| Differential Input Current (CLKinX/X*, OSCin/OSCin*, FBCLKin/FBCLKin*, Fin/Fin*) | I <sub>IN</sub>  | ± 5                             | mA    |

| Moisture Sensitivity Level                                                       | MSL              | 3                               |       |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not assure specific performance limits. For assured specifications and test conditions, see the Electrical Characteristics. The assured specifications apply only to the test conditions listed.

- (2) This device is a high performance RF integrated circuit with an ESD rating up to 2 kV Human Body Model, up to 150 V Machine Model, and up to 250 V Charged Device Model and is ESD sensitive. Handling and assembly of this device should only be done at ESD-free workstations.

- (3) Stresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These are absolute stress ratings only. Functional operation of the device is only implied at these or any other conditions in excess of those given in the operation sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

- (4) Never to exceed 3.6 V.

### 2.2 Package Thermal Resistance

Table 2-1, 64-Lead QFN

|                       |                                                  | LMK04828B |        |  |

|-----------------------|--------------------------------------------------|-----------|--------|--|

| Symbol                | Thermal Metric <sup>(1)</sup>                    | NKD       | Units  |  |

|                       |                                                  | 64 Pins   |        |  |

| $\theta_{JA}$         | Junction-to-ambient thermal resistance (2)       | 24.3      |        |  |

| θ <sub>JC</sub> (TOP) | Junction-to-case(top) thermal resistance (3)     | 6.1       |        |  |

| $\theta_{JB}$         | Junction-to-board thermal resistance (4)         | 3.5       | ° C/W  |  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter (5)   | 0.1       | - C/VV |  |

| $\Psi_{JB}$           | Junction-to-board characterization parameter (6) | 3.5       |        |  |

| $\theta_{JC}(BOTTOM)$ | Junction-to-case(bottom) thermal resistance (7)  | 0.7       |        |  |

- 1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, High-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case(top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\Psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter,  $\Psi_{JB}$  estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case(bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

### 2.3 Recommended Operating Conditions

| Parameter               | Symbol          | Min  | Typical | Max  | Unit |

|-------------------------|-----------------|------|---------|------|------|

| Junction<br>Temperature | TJ              |      |         | 125  | °C   |

| Ambient Temperature     | T <sub>A</sub>  | -40  | 25      | 85   | °C   |

| Supply Voltage          | V <sub>CC</sub> | 3.15 | 3.3     | 3.45 | V    |

**ELECTRICAL SPECIFICATIONS**

### 2.4 Electrical Characteristics

| Symbol                           | Parameter                                                    | Conditions                                                                             | Min   | Тур | Max             | Units |

|----------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-----|-----------------|-------|

|                                  |                                                              | Current Consumption                                                                    | 1     |     | 1               |       |

| I <sub>CC_PD</sub>               | Power Down Supply Current                                    |                                                                                        |       | 1   | 3               | mA    |

| I <sub>CC_CLKS</sub>             | Supply Current (1)                                           | 14 HSDS 8 mA clocks enabled PLL1 and PLL2 locked.                                      |       | 565 | 665             | mA    |

|                                  | CLKin0/0*, CLKin1/1                                          | *, and CLKin2/2* Input Clock Specificat                                                | ions  |     |                 |       |

| $f_{CLKin}$                      | Clock Input Frequency                                        |                                                                                        | 0.001 |     | 750             | MHz   |

| SLEW <sub>CLKin</sub>            | Clock Input Slew Rate (2)                                    | 20% to 80%                                                                             | 0.15  | 0.5 |                 | V/ns  |

| $V_{\text{ID}}CLKin$             | Clock Input                                                  |                                                                                        | 0.125 |     | 1.55            | V     |

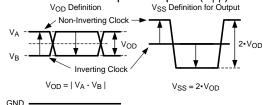

| V <sub>SS</sub> CLKin            | Differential Input Voltage (3)<br>Figure 2-2                 | AC coupled                                                                             | 0.25  |     | 3.1             | Vpp   |

| V                                | Clock Input<br>Single-ended Input Voltage                    | AC coupled to CLKinX;<br>CLKinX* AC coupled to Ground<br>CLKinX_BUF_TYPE = 0 (Bipolar) | 0.25  |     | 2.4             | Vpp   |

| $V_{CLKin}$                      |                                                              | AC coupled to CLKinX;<br>CLKinX* AC coupled to Ground<br>CLKinX_BUF_TYPE = 1 (MOS)     | 0.35  |     | 2.4             | Vpp   |

|                                  | DC offset voltage between CLKinX/CLKinX* (CLKinX* - CLKinX)  | Each pin AC coupled, CLKin0/1/2<br>CLKin0_BUF_TYPE = 0 (Bipolar)                       |       | 0   |                 | mV    |

| V <sub>CLKinX-offset</sub>       |                                                              | Each pin AC coupled, CLKin0/1<br>CLKinX_BUF_TYPE = 1 (MOS)                             |       | 55  |                 | mV    |

|                                  | DC offset voltage between CLKin2/CLKin2* (CLKin2* - CLKin2)  | Each pin AC coupled<br>CLKin2_BUF_TYPE = 1 (MOS)                                       |       | 20  |                 | mV    |

| $V_{CLKin}V_{IH}$                | High input voltage                                           | DC coupled to CLKinX;                                                                  | 2.0   |     | V <sub>CC</sub> | V     |

| $V_{\text{CLKin-}}V_{\text{IL}}$ | Low input voltage                                            | CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = 1 (MOS)                                 | 0.0   |     | 0.4             | V     |

|                                  | FBCLKin/FBCL                                                 | Kin* and Fin/Fin* Input Specifications                                                 |       |     |                 |       |

| f <sub>FBCLKin</sub>             | Clock Input Frequency for<br>0-delay with external feedback. | AC coupled<br>CLKin1_BUF_TYPE = 0 (Bipolar)                                            | 0.001 |     | 750             | MHz   |

| f <sub>Fin</sub>                 | Clock Input Frequency for external VCO or distribution mode. | AC coupled <sup>(4)</sup> CLKin1_BUF_TYPE = 0 (Bipolar)                                | 0.001 |     | 3100            | MHz   |

| V <sub>FBCLKin/Fin</sub>         | Single Ended<br>Clock Input Voltage                          | AC coupled CLKin1_BUF_TYPE = 0 (Bipolar)                                               | 0.25  |     | 2.0             | Vpp   |

| SLEW <sub>FBCLKin/Fin</sub>      | Slew Rate on CLKin (2)                                       | AC coupled; 20% to 80%; (CLKinX_BUF_TYPE = 0)                                          | 0.15  | 0.5 |                 | V/ns  |

<sup>(1)</sup> See applications section Section 7.4 for Icc for specific part configuration and how to calculate Icc for a specific design.

<sup>(2)</sup> In order to meet the jitter performance listed in the subsequent sections of this data sheet, the minimum recommended slew rate for all input clocks is 0.5 V/ns. This is especially true for single-ended clocks. Phase noise performance will begin to degrade as the clock input slew rate is reduced. However, the device will function at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) will be less susceptible to degradation in phase noise performance at lower slew rates due to their common mode noise rejection. However, it is also recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device outputs.

<sup>(3)</sup> See Section 2.6 for definition of  $V_{\text{ID}}$  and  $V_{\text{OD}}$  voltages.

<sup>(4)</sup> Assured by characterization. ATE tested at 2949.12 MHz.

$(3.15 \text{ V} < \text{V}_{CC} < 3.45 \text{ V}, -40 ^{\circ}\text{C} < \text{T}_{A} < 85 ^{\circ}\text{C}$ . Typical values at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at the Recommended Operating Conditions and are **not** assured.)

| Symbol                                | Parameter                                                                                  | Conditions                                                                                                                | Min  | Тур    | Max  | Units   |

|---------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|--------|------|---------|

|                                       |                                                                                            | PLL1 Specifications                                                                                                       |      |        |      |         |

| f <sub>PD1</sub>                      | PLL1 Phase Detector Frequency                                                              |                                                                                                                           |      |        | 40   | MHz     |

|                                       |                                                                                            | $V_{CPout1} = V_{CC}/2$ , PLL1_CP_GAIN = 0                                                                                |      | 50     |      |         |

|                                       |                                                                                            | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 1                                                                |      | 150    |      |         |

| I SOLIBCE                             | PLL1 Charge                                                                                | $V_{CPout1} = V_{CC}/2$ , PLL1_CP_GAIN = 2                                                                                |      | 250    |      | μA      |

| I <sub>CPout1</sub> SOURCE            | Pump Source Current (1)                                                                    |                                                                                                                           |      | •••    |      | μΑ      |

|                                       |                                                                                            | $V_{CPout1} = V_{CC}/2$ , PLL1_CP_GAIN = 14                                                                               |      | 1450   |      |         |

|                                       |                                                                                            | $V_{CPout1} = V_{CC}/2$ , PLL1_CP_GAIN = 15                                                                               |      | 1550   |      |         |

|                                       |                                                                                            | $V_{CPout1}=V_{CC}/2$ , PLL1_CP_GAIN = 0                                                                                  |      | -50    |      |         |

|                                       |                                                                                            | $V_{CPout1}=V_{CC}/2$ , PLL1_CP_GAIN = 1                                                                                  |      | -150   |      |         |

| I <sub>CPout1</sub> SINK              | PLL1 Charge                                                                                |                                                                                                                           |      | -250   |      | μA      |

| ICPout13IIVI                          | Pump Sink Current (1)                                                                      |                                                                                                                           |      |        |      | μΑ      |

|                                       |                                                                                            | $V_{CPout1} = V_{CC}/2$ , PLL1_CP_GAIN = 14                                                                               |      | -1450  |      |         |

|                                       |                                                                                            | $V_{CPout1}=V_{CC}/2$ , PLL1_CP_GAIN = 15                                                                                 |      | -1550  |      |         |

| I <sub>CPout1</sub> %MIS              | Charge Pump<br>Sink / Source Mismatch                                                      | $V_{CPout1} = V_{CC}/2$ , $T = 25  ^{\circ}C$                                                                             |      | 1      | 10   | %       |

| I <sub>CPout1</sub> V <sub>TUNE</sub> | Magnitude of Charge Pump Current<br>Variation vs. Charge Pump Voltage                      | $0.5 \text{ V} < \text{V}_{\text{CPout1}} < \text{V}_{\text{CC}} - 0.5 \text{ V}$<br>$T_{\text{A}} = 25 ^{\circ}\text{C}$ |      | 4      |      | %       |

| I <sub>CPout1</sub> %TEMP             | Charge Pump Current vs. Temperature Variation                                              |                                                                                                                           |      | 4      |      | %       |

| I <sub>CPout1</sub> TRI               | Charge Pump TRI-STATE Leakage<br>Current                                                   | 0.5 V < V <sub>CPout</sub> < V <sub>CC</sub> - 0.5 V                                                                      |      |        | 5    | nA      |

|                                       | PLL 1/f Noise at 10 kHz offset.                                                            | PLL1_CP_GAIN = 350 μA                                                                                                     |      | -117   |      |         |

| PN10kHz                               | Normalized to 1 GHz Output<br>Frequency                                                    | PLL1_CP_GAIN = 1550 μA                                                                                                    |      | -118   |      | dBc/Hz  |

| PN1Hz                                 | Normalized Phase Noise Contribution                                                        | PLL1_CP_GAIN = 350 μA                                                                                                     |      | -221.5 |      | dBc/Hz  |

| PINTEL                                | Normalized Phase Noise Contribution                                                        | PLL1_CP_GAIN = 1550 μA                                                                                                    |      | -223   |      | UBC/FIZ |

|                                       | PLL2 Refer                                                                                 | ence Input (OSCin) Specifications                                                                                         |      |        |      |         |

| f <sub>OSCin</sub>                    | PLL2 Reference Input (2)                                                                   |                                                                                                                           |      |        | 500  | MHz     |

| SLEW <sub>OSCin</sub>                 | PLL2 Reference Clock minimum slew rate on OSCin (3)                                        | 20% to 80%                                                                                                                | 0.15 | 0.5    |      | V/ns    |

| V <sub>OSCin</sub>                    | Input Voltage for OSCin or OSCin*  AC coupled; Single-ended (Unused pin AC coupled to GND) |                                                                                                                           | 0.2  |        | 2.4  | Vpp     |

| V <sub>ID</sub> OSCin                 | Differential voltage swing                                                                 |                                                                                                                           | 0.2  |        | 1.55 | [V]     |

| V <sub>SS</sub> OSCin                 | Figure 2-2                                                                                 | AC coupled                                                                                                                | 0.4  |        | 3.1  | Vpp     |

| V <sub>OSCin-offset</sub>             | DC offset voltage between OSCin/OSCin* (OSCinX* - OSCinX)                                  | Each pin AC coupled                                                                                                       |      | 20     |      | mV      |

| f <sub>doubler_max</sub>              | Doubler input frequency (4)                                                                | EN_PLL2_REF_2X = 1 <sup>(5)</sup> ;<br>OSCin Duty Cycle 40% to 60%                                                        |      |        | 155  | MHz     |

<sup>(1)</sup> This parameter is programmable

<sup>(2)</sup> F<sub>OSCin</sub> maximum frequency assured by characterization. Production tested at 122.88 MHz.

<sup>(3)</sup> In order to meet the jitter performance listed in the subsequent sections of this data sheet, the minimum recommended slew rate for all input clocks is 0.5 V/ns. This is especially true for single-ended clocks. Phase noise performance will begin to degrade as the clock input slew rate is reduced. However, the device will function at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) will be less susceptible to degradation in phase noise performance at lower slew rates due to their common mode noise rejection. However, it is also recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device outputs.

<sup>(4)</sup> Assured by characterization. ATE tested at 122.88 MHz.

<sup>(5)</sup> The EN\_PLL2\_REF\_2X bit enables/disables a frequency doubler mode for the PLL2 OSCin path.

$(3.15 \text{ V} < \text{V}_{CC} < 3.45 \text{ V}, -40 ^{\circ}\text{C} < \text{T}_{A} < 85 ^{\circ}\text{C}$ . Typical values at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at the Recommended Operating Conditions and are **not** assured.)

| Symbol                                | Parameter                                                          | Conditions                                                                                                                       | Min | Тур    | Max | Units      |

|---------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|------------|

|                                       | Crystal (                                                          | Oscillator Mode Specifications                                                                                                   |     |        |     |            |

| F <sub>XTAL</sub>                     | Crystal Frequency Range                                            | Fundamental mode crystal ESR = 200 $\Omega$ (10 to 30 MHz) ESR = 125 $\Omega$ (30 to 40 MHz)                                     | 10  |        | 40  | MHz        |

| C <sub>IN</sub>                       | Input Capacitance of OSCin port                                    | -40 to +85 °C                                                                                                                    |     | 1      |     | pF         |

|                                       | PLL2 Phase Dete                                                    | ector and Charge Pump Specifications                                                                                             |     |        |     |            |

| f <sub>PD2</sub>                      | Phase Detector Frequency (1)                                       |                                                                                                                                  |     |        | 155 | MHz        |

|                                       |                                                                    | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 0                                                                                         |     | 100    |     |            |

| I <sub>CPout</sub> SOURCE             | PLL2 Charge Pump Source Current                                    | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 1                                                                                         |     | 400    |     | Ī <b>a</b> |

|                                       | (2)                                                                | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 2                                                                                         |     | 1600   | μA  |            |

|                                       |                                                                    | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 3                                                                                         |     | 3200   |     |            |

|                                       |                                                                    | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 0                                                                                         |     | -100   |     |            |

| I OINIK                               | DILO Obassa David Octavity (2)                                     | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 1                                                                                         |     | -400   |     | 1          |

| I <sub>CPout</sub> SINK               | PLL2 Charge Pump Sink Current (2)                                  | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 2                                                                                         |     | -1600  |     | μA         |

|                                       |                                                                    | $V_{CPout2}=V_{CC}/2$ , PLL2_CP_GAIN = 3                                                                                         |     | -3200  |     |            |

| I <sub>CPout2</sub> %MIS              | Charge Pump Sink/Source Mismatch                                   | $V_{CPout2}=V_{CC}/2$ , $T_A=25$ °C                                                                                              |     | 1      | 10  | %          |

| I <sub>CPout2</sub> V <sub>TUNE</sub> | Magnitude of Charge Pump Current vs. Charge Pump Voltage Variation | $0.5 \text{ V} < \text{V}_{\text{CPout2}} < \text{V}_{\text{CC}} - 0.5 \text{ V}$<br>$\text{T}_{\text{A}} = 25 ^{\circ}\text{C}$ |     | 4      |     | %          |

| I <sub>CPout2</sub> %TEMP             | Charge Pump Current vs. Temperature Variation                      |                                                                                                                                  |     | 4      |     | %          |

| I <sub>CPout2</sub> TRI               | Charge Pump Leakage                                                | 0.5 V < V <sub>CPout2</sub> < V <sub>CC</sub> - 0.5 V                                                                            |     |        | 10  | nA         |

|                                       | PLL 1/f Noise at 10 kHz offset (3).                                | PLL2_CP_GAIN = 400 μA                                                                                                            |     | -118   |     |            |

| PN10kHz                               | Normalized to<br>1 GHz Output Frequency                            | PLL2_CP_GAIN = 3200 μA                                                                                                           |     | -121   |     | dBc/Hz     |

| PN1Hz                                 | Normalized Phase Noise Contribution                                | PLL2_CP_GAIN = $400 \mu A$                                                                                                       |     | -222.5 |     | dBc/Hz     |

| PN1HZ                                 | (4)                                                                | PLL2_CP_GAIN = 3200 μA                                                                                                           |     | -227   |     | ubc/ITZ    |

<sup>(1)</sup> Assured by characterization. ATE tested at 122.88 MHz.

(2) This parameter is programmable

<sup>(3)</sup> A specification in modeling PLL in-band phase noise is the 1/f flicker noise, L<sub>PLL\_flicker</sub>(f), which is dominant close to the carrier. Flicker noise has a 10 dB/decade slope. PN10kHz is normalized to a 10 kHz offset and a 1 GHz carrier frequency. PN10kHz = L<sub>PLL\_flicker</sub>(10 kHz) - 20log(Fout / 1 GHz), where L<sub>PLL\_flicker</sub>(f) is the single side band phase noise of only the flicker noise's contribution to total noise, L(f). To measure L<sub>PLL\_flicker</sub>(f) it is important to be on the 10 dB/decade slope close to the carrier. A high compare frequency and a clean crystal are important to isolating this noise source from the total phase noise, L(f). L<sub>PLL\_flicker</sub>(f) can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of L<sub>PLL\_flicker</sub>(f) and L<sub>PLL\_flicker</sub>(f).

<sup>(4)</sup> A specification modeling PLL in-band phase noise. The normalized phase noise contribution of the PLL, L<sub>PLL\_flat</sub>(f), is defined as: PN1HZ=L<sub>PLL\_flat</sub>(f) - 20log(N) - 10log(f<sub>PDX</sub>). L<sub>PLL\_flat</sub>(f) is the single side band phase noise measured at an offset frequency, f, in a 1 Hz bandwidth and f<sub>PDX</sub> is the phase detector frequency of the synthesizer. L<sub>PLL\_flat</sub>(f) contributes to the total noise, L(f).

$(3.15 \text{ V} < \text{V}_{CC} < 3.45 \text{ V}, -40 ^{\circ}\text{C} < \text{T}_{A} < 85 ^{\circ}\text{C}$ . Typical values at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at the Recommended Operating Conditions and are **not** assured.)

| Symbol                 | Parameter                                       | Cond                  | itions                                                     | Min  | Тур      | Max  | Units       |

|------------------------|-------------------------------------------------|-----------------------|------------------------------------------------------------|------|----------|------|-------------|

|                        | Ir                                              | nternal VCO Specifica | tions                                                      |      |          |      |             |

|                        | LANG 1000 VOO Toolog Dang                       | VC                    | O0                                                         | 2370 |          | 2600 | N 41 1-     |

| f <sub>VCO</sub>       | LMK04828 VCO Tuning Range                       | VC                    | 2945                                                       |      | 3005     | MHz  |             |

|                        | Fine Tuning Consists site                       | LMK04828 VCO          | 0 at 2457.6 MHz                                            |      | 17 to 27 |      | MHz/V       |

| K <sub>vco</sub>       | Fine Tuning Sensitivity                         | LMK04828 VCO1         | at 2949.12 MHz                                             |      | 17 to 23 |      | IVIIIZ/ V   |

| ΔT <sub>CL</sub>       | Allowable Temperature Drift for Continuous Lock | to output configurat  | or lock, no changes<br>ion are permitted to<br>inuous lock |      |          | 125  | °C          |

|                        |                                                 | Noise Floor           |                                                            |      | -11      |      |             |

|                        |                                                 |                       | LVDS                                                       |      | -156.3   |      |             |

|                        |                                                 |                       | HSDS 6 mA -158.4                                           |      |          |      |             |

|                        |                                                 |                       | HSDS 8 mA                                                  |      | -159.3   |      |             |

|                        | LMK04828, VCO0, Noise Floor                     |                       | HSDS 10 mA                                                 |      | -158.9   | 9    |             |

| L(f) <sub>CLKout</sub> | 20 MHz Offset <sup>(2)</sup>                    | 245.76 MHz            | LVPECL16 /w<br>240 Ω                                       |      | -161.6   |      | dBc/H       |

|                        |                                                 |                       | LVPECL20 /w<br>240 Ω                                       |      | -162.5   |      |             |

|                        |                                                 |                       | LCPECL                                                     |      | -162.1   |      |             |

|                        |                                                 |                       | LVDS                                                       |      | -155.7   |      |             |

|                        |                                                 |                       | HSDS 6 mA                                                  |      | -157.5   |      | °C<br>dBc/H |

|                        |                                                 |                       | HSDS 8 mA                                                  |      | -158.1   |      |             |

| L(f) <sub>CLKout</sub> | LMK04828, VCO1, Noise Floor                     |                       | HSDS 10 mA                                                 |      | -157.7   |      |             |

|                        | 20 MHz Offset <sup>(2)</sup>                    | 245.76 MHz            | LVPECL16 /w<br>240 Ω                                       |      | -160.3   |      | dBc/H       |

|                        |                                                 |                       | LVPECL20 /w<br>240 Ω                                       |      | -161.1   |      |             |

|                        |                                                 |                       | LCPECL                                                     |      | -160.8   |      | 1           |

<sup>(1)</sup> Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the 0x168 register was last programmed with PLL2\_FCAL\_DIS = 0, and still have the part stay in lock. The action of programming the 0x168 register, even to the same value, activates a frequency calibration routine. This implies the part will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reload the appropriate register to ensure it stays in lock. Regardless of what temperature the part was initially programmed at the temperature can never drift outside the frequency range of -40 °C to 85 °C without violating specifications.

<sup>at, the temperature can never drift outside the frequency range of -40 °C to 85 °C without violating specifications.

(2) Data collected using ADT2-1T+ balun. Loop filter is C1 = 47 pF, C2 = 3.9 nF, R2 = 620 Ω, C3 = 10 pF, R3 = 200 Ω, C4 = 10 pF, R4 = 200 Ω, PLL1\_CP = 450 μA, PLL2\_CP = 3.2 mA.. VCO0 loop filter bandwidth = 344 kHz, phase margin = 73 degrees. VCO1 Loop filter loop bandwidth = 233 kHz, phase margin = 70 degrees. CLKoutX\_Y\_IDL = 1, CLKoutX\_Y\_ODL = 0.</sup>

$(3.15 \text{ V} < \text{V}_{CC} < 3.45 \text{ V}, -40 ^{\circ}\text{C} < \text{T}_{A} < 85 ^{\circ}\text{C}$ . Typical values at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at the Recommended Operating Conditions and are **not** assured.)

| Symbol                 | Parameter                                                                                  | Condit                                      | ions                 | Min                | Тур      | Max      | Units              |

|------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------|----------------------|--------------------|----------|----------|--------------------|

|                        | CLKout Closed Loop                                                                         | Jitter Specifications a Co                  | ommercial Quality V  | CXO <sup>(1)</sup> |          |          |                    |

|                        |                                                                                            | Offset = 1 kHz                              |                      |                    | -124.3   |          |                    |

|                        |                                                                                            | Offset =                                    | 10 kHz               |                    | -134.7   |          |                    |

|                        |                                                                                            | Offset = 1                                  | 00 kHz               |                    | -136.5   |          |                    |

| L(f) <sub>CLKout</sub> | LMK04828<br>VCO0                                                                           | Offset =                                    | 1 MHz                |                    | -148.4   |          | dBc/F              |

| L(I)CLKout             | SSB Phase Noise (2)                                                                        |                                             | LVDS                 |                    | -156.4   |          | ubc/n              |

|                        |                                                                                            | Offset = 10 MHz                             | HSDS 8 mA            |                    | -159.1   |          |                    |

|                        |                                                                                            | Onder = 10 Wil 12                           | LVPECL16 /w<br>240 Ω |                    | -160.8   |          |                    |

|                        |                                                                                            | Offset =                                    | 1 kHz                |                    | -124.2   |          |                    |

|                        |                                                                                            | Offset =                                    | 10 kHz               |                    | -134.4   |          |                    |

|                        |                                                                                            | Offset = 1                                  | 00 kHz               |                    | -135.2   |          |                    |

| L(f) <sub>CLKout</sub> | LMK04828<br>VCO1                                                                           | Offset =                                    | 1 MHz                |                    | -151.5   |          | dBc/F              |

| -(I/CLKout             | SSB Phase Noise (2)                                                                        |                                             | LVDS                 |                    | -159.9   |          | - GBC/HZ<br>-<br>- |

|                        |                                                                                            | Offset = 10 MHz                             | HSDS 8 mA            |                    | -155.8   |          |                    |

|                        |                                                                                            | 011361 = 10 WH2                             | LVPECL16 /w<br>240 Ω |                    | -158.1   |          |                    |

|                        |                                                                                            | LVDS, BW = 100                              | Hz to 20 MHz         |                    | 112      |          |                    |

|                        |                                                                                            | LVDS, BW = 12                               | kHz to 20 MHz        |                    | 109      |          |                    |

|                        |                                                                                            | HSDS 8 mA, BW =                             | 100 Hz to 20 MHz     |                    | 102      |          |                    |

|                        |                                                                                            | HSDS 8 mA, BW =                             | 12 kHz to 20 MHz     |                    | 99       |          | fs rms             |

|                        | LMK04828, VCO0<br>f <sub>CLKout</sub> = 245.76 MHz<br>Integrated RMS Jitter <sup>(2)</sup> | LVPECL16<br>BW = 100 Hz                     |                      |                    | 98       |          |                    |

|                        |                                                                                            | LVPECL20 /w 240 Ω,<br>BW = 12 kHz to 20 MHz |                      |                    | 95       |          |                    |

|                        |                                                                                            | LCPECL /\<br>BW = 100 Hz                    | *                    |                    | 96       |          |                    |

|                        |                                                                                            | LCPECL /\<br>BW = 12 kHz                    |                      |                    | 93       |          |                    |

| J <sub>CLKout</sub>    |                                                                                            | LVDS, BW = 100                              | Hz to 20 MHz         |                    | 108      |          |                    |

|                        |                                                                                            | LVDS, BW = 12                               | kHz to 20 MHz        |                    | 105      |          |                    |

|                        |                                                                                            | HSDS 8 mA, BW =                             | 100 Hz to 20 MHz     |                    | 98<br>94 |          |                    |

|                        |                                                                                            | HSDS 8 mA, BW =                             | 12 kHz to 20 MHz     |                    |          | -        |                    |

|                        | LMK04828, VCO1<br>f <sub>CLKout</sub> = 245.76 MHz                                         | LVPECL16<br>BW = 100 Hz                     |                      |                    |          | fs rm    |                    |

|                        | Integrated RMS Jitter (2)                                                                  | LVPECL20<br>BW = 12 kHz                     |                      |                    | 90       | 13 11115 |                    |

|                        |                                                                                            | LCPECL /\ BW = 100 Hz                       | - /                  |                    | 91       |          |                    |

|                        |                                                                                            | LCPECL /\ BW = 12 kHz                       | - /                  |                    | 88       |          |                    |

<sup>(1)</sup> VCXO used is a 122.88 MHz Crystek CVHD-950-122.880.

<sup>(2)</sup> Data collected using ADT2-1T+ balun. Loop filter is C1 = 47 pF, C2 = 3.9 nF, R2 = 620 Ω, C3 = 10 pF, R3 = 200 Ω, C4 = 10 pF, R4 = 200 Ω, PLL1\_CP = 450 μA, PLL2\_CP = 3.2 mA.. VCO0 loop filter bandwidth = 344 kHz, phase margin = 73 degrees. VCO1 Loop filter loop bandwidth = 233 kHz, phase margin = 70 degrees. CLKoutX\_Y\_IDL = 1, CLKoutX\_Y\_ODL = 0.

(3.15 V <  $V_{CC}$  < 3.45 V, -40 °C <  $T_A$  < 85 °C. Typical values at  $V_{CC}$  = 3.3 V,  $T_A$  = 25 °C, at the Recommended Operating Conditions and are **not** assured.)

| Symbol                             | Parameter                                                                                                                                                                                                                  | Conditions                                                               | Min   | Тур  | Max                | Units |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------|------|--------------------|-------|

|                                    | Default Powe                                                                                                                                                                                                               | r On Reset Clock Output Frequency                                        |       |      |                    |       |

| f <sub>CLKout-startup</sub>        | Default output clock frequency at device power on (1)                                                                                                                                                                      |                                                                          |       |      |                    | MHz   |

| f <sub>OSCout</sub>                | OSCout Frequency                                                                                                                                                                                                           |                                                                          |       |      | <sup>(2)</sup> 500 | MHz   |

|                                    |                                                                                                                                                                                                                            | Clock Skew and Delay                                                     |       |      |                    |       |

|                                    | DCLKoutX to SDCLKoutY $F_{CLK} = 245.76$ MHz, $R_L = 100$ $\Omega$ AC coupled $^{(3)}$                                                                                                                                     | Same pair, Same format <sup>(4)</sup> SDCLKoutY_MUX = 0 (Device Clock)   |       |      | 25                 |       |

| T <sub>SKEW</sub>                  | $\label{eq:maximum} \begin{array}{l} \text{Maximum DCLKoutX or SDCLKoutY} \\ \text{to DCLKoutX or SDCLKoutY} \\ \text{$F_{\text{CLK}} = 245.76 \text{ MHz},  R_{\text{L}} = 100  \Omega} \\ \text{AC coupled} \end{array}$ | Any pair, Same format <sup>(4)</sup> SDCLKoutY_MUX = 0 (Device Clock)    |       | 50   |                    | ps    |

| ts <sub>JESD204B</sub>             |                                                                                                                                                                                                                            |                                                                          |       | -80  |                    | ps    |

| f <sub>ADLY</sub> max              | Maximum analog delay frequency                                                                                                                                                                                             | DCLKoutX_MUX = 4                                                         |       | 1536 |                    | MHz   |

|                                    | LVDS Clock Outpu                                                                                                                                                                                                           | its (DCLKoutX, SDCLKoutY, and OSCou                                      | t)    |      |                    |       |

| $V_{OD}$                           | Differential Output Voltage                                                                                                                                                                                                |                                                                          |       | 395  |                    | mV    |

| $\Delta V_{OD}$                    | Change in Magnitude of V <sub>OD</sub> for complementary output states                                                                                                                                                     | T = 25 °C, DC measurement                                                | -60   |      | 60                 | mV    |

| $V_{OS}$                           | Output Offset Voltage                                                                                                                                                                                                      | AC coupled to receiver input $R_1 = 100 \Omega$ differential termination | 1.125 | 1.25 | 1.375              | ٧     |

| $\Delta V_{OS}$                    | Change in V <sub>OS</sub> for complementary output states                                                                                                                                                                  | _                                                                        |       |      | 35                 | mV    |

| т /т                               | Output Rise Time                                                                                                                                                                                                           | 20% to 80%, $R_L$ = 100 Ω, 245.76 MHz                                    |       | 180  |                    | 20    |

| $T_R/T_F$                          | Output Fall Time                                                                                                                                                                                                           | 80% to 20%, $R_L = 100 \Omega$                                           |       | 100  |                    | ps    |

| I <sub>SA</sub><br>I <sub>SB</sub> | Output short circuit current - single ended                                                                                                                                                                                | Single-ended output shorted to GND T = 25 °C                             | -24   |      | 24                 | mA    |

| I <sub>SAB</sub>                   | Output short circuit current - differential                                                                                                                                                                                | Complimentary outputs tied together                                      | -12   |      | 12                 | mA    |

OSCout will oscillate at start-up at the frequency of the VCXO attached to OSCin port. Assured by characterization. ATE tested at 122.88 MHz.

Equal loading and identical clock output configuration on each clock output is required for specification to be valid. Specification not valid for delay mode.

LVPECL uses 120  $\Omega$  emitter resistor, LVDS and HSDS uses 560  $\Omega$  shunt.

| Symbol          | Parameter                                                 | Conditions                                     | Min  | Тур                       | Max | Units |

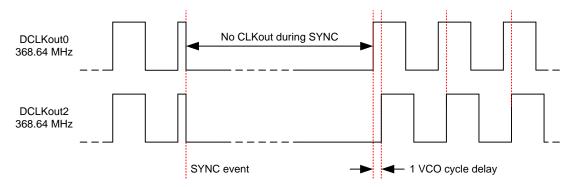

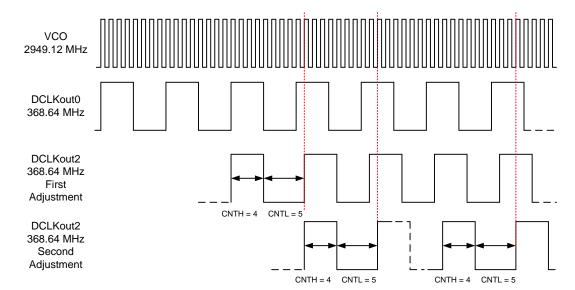

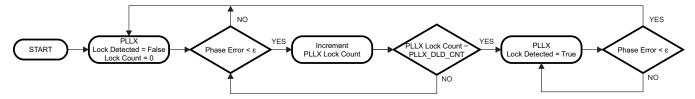

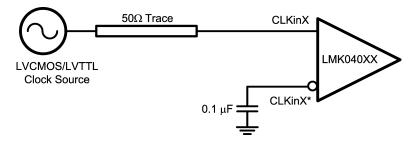

|-----------------|-----------------------------------------------------------|------------------------------------------------|------|---------------------------|-----|-------|