SNLS322E - JUNE 2010-REVISED APRIL 2013

# DS90UB901Q/DS90UB902Q 10 - 43MHz 14 Bit Color FPD-Link III Serializer and Deserializer with Bidirectional Control Channel

Check for Samples: DS90UB901Q, DS90UB902Q

#### **FEATURES**

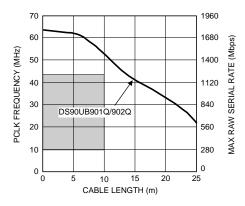

- 10 MHz to 43 MHz Input PCLK Support

- 160 Mbps to 688 Mbps Data Throughput

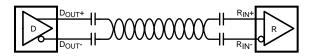

- Single Differential Pair Interconnect

- Bidirectional Control Interface Channel with I<sup>2</sup>C Support

- Embedded Clock with DC Balanced Coding to Support AC-Coupled Interconnects

- Capable to Drive up to 10 Meters Shielded Twisted-Pair

- I<sup>2</sup>C Compatible Serial Interface

- Single Hardware Device Addressing Pin

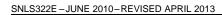

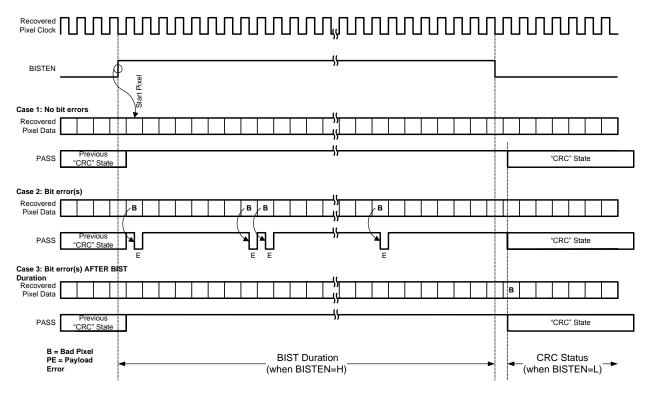

- 16-bit Data Payload with CRC (Cyclic Redundancy Check) for Checking Data Integrity

- Up to 6 Programmable GPIO's

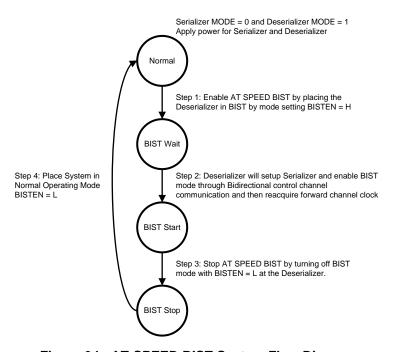

- LOCK Output Reporting Pin and AT-SPEED BIST Diagnosis Feature to Validate Link Integrity

- Integrated Termination Resistors

- 1.8V- or 3.3V-Compatible Parallel Bus Interface

- Single Power Supply at 1.8V

- ISO 10605 ESD and IEC 61000-4-2 ESD Compliant

- Automotive Grade Product: AEC-Q100 Grade 2 Qualified

- Temperature Range -40°C to +105°C

- No Reference Clock Required on Deserializer

- Programmable Receive Equalization

- EMI/EMC Mitigation

- DES Programmable Spread Spectrum (SSCG) Outputs

- DES Receiver Staggered Outputs

#### **APPLICATIONS**

- Automotive Vision Systems

- Rear View, Side View Camera

- Lane Departure Warning

- Parking Assistance

- Blind Spot View

#### DESCRIPTION

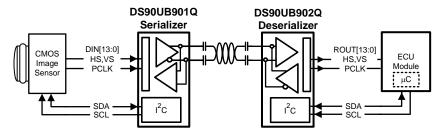

The DS90UB901Q/DS90UB902Q chipset offers a FPD-Link III interface with a high-speed forward channel and a bidirectional control channel for data transmission over a single differential pair. The Serializer/Deserializer pair is targeted for direct connections between automotive camera systems and Host Controller/Electronic Control Unit (ECU). The primary transport sends 16 bits of image data over a single high-speed serial stream together with a low latency bidirectional control channel transport that supports I2C. Included with the 16-bit payload is a selectable data integrity option for CRC (Cyclic Redundancy Check) to monitor transmission link errors. Using TI's embedded clock technology allows transparent full-duplex communication over a single differential pair, carrying asymmetrical bidirectional control information without the dependency of video blanking intervals. This single serial stream simplifies transferring a wide data bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. This significantly saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins.

In addition, the Deserializer inputs provide equalization control to compensate for loss from the media over longer distances. Internal DC balanced encoding/decoding is used to support AC-Coupled interconnects.

A Serializer standby function provides a low powersavings mode with a remote wake up capability for signaling of a remote device.

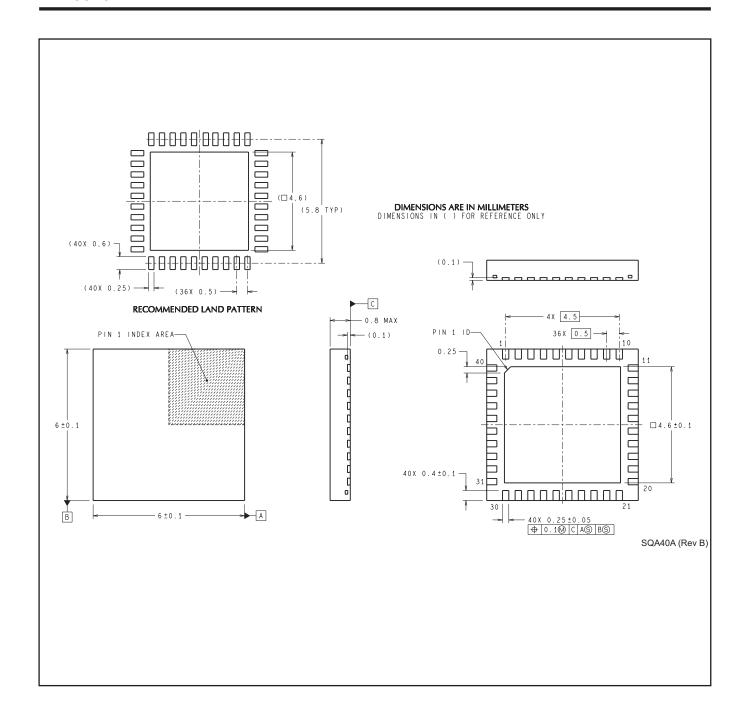

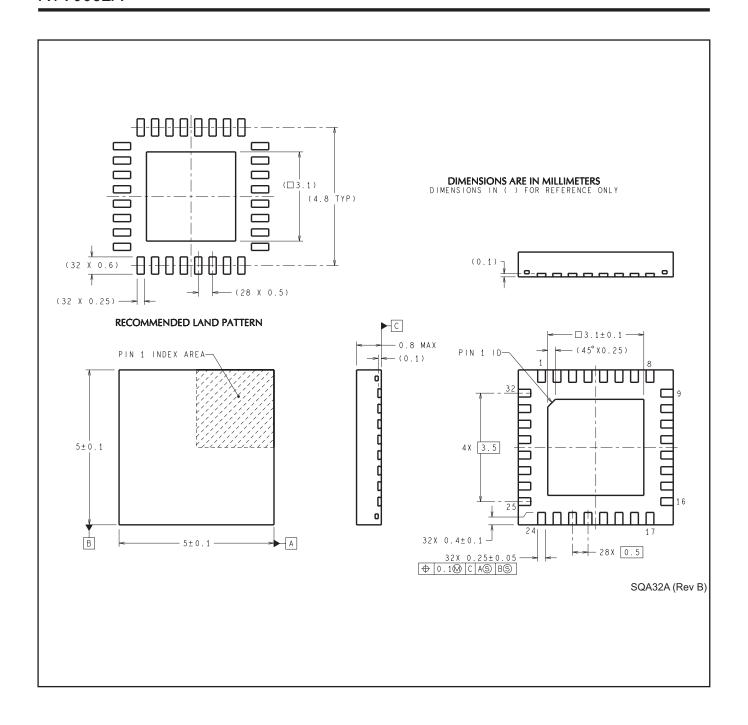

The Serializer is offered in a 32-pin WQFN (5mm x 5mm) package, and Deserializer is offered in a 40-pin WQFN (6mm x 6mm) package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

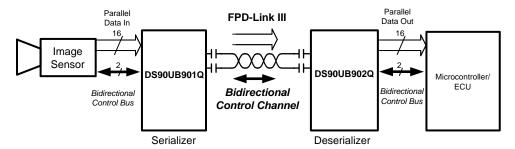

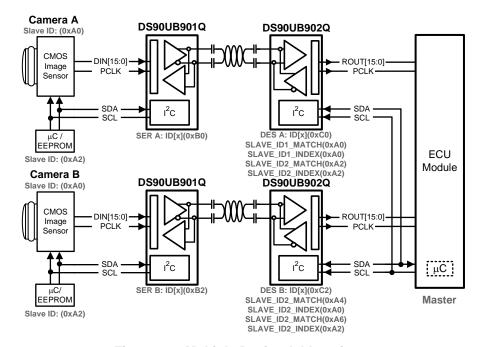

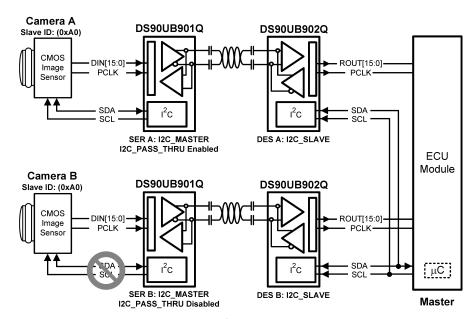

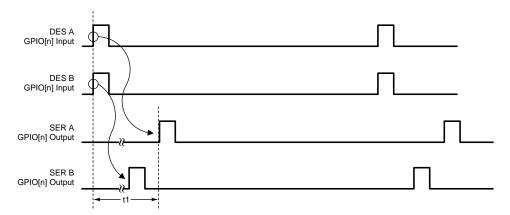

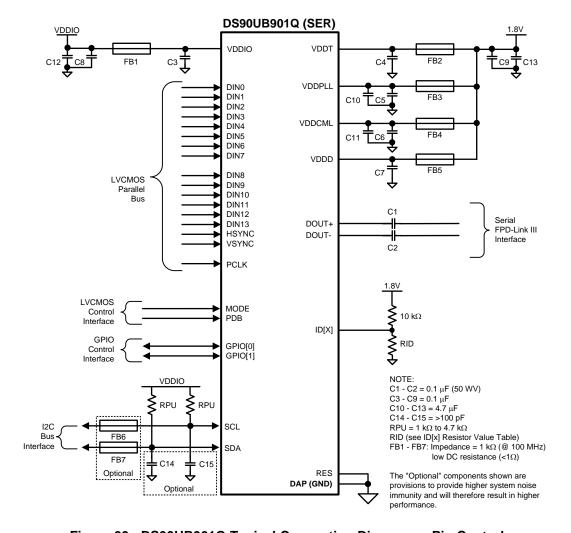

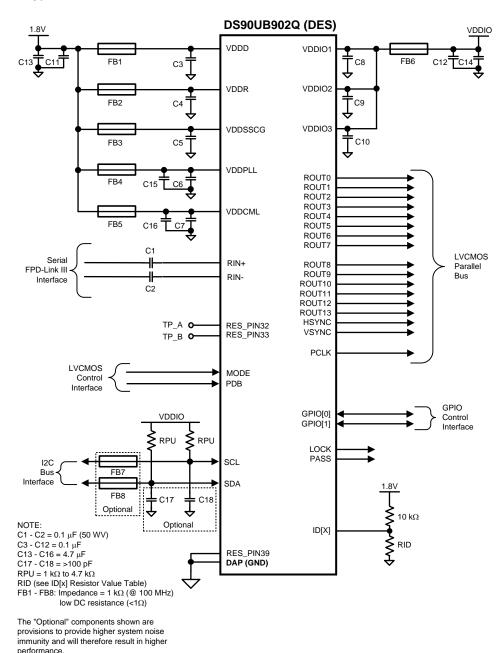

## **Typical Application Diagram**

Figure 1. Typical Application Circuit

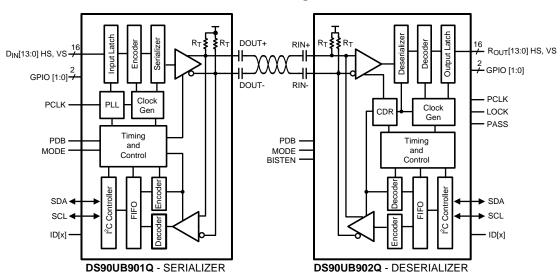

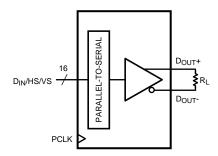

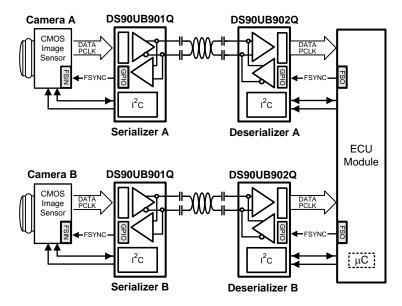

## **Block Diagrams**

Figure 2. Block Diagram

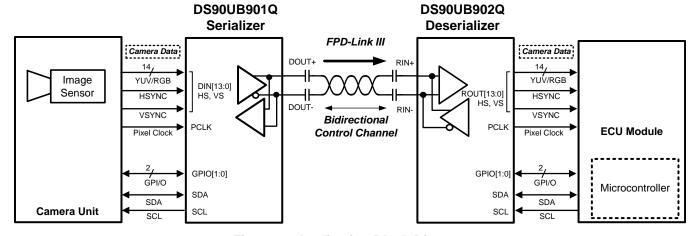

Figure 3. Application Block Diagram

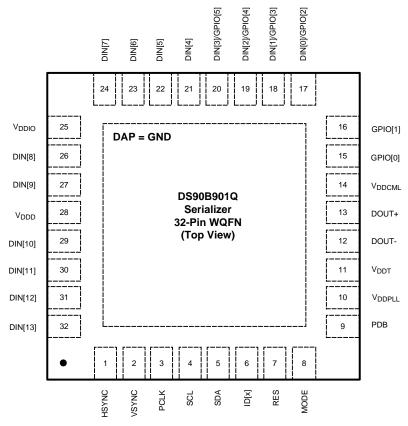

## DS90UB901Q Pin Diagram

Serializer - DS90UB901Q 32 Pin WQFN (Top View) See Package Number RTV0032A

## **DS90UB901Q SERIALIZER PIN DESCRIPTIONS**

| Pin Name               | Pin No.                                                         | I/O, Type                         | Description                                                                                                                                |

|------------------------|-----------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| LVCMOS PARA            | LLEL INTERFAC                                                   | E                                 |                                                                                                                                            |

| DIN[13:0]              | 32, 31, 30, 29,<br>27, 26, 24, 23,<br>22, 21, 20, 19,<br>18, 17 | Inputs,<br>LVCMOS<br>w/ pull down | Parallel data inputs.                                                                                                                      |

| HSYNC                  | 1                                                               | Inputs,<br>LVCMOS<br>w/ pull down | Horizontal SYNC Input                                                                                                                      |

| VSYNC                  | 2                                                               | Inputs,<br>LVCMOS<br>w/ pull down | Vertical SYNC Input                                                                                                                        |

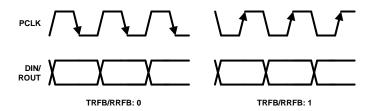

| PCLK                   | 3                                                               | Input, LVCMOS<br>w/ pull down     | Pixel Clock Input Pin. Strobe edge set by TRFB control register.                                                                           |

| GENERAL PUR            | POSE INPUT OU                                                   | TPUT (GPIO)                       |                                                                                                                                            |

| DIN[3:0]/<br>GPIO[5:2] | 20, 19, 18, 17                                                  | Input/Output,<br>LVCMOS           | DIN[3:0] general-purpose pins can be individually configured as either inputs or outputs; used to control and respond to various commands. |

| GPIO[1:0]              | 16, 15                                                          | Input/Output,<br>LVCMOS           | General-purpose pins can be individually configured as either inputs or outputs; used to control and respond to various commands.          |

| BIDIRECTIONAL          | L CONTROL BUS                                                   | - I <sup>2</sup> C COMPATIB       | LE                                                                                                                                         |

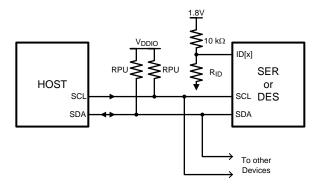

| SCL                    | 4                                                               | Input/Output,<br>Open Drain       | Clock line for the bidirectional control bus communication SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                |

# DS90UB901Q SERIALIZER PIN DESCRIPTIONS (continued)

| Pin Name         | Pin No.     | I/O, Type                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA              | 5           | Input/Output,<br>Open Drain   | Data line for the bidirectional control bus communication SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                                                                                                    |

| MODE             | 8           | Input, LVCMOS<br>w/ pull down | l <sup>2</sup> C Mode select MODE = L, Master mode (default); Device generates and drives the SCL clock line. Device is connected to slave peripheral on the bus. (Serializer initially starts up in Standby mode and is enabled through remote wakeup by Deserializer) MODE = H, Slave mode; Device accepts SCL clock input and attached to an l <sup>2</sup> C controller master on the bus. Slave mode does not generate the SCL clock, but uses the clock generated by the Master for the data transfers. |

| ID[x]            | 6           | Input, analog                 | Device ID Address Select Resistor to Ground and 10 k $\Omega$ pull-up to 1.8V rail. See Table 3                                                                                                                                                                                                                                                                                                                                                                                                               |

| CONTROL AND      | CONFIGURATI | ON                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PDB              | 9           | Input, LVCMOS<br>w/ pull down | Power down Mode Input Pin.  PDB = H, Serializer is enabled and is ON.  PDB = L, Serailizer is in Power Down mode. When the Serializer is in Power Down, the PLL is shutdown, and IDD is minimized. Programmed control register data are NOT retained and reset to default values                                                                                                                                                                                                                              |

| RES              | 7           | Input, LVCMOS<br>w/ pull down | Reserved. This pin MUST be tied LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FPD-LINK III INT | ERFACE      |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DOUT+            | 13          | Input/Output,<br>CML          | Non-inverting differential output, bidirectional control channel input. The interconnect must be AC Coupled with a 100 nF capacitor.                                                                                                                                                                                                                                                                                                                                                                          |

| DOUT-            | 12          | Input/Output,<br>CML          | Inverting differential output, bidirectional control channel input. The interconnect must be AC Coupled with a 100 nF capacitor.                                                                                                                                                                                                                                                                                                                                                                              |

| POWER AND GR     | ROUND       | <u>'</u>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VDDPLL           | 10          | Power, Analog                 | PLL Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDDT             | 11          | Power, Analog                 | Tx Analog Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDDCML           | 14          | Power, Analog                 | CML & Bidirectional Channel Driver Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDDD             | 28          | Power, Digital                | Digital Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDDIO            | 25          | Power, Digital                | Power for I/O stage. The single-ended inputs and SDA, SCL are powered from $V_{DDIO}$ . $V_{DDIO}$ can be connected to a 1.8V ±5% or 3.3V ±10%                                                                                                                                                                                                                                                                                                                                                                |

| VSS              | DAP         | Ground, DAP                   | DAP must be grounded. DAP is the large metal contact at the bottom side, located at the center of the WQFN package. Connected to the ground plane (GND) with at least 9 vias.                                                                                                                                                                                                                                                                                                                                 |

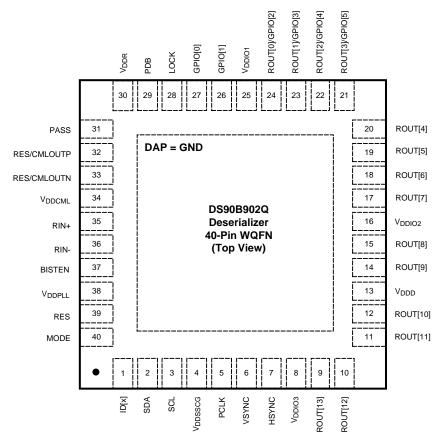

## DS90UB902Q Pin Diagram

Deserializer - DS90UB902Q 40 Pin WQFN (Top View) See Package Number RTA0040A

## **DS90UB902Q DESERIALIZER PIN DESCRIPTIONS**

| Pin Name                 | Pin No.                                                        | I/O, Type                   | Description                                                                                                                                 |

|--------------------------|----------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                |                             | Description                                                                                                                                 |

| LVCMOS PARAI             | LLEL INTERFAC                                                  | E                           |                                                                                                                                             |

| ROUT[13:0]               | 9, 10, 11, 12,<br>14, 15, 17, 18,<br>19, 20, 21, 22,<br>23, 24 | Outputs,<br>LVCMOS          | Parallel data outputs.                                                                                                                      |

| HSYNC                    | 7                                                              | Output,<br>LVCMOS           | Horizontal SYNC Output                                                                                                                      |

| VSYNC                    | 6                                                              | Output,<br>LVCMOS           | Vertical SYNC Output                                                                                                                        |

| PCLK                     | 5                                                              | Output,<br>LVCMOS           | Pixel Clock Output Pin. Strobe edge set by RRFB control register.                                                                           |

| GENERAL PURE             | POSE INPUT OU                                                  | TPUT (GPIO)                 |                                                                                                                                             |

| ROUT[3:0] /<br>GPIO[5:2] | 21, 22, 23, 24                                                 | Input/Output,<br>LVCMOS     | ROUT[3:0] general-purpose pins can be individually configured as either inputs or outputs; used to control and respond to various commands. |

| GPIO[1:0]                | 26, 27                                                         | Input/Output,<br>LVCMOS     | General-purpose pins can be individually configured as either inputs or outputs; used to control and respond to various commands.           |

| BIDIRECTIONAL            | CONTROL BUS                                                    | - I <sup>2</sup> C COMPATIB | LE                                                                                                                                          |

| SCL                      | 3                                                              | Input/Output,<br>Open Drain | Clock line for the bidirectional control bus communication SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                 |

| SDA                      | 2                                                              | Input/Output,<br>Open Drain | Data line for bidirectional control bus communication SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                      |

Copyright © 2010–2013, Texas Instruments Incorporated

# DS90UB902Q DESERIALIZER PIN DESCRIPTIONS (continued)

| Pin Name         | Pin No.       | I/O, Type                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|---------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE             | 40            | Input, LVCMOS<br>w/ pull up   | I <sup>2</sup> C Mode select MODE = L, Master mode; Device generates and drives the SCL clock line, where required such as Read. Device is connected to slave peripheral on the bus. MODE = H, Slave mode (default); Device accepts SCL clock input and attached to an I <sup>2</sup> C controller master on the bus. Slave mode does not generate the SCL clock, but uses the clock generated by the Master for the data transfers. |

| ID[x]            | 1             | Input, analog                 | Device ID Address Select Resistor to Ground and 10 $k\Omega$ pull-up to 1.8V rail. See Table 4                                                                                                                                                                                                                                                                                                                                       |

| CONTROL AND      | CONFIGURATION | ON                            |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PDB              | 29            | Input, LVCMOS<br>w/ pull down | Power down Mode Input Pin.  PDB = H, Deserializer is enabled and is ON.  PDB = L, Deserializer is in Power Down mode. When the Deserializer is in Power Down. Programmed control register data are NOT retained and reset to default values.                                                                                                                                                                                         |

| LOCK             | 28            | Output,<br>LVCMOS             | LOCK Status Output Pin.  LOCK = H, CDR/PLL is Locked, outputs are active  LOCK = L, CDR/PLL is unlocked, the LVCMOS Outputs depend on OSS_SEL control register, the CDR/PLL is shutdown and IDD is minimized. May be used as Link Status.                                                                                                                                                                                            |

| PASS             | 31            | Output,<br>LVCOMS             | When BISTEN = L; Normal operation PASS is high to indicate no errors are detected. The PASS pin asserts low to indicate a CRC error was detected on the Link.                                                                                                                                                                                                                                                                        |

| RES              | 32, 33, 39    | -                             | Reserved Pin 39: This pin MUST be tied LOW. Pins 32,33: Route to test point or leave open if unused. See also FPD-LINK III INTERFACE pin description section.                                                                                                                                                                                                                                                                        |

| BIST MODE        |               |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BISTEN           | 37            | Input, LVCMOS<br>w/ pull down | BIST Enable Pin. BISTEN = H, BIST Mode is enabled. BISTEN = L, BIST Mode is disabled.                                                                                                                                                                                                                                                                                                                                                |

| PASS             | 31            | Output,<br>LVCOMS             | PASS Output Pin for BIST mode. PASS = H, ERROR FREE Transmission PASS = L, one or more errors were detected in the received payload. Leave Open if unused. Route to test point (pad) recommended.                                                                                                                                                                                                                                    |

| FPD-LINK III INT | ERFACE        | 1                             |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RIN+             | 35            | Input/Output,<br>CML          | Non-inverting differential input, bidirectional control channel output. The interconnect must be AC Coupled with a 100 nF capacitor.                                                                                                                                                                                                                                                                                                 |

| RIN-             | 36            | Input/Output,<br>CML          | Inverting differential input, bidirectional control channel output. The interconnect must be AC Coupled with a 100 nF capacitor.                                                                                                                                                                                                                                                                                                     |

| CMLOUTP          | 32            | Output, CML                   | Non-inverting CML Output Monitor point for equalized differential signal. Test port is enabled via control registers.                                                                                                                                                                                                                                                                                                                |

| CMLOUTN          | 33            | Output, CML                   | Inverting CML Output Monitor point for equalized differential signal. Test port is enabled via control registers.                                                                                                                                                                                                                                                                                                                    |

| POWER AND GR     | ROUND         |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDDSSCG          | 4             | Power, Digital                | SSCG Power, 1.8V ±5% Power supply must be connected regardless if SSCG function is in operation.                                                                                                                                                                                                                                                                                                                                     |

| VDDIO1/2/3       | 25, 16, 8     | Power, Digital                | LVTTL I/O Buffer Power, The single-ended outputs and control input are powered from V <sub>DDIO</sub> . V <sub>DDIO</sub> can be connected to a 1.8V ±5% or 3.3V ±10%                                                                                                                                                                                                                                                                |

| VDDD             | 13            | Power, Digital                | Digital Core Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDDR             | 30            | Power, Analog                 | Rx Analog Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDDCML           | 34            | Power, Analog                 | Bidirectional Channel Driver Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                         |

| VDDPLL           | 38            | Power, Analog                 | PLL Power, 1.8V ±5%                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSS              | DAP           | Ground, DAP                   | DAP must be grounded. DAP is the large metal contact at the bottom side, located at the center of the WQFN package. Connected to the ground plane (GND) with at least 16 vias.                                                                                                                                                                                                                                                       |

www.ti.com

# Absolute Maximum Ratings (1)(2)(3)

| Supply Voltage – V <sub>DDn</sub> (1.8V)    |                                          | -0.3V to +2.5V                        |

|---------------------------------------------|------------------------------------------|---------------------------------------|

| Supply Voltage – V <sub>DDIO</sub>          |                                          | -0.3V to +4.0V                        |

| LVCMOS Input Voltage I/O Voltage            |                                          | -0.3V to + (VDDIO + 0.3V)             |

| CML Driver I/O Voltage (V <sub>DD</sub> )   | $-0.3V$ to $+(V_{DD} + 0.3V)$            |                                       |

| CML Receiver I/O Voltage (V <sub>DD</sub> ) | $-0.3V$ to $(V_{DD} + 0.3V)$             |                                       |

| Junction Temperature                        | +150°C                                   |                                       |

| Storage Temperature                         | −65°C to +150°C                          |                                       |

| Maximum Package Power Dissipation Capacity  | Package                                  | 1/θ <sub>JA</sub> °C/W above +25°     |

| Package Derating:                           |                                          |                                       |

| DS001IB004O 22 Lond WOEN                    | $\theta_{JA}$ (based on 9 thermal vias)  | 34.3 °C/W                             |

| DS90UB901Q 32 Lead WQFN                     | $\theta_{JC}$ (based on 9 thermal vias)  | 6.9 °C/W                              |

| DS90UB902Q 40 Lead WQFN                     | $\theta_{JA}$ (based on 16 thermal vias) | 28.0 °C/W                             |

| DS900B902Q 40 Lead WQFN                     | $\theta_{JC}$ (based on 16 thermal vias) | 4.4 °C/W                              |

| ESD Rating (IEC 61000-4-2)                  |                                          | $R_D = 330\Omega, C_S = 150pF$        |

| Air Discharge (DOUT+, DOUT-, RIN+, RIN-)    |                                          | ≥±25 kV                               |

| Contact Discharge (DOUT+, DOUT-, RIN+, RIN- | ·)                                       | ≥±10 kV                               |

| ESD Rating (ISO10605)                       |                                          | $R_D = 330\Omega$ , $C_S = 150/330pF$ |

| ESD Rating (ISO10605)                       |                                          | $R_D = 2K\Omega, C_S = 150/330pF$     |

| Air Discharge (DOUT+, DOUT-, RIN+, RIN-)    |                                          | ≥±15 kV                               |

| Contact Discharge (DOUT+, DOUT-, RIN+, RIN- | r)                                       | ≥±10 kV                               |

| ESD Rating (HBM)                            |                                          | ≥±8 kV                                |

| ESD Rating (CDM)                            |                                          | ≥±1 kV                                |

| ESD Rating (MM)                             | ·                                        | ≥±250 V                               |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional; the device should not be operated beyond such conditions.

# Recommended Operating Conditions<sup>(1)</sup>

|                                                  |                          | Min  | Nom | Max  | Units |

|--------------------------------------------------|--------------------------|------|-----|------|-------|

| Supply Voltage (V <sub>DDn</sub> )               |                          | 1.71 | 1.8 | 1.89 | V     |

| LVCMOS Supply Voltage ( $V_D$ OR                 | DIO)                     | 1.71 | 1.8 | 1.89 | V     |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )       |                          | 3.0  | 3.3 | 3.6  | V     |

|                                                  | V <sub>DDn</sub> (1.8V)  |      |     | 25   | mVp-p |

| Supply Noise                                     | V <sub>DDIO</sub> (1.8V) |      |     |      | mVp-p |

| Supply Noise                                     | V <sub>DDIO</sub> (3.3V) |      |     | 50   | mVp-p |

| Operating Free Air Temperature (T <sub>A</sub> ) |                          | -40  | +25 | +105 | °C    |

| PCLK Clock Frequency                             |                          | 10   |     | 43   | MHz   |

(1) Supply noise testing was done with minimum capacitors (as shown on Figure 39 and Figure 40) on the PCB. A sinusoidal signal is AC coupled to the VDDn (1.8V) supply with amplitude = 25 mVp-p measured at the device VDDn pins. Bit error rate testing of input to the Ser and output of the Des with 10 meter cable shows no error when the noise frequency on the Ser is less than 1 MHz. The Des on the other hand shows no error when the noise frequency is less than 750 kHz.

<sup>(2)</sup> For soldering specifications see product folder at www.ti.com

<sup>(3)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

# Electrical Characteristics (1)(2)(3)

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol           | Parameter                                       | Conditions                                                          |                                     | Min                                              | Тур                               | Max                                              | Units  |

|------------------|-------------------------------------------------|---------------------------------------------------------------------|-------------------------------------|--------------------------------------------------|-----------------------------------|--------------------------------------------------|--------|

| LVCMOS           | S DC SPECIFICATIONS 3.3\                        | / I/O (SER INPUTS, DES C                                            | OUTPUTS, GPIO, CONTR                | OL INPUTS                                        | AND OUTPU                         | ITS)                                             |        |

| V <sub>IH</sub>  | High Level Input Voltage                        | $V_{IN} = 3.0V \text{ to } 3.6V$                                    |                                     | 2.0                                              |                                   | V <sub>IN</sub>                                  | V      |

| $V_{IL}$         | Low Level Input Voltage                         | $V_{IN} = 3.0V \text{ to } 3.6V$                                    |                                     | GND                                              |                                   | 0.8                                              | V      |

| I <sub>IN</sub>  | Input Current                                   | $V_{IN} = 0V \text{ or } 3.6V, V_{IN} = 3.0$                        | 0V to 3.6V                          | -20                                              | ±1                                | +20                                              | μA     |

| $V_{OH}$         | High Level Output Voltage                       | $V_{DDIO}$ = 3.0V to 3.6V, $I_{OH}$                                 | = -4 mA                             | 2.4                                              |                                   | $V_{DDIO}$                                       | V      |

| $V_{OL}$         | Low Level Output Voltage                        | $V_{DDIO} = 3.0V \text{ to } 3.6V, I_{OL} = 0.000 \text{ solution}$ | = +4 mA                             | GND                                              |                                   | 0.4                                              | V      |

| I <sub>OS</sub>  | Output Short Circuit                            | V <sub>OUT</sub> = 0V                                               | Serializer GPIO<br>Outputs          |                                                  | -24                               |                                                  | mA     |

|                  | Current                                         | VOU1 - 0 V                                                          | Deserializer LVCMOS<br>Outputs      |                                                  | -39                               |                                                  | 1117 ( |

| l <sub>OZ</sub>  | TRI-STATE Output<br>Current                     | $PDB = 0V, V_{OUT} = 0V \text{ or } V_{DD}$                         | LVCMOS Outputs                      | -20                                              | ±1                                | +20                                              | μΑ     |

| LVCMOS           | S DC SPECIFICATIONS 1.8\                        | / I/O (SER INPUTS, DES C                                            | OUTPUTS, GPIO, CONTR                | OL INPUTS                                        | AND OUTPU                         | ITS)                                             |        |

| $V_{IH}$         | High Level Input Voltage                        | $V_{IN} = 1.71V \text{ to } 1.89V$                                  | <sub>N</sub> = 1.71V to 1.89V       |                                                  |                                   | V <sub>IN</sub> +0.3                             | V      |

| $V_{IL}$         | Low Level Input Voltage                         | V <sub>IN</sub> = 1.71V to 1.89V                                    |                                     | GND                                              |                                   | 0.35 V <sub>IN</sub>                             | v      |

| I <sub>IN</sub>  | Input Current                                   | $V_{IN} = 0V \text{ or } 1.89V, V_{IN} = 1$                         | .71V to 1.89V                       | -20                                              | ±1                                | +20                                              | μA     |

| $V_{OH}$         | High Level Output Voltage                       | $V_{DDIO} = 1.71V \text{ to } 1.89V,$<br>$I_{OH} = -2 \text{ mA}$   | Serializer GPIO<br>Outputs          | V <sub>DDIO</sub> -                              |                                   | V <sub>DDIO</sub>                                | V      |

|                  | night Level Output Voltage                      | $V_{DDIO} = 1.71V \text{ to } 1.89V,$<br>$I_{OH} = -4 \text{ mA}$   | Deserializer LVCMOS<br>Outputs      | 0.45                                             |                                   |                                                  | V      |

| V <sub>OL</sub>  | Lavelaval Outret Valtage                        | $V_{DDIO} = 1.71V \text{ to } 1.89V,$<br>$I_{OL} = +2 \text{ mA}$   | Serializer GPIO<br>Outputs          | - GND                                            |                                   | 0.45                                             | V      |

|                  | Low Level Output Voltage                        | V <sub>DDIO</sub> = 1.71V to 1.89V,<br>I <sub>OL</sub> = +4 mA      | Deserializer LVCMOS<br>Outputs      | GND                                              |                                   | 0.45                                             | V      |

| I <sub>OS</sub>  | Output Short Circuit                            | V 0V                                                                | Serializer GPIO<br>Outputs          |                                                  | -11                               |                                                  |        |

|                  | Current                                         | V <sub>OUT</sub> = 0V                                               | Deserializer LVCMOS<br>Outputs      |                                                  | -20                               |                                                  | mA mA  |

| l <sub>OZ</sub>  | TRI-STATE Output<br>Current                     | $PDB = 0V, V_{OUT} = 0V \text{ or } V_{DD}$                         | LVCMOS Outputs                      | -20                                              | ±1                                | +20                                              | μΑ     |

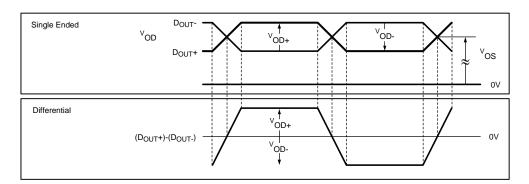

| CML DR           | IVER DC SPECIFICATIONS                          | (DOUT+, DOUT-)                                                      |                                     |                                                  |                                   |                                                  |        |

| V <sub>OD</sub>  | Output Differential Voltage                     | $R_T = 100\Omega$ (Figure 8)                                        |                                     | 268                                              | 340                               | 412                                              | mV     |

| ΔV <sub>OD</sub> | Output Differential Voltage Unbalance           | $R_L = 100\Omega$                                                   |                                     |                                                  | 1                                 | 50                                               | mV     |

| V <sub>OS</sub>  | Output Differential Offset Voltage              | $R_L = 100\Omega$ (Figure 8)                                        |                                     | V <sub>DD (MIN)</sub> -<br>V <sub>OD (MAX)</sub> | V <sub>DD</sub> - V <sub>OD</sub> | V <sub>DD (MAX)</sub> -<br>V <sub>OD (MIN)</sub> | V      |

| ΔV <sub>OS</sub> | Offset Voltage Unbalance                        | $R_L = 100\Omega$                                                   |                                     |                                                  | 1                                 | 50                                               | mV     |

| I <sub>OS</sub>  | Output Short Circuit<br>Current                 | DOUT+/- = 0V,                                                       |                                     |                                                  | -27                               |                                                  | mA     |

| R <sub>T</sub>   | Differential Internal<br>Termination Resistance | Differential across DOUT+                                           | Differential across DOUT+ and DOUT- |                                                  | 100                               | 120                                              | Ω      |

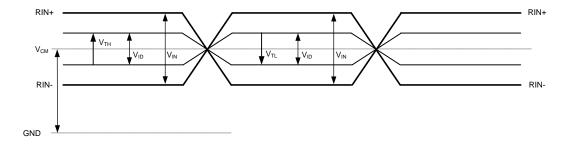

| CML RE           | CEIVER DC SPECIFICATIO                          | NS (RIN+, RIN-)                                                     |                                     |                                                  |                                   |                                                  |        |

| V <sub>TH</sub>  | Differential Threshold High Voltage             | (5)                                                                 |                                     |                                                  |                                   | +90                                              | - 37   |

| V <sub>TL</sub>  | Differential Threshold Low<br>Voltage           | (Figure 10)                                                         |                                     | -90                                              |                                   |                                                  | mV     |

<sup>(1)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

<sup>(2)</sup> Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except VOD, ΔVOD, VTH and VTL which are differential voltages.

<sup>(3)</sup> Typical values represent most likely parametric norms at 1.8V or 3.3V, T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

www.ti.com

# Electrical Characteristics<sup>(1)(2)(3)</sup> (continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol              | Parameter                                           | Condi                                                                                 | itions                                               | Min | Тур  | Max | Units |  |

|---------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------|-----|------|-----|-------|--|

| V <sub>IN</sub>     | Differential Input Voltage<br>Range                 | RIN+ - RIN-                                                                           |                                                      | 180 |      |     | mV    |  |

| I <sub>IN</sub>     | Input Current                                       | $V_{IN} = V_{DD}$ or 0V, $V_{DD} = 1.8$                                               | 89V                                                  | -20 | ±1   | +20 | μA    |  |

| R <sub>T</sub>      | Differential Internal<br>Termination Resistance     | Differential across RIN+ a                                                            | nd RIN-                                              | 80  | 100  | 120 | Ω     |  |

| SER/DE              | S SUPPLY CURRENT *DIG                               | ITAL, PLL, AND ANALOG                                                                 | VDD                                                  |     |      |     |       |  |

| I <sub>DDT</sub>    | Serializer (Tx)                                     | R <sub>T</sub> = 100Ω<br>WORST CASE pattern<br>(Figure 5)                             | VDDn = 1.89V<br>PCLK = 43 MHz                        |     | 62   | 90  | ^     |  |

|                     | VDDn Supply Current (includes load current)         | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                | 55                                                   |     | → mA |     |       |  |

| I <sub>DDIOT</sub>  | Serializer (Tx)                                     | $R_T = 100\Omega$                                                                     | VDDIO = 1.89V<br>PCLK = 43 MHz<br>Default Registers  |     | 2    | 5   | mA    |  |

|                     | VDDIO Supply Current (includes load current)        | WORST CASE pattern (Figure 5)                                                         | VDDIO = 3.6V<br>PCLK = 43 MHz<br>Default Registers   |     | 7    | 15  | IIIA  |  |

| I <sub>DDTZ</sub>   |                                                     | PDB = 0V; All other<br>LVCMOS Inputs = 0V                                             | V <sub>DDn</sub> = 1.89V                             |     | 370  | 775 | μA    |  |

| I <sub>DDIOTZ</sub> | Serializer (Tx) Supply Current Power-down           |                                                                                       | V <sub>DDIO</sub> = 1.89V                            |     | 55   | 125 |       |  |

|                     | Odirent i ower-down                                 | EVOIVIOO Inputs = 0V                                                                  | V <sub>DDIO</sub> = 3.6V                             |     | 65   | 135 |       |  |

| I <sub>DDR</sub>    | Deserializer (Rx) VDDn                              | V <sub>DDn</sub> = 1.89V, C <sub>L</sub> = 8 pF<br>WORST CASE Pattern,<br>(Figure 5)  | PCLK = 43 MHz<br>SSCG[3:0] = ON<br>Default Registers |     | 60   | 96  |       |  |

|                     | Supply Current (includes load current)              | V <sub>DDn</sub> = 1.89V, C <sub>L</sub> = 8 pF<br>RANDOM PRBS-7<br>Pattern           | PCLK = 43 MHz<br>Default Registers                   |     | 53   |     | mA    |  |

| I <sub>DDIOR</sub>  | Deserializer (Rx) VDDIO<br>Supply Current (includes | V <sub>DDIO</sub> = 1.89V, C <sub>L</sub> = 8 pF<br>WORST CASE Pattern,<br>(Figure 5) | PCLK = 43 MHz<br>Default Registers                   |     | 16   | 25  |       |  |

|                     | load current)                                       | V <sub>DDIO</sub> = 3.6V, C <sub>L</sub> = 8 pF<br>WORST CASE Pattern                 | PCLK = 43 MHz<br>Default Registers                   |     | 38   | 64  | †     |  |

| I <sub>DDRZ</sub>   |                                                     |                                                                                       | V <sub>DDn</sub> = 1.89V                             |     | 42   | 400 |       |  |

| I <sub>DDIORZ</sub> | Deserializer (Rx) Supply Current Power-down         | PDB = 0V; All other<br>LVCMOS Inputs = 0V                                             | V <sub>DDIO</sub> = 1.89V                            |     | 8    | 40  | μА    |  |

|                     | 2 2 2 2 2                                           |                                                                                       | $V_{DDIO} = 3.6V$                                    |     | 350  | 800 |       |  |

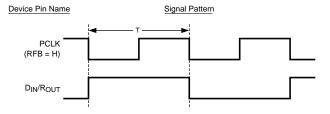

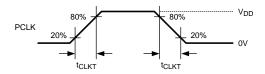

## Recommended Serializer Timing for PCLK(1)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                              | Conditions      | Min  | Тур  | Max  | Units |

|-------------------|----------------------------------------|-----------------|------|------|------|-------|

| t <sub>TCP</sub>  | Transmit Clock Period                  | 10 MHz – 43 MHz | 23.3 | Т    | 100  | ns    |

| t <sub>TCIH</sub> | Transmit Clock Input High Time         |                 | 0.4T | 0.5T | 0.6T | ns    |

| t <sub>TCIL</sub> | Transmit Clock Input Low Time          |                 | 0.4T | 0.5T | 0.6T | ns    |

| t <sub>CLKT</sub> | PCLK Input Transition Time (Figure 11) |                 | 0.5  |      | 3    | ns    |

| f <sub>OSC</sub>  | Internal oscillator clock source       |                 |      | 25   |      | MHz   |

<sup>(1)</sup> Recommended Input Timing Requirements are input specifications and not tested in production.

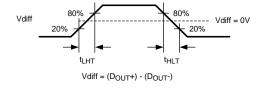

## **Serializer Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                                  | Conditions                                                                                                                                                                                                       | Min        | Тур         | Max              | Units |

|-------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------------|-------|

| t <sub>LHT</sub>  | CML Low-to-High Transition Time                            | $R_L = 100\Omega$ (Figure 6)                                                                                                                                                                                     |            | 150         | 330              | ps    |

| t <sub>HLT</sub>  | CML High-to-Low Transition Time                            | $R_L = 100\Omega$ (Figure 6)                                                                                                                                                                                     |            | 150         | 330              | ps    |

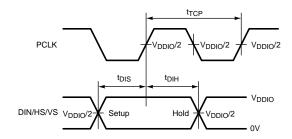

| t <sub>DIS</sub>  | Data Input Setup to PCLK                                   | Coriolizar Data Inputa (Figure 42)                                                                                                                                                                               | 2.0        |             |                  | ns    |

| t <sub>DIH</sub>  | Data Input Hold from PCLK                                  | Serializer Data Inputs (Figure 12)                                                                                                                                                                               | 2.0        |             |                  | ns    |

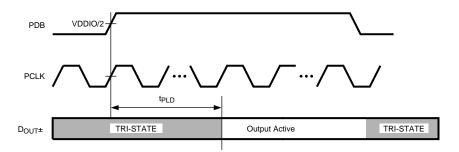

| t <sub>PLD</sub>  | Serializer PLL Lock Time                                   | $R_L = 100\Omega^{(1)(2)}$                                                                                                                                                                                       |            | 1           | 2                | ms    |

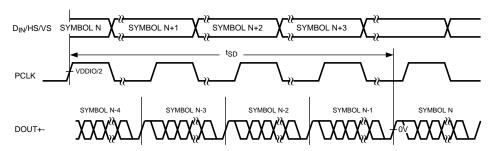

| t <sub>SD</sub>   | Serializer Delay                                           | $R_T = 100\Omega$ , PCLK = 10–43 MHz<br>Register 0x03h b[0] (TRFB = 1)<br>(Figure 14)                                                                                                                            | 6.386T + 5 | 6.386T + 12 | 6.386T +<br>19.7 | ns    |

| t <sub>JIND</sub> | Serializer Output Deterministic<br>Jitter                  | Serializer output<br>intrinsic deterministic jitter .<br>Measured (cycle-cycle) with<br>PRBS-7 test pattern<br>PCLK = 43 MHz <sup>(3)(4)</sup>                                                                   |            | 0.13        |                  | UI    |

| t <sub>JINR</sub> | Serializer Output Random<br>Jitter                         | Serializer output intrinsic random jitter (cycle-cycle). Alternating-1,0 pattern.  PCLK = 43 MHz <sup>(3)(4)</sup>                                                                                               |            | 0.04        |                  | UI    |

| t <sub>JINT</sub> | Peak-to-peak Serializer Output<br>Jitter                   | Serializer output peak-to-peak jitter includes deterministic jitter, random jitter, and jitter transfer from serializer input. Measured (cycle-cycle) with PRBS-7 test pattern.  PCLK = 43 MHz <sup>(3)(4)</sup> |            | 0.396       |                  | UI    |

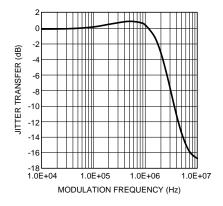

| $\lambda_{STXBW}$ | Serializer Jitter Transfer<br>Function -3 dB Bandwidth     | PCLK = 43 MHz, Default Registers (Figure 20) <sup>(3)</sup>                                                                                                                                                      |            | 1.90        |                  | MHz   |

| $\delta_{STX}$    | Serializer Jitter Transfer<br>Function (Peaking)           | PCLK = 43 MHz, Default Registers (Figure 20) <sup>(3)</sup>                                                                                                                                                      |            | 0.944       |                  | dB    |

| $\delta_{STXf}$   | Serializer Jitter Transfer<br>Function (Peaking Frequency) | PCLK = 43 MHz, Default Registers (Figure 20) <sup>(3)</sup>                                                                                                                                                      |            | 500         |                  | kHz   |

<sup>(1)</sup> t<sub>PLD</sub> and t<sub>DDLT</sub> is the time required by the serializer and deserializer to obtain lock when exiting power-down state with an active PCLK

<sup>(2)</sup> Specification is by design.

<sup>(3)</sup> Typical values represent most likely parametric norms at 1.8V or 3.3V, T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

<sup>(4)</sup> UI – Unit Interval is equivalent to one ideal serialized data bit width. The UI scales with PCLK frequency.

## **Deserializer Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                        | Conditions                                                                               | Pin/Freq.                   | Min           | Тур                | Max            | Units |

|-------------------|--------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|---------------|--------------------|----------------|-------|

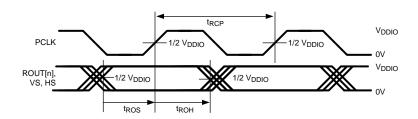

| t <sub>RCP</sub>  | Receiver Output Clock Period                     | $t_{RCP} = t_{TCP}$                                                                      | PCLK                        | 23.3          | Т                  | 100            | ns    |

| t <sub>PDC</sub>  | PCLK Duty Cycle                                  | Default Registers<br>SSCG[3:0] = OFF                                                     | PCLK                        | 45            | 50                 | 55             | %     |

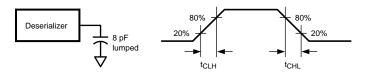

| t <sub>CLH</sub>  | LVCMOS Low-to-High Transition Time               | V <sub>DDIO</sub> : 1.71V to 1.89V or 3.0V to 3.6V,                                      |                             | 1.3           | 2.0                | 2.8            |       |

| t <sub>CHL</sub>  | LVCMOS High-to-Low Transition Time               | C <sub>L</sub> = 8 pF (lumped load)<br>Default Registers<br>(Figure 16) <sup>(1)</sup>   | PCLK                        | 1.3           | 2.0                | 2.8            | ns    |

| t <sub>CLH</sub>  | LVCMOS Low-to-High Transition Time               |                                                                                          | ROUT[13:0],                 | 1.6           | 2.4                | 3.3            |       |

| t <sub>CHL</sub>  | LVCMOS High-to-Low Transition Time               |                                                                                          | HSYNC, VSYNC                | 1.6           | 2.4                | 3.3            | ns    |

| t <sub>ROS</sub>  | ROUT Setup Data to PCLK                          | V <sub>DDIO</sub> : 1.71V to 1.89V or                                                    |                             | 0.38T         | 0.5T               |                |       |

| t <sub>ROH</sub>  | ROUT Hold Data to PCLK                           | 3.0V to 3.6V,<br>C <sub>L</sub> = 8 pF (lumped load)<br>Default Registers<br>(Figure 18) | ROUT[13:0],<br>HSYNC, VSYNC | 0.38T         | 0.5T               |                | ns    |

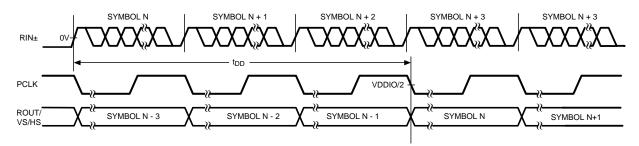

| t <sub>DD</sub>   | Deserializer Delay                               | Default Registers<br>Register 0x03h b[0]<br>(RRFB = 1) (Figure 17)                       | 10 MHz-43 MHz               | 4.571T<br>+ 8 | 4.571T<br>+ 12     | 4.571T<br>+ 16 | ns    |

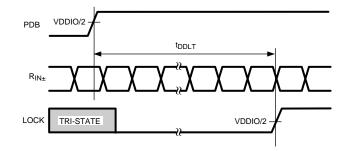

| t <sub>DDLT</sub> | Deserializer Data Lock Time                      | (Figure 15) <sup>(2)</sup>                                                               | 10 MHz-43 MHz               |               |                    | 10             | ms    |

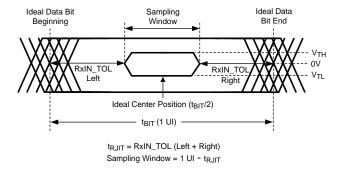

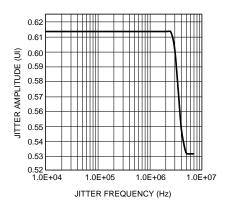

| t <sub>RJIT</sub> | Receiver Input Jitter Tolerance                  | (Figure 19,<br>Figure 21) <sup>(3)(4)</sup>                                              | 43 MHz                      |               | 0.53               |                | UI    |

| t <sub>RCJ</sub>  | Receiver Clock Jitter                            | PCLK                                                                                     | 10 MHz                      |               | 300                | 550            | 2     |

|                   | Receiver Clock Jitter                            | $SSCG[3:0] = OFF^{(1)(5)}$                                                               | 43 MHz                      |               | 120                | 250            | ps    |

| $t_{DPJ}$         | Deserializer Period Jitter                       | PCLK                                                                                     | 10 MHz                      |               | 425                | 600            | nc    |

|                   | Deserranzer Ferrou Sitter                        | $SSCG[3:0] = OFF^{(1)(6)}$                                                               | 43 MHz                      |               | 320                | 480            | ps    |

| $t_{DCCJ}$        | Deserializer Cycle-to-Cycle Clock                | PCLK                                                                                     | 10 MHz                      |               | 320                | 500            | ps    |

|                   | Jitter                                           | $SSCG[3:0] = OFF^{(7)(1)}$                                                               | 43 MHz                      |               | 300                | 500            | ρs    |

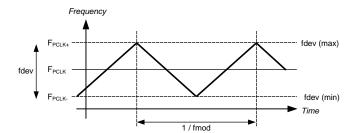

| fdev              | Spread Spectrum Clocking<br>Deviation Frequency  | LVCMOS Output Bus<br>SSC[3:0] = ON                                                       | 20 MHz-43 MHz               |               | ±0.5% to ±2.0%     |                | %     |

| fmod              | Spread Spectrum Clocking<br>Modulation Frequency | (Figure 22)                                                                              | 20 MHz-43 MHz               |               | 9 kHz to<br>66 kHz |                | kHz   |

Specification is by characterization and is not tested in production.

t<sub>PLD</sub> and t<sub>DDLT</sub> is the time required by the serializer and deserializer to obtain lock when exiting power-down state with an active PCLK

UI - Unit Interval is equivalent to one ideal serialized data bit width. The UI scales with PCLK frequency.

$t_{RJ|T}$  max (0.61UI) is limited by instrumentation and actual  $t_{RJ|T}$  of in-band jitter at low frequency (<2 MHz) is greater 1 UI.  $t_{DCJ}$  is the maximum amount of jitter measured over 30,000 samples based on Time Interval Error (TIE).  $t_{DPJ}$  is the maximum amount the period is allowed to deviate measured over 30,000 samples.

t<sub>DCCJ</sub> is the maximum amount of jitter between adjacent clock cycles measured over 30,000 samples.

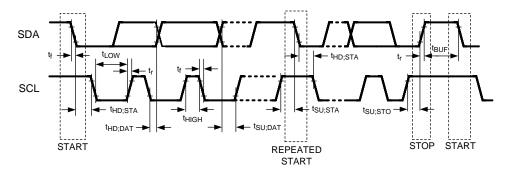

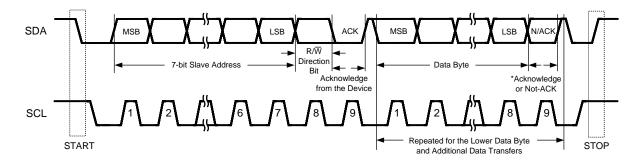

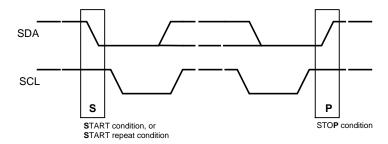

# Bidirectional Control Bus AC Timing Specifications (SCL, SDA) - I<sup>2</sup>C Compliant

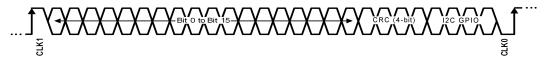

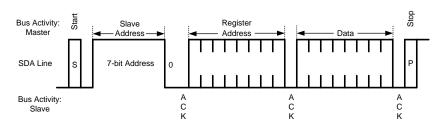

Over recommended supply and temperature ranges unless otherwise specified. See Figure 4.

| Symbol               | Parameter                                             | Conditions                                          | Min | Тур | Max  | Units |

|----------------------|-------------------------------------------------------|-----------------------------------------------------|-----|-----|------|-------|

| RECOMM               | ENDED INPUT TIMING REQUIREMENTS                       | (1)                                                 | 1   | •   |      | •     |

| f <sub>SCL</sub>     | SCL Clock Frequency                                   |                                                     | >0  |     | 100  | kHz   |

| $t_{LOW}$            | SCL Low Period                                        |                                                     | 4.7 |     |      | μs    |

| t <sub>HIGH</sub>    | SCL High Period                                       |                                                     | 4.0 |     |      | μs    |

| t <sub>HD:STA</sub>  | Hold time for a start or a repeated start condition   |                                                     | 4.0 |     |      | μs    |

| t <sub>SU:STA</sub>  | Set Up time for a start or a repeated start condition |                                                     | 4.7 |     |      | μs    |

| t <sub>HD:DAT</sub>  | Data Hold Time                                        | f <sub>SCL</sub> = 100 kHz                          | 0   |     | 3.45 | μs    |

| t <sub>SU:DAT</sub>  | Data Set Up Time                                      |                                                     | 250 |     |      | ns    |

| t <sub>SU:STO</sub>  | Set Up Time for STOP Condition                        |                                                     | 4.0 |     |      | μs    |

| t <sub>r</sub>       | SCL & SDA Rise Time                                   |                                                     |     |     | 1000 | ns    |

| t <sub>f</sub>       | SCL & SDA Fall Time                                   |                                                     |     |     | 300  | ns    |

| C <sub>b</sub>       | Capacitive load for bus                               |                                                     |     |     | 400  | pF    |

| SWITCHIN             | NG CHARACTERISTICS <sup>(2)</sup>                     |                                                     | 11. | 1   | 1    |       |

| ,                    | SCL Clock Frequency                                   |                                                     |     | 100 | 100  | - kHz |

| f <sub>SCL</sub>     |                                                       |                                                     |     | 100 |      |       |

|                      | SCL Low Period                                        |                                                     | 4.7 |     |      |       |

| t <sub>LOW</sub>     | SCL LOW Period                                        |                                                     | 4.7 |     |      | μs    |

| <b>t</b>             | SCL High Period                                       |                                                     | 4.0 |     |      | μs    |

| t <sub>HIGH</sub>    | OCE Trigit T enou                                     |                                                     | 4.0 |     |      | μδ    |

| t <sub>HD:STA</sub>  | Hold time for a start or a repeated start condition   |                                                     | 4.0 |     |      | μs    |

| t <sub>SU:STA</sub>  | Set Up time for a start or a repeated start condition |                                                     | 4.7 |     |      | μs    |

| t <sub>HD:DAT</sub>  | Data Hold Time                                        |                                                     | 0   |     | 3.45 | μs    |

| t <sub>SU:DAT</sub>  | Data Set Up Time                                      |                                                     | 250 |     |      | ns    |

| t <sub>SU:STO</sub>  | Set Up Time for STOP Condition                        | Serializer MODE = 0                                 | 4.0 |     |      | μs    |

| t <sub>f</sub>       | SCL & SDA Fall Time                                   |                                                     |     |     | 300  | ns    |

| t <sub>BUF</sub>     | Bus free time between a stop and start condition      | Serializer MODE = 0                                 | 4.7 |     |      | μs    |

|                      |                                                       | Serializer MODE = 1                                 |     | 1   |      |       |

| t <sub>TIMEOUT</sub> | NACK Time out                                         | Deserializer MODE = 1<br>Register 0x06 b[2:0]=111'b |     | 25  |      | ms    |

<sup>1)</sup> Recommended Input Timing Requirements are input specifications and not tested in production.

<sup>(2)</sup> Specification is by design.

Figure 4. Bidirectional Control Bus Timing

## Bidirectional Control Bus DC Characteristics (SCL, SDA) - I<sup>2</sup>C Compliant

Over recommended supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                | Conditions                                                  | Min                        | Тур | Max                        | Units |

|-----------------|--------------------------|-------------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| V <sub>IH</sub> | Input High Level         | SDA and SCL                                                 | 0.7 x<br>V <sub>DDIO</sub> |     | V <sub>DDIO</sub>          | V     |

| $V_{IL}$        | Input Low Level Voltage  | SDA and SCL                                                 | GND                        |     | 0.3 x<br>V <sub>DDIO</sub> | V     |

| V <sub>HY</sub> | Input Hysteresis         | SDA and SCL                                                 |                            | >50 |                            | mV    |

| I <sub>OZ</sub> | TRI-STATE Output Current | PDB = 0V, $V_{OUT} = 0V$ or $V_{DD}$                        | -20                        | ±1  | +20                        | μΑ    |

| I <sub>IN</sub> | Input Current            | SDA or SCL,<br>Vin = V <sub>DDIO</sub> or GND               | -20                        | ±1  | +20                        | μΑ    |

| C <sub>IN</sub> | Input Pin Capacitance    |                                                             |                            | <5  |                            | pF    |

| V <sub>OL</sub> | Low Lovel Output Voltage | SCL and SDA, $V_{DDIO} = 3.0V$<br>$I_{OL} = 1.5 \text{ mA}$ |                            |     | 0.36                       | V     |

|                 | Low Level Output Voltage | SCL and SDA, $V_{DDIO} = 1.71V$<br>$I_{OL} = 1 \text{ mA}$  |                            |     | 0.36                       | V     |

## **AC Timing Diagrams and Test Circuits**

Figure 5. "Worst Case" Test Pattern

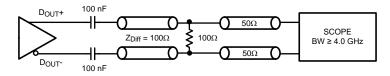

Figure 6. Serializer CML Output Load and Transition Times

Figure 7. Serializer CML Output Load and Transition Times

Figure 8. Serializer VOD DC Diagram

Figure 9. Serializer VOD DC Diagram

Figure 10. Differential VTH/VTL Definition Diagram

Figure 11. Serializer Input Clock Transition Times

Figure 12. Serializer Setup/Hold Times

Figure 13. Serializer Data Lock Time

Figure 14. Serializer Delay

Figure 15. Deserializer Data Lock Time

Figure 16. Deserializer LVCMOS Output Load and Transition Times

Figure 17. Deserializer Delay

Figure 18. Deserializer Output Setup/Hold Times

Figure 19. Receiver Input Jitter Tolerance

Figure 20. Typical Serializer Jitter Transfer Function Curve at 43 MHz

Figure 21. Typical Deserializer Input Jitter Tolerance Curve at 43 MHz

Figure 22. Spread Spectrum Clock Output Profile

# Table 1. DS90UB901Q Control Registers

| Addr<br>(Hex) | Name                          | Bits | Field                             | R/W             | Default         | Description                                                                                                                                                                                                                  |  |

|---------------|-------------------------------|------|-----------------------------------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               | I <sup>2</sup> C Device ID    | 7:1  | DEVICE ID                         | DW              | O. DOIL         | 7-bit address of Serializer; 0x58'h (1011_000X'b) default                                                                                                                                                                    |  |