OBSOLETE

LM1279

www.ti.com

SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

# LM1279 110 MHz RGB Video Amplifier System with OSD

Check for Samples: LM1279

### **FEATURES**

- Three Wideband Video Amplifiers 110 MHz @ -3dB (4 V<sub>PP</sub> Output)

- **OSD Signal to Any OSD Input Pin** Automatically Switches All 3 Outputs to the OSD Mode

- Fast OSD Switching Time, Typically 5 ns

- 3.5 kV ESD Protection

- Fixed Cutoff Level Typically Set to 1.35V

- 0V to 4V, High Impedance DC Contrast Control with Over 40 dB Range

- 0V to 4V, High Impedance DC Drive Control (0 dB to -12 dB Range)

- Matched (±0.3 dB or 3.5%) Attenuators for **Contrast Control**

- **Output Stage Directly Drives CRT Drivers**

- Ideal Combination with LM2407 CRT Driver

### APPLICATIONS

- **High Resolution RGB CRT Monitors**

- Video AGC Amplifiers

- Wideband Amplifiers with Contrast and Drive Controls

- Interface Amplifiers for LCD or CCD Systems

### DESCRIPTION

The LM1279 is a full featured and low cost video amplifier with OSD (On Screen Display). 8V operation for low power and increased reliability. Supplied in a 20-pin DIP package, accommodating very compact designs of the video channel requiring OSD. All video functions controlled by 0V to 4V high impedance DC inputs. This provides easy interfacing to 5V DACs used in computer controlled systems and digital alignment systems. Unique OSD switching, no OSD switching signal required. An OSD signal at any OSD input typically switches the LM1279 to the OSD mode within 5 ns. Ideal video amplifier for the low cost OSD monitor with resolutions up to 1280 x 1024. The LM1279 provides superior protection against ESD. Excellent alternative for the MC13282 in new designs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

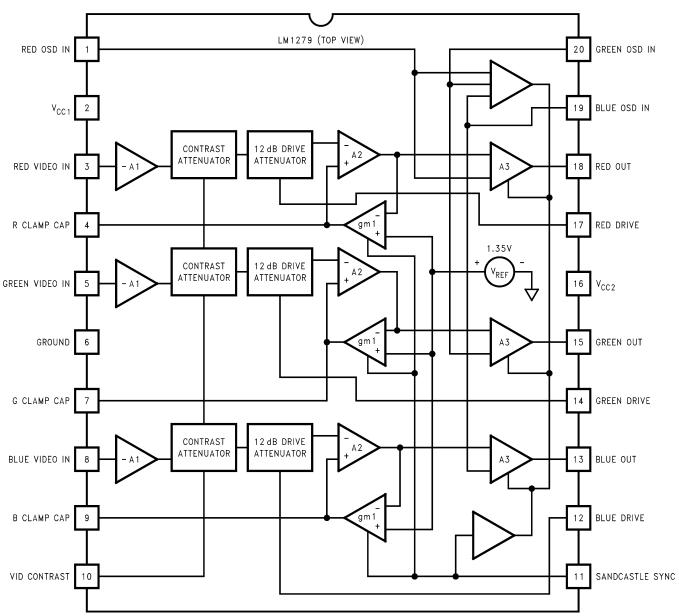

Figure 1. See Package PDIP (NFH)

SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

| Supply Voltage Pins 2 and 16 <sup>(3)</sup>     |                                                    | 10V                         |

|-------------------------------------------------|----------------------------------------------------|-----------------------------|

| Peak Video Output Source Current                | Any One Amp Pins 13, 15, or 18                     | 28 mA                       |

| Voltage at Any Input Pin (VIN)                  |                                                    | $V_{CC} \ge V_{IN} \ge GND$ |

| Power Dissipation (P <sub>D</sub> )             | Above 25°C Derate Based on $\theta_{JA}$ and $T_J$ | 2.1W                        |

| Thermal Resistance to Ambient ( $\theta_{JA}$ ) |                                                    | 60°C/W                      |

| Thermal Resistance to Case $(\theta_{JA})$      | 37°C/W                                             |                             |

| Junction Temperature (T <sub>J</sub> )          |                                                    | 150°C                       |

| ESD Susceptibility <sup>(4)</sup>               |                                                    | 3.5 kV                      |

| ESD Machine Model <sup>(5)</sup>                |                                                    | 300V                        |

| Storage Temperature                             |                                                    | −65°C to 150°C              |

| Lead Temperature Soldering, 10 sec              |                                                    | 265°C                       |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) V<sub>CC</sub> supply pins 2 and 16 must be externally wired together to prevent internal damage during V<sub>CC</sub> power on/off cycles.

(4) Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

(5) Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200 pF cap is charged to the specified voltage, then discharged directly into the IC with no external series resistor (resistance of discharge path must be under 50Ω).

### **OPERATING RATINGS**<sup>(1)</sup>

| Temperature Range                 | 0°C to 70°C                                                |

|-----------------------------------|------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> ) | $7.5 \text{V} \leq \text{V}_{\text{CC}} \leq 8.5 \text{V}$ |

(1) Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the ELECTRICAL CHARACTERISTICS. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

www.ti.com

### DC ELECTRICAL CHARACTERISTICS

$T_{A} = 25^{\circ}C; V_{CC1} = V_{CC2} = 8V; V_{10} = 4V; V_{Drive} = 4V; V_{11} = 7V; V_{OSD} = 0V; R_{L} = 390\Omega \text{ unless otherwise stated.}$

| Symbol                           | Parameter                                        | Condition                                      | Typical <sup>(1)</sup> | Limit <sup>(2)</sup> | Units    |

|----------------------------------|--------------------------------------------------|------------------------------------------------|------------------------|----------------------|----------|

| I <sub>S</sub>                   | Supply Current                                   | $I_{CC1} + I_{CC2} - I_{Load}^{(3)}$           | 80                     | 90                   | mA(max)  |

| V <sub>3, 5, 8</sub>             | Video Amplifier Input Bias Voltage               |                                                | 2.5                    |                      | V        |

| R <sub>IN</sub>                  | Video Input Resistance                           | Any One Amplifier                              | 20                     |                      | kΩ       |

| V <sub>11off</sub>               | Sandcastle Off Voltage                           |                                                | 1.4                    | 1.2                  | V (max)  |

| V <sub>11blank</sub>             | Sandcastle Blank Voltage                         | Start of Blank Region                          | 1.4                    | 1.7                  | V (min)  |

| V <sub>11blank</sub>             | Sandcastle Blank Voltage                         | End of Blank Region                            | 2.8                    | 3.2                  | V (max)  |

| V <sub>11clamp &amp; Blank</sub> | Sandcastle Clamp and Blank On Voltage            | Start of Clamp and Blank Region                | 3.2                    | 3.6                  | V (min)  |

| V <sub>11clamp &amp; Blank</sub> | Sandcastle Clamp and Blank On Voltage            | End of Clamp and Blank Region                  | 6.2                    | 5.8                  | V (max)  |

| V <sub>11clamp</sub>             | Sandcastle Clamp On/Blank Off Voltage            | Clamp Only Region, Max = $V_{CC}$              | 6.2                    | 6.5                  | V (min)  |

| I <sub>110ff</sub>               | Sandcastle Off Current                           | V <sub>11</sub> = 0V                           | -5.0                   | -8.0                 | µA(max)  |

| I <sub>11test</sub>              | Sandcastle Clamp On/Blank Off Curr               | V <sub>11</sub> = 6.5V                         | -100                   | -500                 | nA(max)  |

| I <sub>clamp</sub>               | Clamp Cap Charge Current                         | Clamp Comparators On                           | ±750                   | ±500                 | μA(min)  |

| I <sub>bias</sub>                | Clamp Cap Bias Discharge Current                 | Clamp Comparators Off                          | 50                     | 200                  | nA (max) |

| V <sub>OL</sub>                  | Video Black Level                                | $V_{Video in} = 0V, V_{11} = 6.5V$             | 1.35                   | 1.55                 | V (max)  |

| ΔV <sub>OL</sub>                 | Video ∆Black Level Output Voltage <sup>(4)</sup> | Between Any Two Amplifiers                     | ±50                    | ±200                 | mV (max) |

| V <sub>OH</sub>                  | Video Output High Voltage                        | V <sub>11</sub> < 1.2V                         | 5.0                    | 4.6                  | V (min)  |

| I <sub>10, 12, 14, 17</sub>      | Contrast/Drive Control Input Current             | $V_{Contrast} = V_{Drive} = 0V \text{ to } 4V$ | -0.25                  | -1.5                 | µA (max) |

| I <sub>11, 191, 201</sub>        | OSD Low Input Current (each)                     | V <sub>OSD in</sub> = 0V                       | -2.5                   | -10.0                | µA(max)  |

| I <sub>1h, 19h, 20h</sub>        | OSD High Input Current (each)                    | V <sub>OSD in</sub> = 5V                       | 100                    | 130                  | µA(max)  |

| V <sub>OL</sub> (Blank)          | Video Output during Blanking                     | V <sub>11</sub> = 1.7V                         | 0.1                    | 0.5                  | V (max)  |

(1) Typical specifications are specified at +25°C and represent the most likely parametric norm.

(2) Tested limits are specified to TI's AOQL (Average Outgoing Quality Level).

(3) The supply current specified is the current for  $V_{CC1}$  and  $V_{CC2}$  minus the current through  $R_L$  ( $I_{supply} = I_{CC1} + I_{CC2} - I_L$ ). The supply current for  $V_{CC2}$  (pin 16) does depend on the output load. With video output at 1V DC, the additional current through  $V_{CC2}$  is 7.7 mA with  $R_L = 390\Omega$ .

(4) Output voltage is dependent on load resistor. Test circuit uses  $R_L = 390\Omega$ .

www.ti.com

### **AC ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}C$ ;  $V_{CC1} = V_{CC2} = 8V$ . Manually adjust Video Output pins 13, 15, and 18 to 4V DC for the AC test unless otherwise stated.<sup>(1)</sup>

| Symbol                    | Parameter                                                  | Conditions                                         | Typical <sup>(2)</sup> | Limit <sup>(3)</sup> | Units     |

|---------------------------|------------------------------------------------------------|----------------------------------------------------|------------------------|----------------------|-----------|

| A <sub>Vmax</sub>         | Video Amplifier Gain                                       | $V_{10} = 4V, V_{IN} = 635 \text{ mV}_{PP}$        | 6.8                    | 5.9                  | V/V (min) |

|                           |                                                            | $V_{drive} = 4V$                                   | 16.7                   | 15.4                 | dB (min)  |

| ΔA <sub>V 2V</sub>        | Contrast Attenuation @ 2V                                  | Ref: $A_V$ max, $V_{10} = 2V$                      | -6                     |                      | dB        |

| ΔA <sub>V 0.25V</sub>     | Contrast Attenuation @ 0V                                  | Ref: $A_V$ max, $V_{10} = 0V$                      | -35                    |                      | dB        |

| ΔDrive                    | Drive Control Range                                        | $V_{drive} = 0V$ to 4V, $V_{10} = 4V$              | 12                     |                      | dB        |

| A <sub>V match</sub>      | Absolute Gain Match @ Av max                               | $V_{10} = 4V, V_{drive} = 4V^{(4)}$                | ±0.3                   |                      | dB        |

| A <sub>V track</sub>      | Gain Change Between Amplifiers                             | $V_{10} = 4V$ to $2V^{(4)(5)}$                     | ±0.3                   |                      | dB        |

| f(−3 dB)                  | Video Amplifier Bandwidth <sup>(6)(7)</sup>                | $V_{10} = 4V, V_{drive} = 4V, V_{O} = 3.5 V_{P,P}$ | 110                    |                      | MHz       |

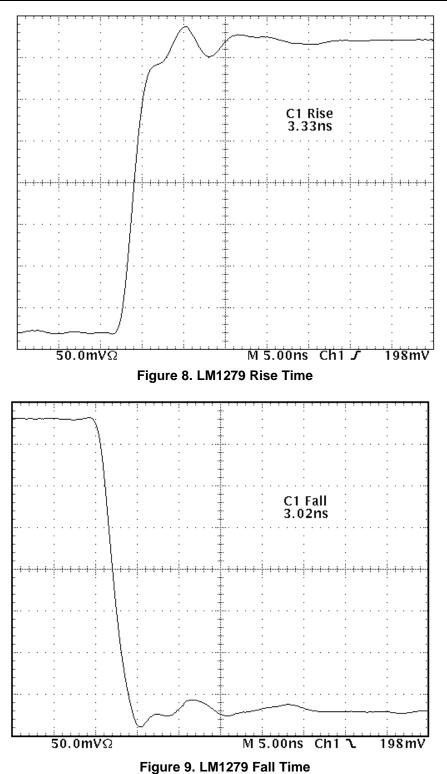

| t <sub>r</sub> (Video)    | Video Output Rise Time                                     | $V_{O} = 3.5 V_{P-P}^{(6)}$                        | 3.6                    |                      | ns        |

| t <sub>f</sub> (Video)    | Video Output Fall Time                                     | $V_{O} = 3.5 V_{P-P}^{(6)}$                        | 3.2                    |                      | ns        |

| V <sub>sep</sub> 10 kHz   | Video Amplifier 10 kHz Isolation                           | $V_{10} = 4V^{(8)}$                                | -70                    |                      | dB        |

| V <sub>sep</sub> 10 MHz   | Video Amplifier 10 MHz Isolation                           | $V_{10} = 4V^{(6)(8)}$                             | -50                    |                      | dB        |

| $\Delta V_{OL}(OSD)$      | OSD Black Level, Difference from<br>Video Black Level      | V <sub>OSD in</sub> = 0.8V, OSD Mode               | -0.4                   | -0.7                 | V (max)   |

| V <sub>OH</sub> (OSD)     | OSD Output High Voltage (above measured video black level) | $V_{OSD in}$ = 2.5V, OSD Mode                      | 2.1                    | 2.4                  | V (max)   |

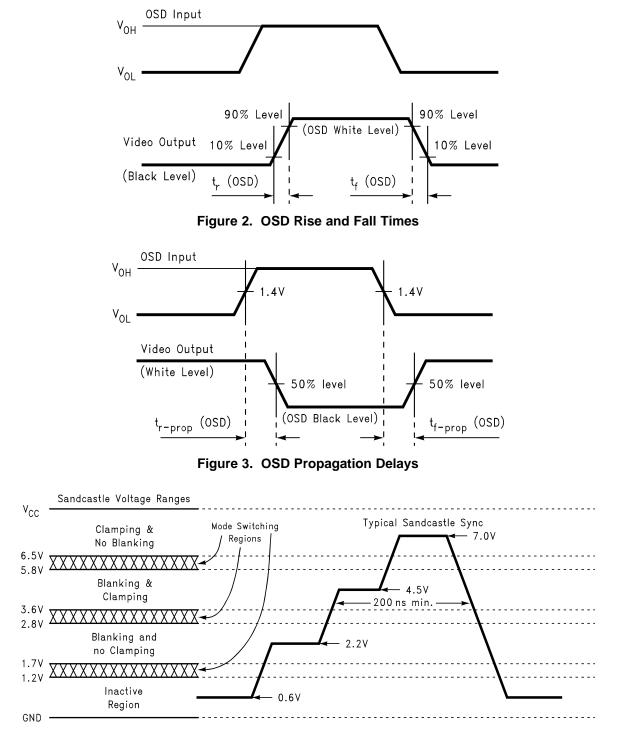

| t <sub>r</sub> (OSD)      | Going into OSD Mode                                        | OSD Mode (See Figure 2)                            | 5.0                    |                      | ns        |

| t <sub>f</sub> (OSD)      | Going out of OSD Mode                                      | OSD Mode (See Figure 2)                            | 10.0                   |                      | ns        |

| t <sub>r-prop</sub> (OSD) | Starting OSD Propagation Delay                             | Switching to OSD Mode (See Figure 3)               | 13.0                   |                      | ns        |

| t <sub>f-prop</sub> (OSD) | Ending OSD Propagation Delay                               | Switching to Vid. Mode (See Figure 3)              | 14.0                   |                      | ns        |

| T <sub>pw</sub> (Clamp)   | Input Clamp Pulse Width (Part of Sandcastle Sync)          | See <sup>(9)</sup>                                 |                        | 200                  | ns (min)  |

(1) During the AC test the 4V DC level is the center voltage of the AC output signal. For example, if the output is 4 V<sub>PP</sub> the signal will swing between 2V DC and 6V DC.

(2) Typical specifications are specified at +25°C and represent the most likely parametric norm.

(3) Tested limits are specified to TI's AOQL (Average Outgoing Quality Level).

(4) Measure gain difference between any two amplifiers.  $V_{IN} = 635 \text{ mV}_{PP}$ .

(5)  $\Delta A_V$  track is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three attenuators. It is the difference in gain change between any two amplifiers with the contrast voltage (V<sub>10</sub>) at either 4V or 2V measured relative to an A<sub>V</sub> max condition, V<sub>10</sub> = 4V. For example, at A<sub>V</sub> max the three amplifiers' gains might be 17.1 dB, 16.9 dB, and 16.8 dB and change to 11.2 dB, 10.9 dB and 10.7 dB respectively for V<sub>10</sub> = 2V. This yields the measured typical ± 0.1 dB channel tracking.

(6) When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit board without socked is recommended. Video amplifier 10 MHz isolation test also requires this printed circuit board. The reason for a double sided full ground plane PCB is that large measurement variations occur in single sided PCBs.

(7) Adjust input frequency from 10 MHz ( $A_V$  max reference level) to the -3 dB corner frequency ( $f_{-3 \text{ dB}}$ ).

(8) Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation. Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at  $f_{IN} = 10$  MHz for  $V_{sep} = 10$  MHz.

(9) A minimum pulse width of 200 ns is specified for a horizontal line of 15 kHz. This limit is specified by design. If a lower line rate is used then a longer clamp pulse may be required.

### **Timing Diagrams**

OBSOLETE

SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

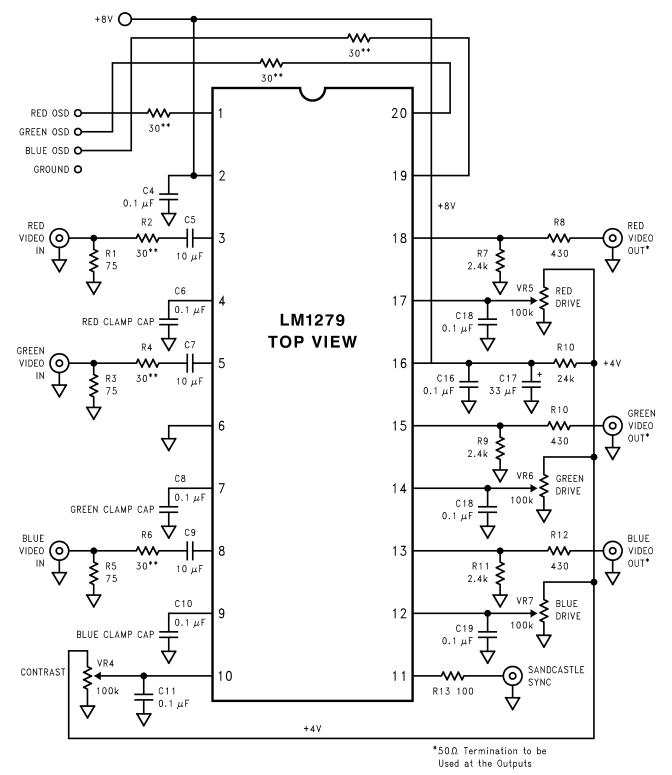

## Test Circuits

www.ti.com

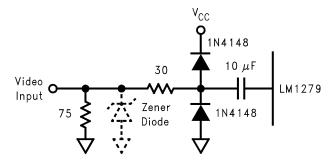

\*\***Note:** All video inputs *must* have a series 30Ω resistor for protection against EOS (Electrical Over Stress). If the OSD signals are external to the monitor, or these signals are present any time when +8V is not fully powered up, then the OSD inputs also *require* a series 30Ω resistor.

### Figure 5. LM1279 OSD Video Pre-amp Demonstration Board Schematic

www.ti.com

### **PIN DESCRIPTIONS**

| Pin<br>No.           | Pin<br>Name                                        | Schematic                                                            | Description                                                                                                                                                                                       |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>19<br>20        | Red OSD Input<br>Blue OSD Input<br>Green OSD Input | V <sub>CC1</sub> * ESD protection<br>diodes<br>OSD<br>Input<br>* 50k | These are standard TTL inputs. An OSD signal<br>at any of the three pins will automatically<br>switch the pre-amp into the OSD mode. 7<br>colors, including white, are available.                 |

| 2                    | V <sub>CC1</sub>                                   | • •                                                                  | Power supply pin (excluding output stage)                                                                                                                                                         |

| 3<br>5<br>8          | Red Video In<br>Green Video In<br>Blue Video In    | Video<br>Input<br>* ESD protection<br>diodes                         | Video inputs. These inputs <i>must</i> be AC<br>Coupled with a minimum of a 1 $\mu$ F cap, 10 $\mu$ F<br>is preferred. A series resistor of about 33 $\Omega$<br>must be used for ESD protection. |

| 4<br>7<br>9          | Red Clamp Cap<br>Green Clamp Cap<br>Blue Clamp Cap | Clamp<br>Cap<br>• ESD protection<br>diodes                           | The external clamp cap is charged and discharged to the correction voltage needed for DC restoration. 0.1 µF is the recommended value.                                                            |

| 6                    | Ground                                             | • • • •                                                              | Ground pin.                                                                                                                                                                                       |

| 10<br>12<br>14<br>17 | Contrast<br>Blue Drive<br>Green Drive<br>Red Drive | Contrast/<br>Drive                                                   | Contrast control pin:<br>4V - no attenuation<br>0V - over 40 dB attenuation<br>Drive control pins:<br>4V - no attenuation<br>0V - 20 dB attenuation                                               |

SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

| (continued) |                  |                                                           |                                                                                                                                                                    |  |  |

|-------------|------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>No.  | Pin<br>Name      | Schematic                                                 | Description                                                                                                                                                        |  |  |

| 11          | Sandcastle Input | * ESD protection<br>diodes<br>Sandcastle<br>Input         | The sandcastle input allows for blanking only,<br>or blanking with DC restoration. Blanking<br>requires a 2V input. Clamping with blanking<br>requires a 4V input. |  |  |

| 13          | Blue Video Out   |                                                           | Video output. For proper black level the output                                                                                                                    |  |  |

| 15          | Green Video Out  | V <sub>CC2</sub>                                          | must drive $390\Omega$ impedance.                                                                                                                                  |  |  |

| 18          | Red Video Out    | 50<br>* ESD protection<br>diodes<br>20<br>Video<br>Output |                                                                                                                                                                    |  |  |

| 16          | V <sub>CC2</sub> |                                                           | Power supply pin for the output stage. There are no internal connections to $V_{\text{CC1}}.$                                                                      |  |  |

### ESD AND ARC-OVER PROTECTION

The ESD cells of the LM1279 are improved over the ESD cells used in typical video pre-amps. The monitor designer must still use good PC board layout techniques when designing with the LM1279. The human body model ESD susceptibility of these parts is rated at 3 kV<sup>(1)</sup>. However, many monitor manufacturers are now testing their monitors to the level 4 of the IEC 801-2 specification. This requires the inputs to the monitor to survive an 8 kV discharge. If the monitor designer expects to survive such levels he MUST provide external ESD protection to the video pre-amp inputs! PC board layout is very important with LM1279 as with other video pre-amps. The LM1279 provides excellent protection against ESD and arc-over, but the LM1279 is not a substitute for good PCB layout.

Figure 6 shows the recommended input protection for a video pre-amp. The two diodes at the video pre-amp input and after the  $30\Omega$  series resistor offers the best protection against ESD. When this protection is combined with a good PCB layout, the video pre-amp will easily survive the IEC 801-2 level 4 (8 kV ESD) testing commonly done by monitor manufacturers. If the protection diodes are moved to the video input side of the  $30\Omega$  resistor, then the ESD protection will be less effective. There is also the risk of damaging the diodes since there is no resistor for current limiting. In such a design a heavier duty diode, such as the FDH400, should be used. It is strongly recommended that the protection diodes be added as shown in Figure 6. The 1N4148 diode has a maximum capacitance of 4 pF. This would have little effect on the response of the video system due to the low impedance of the input video.

Many monitor designers prefer to use a single zener diode instead of the recommended two diodes at the video pre-amp input. The required location of the zener diode is shown in Figure 6. It is shown as a dashed line, indicating an alternative to the two diode solution. The zener diode does give the savings of one component, but now the protection is less effective. To minimize capacitance, the zener diode needs to have a zener voltage of 24V or higher. This is well above the  $V_{CC}$  voltage of the LM1279. The zener diode must be located at the video input for protection against a low voltage surge. The 30 $\Omega$  resistor is needed to limit the current of such a voltage surge, protecting the video pre-amp. Protection against ESD by using a zener diode is about as effective as having the two diodes at the video input (same location as the zener diode). A higher series resistor may be necessary for protection against the zener voltage, but the higher resistor value will impair the performance of the LM1279; resulting in a lower bandwidth and a less stable black level. For maximum reliability the monitor designer should not consider the zener diode solution for ESD protection of the LM1279.

(1) Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

The ESD cells of the LM1279 also gives good tolerance against arc-over. Once again the monitor designer must be careful in his PCB layout for good arc-over protection. In the video chain only the outputs of the CRT driver are directly exposed to the voltages that may occur during arc-over. A good PCB layout is the best protection for the video pre-amp against arc-over. The pre-amp vulnerability is mainly through the ground traces on the PCB. For proper operation all ground connections associated with the video pre-amp, including the grounds to the bypass capacitors, must have short returns to the ground pins. A significant ground plane should be used to connect all the pre-amp grounds. *Figure 16*, the demo board layout, is an excellent example on an effective ground plane, yet using only a single sided PCB layout. Here is a check list to make sure a PC board layout has good grounding:

- All associated grounds with the video pre-amp are connected together through a large ground plane.

- CRT driver ground is connected to the video pre-amp ground at one point.

- CRT and arc protection grounds are connected directly to chassis, or the main ground. There is no arc-over current flow from these grounds through the pre-amp or CRT driver grounds.

If any one of the above suggestions are not followed, then the LM1279 may become vulnerable to arc-over. Improper grounding is by far the most common cause of a video pre-amp failure during arc-over.

Figure 6. Recommended Video Input ESD Protection

### FUNCTIONAL DESCRIPTION

Figure 1 on the front page shows the block diagram of the LM1279 along with the pinout of the IC. Each channel receives a video input signal at its input amplifier (-A1). The output of the input amplifier goes to the contrast attenuator stage. For easy interfacing to 5V DACs all controls inputs, including the contrast control, use a 0V to 4V range. The contrast control has no attenuation with an input of 4V, and has full attenuation (over -40 dB) with a 0V input. All three channels will accurately track the contrast control setting at pin 10. Each channel will have the same amount of attenuation for a given input voltage typically to within  $\pm 0.3$  dB. All channels will track because the contrast control is the first stage of attenuation and the internal control voltage generated from the input voltage is common to all three channels.

The output of the contrast attenuator goes to the drive attenuator. This stage has a 12 dB control range. This stage is used for color balance, so the adjustment range has been limited to 12 dB for a more accurate color balance. Each channel has its own independent control pin with the 0V to 4V control range. An input of 4V give no attenuation, and an input of 0V gives the full 12 dB attenuation.

The output of the drive attenuator stage goes to the inverting input of A2. Since this is the second inversion stage, the output of A2 will be the non-inverted video signal. Note that the output of gm1 goes to the non-inverting input of A2. Also note that the output of A2 goes to the inverting input of gm1. This is the feedback for the clamp circuitry. The output stage of A2 is an exact duplicate of the video output through A3. If a 390 $\Omega$  load impedance is used at the video output, then the black level at the output stage will accurately track the output of A2. The other input to gm1 is the desired black level output of the LM1279. Since the LM1279 has a fixed black level output, the non-inverting inputs to gm1 in all three channels go to a fixed 1.35V internal reference. This sets the black level output to a nominal 1.35V. gm1 acts like a sample and hold amplifier. Once the sandcastle sync exceeds 3.6V gm1 is activated, driving the input of A2 to a level where the video output will be 1.35V. For proper DC restoration it is important that gm1 be activated only during the horizontal flyback time when the video is at the black level. gm1 also charges the clamp cap to the correct voltage to maintain a 1.35V black level at the video output. When gm1 is turned off the voltage stored on the clamp cap will maintain the correct black level during the active video, thus restoring the DC level for a 1.35V black level.

The input of A3 receives the output from A2. The video channel of A3 is a duplication of the output stage to A2. As mentioned in the previous paragraph this is done so that the DC restoration can be done at the A2 stage. A3 also receives the OSD input and a sandcastle input for blanking. By doing DC restoration at the A2 stage, OSD or blanking can be activated at the output stage during the time DC restoration is being done at A2. There is an interface circuit between the sandcastle input and the A3 output stages. This interface circuit will activate the blanking if the sandcastle sync input is between 1.7V and 6.0V. The blanking mode will force the output down to a level of about 0.1V. This is a blacker-than-black level and can be used for blanking at the cathodes of the CRT.

Once the sandcastle exceeds 6.5V, then the output will no longer be in the blanked mode, but DC restoration is still being done on the video signal.

The OSD signal goes into a special interface circuit. The output of this circuit will drive the output of A3 to either an OSD black level or to about 2.4V above the video black level (OSD white level). The OSD black level is about 300 mV below the video black level. This ensures that if the OSD signal is not activated for a particular channel, then its output will be slightly below the cutoff level. If an OSD input is received in a particular channel, then the video output will be at the OSD white level. The OSD mode is automatically activated if there is only one OSD signal to any of the video channels. This OSD control circuit will allow any color, except black, during the OSD mode. This also saves the need for a special signal to switch into the OSD mode. Remember that at least one OSD input must be high to enable the OSD mode, therefore black can't be used in the OSD window.

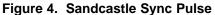

### Sandcastle Sync

This special sync signal is used to allow for a 20-pin OSD video pre-amp with all the desired controls. By using a sandcastle sync, both clamping and blanking can be activated from the same pin. Figure 4 shows the sandcastle sync signal. There are four possible modes of operation with the Sandcastle pulse. These modes are:

- 1. Inactive Region

- 2. Blanking and no Clamping

- 3. Blanking and Clamping

- 4. Clamping and no Blanking

Figure 4 also shows the voltage levels where the LM1279 switches from one mode to the other mode. As an example the LM1279 will switch from the inactive mode to the blanking and no clamping mode between 1.2V and 1.7V. For proper operation the inactive input must be safely below the 1.2V level. The blanking with no clamping pulse must be safely above 1.7V and below 2.8V. Blanking and clamping must be between 3.6V and 5.8V. Clamping and no blanking must be above 6.5V with the maximum voltage being limited by  $V_{CC}$ .

If the monitor designer desires to blank at the cathode, then he would go into the blanking and no clamping mode for most of the flyback period. During this period it is also necessary to do DC restoration. During this time the LM1279 should be operated in the blanking and clamping mode. In this mode DC restoration is done without interfering with blanking.

In some designs the horizontal phase shift capability of the monitor is very large. In these designs the video can be moved so the flyback period can be displayed during the active trace period for the video. Now the clamping could be done during the normal video sweep time. During this period clamping with blanking will give a black bar on the CRT screen. This is not a normal operating mode of the monitor, but the monitor designer still may prefer not to display this black bar. Under this condition the clamp pulse must be above 6.5V.

A simple two transistor sandcastle generator is covered in separate application note. This circuit will generate all four states for the sandcastle sync, including the clamp with no blanking when the clamping function occurs during the period for active video. The switching time between the inactive region and the clamp only region must be less than 30 ns if complete elimination of any blanking pulse is required in an application.

### **APPLICATIONS OF THE LM1279**

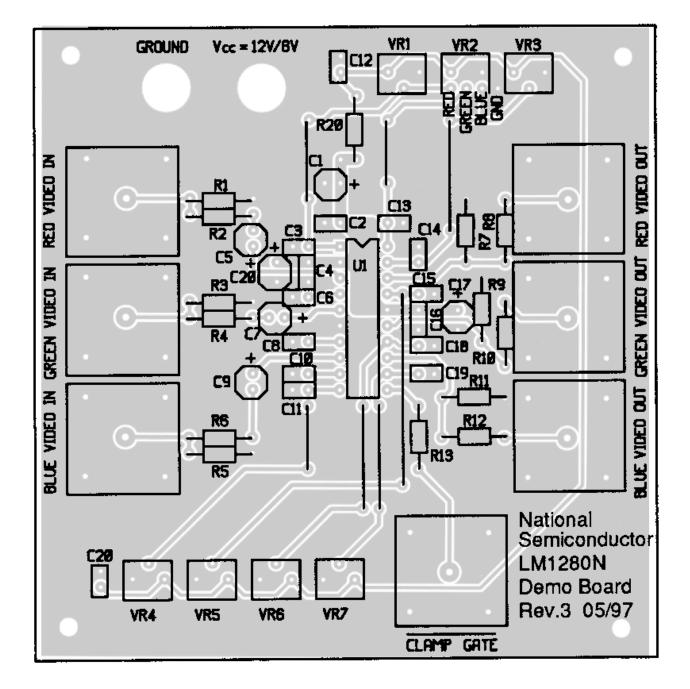

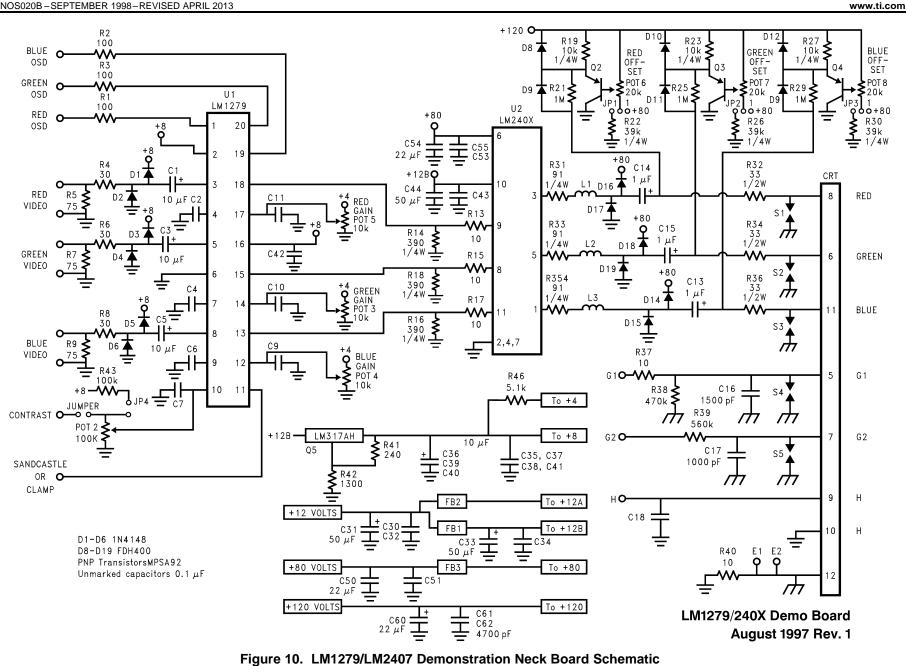

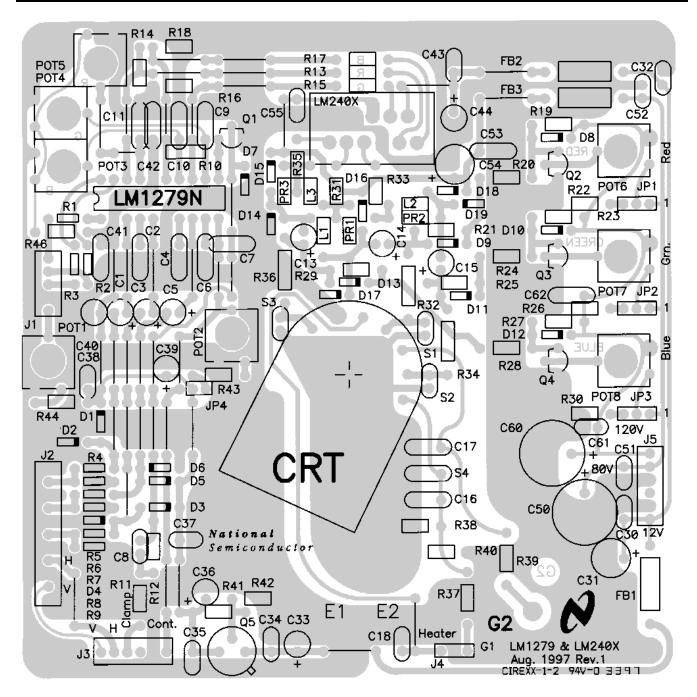

Two demonstration boards are available to evaluate the LM1279. One board is the pre-amp demonstration board. This board was used for testing and characterizing the LM1279. The schematic for this board is shown in Figure 5 and the printed circuit layout for this board is shown in Figure 7. The other board is a complete video channel neck board that can be directly plugged into the CRT socket. The schematic for this board is shown in Figure 10 and the printed circuit layout is shown in Figure 11. The CRT driver used on this board is the LM2407. Any of TI's monolithic CRT drivers can be used in this board, but the LM2407 is considered the best match to the LM1279 based on cost and performance.

Some important notes on Figure 5. All three video inputs have a 75 $\Omega$  terminating resistor for a 75 $\Omega$  video system. This is the normal video impedance of the video from a computer system. It is possible to also have a 50 $\Omega$  system, then R1, R3, and R5 would be changed to 50 $\Omega$ . R2, R4, and R6 are in series with the video inputs of the LM1279. These three 30 $\Omega$  resistors are required to protect the IC from any sudden voltage surges that may result during the power up and power down modes, or when connecting the monitor to other equipment. The monitor designer must include these resistors in his design for good monitor reliability. If additional protection against ESD at the video inputs is necessary, then adding clamp diodes on the IC side of the 30 $\Omega$  resistors is recommended, one to V<sub>CC1</sub> and one to ground (see Figure 6). Sometimes a designer may want to increase the value of the 30 $\Omega$  resistors at the video inputs, for additional ESD protection. This is not recommended with the LM1279. C5, C7, and C9 are part of the DC restoration circuit. This circuit is depending on a total maximum circuit resistance of about 110 $\Omega$ ; 30 $\Omega$  input series resistor plus 75 $\Omega$  for the video termination resistor. Increasing the value of the 30 $\Omega$  resistors will exceed the 110 $\Omega$  limit. The excellent internal ESD protection and the external clamp diodes (if needed) will provide excellent ESD protection.

The 30Ω resistors in series with the OSD inputs are also necessary if the OSD signals are external to the monitor, or if these signals are present any time when the +8V is not fully powered up. Interfacing to the OSD inputs is quite easy since the signal processing necessary to match the OSD signals to the video levels is done internal by the LM1279. There is also no need for an OSD window signal. Any time there is a high TTL signal at any of the three OSD inputs, the LM1279 will automatically switch to the OSD mode. A high TTL OSD signal will give a high video output for that color. The OSD level is fixed, typically 2.3V above the video black level. This will give a fixed brightness to the OSD window, but not at maximum video brightness which could be unpleasant to the user. Figure 2 and Figure 3 show the timing diagrams of the OSD signals for the LM1279.

The recommended load impedance for the LM1279 is  $390\Omega$ . However, some changes in the load impedance can be made. If the load impedance is reduced, the monitor designer must confirm that the part is still operating in its proper die temperature range, never exceeding a die temperature of  $150^{\circ}$ C. When changing the load impedance, the black level shift is shown in the chart below. The measured V<sub>P-P</sub> output with under 1% distortion is also listed.

| Load | V <sub>P-P</sub> | Blk. Level Shift |

|------|------------------|------------------|

| 430Ω | 3.62V            | +15 mV           |

| 390Ω | 3.62V            | 0 mV             |

| 330Ω | 3.58V            | −25 mV           |

| 270Ω | 3.51V            | −45 mV           |

When using a lower load impedance, the LM1279 does go into hard clipping more quickly. This does reduce the headroom of the video output.

Board layout is always critical in a high frequency application such as using the LM1279. A poor layout can result in ringing of the video waveform after sudden transitions, or the part could actually oscillate. A good ground plane and proper routing of the +8V are important steps to a good PCB layout. The LM1279 does require very good coupling between  $V_{CC1}$  and  $V_{CC2}$  (pins 2 and 16). This is clearly shown in Figure 7 and Figure 11 with the short and large trace between pins 2 and 16. Both demonstration boards offer the monitor designer an excellent example of good ground plane being used with the LM1279. These boards are single sided, yet allow the LM1279 to operate at its peak performance. The neck board also shows a good example of interfacing to a CRT driver and to the CRT. The video signal path is kept as short as possible between the LM1279 and the CRT driver, and also between the CRT driver and the CRT socket. Actual performance of the LM1279 in the video pre-amp demonstration board is shown in Figure 8 and Figure 9.

#### References

Ott, Henry W. Noise Reduction Techniques in Electronic Systems, John Wiley & Sons, New York, 1976

Zahid Rahim, "Guide to CRT Video Design," Application Note 861, Texas Instruments Corp., Jan. 1993

www.ti.com

### Applications of the LM1279

Figure 7. LM1279 OSD Video Pre-\Amp Demontration Board Layout

SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

TEXAS INSTRUMENTS

SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

www.ti.com

Figure 11. LM1279/LM2407 Demonstration Neck Board Layout

#### SNOS020B-SEPTEMBER 1998-REVISED APRIL 2013

### **REVISION HISTORY**

| Ch | nanges from Revision A (April 2013) to Revision B Pa | age |

|----|------------------------------------------------------|-----|

| •  | Changed layout of National Data Sheet to TI format   | 18  |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated