# LF6197

LF6197 160 ns Monolithic Sample-and-Hold Amplifier

Literature Number: SNOS640A

# LF6197 160 ns Monolithic Sample-and-Hold Amplifier

## **General Description**

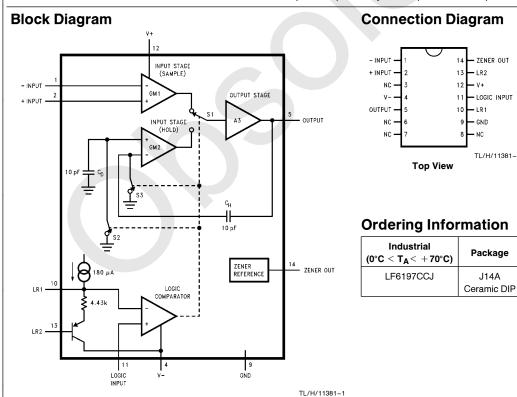

The LF6197 is a monolithic sample-and-hold (S/H) amplifier that uses a proprietary "current-multiplexed sample-andhold" technique to offer extremely high speed while maintaining 12 bits or higher accuracy. The device is built using National's advanced junction-isolated VIPTM (Vertically Integrated PNP) and BI-FETTM process technologies.

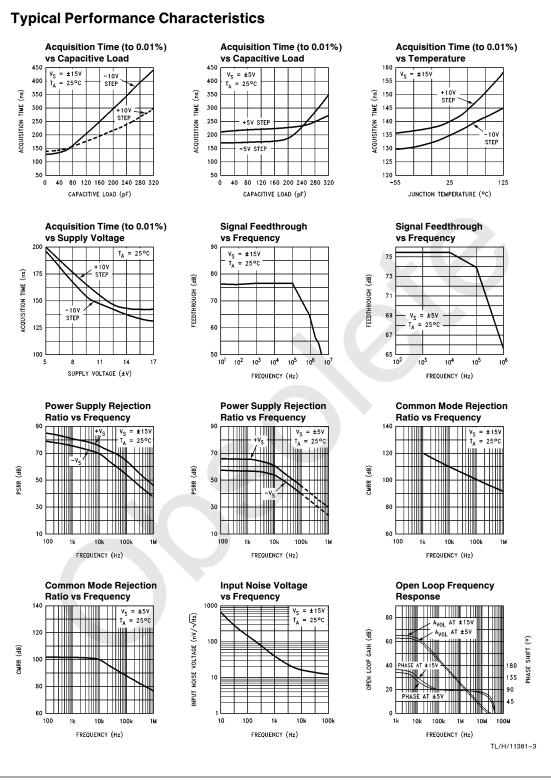

The LF6197 acquires a 10V step input to within  $\pm 0.01\%$  in 160 ns and has 10 mV hold step error when going from sample to hold mode. The input offset voltage in the sample mode is typically 3 mV. Even at extremely fast acquisition speeds, no compromises are made in the droop rate, which is 0.6  $\mu\text{V}/\mu\text{s}.$  When configured for unity gain, the DC gain error is 0.03%. The feedthrough attenuation in the hold mode is 83 dB at DC and 77 dB at 100 kHz.

The LF6197 can be externally configured for either inverting or non-inverting gains, thus offering additional flexibility to the user. The device includes an internal 10 pF hold capaci-

#### **Features**

- Operates with supply voltages from  $\pm 5V$  to  $\pm 18V$

- CMOS, TTL and ECL compatible logic input

- Adjustable inverting or non-inverting gain

- Internal hold capacitor

- High power-supply rejection in both sample and hold modes

# **Key Specifications**

| ■ Acquisition time (10V step to 0.01%) | 160 ns              |

|----------------------------------------|---------------------|

| ■ Hold mode settling time (10V step to | 0.01%) 50 ns        |

| ■ Droop rate                           | 0.6 μV/μs           |

| ■ Hold step                            | 10 mV               |

| ■ Aperture jitter                      | 8 ps <sub>rms</sub> |

| ■ Feedthrough attenuation at DC        | 83 dB               |

| ■ Small signal bandwidth               | 25 MHz              |

## **Applications**

- High-speed data acquisition systems

- Automatic test equipment

- High-speed instrumentation

- Replaces expensive hybrid sample-and-hold amplifiers

- ZENER OUT

- LOGIC INPUT

TL/H/11381-2

**Package**

J14A

- LR2 <del>-</del> ۷+

- LR 1

- GND NC.

#### **Absolute Maximum Ratings** (Notes 1, 2)

Positive Supply Voltage (V+) Negative Supply Voltage (V-) -18V

$V^+$  or  $V^-$  or  $\pm 12.5 V$ , Analog Input Voltage whichever is less

Logic Input to LR1 Differential Voltage  $\pm 5V$ Power Dissipation (Note 3) 1.2W

Duration of Output Short Circuit to GND (Note 4)

**ESD Susceptibility**

All Pins except Pin 13 (Note 5) 2000V Pin 13 only (Note 5) 1500V

Lead Temperature (Soldering, 10 sec.)

J Package 300°C Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

# Operating Ratings (Notes 1, 2)

$\begin{array}{l} T_{MIN} \leq T_A \leq T_{MAX} \\ 0^{\circ}C \leq T_A \leq +70^{\circ}C \end{array}$ Temperature Range LF6197CCJ  $+\,4.75V\,\leq\,V^{\,+}\,\leq\,+\,15.75V$ Positive Supply Voltage  $-15.75V \le V^- \le -4.75V$ Negative Supply Voltage

#### **Electrical Characteristics**

Unless otherwise specified, the following specifications apply for V<sup>+</sup> = +15V, V<sup>-</sup> = -15V,  $-12V \le V_{\text{IN}} \le +12V$ ,  $R_L > 1$  k $\Omega$ ,  $C_L \le 40$  pF, Logic Reference 2 (LR2) voltage = 0V and Logic Input Voltage  $\le 1.4V$  threshold, (Unit is in "sample" mode).  $V_S$  refers to the supply voltages,  $V^+$  and  $V^-$ . Boldface limits apply for  $T_A = T_J$  from  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C.$

| Symbol                   | Parameter                       | Conditions                           | Typical<br>(Note 6) | Limit<br>(Note 7) | Units<br>(Limit)     |

|--------------------------|---------------------------------|--------------------------------------|---------------------|-------------------|----------------------|

| NPUT CHARA               | CTERISTICS                      |                                      |                     |                   | <u> </u>             |

| V <sub>OS</sub>          | Input Offset Voltage            | V <sub>S</sub> = ±5V, (Note 8)       | ±3.0<br>±3.0        | ± 6.0             | mV (max)<br>mV (max) |

| $\Delta V_{OS}/\Delta T$ | Input Offset Drift              |                                      | 15                  |                   | μV/°C                |

| R <sub>IN, com</sub>     | Input Resistance (common mode)  |                                      | 10                  |                   | MΩ                   |

| R <sub>IN, dif</sub>     | Input Resistance (differential) |                                      | 300                 |                   | kΩ                   |

| CMRR                     | Common Mode Rejection Ratio     | $V_{CM} = \pm 10V$                   | 100                 | 80                | dB (min)             |

| I <sub>B+</sub>          | Positive Input Bias Current     |                                      | 7                   | 17                | μΑ (max)             |

| I <sub>B</sub> _         | Negative Input Bias Current     |                                      | 1                   | 7.5               | μΑ (max)             |

| RANSFER CH               | IARACTERISTICS                  |                                      |                     |                   |                      |

|                          | DC Open Loop Gain               | $V_{OUT} = \pm 12V, R_L = 1 k\Omega$ | 70                  | 65                | dB (min)             |

|                          | DC Open Loop Gain (Note 8)      | $V_S = \pm 5V, V_{OUT} = \pm 2.5V$   | 55                  | 49                | dB (min)             |

|                          | Gain Error (Note 9)             |                                      | 0.03                |                   | % (max)              |

|                          | Gain Linearity Error            | $V_{OUT} = \pm 10V$                  | 0.003               | 0.0045            | % (max)              |

| f <sub>u</sub>           | Gain Bandwidth Product          |                                      | 25                  | 14                | MHz (min)            |

| UTPUT CHAI               | RACTERISTICS                    |                                      |                     |                   |                      |

| R <sub>OUT</sub>         | Output Resistance               |                                      | 0.02                |                   | Ω                    |

| SR                       | Slew Rate                       |                                      | 145                 |                   | V/µs                 |

|                          | Short Circuit Source Current    |                                      | -63                 | -25               | mA (min)             |

|                          | Short Circuit Sink Current      |                                      | 70                  | 25                | mA (min)             |

| CL                       | Maximum Capacitive Load         | No Oscillation                       | 200                 |                   | pF                   |

**Electrical Characteristics** (Continued) Unless otherwise specified, the following specifications apply for V<sup>+</sup> = +15V, V<sup>-</sup> = -15V, -12V  $\leq$  V<sub>IN</sub>  $\leq$  +12V, R<sub>L</sub> > 1 k $\Omega$ , C<sub>L</sub>  $\leq$  40 pF, Logic Reference 2 (LR2) voltage = 0V and Logic Input Voltage < 1.4V threshold, (Unit is in "sample" mode). V<sub>S</sub> refers to the supply voltages, V<sup>+</sup> and V<sup>-</sup>. **Boldface limits apply for T<sub>A</sub>** = **T**<sub>J</sub> **from T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C.

| Symbol             | Parameter                                                   | Conditions                                                                                                                                       | Typical<br>(Note 6) | Limit<br>(Note 7) | Units<br>(Limit)           |

|--------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|----------------------------|

| SAMPLE/HC          | OLD CHARACTERISTICS                                         |                                                                                                                                                  |                     |                   | I                          |

| <sup>t</sup> ACQ   | Acquisition Time<br>to 0.1% (Note 10)<br>to 0.01% (Note 10) | 10V step<br>+ 10V step                                                                                                                           | 130<br>145          | 240<br><b>260</b> | ns<br>ns (max)<br>ns (max) |

|                    |                                                             | −10V step                                                                                                                                        | 160                 | 240<br><b>260</b> | ns (max)<br>ns (max)       |

| t <sub>AD</sub>    | Aperture Delay Time                                         |                                                                                                                                                  | 4                   |                   | ns                         |

| $t_{AJ}$           | Aperture Jitter                                             |                                                                                                                                                  | 8                   |                   | ps <sub>rms</sub>          |

|                    | Droop Rate                                                  |                                                                                                                                                  | 0.6                 | 10                | μV/μs (max)                |

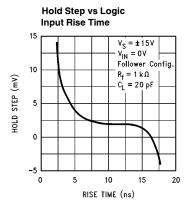

| V <sub>HS</sub>    | Hold Step (Note 11)                                         |                                                                                                                                                  | ±10                 |                   | mV (max)                   |

| t <sub>HMS</sub>   | Hold Mode Settling Time to 0.01%                            | 10V step                                                                                                                                         | 50                  |                   | ns                         |

|                    | Feedthrough Attenuation (Note 12)                           | $ f = 1 \text{ kHz}, V_{\text{IN}} = 20 \text{ V}_{\text{p-p}} $ $ f = 100 \text{ kHz}, V_{\text{IN}} = 20 \text{ V}_{\text{p-p}} $              | 83<br>77            | 80                | dB (min)<br>dB             |

| DYNAMIC C          | HARACTERISTICS                                              |                                                                                                                                                  |                     |                   |                            |

| THD                | Total Harmonic Distortion                                   | $\begin{array}{l} f = 10 \text{ kHz, V}_{IN} = 20 \text{ V}_{p\text{-}p} \\ f = 150 \text{ kHz, V}_{IN} = 20 \text{ V}_{p\text{-}p} \end{array}$ | -83<br>-78          |                   | dB<br>dB                   |

| FPBW               | Full Power Bandwidth (Note 13)                              | $V_{IN} = 20 V_{p-p}$                                                                                                                            | 2.3                 |                   | MHz                        |

|                    | Small Signal Bandwidth                                      |                                                                                                                                                  | 25                  |                   | MHz                        |

| DIGITAL LO         | GIC CHARACTERISTICS                                         |                                                                                                                                                  |                     |                   |                            |

| V <sub>IN(1)</sub> | Logical "1" Input Voltage                                   |                                                                                                                                                  |                     | 2.0               | V (min)                    |

| V <sub>IN(0)</sub> | Logical "0" Input Voltage                                   |                                                                                                                                                  |                     | 8.0               | V (max)                    |

|                    | Logic Input Current                                         |                                                                                                                                                  | 6                   | 20                | μA (max)                   |

|                    | Logic Reference 2 Input Current                             |                                                                                                                                                  | 3                   | 5                 | μΑ (max)                   |

|                    | Differential Logic Threshold<br>(Logic Input to LR1)        |                                                                                                                                                  | 1.4                 | 1.1<br>1.6        | V(min)<br>V(max)           |

| POWER SUF          | PPLY CHARACTERISTICS                                        |                                                                                                                                                  |                     |                   |                            |

| I <sub>S+</sub>    | Positive Supply Current                                     |                                                                                                                                                  | 20                  | 30                | mA (max)                   |

| I <sub>S+</sub>    | Positive Supply Current                                     | V <sub>S</sub> = ±5V (Note 8)                                                                                                                    | 18.2                | 27                | mA (max)                   |

| I <sub>S</sub> _   | Negative Supply Current                                     |                                                                                                                                                  | 20                  | 30                | mA (max)                   |

| I <sub>S</sub> _   | Negative Supply Current                                     | $V_S = \pm 5V$ (Note 8)                                                                                                                          | 17.5                | 27                | mA (max)                   |

| PSRR               | Power Supply Rejection Ratio                                | $V_S = \pm 12V \text{ to } \pm 16V$                                                                                                              | 84                  | 74                | dB (min)                   |

#### **Electrical Characteristics** (Continued)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$ .  $\Theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_D = (T_{Jmax} - T_A)/\Theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{Jmax} = 150^{\circ}\text{C}$  and  $\theta_{JA} = 125^{\circ}\text{C/W}$ . The Power Derating Curve shows the safe thermal operating area for this device.

Note 4: Continuous short-circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

Note 5: Human body model, 100 pF capacitor discharged through a 1.5 k $\!\Omega$  resistor.

**Note 6:** Typicals are at  $T_A = 25^{\circ}C$  and represent the most likely parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Operation at  $\pm 5 \text{V}$  requires that pin 14 be forced to 2.5 V.

Note 9: Gain error is calculated from the measured open loop gain.

Note 10: The acquisition time of the LF6197 has been measured when the device has been configured as an inverting amplifier with a gain of -1, feedback resistor of 2 k $\Omega$ , feedback capacitor of 1 pF, and a total load resistor of 1 k $\Omega$ .

Note 11: Hold step is measured with the LF6197 configured as a unity gain follower and input connected to ground. A TTL pulse with 4 ns rise and fall times is applied to the logic input; the hold step is dependent on the slew rate of the logic input pulse.

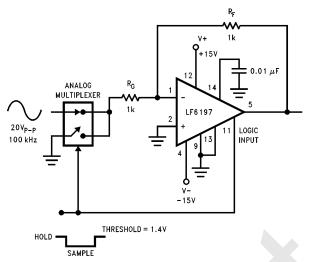

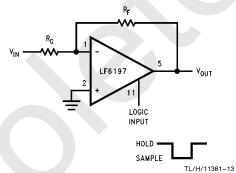

Note 12: See test circuit, Figure 1.

Note 13: Full power bandwidth is calculated using FPBW = SR/( $2\pi V_P$ ); where SR is the measured slew rate and  $V_P$  is the peak voltage.

TL/H/11381-15

# **Power Derating Curve** 1.4 1.2 Maximum Package Thermal 1.0 POWER DISSIPATION (W) 0.8 12 0.6 Safe Operating Area 0.4 0.2 0 └ -40 -20 60 40 100 120 AMBIENT TEMPERATURE (°C)

TL/H/11381-16

# **Test Circuit**

FIGURE 1. Circuit configuration for the measurement of feedthrough attenuation. Input is connected to ground in sample mode and is connected to 20 Vpp, 100 kHz sine wave in hold mode.

# **Pin Descriptions**

| Pin Descrip | uons                                                                                                                                                                                                                                           |                                |                                                                                                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V+ (12)     | This is the positive power supply pin. A $+5V$ to $+15V$ supply voltage should be applied to this pin and bypassed to ground with a 0.1 $\mu\text{F}$ ceramic capacitor in parallel with a 4.7 $\mu\text{F}$ tantalum capacitor.               | LR1 (10)                       | This is the Logic Reference 1 input. By applying the appropriate logic threshold at this pin, the sample-and-hold amplifier's logic input can be made either CMOS or ECL compatible. For TTL logic levels, this pin should remain unconnected.   |

| V- (4)      | This is the negative power supply pin. A $-5\text{V}$ to $-15\text{V}$ supply voltage should be applied to this pin and bypassed to ground with a 0.1 $\mu\text{F}$ ceramic capacitor in parallel with a 4.7 $\mu\text{F}$ tantalum capacitor. | LR2 (13)                       | This is the Logic Reference 2 input. For TTL logic levels, this pin should be connected to ground; this sets the logic threshold at the logic comparator's inverting pin at 1.4V. For CMOS or ECL logic levels this pin should either remain un- |

| GND (9)     | This is the ground reference pin. All signals are referenced to the potential at this pin.                                                                                                                                                     | Logic Input (11)               | connected or connected to pin 10.  This is the logic control input pin. A logic low at this pin will configure the amplifier                                                                                                                     |

| -Input (1)  | ·                                                                                                                                                                                                                                              |                                | in the "sample" mode while a logic high will configure the amplifier in the "hold" mode. The TTL, CMOS, or ECL logic compatibility will be determined by the voltage threshold set at the logic comparator's inverting input.                    |

|             |                                                                                                                                                                                                                                                | Zener Reference<br>Output (14) | For optimum acquisition and settling times, this pin must be bypassed to ground with a 0.01 $\mu$ F capacitor. Furthermore, for $\pm$ 5V supply operation, this pin                                                                              |

| + Input (2) | This is the non-inverting input of the "sample" amplifier. This pin should be                                                                                                                                                                  |                                | must be biased at 2.5V from a low impedance source.                                                                                                                                                                                              |

|             | driven from a low impedance source.                                                                                                                                                                                                            | NC (3,6,7,8)                   | No connection.                                                                                                                                                                                                                                   |

| Output (5)  | This is the output of the sample-and-hold amplifier.                                                                                                                                                                                           |                                |                                                                                                                                                                                                                                                  |

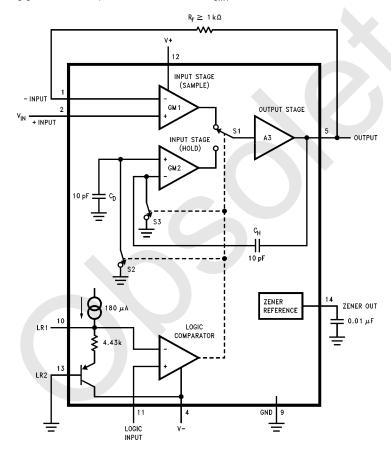

# **Functional Description**

The LF6197 uses a proprietary "current-multiplexed sample-and-hold" technique as depicted in the simplified block diagram (Figure 2). The amplifier consists of two transconductance input stages  $g_{m1}$  and  $g_{m2}$  and a common gain and output buffer stage A3. In the sample mode, internal current switching is employed to connect the input stage  $g_{m1}$  to the common output stage A3 while input stage  $g_{m2}$  is disconnected. Additionally, switches S2 and S3 are closed, thereby shorting the internal dummy capacitor and connecting one end of the hold capacitor to a low impedance ground. Although the simplified schematic shows the switches S1 and S2 connected to ground, the switches are in fact connected to a reference potential which appears as a common mode voltage at the two inputs of  $g_{m2}$ .

For unity gain, the inverting input of  $g_{m1}$  is externally connected to the output through a resistor, thus closing the loop around the amplifier. Conventional op-amp feedback topologies may be employed to configure the amplifier for inverting and non-inverting gains. In the sample mode, a current

booster in the output stage rapidly charges the hold capacitor. A wide-bandwidth amplifier, high-current output stage and fast current-switched hold-to-sample mode selection allows for a slew rate of 145 V/ $\mu$ s and acquisition time of under 200 ns.

When there is a change to the Hold mode, switches S2 and S3 are quickly opened and switch S1 is effectively connected to the output of  $g_{\rm m2}$  while input stage  $g_{\rm m1}$  is disconnected. The composite amplifier is now comprised of  $g_{\rm m2}$  and A3 and the loop around the amplifier is closed by the hold capacitor. Note that the opening of switch S3 causes charge injection into the hold capacitor. However, an equal amount of charge is injected into the dummy capacitor due to the opening of a matched switch S2. The net effect is a differential cancellation of charge and thus the pedestal error (hold step) is greatly reduced. Meanwhile, excellent feedthrough attenuation is achieved because the input signal is isolated from the output by the inactive input stage  $g_{\rm m1}$ .

TL/H/11381-5

FIGURE 2. Simplified Block Diagram of LF6197 Sample-and-Hold Amplifier, Connected for Unity Gain and TTL Logic

# **Application Hints**

#### 1.0 LOGIC CONFIGURATIONS

The LF6197 can be configured to interface with TTL, CMOS, or ECL logic. The device is configured for the desired logic using the two Logic Reference pins (LR1 and LR2).

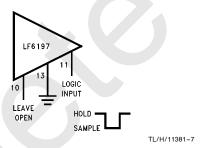

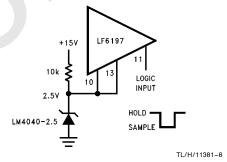

#### 1.1 TTL Logic

To configure the device to operate with TTL logic, the LR1 pin should be left open and the LR2 pin should be grounded (*Figure 4*). This will set the threshold of the logic comparator at 1.4V.

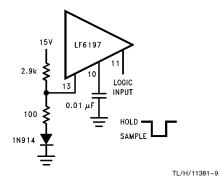

#### 1.2 CMOS Logic

To configure the device to operate with CMOS logic (with a 2.5V threshold at the comparator), several options are available. The LR1 and LR2 pins can be tied together and connected to a 2.5V reference (*Figure 5*); or LR2 can be set to 1.1V with a resistor diode network and LR1 can be bypassed to ground with a 0.01  $\mu$ F capacitor (*Figure 6*).

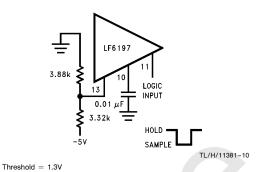

#### 1.3 ECL Logic

To operate with ECL logic (threshold at -1.3V), set LR2 at -2.7V with a voltage divider from the negative supply and bypass LR1 with a 0.01  $\mu$ F capacitor (*Figure 7*).

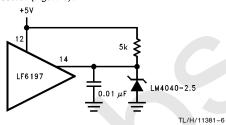

#### 2.0 ZENER REFERENCE OUTPUT

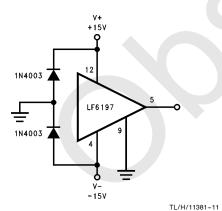

The LF6197 includes an internal zener diode to bias various sections of the chip. The zener diode output is brought out at pin 14; the voltage at this pin is typically 6.25V when the device is powered from  $\pm$  15V supplies. For optimum device performance, pin 14 must be bypassed to ground with a 0.01  $\mu F$  capacitor. If the device is powered from  $\pm$  5V supplies, then pin 14 must be biased at 2.5V from a low impedance source (Figure 3).

FIGURE 3. Biasing Pin 14 to 2.5V for Operation from  $\pm$  5V Supplies

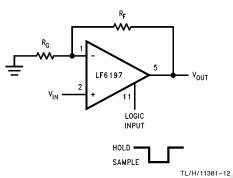

#### 3.0 ADJUSTING GAIN

The LF6197 allows the user to amplify as well as to sampleand-hold an input signal. This feature eliminates the need for an amplifier preceding the S/H amplifier in many applications. Familiar op-amp feedback topologies are employed to configure the LF6197 for non-inverting (Figure 8) or inverting (Figure 9) gains. Note that a feedback resistor of value 1 k $\Omega$  or larger must be used for all gain settings, including non-inverting unity gain. The feedback resistor is required to limit the current through LF6197's internal clamp diodes when the device is in the hold mode.

#### 4.0 POWER SUPPLY SEQUENCING

When power supply to the LF6197 is turned on, the negative supply must come on before the positive supply. Meanwhile, when the power supply is turned off, the positive supply must turn off before the negative supply. Improper power supply sequencing may destroy the device. To protect the device against improper power supply sequencing, anti-reversal diodes may be used across the supply pins (Figure 10).

Threshold = 1.4V FIGURE 4. TTL Logic

Threshold = 2.5V

FIGURE 5. CMOS Logic

# **Application Hints** (Continued)

Threshold = 2.5V

FIGURE 6. Another Circuit for CMOS Logic

FIGURE 7. ECL Logic

FIGURE 8. LF6197 with Non-Inverting Gain

FIGURE 9. LF6197 with Inverting Gain

FIGURE 10. Using Anti-Reversal Diodes to Protect LF6197 from Improper Power Supply Sequencing

TL/H/11381-14

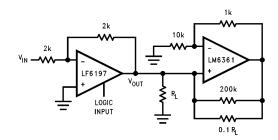

FIGURE 11. Increasing Linearity to 16 Bits Using a

Negative Impedance Load at the Output of LF6197

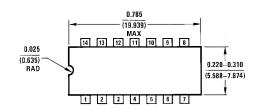

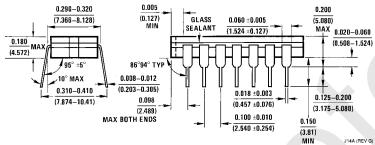

# Physical Dimensions inches (millimeters)

Ceramic Dual-In-Line Package (J) Order Number LF6197CCJ NS Package Number J14A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: onlyeg@etervel.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9860 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

TI E2E Community Home Page <u>e2e.ti.com</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated