OBSOLETE

www.ti.com

SNOS854D - AUGUST 2000 - REVISED APRIL 2013

CLC410 Fast Settling, Video Op Amp with Disable

Check for Samples: CLC410

# **FEATURES**

- -3dB Bandwidth of 200MHz

- 0.05% Settling in 12ns

- Low Power, 160mW (40mW Disabled)

- Low Distortion, -60dBc at 20MHz

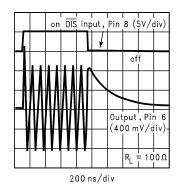

- Fast Disable (200ns)

- Differential Gain/Phase: 0.01%/0.01°

- ±1 to ±8 Closed-Loop Gain Range

# **APPLICATIONS**

- Video Switching and Distribution

- Analog Bus Driving (with Disable)

- Low Power "Standby" using Disable

- Fast, Precision A/D Conversion

- D/A Current-to-Voltage Conversion

- IF Processors

- High Speed Communications

# DESCRIPTION

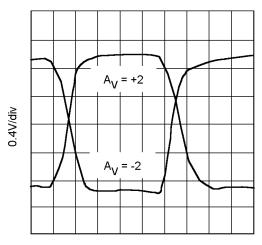

The current-feedback CLC410 is a fast settling, wideband, monolithic op amp with fast disable/enable feature. Designed for low gain applications ( $A_V = \pm 1$  to  $\pm 8$ ), the CLC410 consumes only 160mW of power (180mW max) yet provides a -3dB bandwidth of 200MHz ( $A_V = \pm 2$ ) and 0.05% settling in 12ns (15ns max). Plus, the disable feature provides fast turn on (100ns) and turn off (200ns). In addition, the CLC410 offers both high performance and stability without compensation - even at a gain of  $\pm 1$ .

The CLC410 provides a simple, high performance solution for video switching and distribution applications, especially where analog buses benefit from use of the disable function to "multiplex" signals onto the bus. Differential gain/phase of 0.01%/0.01° provide high fidelity and the 60mA output current offers ample drive capability.

The CLC410's fast settling, low distortion, and high drive capabilities make it an ideal ADC driver. The low 160mW quiescent power consumption and very low 40mW disabled power consumption suggest use where power is critical and/or "system off" power consumption must be minimized.

The CLC410 is available in several versions to meet a variety of requirements. A three letter suffix determines the version.

### Enhanced Solutions (Military/Aerospace)

SMD Number: 5962-90600

Space level versions also available.

Figure 1. Enable/Disable Response

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNOS854D-AUGUST 2000-REVISED APRIL 2013

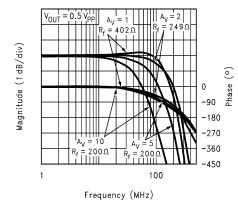

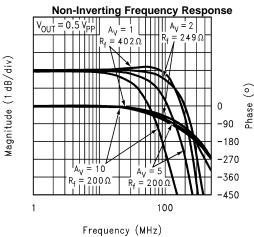

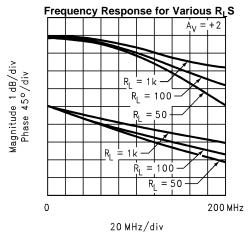

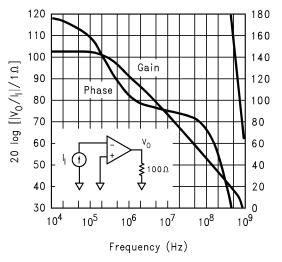

#### Figure 2. Non-Inverting Frequency Response

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

| Supply Voltage (V <sub>CC</sub> )    | ±7V                                                                                                                         |                  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------|

| I <sub>OUT</sub>                     | Output is short circuit protected to ground, but maximum reliability will be maintained if I <sub>OUT</sub> does not exceed | 60mA             |

| Common Mode Input Voltage            |                                                                                                                             | ±V <sub>CC</sub> |

| Differential Input Voltage           |                                                                                                                             | 5V               |

| Disable Input Voltage (pin 8)        | ±V <sub>CC</sub> -1V                                                                                                        |                  |

| Applied output voltage when disabled | ±V <sub>CC</sub>                                                                                                            |                  |

| Junction Temperature                 | +150°C                                                                                                                      |                  |

| Operating Temperature Range          | −40°C to +85°C                                                                                                              |                  |

| Storage Temperature Range            | −65°C to +150°C                                                                                                             |                  |

| Lead Solder Duration (+300°C)        | 10 sec                                                                                                                      |                  |

| ESD Rating (human body model)        | 500V                                                                                                                        |                  |

(1) "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the devices should be operated at these limits. The table of ELECTRICAL CHARACTERISTICS specifies conditions of device operation.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

### **OPERATING RATINGS**

| Thermal Resistance                          |        |         |  |  |  |

|---------------------------------------------|--------|---------|--|--|--|

| Package ( $\theta_{JC}$ ) ( $\theta_{JA}$ ) |        |         |  |  |  |

| PDIP                                        | 65°C/W | 120°C/W |  |  |  |

| SOIC                                        | 60°C/W | 140°C/W |  |  |  |

# ELECTRICAL CHARACTERISTICS

$A_V$  = +2,  $V_{CC}$  = ±5V,  $R_L$  = 100 $\Omega,~R_f$  = 250 $\Omega;$  unless specified

| Symbol              | Parameter                 | meter Conditions Typ                 |       | Max/Min <sup>(1)</sup> | Units |       |     |

|---------------------|---------------------------|--------------------------------------|-------|------------------------|-------|-------|-----|

| Ambient Temperature |                           | CLC410AJ                             | +25°C | -40°C                  | +25°C | +85°C |     |

| Frequency           | Frequency Domain Response |                                      |       |                        |       |       |     |

| SSBW                | -3dB Bandwidth            | V <sub>OUT</sub> <0.5V <sub>PP</sub> | 200   | >150                   | >150  | >120  | MHz |

| LSBW                |                           | $V_{OUT} < 5V_{PP},$<br>$A_V = +5$   | 50    | >35                    | >35   | >35   | MHz |

(1) Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

SNOS854D - AUGUST 2000 - REVISED APRIL 2013

www.ti.com

$A_V$  = +2,  $V_{CC}$  = ±5V,  $R_L$  = 100 $\Omega,~R_f$  = 250 $\Omega;$  unless specified

| Symbol     | Parameter                                          |                     | Conditions                                      | Тур  | Max/Min <sup>(1)</sup> |       |       | Units        |

|------------|----------------------------------------------------|---------------------|-------------------------------------------------|------|------------------------|-------|-------|--------------|

|            | Gain Flatness                                      |                     | $V_{OUT} < 0.5 V_{PP}$                          |      |                        |       |       |              |

| GFPL       | Peaking                                            |                     | DC to 40MHz                                     | 0    | <0.4                   | <0.3  | <0.4  | dB           |

| GFPH       | Peaking                                            |                     | >40MHz                                          | 0    | <0.7                   | <0.5  | <0.7  | dB           |

| GFR        | Rolloff                                            |                     | DC to 75MHz                                     | 0.6  | <1                     | <1    | <1.3  | dB           |

| LPD        | Linear Phase Deviation                             |                     | DC to 75MHz                                     | 0.2  | <1                     | <1    | <1.2  | deg          |

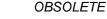

| Time Dom   | nain Response                                      |                     |                                                 |      |                        |       |       |              |

| TRS        | Rise and Fall Time                                 |                     | 0.5V Step                                       | 1.6  | <2.4                   | <2.4  | <2.4  | ns           |

| TRL        | _                                                  |                     | 5V Step                                         | 6.5  | <10                    | <10   | <10   | ns           |

| TSP        | Settling Time to                                   | ±0.1%               | 2V Step                                         | 10   | <13                    | <13   | <13   | ns           |

| TS         | _                                                  | ±0.05%              | 2V Step                                         | 12   | <15                    | <15   | <15   | ns           |

| OS         | Overshoot                                          |                     | 0.5V Step                                       | 0    | <15                    | <10   | <10   | %            |

| SR         | Slew Rate                                          | A <sub>V</sub> = +2 |                                                 | 700  | >430                   | >430  | >430  | V/µs         |

| SR1        | _                                                  | A <sub>V</sub> = −2 |                                                 | 1600 | _                      | _     | _     | V/µs         |

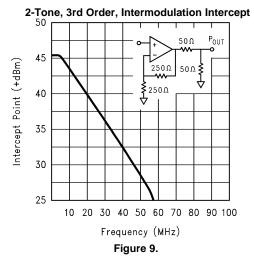

| Distortion | And Noise Response                                 |                     |                                                 |      |                        |       |       | -            |

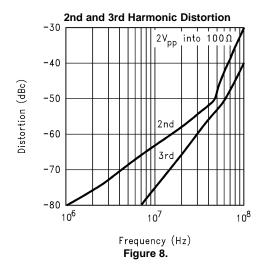

| HD2        | 2nd Harmonic Distortion                            |                     | 2V <sub>PP</sub> , 20MHz                        | -60  | <-40                   | <-45  | <-45  | dBc          |

| HD3        | 3rd harmonic distortion                            |                     | 2V <sub>PP</sub> , 20MHz                        | -60  | <-50                   | <-50  | <-50  | dBc          |

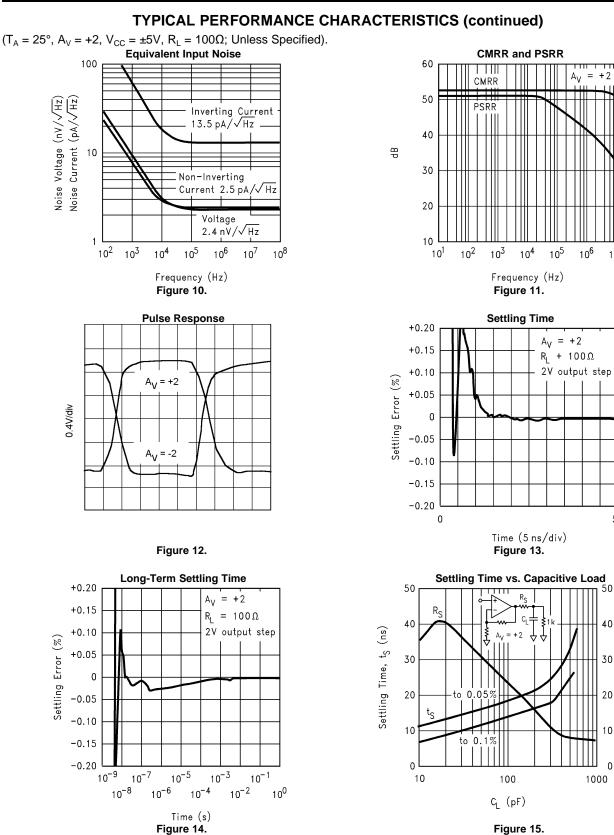

|            | Equivalent Input Noise                             |                     |                                                 |      |                        |       |       |              |

| SNF        | Noise Floor                                        |                     | >1MHz <sup>(2)</sup>                            | -157 | <-154                  | <-154 | <-153 | dBm<br>(1Hz) |

| INV        | Integrated Noise                                   |                     | 1MHz to 200MHz <sup>(2)</sup>                   | 40   | <54                    | <57   | <63   | μV           |

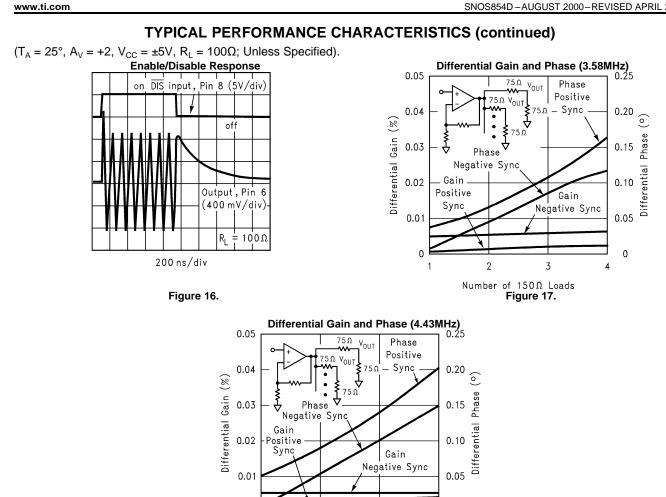

| DG         | Differential Gain <sup>(3)</sup>                   |                     | (See TYPICAL<br>PERFORMANCE<br>CHARACTERISTICS) | 0.01 | 0.05                   | 0.04  | 0.04  | %            |

| DP         | Differential Phase <sup>(3)</sup>                  |                     | (See TYPICAL<br>PERFORMANCE<br>CHARACTERISTICS) | 0.01 | 0.1                    | 0.02  | 0.02  | deg          |

| Disable/E  | nable Performance                                  |                     |                                                 |      |                        |       |       |              |

| TOFF       | Disable Time to >50dB<br>Attenuation at 10MHz      |                     |                                                 | 200  | <1000                  | <1000 | <1000 | ns           |

| TON        | Enable Time                                        |                     |                                                 | 100  | <200                   | <200  | <200  | ns           |

|            | DIS Voltage                                        |                     |                                                 |      |                        |       |       |              |

| VDIS       | To Disable                                         |                     |                                                 | 1.0  | 0.5                    | 0.5   | 0.5   | V            |

| VEN        | To Enable                                          |                     |                                                 | 2.6  | 2.3                    | 3.2   | 4.0   | V            |

|            | DIS current (sourced<br>from CLC410, see Figure 23 | 3)                  |                                                 |      |                        |       |       |              |

| IDIS       | To Disable                                         |                     |                                                 | 200  | 250                    | 250   | 250   | μA           |

| IEN        | To Enable                                          |                     |                                                 | 80   | 60                     | 60    | 60    | μA           |

| OSD        | Off Isolation                                      |                     | At 10MHz                                        | 59   | >55                    | >55   | >55   | dB           |

| Static, DC | Performance                                        |                     |                                                 | •    | +                      | •     | •     | •            |

| VIO        | Input Offset Voltage (4)                           |                     |                                                 | 2    | <±8.2                  | <±5.0 | <±9.0 | mV           |

| DVIO       | average temperature coefficient                    |                     |                                                 | 20   | <±40                   | _     | <±40  | µV/°C        |

| IBN        | Input Bias Current <sup>(4)</sup>                  |                     | Non Inverting                                   | 10   | <±36                   | <±20  | <±20  | μA           |

| DIBN       | Average Temperature Coefficient                    |                     |                                                 | 100  | <±200                  | -     | <±100 | nA/°C        |

| IBI        | Input Bias Current <sup>(4)</sup>                  |                     | Inverting                                       | 10   | <±36                   | <±20  | <±30  | μA           |

| DIBI       | Average Temperature Coefficient                    |                     |                                                 | 50   | <±200                  | _     | <±100 | nA/°C        |

(2) Noise tests are performed from 5MHz to 200MHz.

(3) Differential gain and phase measured at:  $A_V = +2$ ,  $R_f = 250\Omega$ ,  $R_L = 150\Omega \ 1V_{PP}$  equivalent video signal, 0-100 IRE, 40 IRE<sub>PP</sub>, 3.58 MHz, IRE =0 volts, at 75 $\Omega$  load. See text.

(4) AJ-level: spec. is 100% tested at +25°C, sample at 85°C.

SNOS854D-AUGUST 2000-REVISED APRIL 2013

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

$A_V = +2$ ,  $V_{CC} = \pm 5V$ ,  $R_L = 100\Omega$ ,  $R_f = 250\Omega$ ; unless specified

| Symbol    | Parameter                     | Conditions            | Тур  | Max/Min <sup>(1)</sup> |       | Units |    |

|-----------|-------------------------------|-----------------------|------|------------------------|-------|-------|----|

| PSRR      | Power Supply Rejection Ratio  |                       | 50   | >45                    | >45   | >45   | dB |

| CMRR      | Common Mode Rejection Ratio   |                       | 50   | >45                    | >45   | >45   | dB |

| ICC       | Supply Current <sup>(4)</sup> | No Load, Quiescent    | 16   | <18                    | <18   | <18   | mA |

| ISD       | Supply Current, Disabled      | No Load, Quiescent    | 4    | <6 <6 <6               |       | <6    | mA |

| Miscellan | eous Performance              |                       |      |                        |       |       |    |

| RIN       | Non-Inverting Input           | Resistance            | 200  | >50                    | >100  | >100  | kΩ |

| CIN       |                               | Capacitance           | 0.5  | <2                     | <2    | <2    | pF |

| RO        | Output Impedance              | At DC                 | 0.1  | <0.2                   | <0.2  | <0.2  | Ω  |

| ROD       | Output Impedance, Disabled    | Resistance, at DC     | 200  | <100                   | <100  | <100  | kΩ |

| COD       |                               | Capacitance,at DC     | 0.5  | <2                     | <2    | <2    | pF |

| VO        | Output Voltage Range          | No Load               | ±3.5 | >±3                    | >±3.2 | >±3.2 | V  |

| CMIR      | Common Mode Input Range       | For Rated Performance | ±2.1 | >±1.2                  | >±2   | >±2   | V  |

| Ю         | Output Current                | -40°C to +85°C        | ±70  | >±35                   | >±50  | >±50  | mA |

| Ю         | _                             | -55°C to +125°C       | ±60  | >±30                   | >±50  | >±50  | mA |

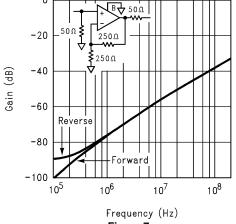

$(T_{A}$  = 25°,  $A_{V}$  = +2,  $V_{CC}$  = ±5V,  $R_{L}$  = 100 $\Omega;$  Unless Specified).

Figure 6.

SNOS854D - AUGUST 2000 - REVISED APRIL 2013

Forward and Reverse Gain During Disable

10<sup>7</sup>

50

50

40

30 g

10

0

R 20

SNOS854D-AUGUST 2000-REVISED APRIL 2013

www.ti.com

6

SNOS854D - AUGUST 2000 - REVISED APRIL 2013

2

Number of 150Ω Loads **Figure 18.**

3

0

4

0

1

Texas Instruments

SNOS854D-AUGUST 2000-REVISED APRIL 2013

www.ti.com

# ENABLE/DISABLE OPERATION

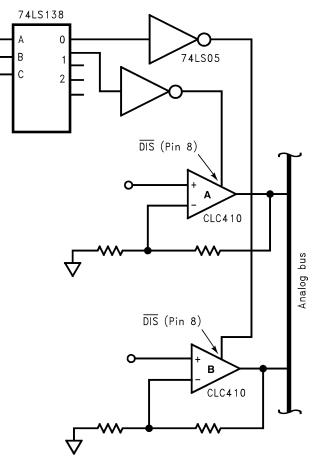

The CLC410 has an enable/disable feature that is useful for conserving power and for multiplexing the outputs of several amplifiers onto an analog bus (Figure 21). Disabling an amplifier while not in use reduces power supply current and the output and inverting input pins become a high impedance.

CLC410

www.ti.com

Figure 21.

TEXAS INSTRUMENTS

www.ti.com

SNOS854D-AUGUST 2000-REVISED APRIL 2013

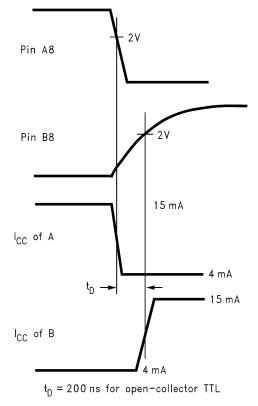

#### Figure 22.

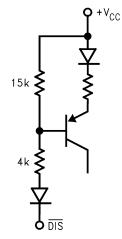

Pin 8, the  $\overline{\text{DIS}}$  pin, can be driven from either open-collector TTL or from 5V CMOS. A logic low disables the amplifier and an internal 15k $\Omega$  pull-up resistor ensures that the amplifier is enabled if pin 8 is not connected (Figure 23). Both TTL and 5V CMOS logic are ensured to drive a high enough high-level output voltage (V<sub>OH</sub>) to ensure that the CLC410 is enabled. Whichever type used, "break-before-make" operation should be established when outputs of several amplifiers are connected together. This is important for avoiding large, transient currents flowing between amplifiers when two or more are simultaneously enabled. Typically, proper operation is ensured if all the amplifiers are driven from the same decoder integrated circuit because logic output rise times tend to be longer than fall times. As a result, the amplifier being disabled will reach the 2V threshold sooner than the amplifier being enabled (see t<sub>D</sub> of Figure 22 timing diagram).

Figure 23. Equivalent of DIS input

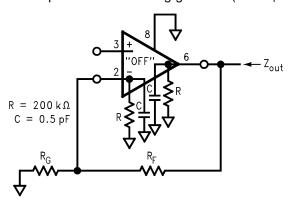

During disable, supply current drops to approximately 4mA and the inverting input and output pin impedances become  $200k\Omega||0.5pF$  each. The total impedance that a disabled amplifier and its associated feedback network presents to the analog bus is determined from Figure 24. For example, at a non-inverting gain of 1, the output impedance at video frequencies is  $100k\Omega||1pF$  since the  $250\Omega$  feedback resistor is a negligible impedance. Similarly, output impedance is  $500\Omega||0.5pF$  at a non-inverting gain of 2 (with  $R_f = R_g = 250\Omega$ ).

Figure 24.

## DIFFERENTIAL GAIN AND PHASE

Plots on the preceding page illustrate the differential gain and phase performance of the CLC410 at both 3.58MHz and 4.43MHz. Application Note OA-08 presents a measurement technique for measuring the very low differential gain and phase of the CLC410. Observe that the gain and phase errors remain low even as the output loading increases, making the device attractive for driving multiple video outputs.

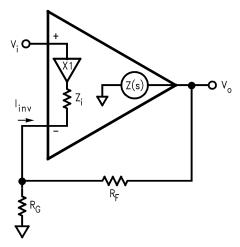

## UNDERSTANDING THE LOOP GAIN

The CLC410 is a current-feedback op amp. Referring to the equivalent circuit of Figure 26, any current flowing in the inverting input is amplified to a voltage at the output through the transimpedance gain shown below. This Z(s) is analogous to the open-loop gain of a voltage feedback amplifier.

Figure 25. Open-Loop Transimpedance Gain, Z(s)

# CLC410

SNOS854D-AUGUST 2000-REVISED APRIL 2013

12

Developing the non-inverting frequency response for the topology of Figure 21 yields:

$$\frac{V_{O}}{V_{i}} = \frac{1 + R_{f} / R_{g}}{1 - 1 / LG}$$

where LG is the loop gain defined by,

**—** / 、

$$LG = \frac{Z(s)}{R_f} \times \frac{1}{1 + Z_i / (R_f IIR_g)}$$

Equation 1 has a form identical to that for a voltage feedback amplifier with the differences occurring in the LG expression, eq.2. For an idealized treatment, set  $Z_i = 0$  which results in a very simple LG=Z(s)/R<sub>f</sub> (Derivation of the transfer function for the case where  $Z_i = 0$  is given in Application Note AN300-1). Using the Z(s) (open-loop transimpedance gain) plot shown on the previous page and dividing by the recommended R<sub>f</sub> = 250 $\Omega$ , yields a large loop gain at DC. As a result, Equation 1 shows that the closed-loop gain at DC is very close to  $(1+R_f/R_g)$ .

Figure 26. Current Feedback Topology

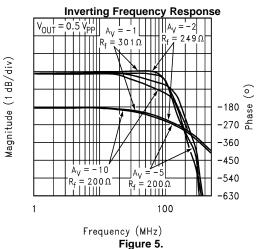

At higher frequencies, the roll-off of Z(s) determines the closed-loop frequency response which, ideally, is dependent only on R<sub>f</sub>. The specifications reported on the previous pages are therefore valid only for the specified  $R_f = 250\Omega$ . Increasing R<sub>f</sub> from 250 $\Omega$  will decrease the loop gain and band width, while decreasing it will increase the loop gain possibly leading to inadequate phase margin and closed-loop peaking. Conversely, fixing R<sub>f</sub> will hold the frequency response constant while the closed-loop gain can be adjusted using R<sub>q</sub>.

The CLC410 departs from this idealized analysis to the extent that the inverting input impedance is finite. With the low quiescent power of the CLC410,  $Z_i \approx 50\Omega$  leading to drop in loop gain and bandwidth at high gain settlings, as given by Equation 2. The second term in Equation 2 accounts for the division in feedback current that occurs between  $Z_i$  and  $R_f \| R_g$  at the inverting node of the CLC410. This decrease in bandwidth can be circumvented as described in "Increasing Bandwidth at High Gains." Also see "Current Feedback Amplifiers" in the TI Databook for a thorough discussion of current feedback op amps.

# **INCREASING BANDWIDTH AT HIGH GAINS**

Bandwidth may be increased at high closed-loop gains by adjusting  $R_f$  and  $R_g$  to make up for the losses in loop gain that occur at these high gain settlings due to current division at the inverting input. An approximate relationship may be obtained by holding the LG expression constant as the gain is changed from the design point used in the specifications (that is,  $R_f = 250\Omega$  and  $R_g = 250\Omega$ ). For the CLC400 this gives,

www.ti.com

(1)

(2)

where

• Avis the non-inverting gain

(3)

(4)

Note that with  $A_V = +2$  we get the specified  $R_f = 250\Omega$ , while at higher gains, a lower value gives stable performance with improved bandwidth.

# DC ACCURACY AND NOISE

Since the two inputs for the CLC410 are quite dissimilar, the noise and offset error performance differs somewhat from that of a standard differential input amplifier. Specifically, the inverting input current noise is much larger than the non-inverting current noise. Also the two input bias currents are physically unrelated rendering bias current cancellation through matching of the inverting and non-inverting pin resistors ineffective.

In Equation 4, the output offset is the algebraic sum of the equivalent input voltage and current sources that influence DC operation. Output noise is determined similarly except that a root-sum-of-squares replaces the algebraic sum.  $R_s$  is the non-inverting pin resistance.

### Equation

Output Offset  $V_0 = \pm IBN \times R_s(1 + R_f/R_g) \pm VIO (1 + R_f/R_g) \pm IBI \times R_f$

An important observation is that for fixed  $R_f$ , offsets as referred to the input improve as the gain is increased (divide all terms by  $1+R_f/R_g$ ). A similar result is obtained for noise where noise figure improves as a gain increases.

The input noise plot shown in the CLC400 datasheet applies equally as well to the CLC410.

# CAPACITIVE FEEDBACK

Capacitive feedback should not be used with the CLC410 because of the potential for loop instability. See Application Note OA-7 for active filter realizations with the CLC410.

# OFFSET ADJUSTMENT PIN

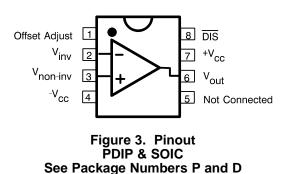

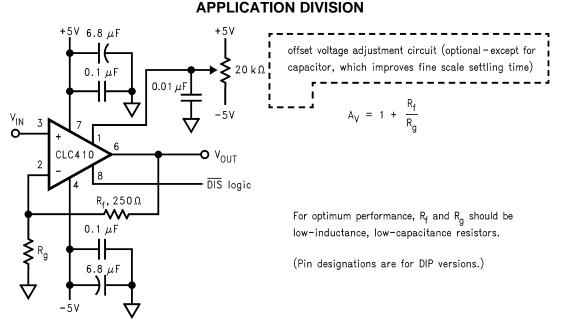

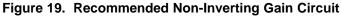

Pin 1 can be connected to a potentiometer as shown in Figure 19 and used to adjust the input offset of the CLC410. Full range adjustment of  $\pm 5V$  on pin 1 will yield a  $\pm 10$ mV input offset adjustment range. Pin 1 should always be bypassed to ground with a ceramic capacitor located close to the package for best settling performance.

# PRINTED CIRCUIT LAYOUT

As with any high frequency device, a good PCB layout will enhance performance. Ground plane construction and good power supply bypassing close to the package are critical to achieving full performance. In the non-inverting configuration, the amplifier is sensitive to stray capacitance to ground at the inverting input. Hence, the inverting node connections should be small with minimal coupling to the ground plane. Shunt capacitance across the feedback resistor should not be used to compensate for this effect.

SNOS854D-AUGUST 2000-REVISED APRIL 2013

www.ti.com

Parasitic or load capacitance directly on the output will introduce additional phase shift in the loop degrading the loop phase margin and leading to frequency response peaking. A small series resistor before the capacitance effectively decouples this effect. The graphs on the preceding page illustrates the required resistor value and resulting performance vs. capacitance.

Precision buffed resistors (PRP8351 series from Precision Resistive Products) with low parasitic reactances were used to develop the data sheet specifications. Precision carbon composition resistors will also yield excellent results. Standard spirally-trimmed RN55D metal film resistors will work with a slight decrease in bandwidth due to their reactive nature at high frequencies.

Evaluation PC boards (part no. 730013 for through-hole and 730027 for SOIC) for the CLC404 are available.

#### SNOS854D - AUGUST 2000 - REVISED APRIL 2013

## **REVISION HISTORY**

| Ch | anges from Revision C (April 2013) to Revision D   | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 14   |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated