# LMP8358 Zero-Drift, Programmable Instrumentation Amplifier with Diagnostics

Check for Samples: LMP8358

## **FEATURES**

Typical Values Unless Otherwise Noted,  $T_A = 25^{\circ}C$

- Supply Voltage 2.7V to 5.5V

- Supply Current 1.8 mA

- Max Gain Error 0.15%

- Max Gain Drift 16 ppm/°C

- Min CMRR 110 dB

- Max Offset Voltage 10 μV

- Max Offset Voltage Drift 50 nV/°C

- GBW (Gain = 10) 8 MHz

- Max Non-Linearity 100 ppm

- Operating Temperature Range -40°C to 125°C

- Input Fault Detection

- SPI or Pin Configurable Modes

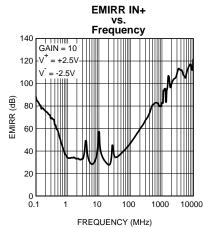

- EMIRR at 1.8GHz 92 dB

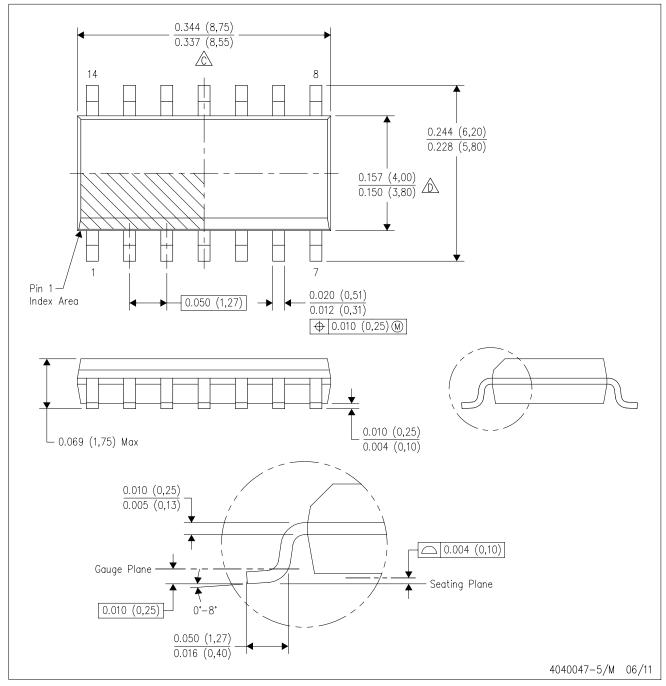

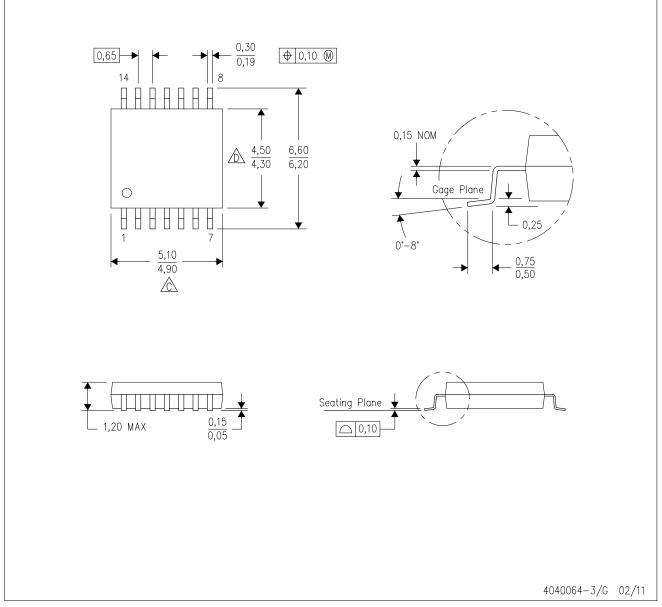

- 14-Pin SOIC and 14-Pin TSSOP Package

### APPLICATIONS

- Bridge Sensor Amplifier

- Thermopile Amplifier

- Portable Instrumentation

- Medical Instrumentation

- Precision Low-side Current Sensing

### DESCRIPTION

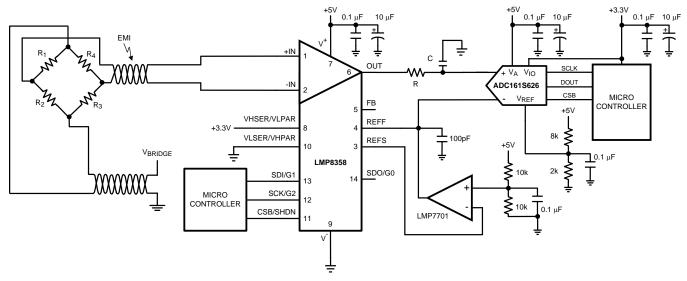

The LMP8358 is a precision programmable-gain instrumentation amplifier in TI's LMP™ precision amplifier family. Its gain can be programmed to 10, 20, 50, 100, 200, 500, or 1000 through an SPIcompatible serial interface or through a parallel interface. Alternatively, its gain can be set to an arbitrary value using two external resistors. The LMP8358 uses patented techniques to measure and continuously correct its input offset voltage, eliminating offset drift over time and temperature and the effect of 1/f noise. Its ground-sensing CMOS input features a high CMRR and low input bias currents. It is capable of sensing differential input voltages in a common-mode range that extends from 100mV below the negative supply to 1.4V below the positive supply, making it an ideal solution for interfacing with groundsensors, referenced supply-referenced bridges, and any other application requiring precision and long-term stability. Additionally, the LMP8358 includes fault detection circuitry to detect open and shorted inputs and deteriorating connections to the signal source. Other features that make the LMP8358 a versatile solution for many applications are its railto-rail output, low input voltage noise and high gainbandwidth product.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LMP is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

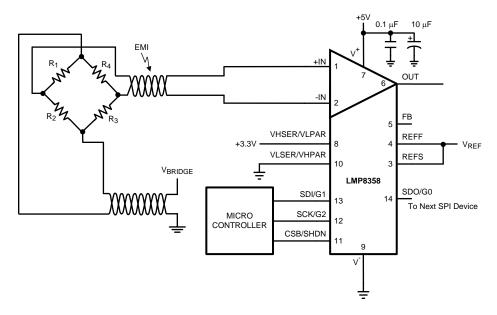

# **Typical Application**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)

| Absolute Maximum Ratings                                            |                                                           |                |

|---------------------------------------------------------------------|-----------------------------------------------------------|----------------|

| ESD Tolerance (3)                                                   | Human Body Model                                          | 2kV            |

|                                                                     | Machine Model                                             | 200V           |

|                                                                     | Charge Device                                             | 1kV            |

| V <sub>IN</sub> Differential (V <sub>+IN</sub> - V <sub>-IN</sub> ) |                                                           | V <sub>S</sub> |

| Output Short Circuit Duration (4)                                   |                                                           |                |

| Any pin relative to V                                               |                                                           | 6V, −0.3V      |

| +IN, -IN, OUT Pins                                                  | V+ +0.3V, V⁻ −0.3V                                        |                |

| +IN, -IN Pins                                                       |                                                           | ±10 mA         |

| Storage Temperature Range                                           |                                                           | −65°C to 150°C |

| Junction Temperature <sup>(5)</sup>                                 |                                                           | 150°C          |

| For soldering specifications: see produc                            | t folder at www.ti.com and http://www.ti.com/lit/SNOA549. | ,              |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not ensured. For ensured specifications and the test conditions, see Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22–A115–A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22–C101–C (ESD FICDM std. of JEDEC).

- (4) The short circuit test is a momentary test which applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can exceed the maximum allowable junction temperature of 150°C.

- (5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

www.ti.com

# Operating Ratings (1)

| Temperature Range                                                   |              | -40°C to 125°C |

|---------------------------------------------------------------------|--------------|----------------|

| Supply Voltage $(V_S = V^+ - V^-)$                                  |              | 2.7V to 5.5V   |

| V <sub>IN</sub> Differential (V <sub>+IN</sub> - V <sub>-IN</sub> ) |              | ±100mV         |

| Package Thermal Resistance (θ <sub>JA</sub> <sup>(2)</sup> )        | 14-Pin SOIC  | 145°C/W        |

|                                                                     | 14-Pin TSSOP | 135°C/W        |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not ensured. For ensured specifications and the test conditions, see Electrical Characteristics.

### 3.3V Electrical Characteristics

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C.  $V^+$  = 3.3V ,  $V^-$  = 0V,  $V_{REF}$  =  $V^+/2$ ,  $V_{CM}$  =  $V^+/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_{REF}$ ,  $C_L$  = 10 pF; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                             | Conditions                                                         | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units              |

|-------------------|-------------------------------------------------------|--------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|

| Vos               | Input Offset Voltage                                  | $V_{CM} = V^+/2$                                                   |                    | 1                  | 10<br><b>15</b>    | μV                 |

|                   |                                                       | $V_{CM} = 0V$                                                      |                    | 1                  | 10<br><b>15</b>    | μν                 |

| TCV <sub>OS</sub> | Input Offset Voltage Temperature Drift <sup>(3)</sup> | $V_{CM} = V^+/2$                                                   |                    |                    | 50                 | nV/°C              |

|                   |                                                       | $V_{CM} = 0V$                                                      |                    |                    | 50                 | IIV/ C             |

| CMRR              | Common Mode Rejection Ratio                           | $V^ 0.1V \le V_{CM} \le V^+ - 1.4V$                                | 110<br><b>105</b>  | 139                |                    | dB                 |

| CMVR              | Common Mode Voltage Range                             | CMRR ≥ 110 dB                                                      | -0.1               |                    | 1.9                | V                  |

| $V_{REF}RR$       | V <sub>REF</sub> Rejection Ratio                      | $V^- + 0.1V \le V_{REFF} \le V^+ - 1.4V$                           | 110<br><b>105</b>  | 145                |                    | dB                 |

| PSRR              | Power supply Rejection Ratio                          | 2.7V ≤ V <sup>+</sup> ≤ 5.5V                                       | 112<br><b>105</b>  | 138                |                    | dB                 |

| EMIRR             | Electro Magnetic Interference Rejection               | $+IN / -IN$ , $V_{RF} = 100 \text{ mV}_P$ , $f = 900 \text{ MHz}$  |                    | 83                 |                    | dB                 |

|                   | Ratio                                                 | $+IN / -IN$ , $V_{RF} = 100 \text{ mV}_P$ , $f = 1800 \text{ MHz}$ |                    | 93                 |                    | uБ                 |

| $Z_{INDM}$        | Differential Input Impedance                          |                                                                    |                    | 50  1              |                    | MΩ II pF           |

| Z <sub>INCM</sub> | Common Mode Input Impedance                           |                                                                    |                    | 50  1              |                    | MΩ ∥ pF            |

| $V_{INDM}$        | Differential Mode Input Voltage                       |                                                                    |                    |                    | ±100               | mV                 |

| I <sub>B</sub>    | Input Bias Current                                    |                                                                    |                    | 0.006              | 1.2<br><b>2</b>    | nA                 |

| los               | Input Offset Current                                  |                                                                    |                    | 0.1                | 112                | pА                 |

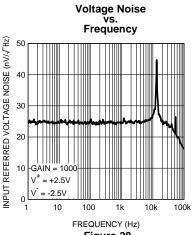

| e <sub>n</sub>    | Input Voltage Noise Density                           | Gain = 10, f = 1 kHz                                               |                    | 27                 |                    |                    |

|                   |                                                       | Gain = 20, f = 1 kHz                                               |                    | 31                 |                    |                    |

|                   |                                                       | Gain = 50, f = 1 kHz                                               |                    | 28                 |                    |                    |

|                   |                                                       | Gain = 100, f = 1 kHz                                              |                    | 27                 |                    | nV/√ <del>Hz</del> |

|                   |                                                       | Gain = 200, f = 1 kHz                                              |                    | 28                 |                    | 110/1112           |

|                   |                                                       | Gain = 500, f = 1 kHz                                              |                    | 28                 |                    |                    |

|                   |                                                       | Gain = 1000, f = 1 kHz                                             |                    | 27                 |                    |                    |

|                   |                                                       | Gain = External, f = 1 kHz                                         |                    | 27                 |                    |                    |

<sup>(2)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical Values indicate the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(3)</sup> The offset voltage average drift is determined by dividing the value of V<sub>OS</sub> at the temperature extremes by the total temperature change.

# 3.3V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C.  $V^+$  = 3.3V ,  $V^-$  = 0V,  $V_{REF}$  =  $V^+/2$ ,  $V_{CM}$  =  $V^+/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_{REF}$ ,  $C_L$  = 10 pF; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                          | Conditions                                                                                                                | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup>  | Units              |

|----------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------|--------------------|

| e <sub>n</sub> | Input Voltage Noise                | Gain = 10, 0.1 Hz < f < 10 Hz                                                                                             |                    | 0.9                |                     |                    |

|                |                                    | Gain = 20, 0.1 Hz < f < 10 Hz                                                                                             |                    | 0.6                |                     |                    |

|                |                                    | Gain = 50, 0.1 Hz < f < 10 Hz                                                                                             |                    | 0.6                |                     |                    |

|                |                                    | Gain = 100, 0.1 Hz < f < 10 Hz                                                                                            |                    | 0.7                |                     |                    |

|                |                                    | Gain = 200, 0.1 Hz < f < 10 Hz                                                                                            |                    | 0.6                |                     | $\mu V_{PP}$       |

|                |                                    | Gain = 500, 0.1 Hz < f < 10 Hz                                                                                            |                    | 0.6                |                     |                    |

|                |                                    | Gain = 1000, 0.1 Hz < f < 10 Hz                                                                                           |                    | 0.6                |                     |                    |

|                |                                    | Gain = External, 0.1 Hz < f < 10 Hz                                                                                       |                    | 0.6                |                     |                    |

| In             | Input Current Noise Density        | Gain = 100, f = 1 kHz                                                                                                     |                    | 0.5                |                     | pA/√ <del>Hz</del> |

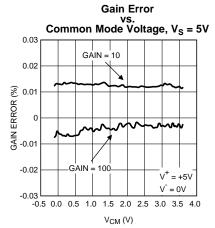

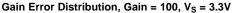

| G <sub>E</sub> | Gain Error                         | Gain = 10, 20, 50, 100, 200, 500<br>V <sub>OUT</sub> = V <sub>REF</sub> + 1V and V <sub>OUT</sub> = V <sub>REF</sub> - 1V |                    | 0.03               | 0.1<br><b>0.15</b>  | %                  |

| G <sub>E</sub> | Gain Error                         | Gain = 1000<br>$V_{OUT} = V_{REF} + 1V$ and $V_{OUT} = V_{REF} - 1V$                                                      |                    | 0.03               | 0.15<br><b>0.25</b> | %                  |

| G <sub>E</sub> | Gain Error Contribution from Chip  | $V_{OUT} = V_{REF} + 1V$ and $V_{OUT} = V_{REF} - 1V$                                                                     |                    | 0.03               |                     | %                  |

|                | Gain Error Temperature Coefficient | For all gain settings (internal and external), $V_{OUT} = V_{REF} + 1V$ and $V_{OUT} = V_{REF} - 1V$                      |                    | 3                  | 16                  | ppm/°C             |

| NL             | Non-Linearity                      |                                                                                                                           |                    | 3.3                | 100                 | ppm                |

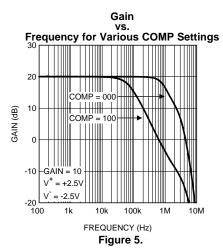

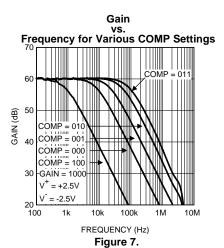

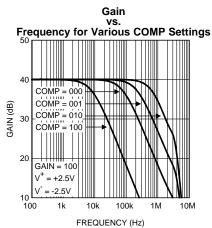

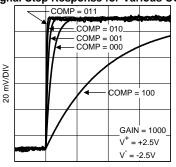

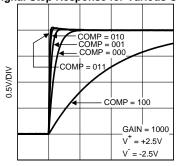

| GBW            | Gain Bandwidth                     | COMP[2:0] =000b, Gain > 10                                                                                                |                    | 8                  |                     |                    |

|                |                                    | COMP[2:0] = 001b, Gain > 30                                                                                               |                    | 24                 |                     |                    |

|                |                                    | COMP[2:0] = 010b, Gain > 200                                                                                              |                    | 80                 |                     | MHz                |

|                |                                    | COMP[2:0] = 011b, Gain > 300                                                                                              |                    | 240                |                     |                    |

|                |                                    | COMP[2:0] = 1xxb, Gain > 1                                                                                                |                    | 0.8                |                     |                    |

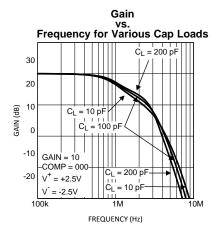

| BW             | −3 dB Bandwidth                    | Gain = 10, COMP[2:0] = 000b                                                                                               |                    | 900                |                     |                    |

|                |                                    | Gain = 10, COMP[2:0] = 1xxb                                                                                               |                    | 70                 |                     |                    |

|                |                                    | Gain = 20, COMP[2:0] = 000b                                                                                               |                    | 400                |                     |                    |

|                |                                    | Gain = 20, COMP[2:0] = 1xxb                                                                                               |                    | 37                 |                     |                    |

|                |                                    | Gain = 50, COMP[2:0] = 001b                                                                                               |                    | 490                |                     |                    |

|                |                                    | Gain = 50, COMP[2:0] = 1xxb                                                                                               |                    | 16                 |                     |                    |

|                |                                    | Gain = 100, COMP[2:0] = 010b                                                                                              |                    | 680                |                     | ld la              |

|                |                                    | Gain = 100, COMP[2:0] = 1xxb                                                                                              |                    | 8                  |                     | kHz                |

|                |                                    | Gain = 200, COMP[2:0] = 010b                                                                                              |                    | 195                |                     |                    |

|                |                                    | Gain = 200, COMP[2:0] = 1xxb                                                                                              |                    | 4                  |                     |                    |

|                |                                    | Gain = 500, COMP[2:0] = 011b                                                                                              |                    | 130                |                     |                    |

|                |                                    | Gain = 500, COMP[2:0] = 1xxb                                                                                              |                    | 1.5                |                     |                    |

|                |                                    | Gain = 1000, COMP[2:0] = 011b                                                                                             |                    | 89                 |                     |                    |

|                |                                    | Gain = 1000, COMP[2:0] = 1xxb                                                                                             |                    | 0.8                |                     |                    |

| SR             | Slew Rate <sup>(4)</sup>           | COMP[2:0] = 000b, 10% to 90% of Step,<br>$V_{OUT} = 2 V_{PP}$                                                             |                    | 1.6                |                     |                    |

|                |                                    | COMP[2:0] = 001b, 10% to 90% of Step, $V_{OUT} = 2 V_{PP}$                                                                |                    | 3.8                |                     |                    |

|                |                                    | COMP[2:0] = 010b, 10% to 90% of Step, $V_{OUT} = 2 V_{PP}$                                                                |                    | 6.5                |                     | V/µs               |

|                |                                    | COMP[2:0] = 011b, 10% to 90% of Step,<br>$V_{OUT} = 2 V_{PP}$                                                             |                    | 9.3                |                     |                    |

|                |                                    | COMP[2:0] = 1xxb, 10% to 90% of Step,<br>$V_{OUT} = 2 V_{PP}$                                                             |                    | 0.17               |                     |                    |

Product Folder Links: LMP8358

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

Slew rate is the average of the rising and falling slew rates. (4)

# 3.3V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}\text{C}$ .  $V^+ = 3.3\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{REF} = V^+/2$ ,  $V_{CM} = V^+/2$ ,  $R_L = 10 \text{ k}\Omega$  to  $V_{REF}$ ,  $C_L = 10 \text{ pF}$ ; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                             | Conditions                                                            | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units                     |

|--------------------|---------------------------------------|-----------------------------------------------------------------------|--------------------|--------------------|--------------------|---------------------------|

| t <sub>s</sub>     | 0.01% Settling Time                   | 2 V Step, C <sub>L</sub> = 10 pF, COMP[2:0] = 011b                    |                    | 4                  |                    | μs                        |

| V <sub>OUT</sub>   | Output Voltage Swing High             | $R_L = 2 k\Omega$ to $V^+/2$                                          |                    |                    | 32<br><b>40</b>    |                           |

|                    |                                       | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                           |                    |                    | 12<br><b>17</b>    | mV from top rail          |

|                    |                                       | $R_L > 1 M\Omega$ to $V^+/2$                                          |                    |                    | 7<br>12            |                           |

|                    | Output Voltage Swing Low              | $R_L = 2 k\Omega$ to $V^+/2$                                          |                    |                    | 28<br><b>38</b>    |                           |

|                    |                                       | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                           |                    |                    | 12<br><b>17</b>    | mV from<br>bottom<br>rail |

|                    |                                       | $R_L > 1 M\Omega$ to $V^+/2$                                          |                    |                    | 8<br><b>13</b>     | Idii                      |

| I <sub>OUT</sub>   | Output Current Sourcing               | V <sub>OUT</sub> tied to V <sup>+</sup> /2                            | 21<br><b>15</b>    | 28                 |                    | - mA                      |

|                    | Output Current Sinking                | V <sub>OUT</sub> tied to V <sup>+</sup> /2                            | 32<br><b>25</b>    | 37                 |                    |                           |

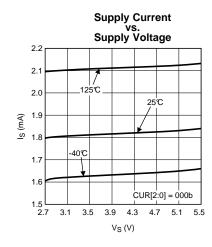

| Is                 | Supply Current                        | Fault detection off, V <sub>IN DIFF</sub> = 0V                        |                    | 1.8                | 2.1                | mA                        |

|                    |                                       | Fault detection on, V <sub>IN DIFF</sub> = 0V                         |                    | 1.9                | 2.2                | mA                        |

|                    |                                       | in Shutdown                                                           |                    | 0.014              | 1                  | μΑ                        |

| T <sub>SD_ON</sub> | Turn-on time from Shutdown            |                                                                       |                    | 85                 |                    | μs                        |

| PSE                | Prescaler Error (Offset + Gain Error) | $V_{CM} = V^+/2$                                                      |                    | 5                  | 15                 | mV                        |

|                    | Prescaler Gain Factor                 |                                                                       |                    | 0.02               |                    | V/V                       |

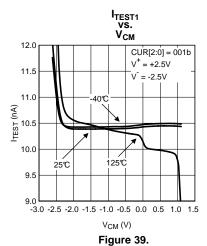

| I <sub>TEST</sub>  | Fault Detection: Test Current         | Setting 1 (CUR[2:0] = 001b), V <sub>CM</sub> < V <sup>+</sup> - 1.15V |                    | 10                 |                    | nA                        |

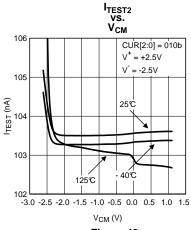

|                    |                                       | Setting 2 (CUR[2:0] = 010b), V <sub>CM</sub> < V <sup>+</sup> - 1.15V |                    | 100                |                    | nA                        |

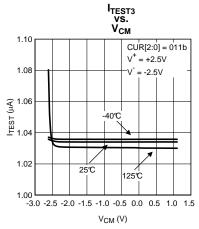

|                    |                                       | Setting 3 (CUR[2:0] = 011b), V <sub>CM</sub> < V <sup>+</sup> - 1.15V |                    | 1                  |                    | μΑ                        |

|                    |                                       | Setting 4 (CUR[2:0] = 100b), V <sub>CM</sub> < V <sup>+</sup> - 1.15V |                    | 10                 |                    | μA                        |

|                    |                                       | Setting 5 (CUR[2:0] = 101b), V <sub>CM</sub> < V <sup>+</sup> - 1.15V |                    | 100                |                    | μA                        |

### 5.0V Electrical Characteristics

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C.  $V^+$  = 5.0V ,  $V^-$  = 0V,  $V_{REF}$  =  $V^+/2$ ,  $V_{CM}$  =  $V^+/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_{REF}$ ,  $C_L$  = 10 pF; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                             | Conditions           | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units  |

|-------------------|-------------------------------------------------------|----------------------|--------------------|--------------------|--------------------|--------|

| V <sub>OS</sub>   | Input Offset Voltage                                  | $V_{CM} = V^+/2$     |                    | 0.9                | 10<br><b>15</b>    | \/     |

|                   |                                                       | V <sub>CM</sub> = 0V |                    | 0.9                | 10<br><b>15</b>    | μV     |

| TCV <sub>OS</sub> | Input Offset Voltage Temperature Drift <sup>(3)</sup> | $V_{CM} = V^+/2$     |                    |                    | 50                 | nV/°C  |

|                   |                                                       | $V_{CM} = 0V$        |                    |                    | 50                 | IIV/*C |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical Values indicate the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(3)</sup> The offset voltage average drift is determined by dividing the value of VOS at the temperature extremes by the total temperature change.

# 5.0V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C.  $V^+$  = 5.0V ,  $V^-$  = 0V,  $V_{REF}$  =  $V^+/2$ ,  $V_{CM}$  =  $V^+/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_{REF}$ ,  $C_L$  = 10 pF; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                               | Conditions                                                                                                                | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup>  | Units              |

|-------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------|--------------------|

| CMRR              | Common Mode Rejection Ratio             | $V^ 0.1V \le V_{CM} \le V^+ - 1.4V$                                                                                       | 116<br><b>105</b>  | 142                |                     | dB                 |

| $V_{REF}RR$       | V <sub>REF</sub> Rejection Ratio        | $V^- + 0.1V \le V_{REFF} \le V^+ - 1.4V$                                                                                  | 115<br><b>105</b>  | 150                |                     | dB                 |

| CMVR              | Common Mode Voltage Range               | CMRR ≥ 115 dB                                                                                                             | -0.1               |                    | 3.6                 | V                  |

| PSRR              | Power supply Rejection Ratio            | 2.7V ≤ V <sup>+</sup> ≤ 5.5V                                                                                              | 112<br><b>105</b>  | 138                |                     | dB                 |

| EMIRR             | Electro Magnetic Interference Rejection | $+IN / -IN$ , $V_{RF} = 100 \text{ mV}_P$ , $f = 900 \text{ MHz}$                                                         |                    | 83                 |                     | ٩D                 |

|                   | Ratio                                   | $+IN / -IN$ , $V_{RF} = 100 \text{ mV}_P$ , $f = 1800 \text{ MHz}$                                                        |                    | 93                 |                     | dB                 |

| $Z_{\text{INDM}}$ | Differential Input Impedance            |                                                                                                                           |                    | 50  1              |                     | MΩ II pF           |

| $Z_{\text{INCM}}$ | Common Mode Input Impedance             |                                                                                                                           |                    | 50  1              |                     | MΩ II pF           |

| $V_{\text{INDM}}$ | Differential Mode Input Voltage         |                                                                                                                           |                    |                    | ±100                | mV                 |

| I <sub>B</sub>    | Input Bias Current                      |                                                                                                                           |                    | 0.006              | 1.2<br><b>2</b>     | nA                 |

| Ios               | Input Offset Current                    |                                                                                                                           |                    | 0.2                | 113                 | pА                 |

| e <sub>n</sub>    | Input Voltage Noise Density             | Gain = 10, f = 1 kHz                                                                                                      |                    | 25                 |                     |                    |

|                   |                                         | Gain = 20, f = 1 kHz                                                                                                      |                    | 28                 |                     |                    |

|                   |                                         | Gain = 50, f = 1 kHz                                                                                                      |                    | 26                 |                     |                    |

|                   |                                         | Gain = 100, f = 1 kHz                                                                                                     |                    | 25                 |                     | nV/√Hz             |

|                   |                                         | Gain = 200, f = 1 kHz                                                                                                     |                    | 28                 |                     |                    |

|                   |                                         | Gain = 500, f = 1 kHz                                                                                                     |                    | 26                 |                     |                    |

|                   |                                         | Gain = 1000, f = 1 kHz                                                                                                    |                    | 25                 |                     |                    |

|                   |                                         | Gain = External, f = 1 kHz                                                                                                |                    | 25                 |                     |                    |

| e <sub>n</sub>    | Input Voltage Noise                     | Gain = 10, 0.1 Hz < f < 10 Hz                                                                                             |                    | 0.7                |                     |                    |

|                   |                                         | Gain = 20, 0.1 Hz < f < 10 Hz                                                                                             |                    | 0.7                |                     |                    |

|                   |                                         | Gain = 50, 0.1 Hz < f < 10 Hz                                                                                             |                    | 0.5                |                     |                    |

|                   |                                         | Gain = 100, 0.1 Hz < f < 10 Hz                                                                                            |                    | 0.6                |                     | \/                 |

|                   |                                         | Gain = 200, 0.1 Hz < f < 10 Hz                                                                                            |                    | 0.6                |                     | $\mu V_{PP}$       |

|                   |                                         | Gain = 500, 0.1 Hz < f < 10 Hz                                                                                            |                    | 0.5                |                     |                    |

|                   |                                         | Gain = 1000, 0.1 Hz < f < 10 Hz                                                                                           |                    | 0.6                |                     |                    |

|                   |                                         | Gain = External, 0.1 Hz < f < 10 Hz                                                                                       |                    | 0.6                |                     |                    |

| In                | Input Current Noise Density             | Gain = 100, f = 1 kHz                                                                                                     |                    | 0.5                |                     | pA/√ <del>Hz</del> |

| G <sub>E</sub>    | Gain Error                              | Gain = 10, 20, 50, 100, 200, 500<br>V <sub>OUT</sub> = V <sub>REF</sub> + 1V and V <sub>OUT</sub> = V <sub>REF</sub> - 1V |                    | 0.03               | 0.1<br><b>0.15</b>  | %                  |

| G <sub>E</sub>    | Gain Error                              | Gain = 1000<br>$V_{OUT} = V_{REF} + 1V$ and $V_{OUT} = V_{REF} - 1V$                                                      |                    | 0.03               | 0.15<br><b>0.25</b> | %                  |

| $G_{E}$           | Gain Error Contribution from chip       | $V_{OUT} = V_{REF} + 1V$ and $V_{OUT} = V_{REF} - 1V$                                                                     |                    | 0.03               |                     | %                  |

|                   | Gain Error Temperature Coefficient      | For all gain settings (internal and external), $V_{OUT} = V_{REF} + 1V$ and $V_{OUT} = V_{REF} - 1V$                      |                    | 3                  | 16                  | ppm/°C             |

| NL                | Non-Linearity                           |                                                                                                                           |                    | 3                  | 100                 | ppm                |

| GBW               | Gain Bandwidth                          | COMP[2:0] = 000b, Gain > 10                                                                                               |                    | 8                  |                     |                    |

|                   |                                         | COMP[2:0] = 001b, Gain > 100                                                                                              |                    | 24                 |                     |                    |

|                   |                                         | COMP[2:0] = 010b, Gain > 200                                                                                              |                    | 80                 |                     | MHz                |

|                   |                                         | COMP[2:0] = 011b, Gain > 500                                                                                              |                    | 240                |                     | IVII IZ            |

|                   |                                         | COMP[2:0] = 1xxb,<br>Gain => 1                                                                                            |                    | 8.0                |                     |                    |

# **5.0V Electrical Characteristics (continued)**

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C.  $V^+$  = 5.0V ,  $V^-$  = 0V,  $V_{REF}$  =  $V^+/2$ ,  $V_{CM}$  =  $V^+/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_{REF}$ ,  $C_L$  = 10 pF; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                             | Conditions                                                                    | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units                     |

|--------------------|---------------------------------------|-------------------------------------------------------------------------------|--------------------|--------------------|--------------------|---------------------------|

| BW                 | -3 dB Bandwidth                       | Gain = 10, COMP[2:0] = 000b                                                   |                    | 930                |                    |                           |

|                    |                                       | Gain = 10, COMP[2:0] = 1xxb                                                   |                    | 74                 |                    |                           |

|                    |                                       | Gain = 20, COMP[2:0] = 000b                                                   |                    | 385                |                    |                           |

|                    |                                       | Gain = 20, COMP[2:0] = 1xxb                                                   |                    | 37                 |                    |                           |

|                    |                                       | Gain = 50, COMP[2:0] = 001b                                                   |                    | 460                |                    |                           |

|                    |                                       | Gain = 50, COMP[2:0] = 1xxb                                                   |                    | 16                 |                    |                           |

|                    |                                       | Gain = 100, COMP[2:0] = 010b                                                  |                    | 640                |                    |                           |

|                    |                                       | Gain = 100, COMP[2:0] = 1xxb                                                  |                    | 8                  |                    | kHz                       |

|                    |                                       | Gain = 200, COMP[2:0] = 010b                                                  |                    | 195                |                    |                           |

|                    |                                       | Gain = 200, COMP[2:0] = 1xxb                                                  |                    | 4                  |                    |                           |

|                    |                                       | Gain = 500, COMP[2:0] = 011b                                                  |                    | 130                |                    |                           |

|                    |                                       | Gain = 500, COMP[2:0] = 1xxb                                                  |                    | 1.5                |                    |                           |

|                    |                                       | Gain = 1000, COMP[2:0] = 011b                                                 |                    | 89                 |                    |                           |

|                    |                                       | Gain = 1000, COMP[2:0] = 1xxb                                                 |                    | 0.8                |                    |                           |

| SR                 | Slew Rate <sup>(4)</sup>              | COMP[2:0] = 000b, 10% to 90% of Step,<br>V <sub>OUT</sub> = 2 V <sub>PP</sub> |                    | 1.7                |                    |                           |

|                    |                                       | COMP[2:0] = 001b, 10% to 90% of Step,<br>V <sub>OUT</sub> = 2 V <sub>PP</sub> |                    | 5.0                |                    |                           |

|                    |                                       | COMP[2:0] = 010b, 10% to 90% of Step, $V_{OUT} = 2 V_{PP}$                    |                    | 9.0                |                    | V/µs                      |

|                    |                                       | COMP[2:0] = 011b, 10% to 90% of Step, $V_{OUT} = 2 V_{PP}$                    |                    | 11.0               |                    |                           |

|                    |                                       | COMP[2:0] = 1xxb, 10% to 90% of Step,<br>$V_{OUT} = 2 V_{PP}$                 |                    | 0.16               |                    |                           |

| t <sub>s</sub>     | 0.01% Settling Time                   | 2 V Step, C <sub>L</sub> = 10 pF, COMP[2:0] = 011b                            |                    | 4                  |                    | μs                        |

| V <sub>OUT</sub>   | Output Voltage Swing High             | $R_L = 2 k\Omega$ to $V^+/2$                                                  |                    |                    | 52<br><b>62</b>    |                           |

|                    |                                       | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                   |                    |                    | 22<br><b>30</b>    | mV from top rail          |

|                    |                                       | $R_L > 1 M\Omega$ to $V^+/2$                                                  |                    |                    | 12<br><b>17</b>    |                           |

|                    | Output Voltage Swing Low              | $R_L = 2 k\Omega \text{ to } V^+/2$                                           |                    |                    | 42<br><b>55</b>    |                           |

|                    |                                       | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                   |                    |                    | 16<br><b>22</b>    | mV from<br>bottom<br>rail |

|                    |                                       | $R_L > 1 M\Omega$ to V <sup>+</sup> /2                                        |                    |                    | 12<br><b>17</b>    |                           |

| I <sub>OUT</sub>   | Output Current Sourcing               | V <sub>OUT</sub> tied to V <sup>+</sup> /2                                    | 23<br><b>16</b>    | 31                 |                    | mA                        |

|                    | Output Current Sinking                | V <sub>OUT</sub> tied to V <sup>+</sup> /2                                    | 34<br><b>30</b>    | 41                 |                    | ША                        |

| $I_S$              | Supply Current                        | Fault detection off, V <sub>IN DIFF</sub> = 0V                                |                    | 1.8                | 2.1                | mA                        |

|                    |                                       | Fault detection on, V <sub>IN DIFF</sub> = 0V                                 |                    | 1.9                | 2.2                | mA                        |

|                    |                                       | in Shutdown                                                                   |                    | 0.006              | 1                  | μΑ                        |

| T <sub>SD_ON</sub> | Turn-on time from Shutdown            |                                                                               |                    | 85                 |                    | μs                        |

| PS <sub>E</sub>    | Prescaler Error (Offset + Gain Error) | $V_{CM} = V^{+}/2$                                                            |                    | 5                  | 8                  | mV                        |

|                    | Prescaler Gain Factor                 |                                                                               |                    | 0.02               |                    | V/V                       |

<sup>(4)</sup> Slew rate is the average of the rising and falling slew rates.

# 5.0V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A$  = 25°C.  $V^+$  = 5.0V ,  $V^-$  = 0V,  $V_{REF}$  =  $V^+/2$ ,  $V_{CM}$  =  $V^+/2$ ,  $R_L$  = 10 k $\Omega$  to  $V_{REF}$ ,  $C_L$  = 10 pF; Serial Control Register: G[2:0] = 110b (Gain = 1000x), COMP[2:0] = 000b, MUX[1:0] = 00b, POL, SHDN, FILT, PIN = 0b, CUR[2:0] = 000b. **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter | Conditions                                                            | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |

|-------------------|-----------|-----------------------------------------------------------------------|--------------------|--------------------|--------------------|-------|

| I <sub>TEST</sub> | 01        | Setting 1 (CUR[2:0] = 001b), V <sub>CM</sub> < V <sup>+</sup> - 2.25V |                    | 10                 |                    | nA    |

|                   |           | Setting 2 (CUR[2:0] = 010b), V <sub>CM</sub> < V <sup>+</sup> - 2.25V |                    | 100                |                    | nA    |

|                   |           | Setting 3 (CUR[2:0] = 011b), V <sub>CM</sub> < V <sup>+</sup> - 2.25V |                    | 1                  |                    | μA    |

|                   |           | Setting 4 (CUR[2:0] = 100b), V <sub>CM</sub> < V <sup>+</sup> - 2.25V |                    | 10                 |                    | μA    |

|                   |           | Setting 5 (CUR[2:0] = 101b), V <sub>CM</sub> < V <sup>+</sup> - 2.25V |                    | 100                |                    | μΑ    |

# **Electrical Characteristics (Serial Interface)**

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V^+ - V^- \ge 2.7V$ ,  $V^+ \ge VHSER/VLPAR$ ,  $V^- \le VLSER/VHPAR$ ,  $V_D = (VHSER/VLPAR) - (VLSER/VHPAR) \ge 2.5V$ .

| Symbol                         | Parameter                                       | Conditions                                                          | Min <sup>(1)</sup>    | Typ <sup>(2)</sup> | Max <sup>(1)</sup>   | Units |

|--------------------------------|-------------------------------------------------|---------------------------------------------------------------------|-----------------------|--------------------|----------------------|-------|

| V <sub>IL</sub>                | Input Logic Low Threshold                       |                                                                     |                       |                    | 0.3 × V <sub>D</sub> | V     |

| V <sub>IH</sub>                | Input Logic High Threshold                      |                                                                     | $0.7 \times V_D$      |                    |                      | V     |

| V <sub>OL</sub>                | Output Logic Low Threshold                      | I <sub>SDO</sub> = 2mA                                              |                       |                    | 0.2                  | V     |

| V <sub>OH</sub>                | Output Logic High Threshold                     | I <sub>SDO</sub> = 2mA                                              | V <sub>D</sub> - 0.2V |                    |                      |       |

| I <sub>SDO</sub>               | Output Source Current, SDO                      | $V_D = 3.3V \text{ or } 5.0V,$<br>CSB = 0V, $V_{OH} = V^+ - 0.7V$   | -2                    |                    |                      | A     |

|                                | Output Sink Current, SDO                        | V <sub>D</sub> = 3.3V or 5.0V,<br>CSB = 0V, V <sub>OL</sub> = 1.0V  | 2                     |                    |                      | mA    |

| l <sub>OZ</sub>                | Output Tri-state Leakage Current, SDO           | $V_D = 3.3V \text{ or } 5.0V,$<br>CSB = $V_D = 3.3V \text{ or } 5V$ |                       |                    | ±1                   | μΑ    |

| t <sub>1</sub>                 | High Period, SCK                                | (3)                                                                 | 100                   |                    |                      | ns    |

| t <sub>2</sub>                 | Low Period, SCK                                 | (3)                                                                 | 100                   |                    |                      | ns    |

| t <sub>3</sub>                 | Set Up Time, CSB to SCK                         | (3)                                                                 | 50                    |                    |                      | ns    |

| t <sub>4</sub>                 | Set Up Time, SDI to SCK                         | (3)                                                                 | 30                    |                    |                      | ns    |

| t <sub>5</sub>                 | Hold Time, SCK to SDI                           | (3)                                                                 | 10                    |                    |                      | ns    |

| t <sub>6</sub>                 | Prop. Delay, SCK to SDO                         | (3)                                                                 |                       |                    | 60                   | ns    |

| t <sub>7</sub>                 | Hold Time, SCK Transition to CSB<br>Rising Edge | (3)                                                                 | 50                    |                    |                      | ns    |

| t <sub>8</sub>                 | CSB Inactive                                    | (3)                                                                 | 50                    |                    |                      | ns    |

| t <sub>9</sub>                 | Prop. Delay, CSB to SDO Active                  | (3)                                                                 |                       |                    | 50                   | ns    |

| t <sub>10</sub>                | Prop. Delay, CSB to SDO Inactive                | (3)                                                                 |                       |                    | 50                   | ns    |

| t <sub>11</sub>                | Hold Time, SCK Transition to CSB Falling Edge   | (3)                                                                 | 10                    |                    |                      | ns    |

| t <sub>r</sub> /t <sub>f</sub> | Signal Rise and Fall Times                      | (3)                                                                 | 1.5                   |                    | 5                    | ns    |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical Values indicate the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(3)</sup> Load for these tests is shown in the Timing Diagram Test Circuit.

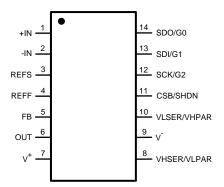

# **Connection Diagram**

Figure 1. 14-Pin SOIC/ 14-Pin TSSOP Top View

# **Pin Descriptions**

| Pin Name       | Communic        | cation Mode            |

|----------------|-----------------|------------------------|

|                | Serial          | Parallel               |

| +IN            | Positiv         | ve Input               |

| -IN            | Negati          | ve Input               |

| REFS           | Referen         | ce Sense               |

| REFF           | Referer         | nce Force              |

| FB             | Fee             | dback                  |

| OUT            | Οι              | ıtput                  |

| V <sup>+</sup> | Positive        | e Supply               |

| VHSER/VLPAR    | Set High        | Set Low                |

| V <sup>-</sup> | Negativ         | re Supply              |

| VLSER/VHPAR    | Set Low         | Set High               |

| CSB/SHDN       | Chip Select     | Shutdown (Active High) |

| SCK/G2         | Serial Clock    | Gain (MSB)             |

| SDI/G1         | Serial Data In  | Gain                   |

| SDO/G0         | Serial Data Out | Gain (LSB)             |

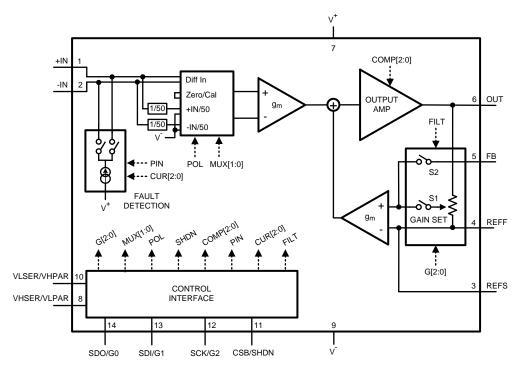

# **Block Diagram**

Figure 2. 14-Pin SOIC/ 14-Pin TSSOP

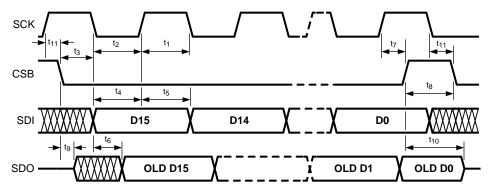

# **Timing Diagrams**

Figure 3. SPI Timing Diagram

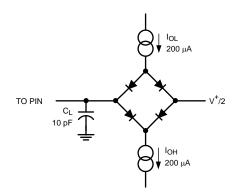

Figure 4. Timing Diagram Test Circuit

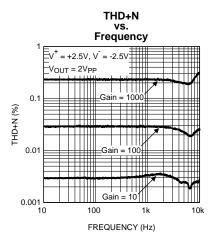

# **Typical Performance Characteristics**

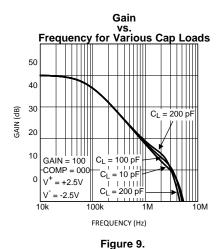

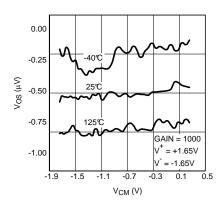

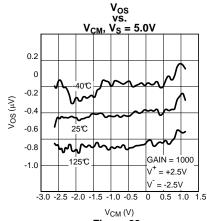

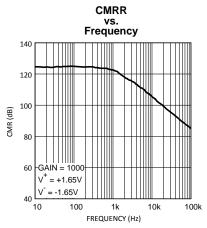

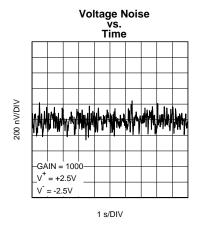

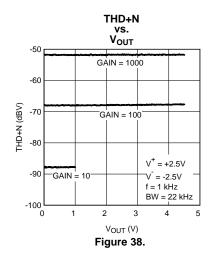

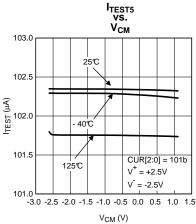

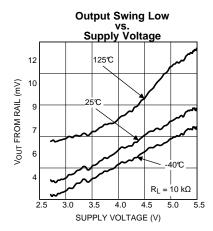

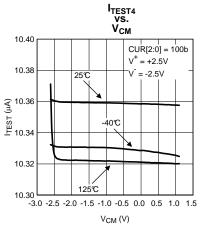

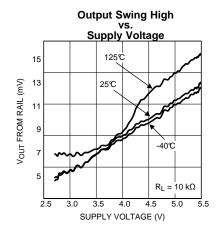

$V^+$  = 3.3V and  $T_A$  = 25°C unless otherwise noted.

Figure 6.

Figure 8.

Figure 10.

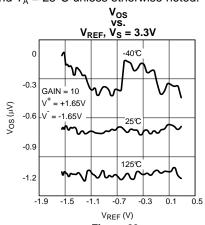

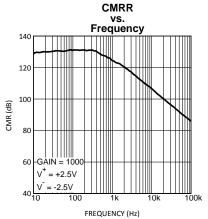

$V^+$  = 3.3V and  $T_A$  = 25°C unless otherwise noted.

Figure 11.

Figure 13.

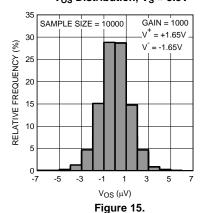

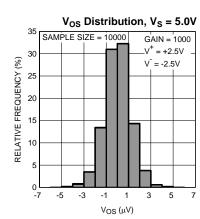

# $V_{OS}$ Distribution, $V_{S} = 3.3V$

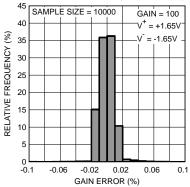

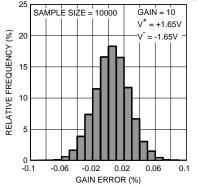

Gain Error Distribution, Gain = 10,  $V_S = 3.3V$

Figure 12.

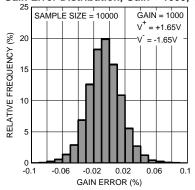

## Gain Error Distribution, Gain = 1000, V<sub>S</sub> = 3.3V

Figure 14.

Figure 16.

$V^+ = 3.3V$  and  $T_A = 25^{\circ}C$  unless otherwise noted.

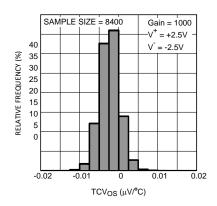

$TCV_{OS}$  Distribution,  $V_S = 3.3V$

Figure 17.

Figure 19.

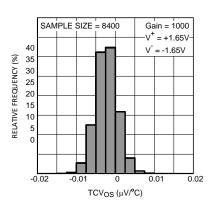

$TCV_{OS}$  Distribution,  $V_S = 5V$

Figure 18.

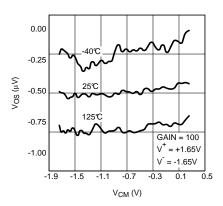

Figure 20.

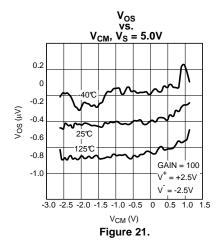

Figure 22.

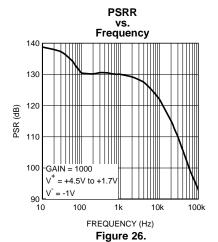

$V^+ = 3.3V$  and  $T_A = 25^{\circ}C$  unless otherwise noted.

Figure 23.

Figure 25.

Figure 27.

Figure 24.

Figure 28.

$V^+$  = 3.3V and  $T_A$  = 25°C unless otherwise noted.

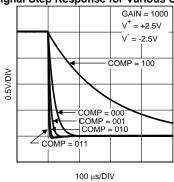

# Small Signal Step Response for Various COMP Settings

Figure 29.

### 100 μs/DIV

## Large Signal Step Response for Various COMP Settings

100 μs/DIV Figure 31.

Figure 33.

## Small Signal Step Response for Various COMP Settings

Figure 30.

### Large Signal Step Response for Various COMP Settings

Figure 32.

Figure 34.

$V^+$  = 3.3V and  $T_A$  = 25°C unless otherwise noted.

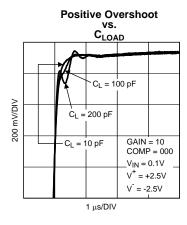

Figure 35.

Figure 37.

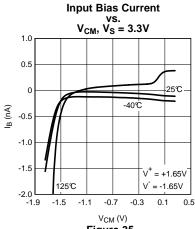

**Input Bias Current** . V<sub>CM</sub>, V<sub>S</sub> = 5.0V 1.0 0.5 I<sub>B</sub> (nA) -40℃ -0.5 -2.0 = +2.5V  $V^{-} = -2.5V$ -3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 V<sub>CM</sub> (V)

Figure 36.

Figure 40.

$V^+$  = 3.3V and  $T_A$  = 25°C unless otherwise noted.

Figure 41.

Figure 43.

Figure 45.

Figure 42.

Figure 44.

Figure 46.

### APPLICATION INFORMATION

### INTRODUCTION

The LMP8358 is a precision programmable gain instrumentation amplifier. Its gain can be programmed to 10, 20, 50, 100, 200, 500 or 1000 through an SPI-compatible serial interface or through a parallel interface. Alternatively, its gain can be set to an arbitrary value using external resistors. Note that at low gains the dynamic range is limited by the maximum input differential voltage of ±100mV. The LMP8358 uses patented techniques to measure and continuously correct its input offset voltage, eliminating offset drift over time and temperature, and the effect of 1/f noise. Its ground sensing CMOS input features a high CMRR and low input bias currents. It is capable of sensing differential input voltages in a common-mode range that extends from 100 mV below the negative supply to 1.4V below the positive supply, making it an ideal solution for interfacing with ground-referenced sensors, supply-referenced sensor bridges, and any other application requiring precision and long term stability. Additionally, the LMP8358 includes fault detection circuitry, so open and shorted inputs can be detected, as well a deteriorating connection to the signal source. Other features that make the LMP8358 a versatile solution for many applications are: its rail-to-rail output, low input voltage noise and high gain-bandwidth product.

### TRANSIENT RESPONSE TO FAST INPUTS

The LMP8358 is a current-feedback instrumentation amplifier that consists of two auto-zeroed input stages. These two input stages are operated in a ping-pong fashion: as one stage is auto-zeroed the other stage provides the path between the input pins and the output. The auto-zeroing decreases offset, offset drift, and 1/f noise while the ping-pong architecture provides a continuous path between the input and the output. As with all devices that use auto-zeroing, care must be taken with the signal frequency used with the device. On-chip continuous auto-zero correction circuitry eliminates the 1/f noise and significantly reduces the offset voltage and offset voltage drift; all of which are very low-frequency events. For slow-changing sensor signals, below 2kHz, this correction is transparent. Higher-frequency signals as well as fast changing edges will show a settling and ramping time lasting about 1µs. Like all auto-zeroing devices, if the input frequency is above the auto-zero frequency, aliasing will occur. This can occur both at the auto-zeroing frequency of about 12kHz and the ping-pong frequency of about 50kHz. If needed, a low-pass filter should be placed on the output of the LMP8358 to filter out this disturbance.

## COMMUNICATION WITH THE PART AND REGISTER DESCRIPTION

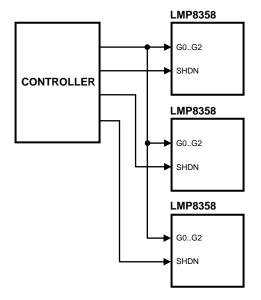

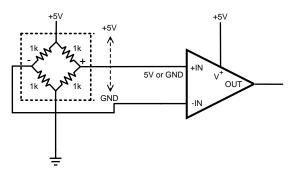

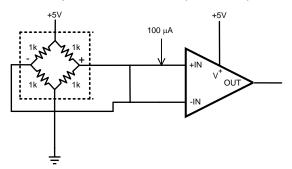

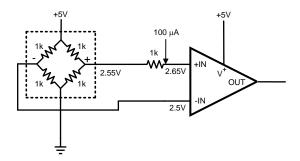

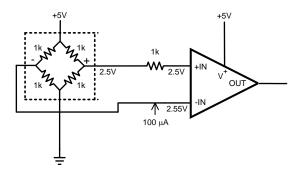

The LMP8358 supports a serial and a parallel digital interface mode as shown in Figure 47 and Figure 48.

**Parallel user mode** Gain is set using G0, G1 and G2 pins. The shutdown mode can be activated by asserting SHDN. Fault detection features are unavailable.

Serial user mode The part is SPI-programmable through SDI, SCK, SDO and CSB. All features are available.

Figure 47. (A) Communication with LMP8358 in Parallel Mode

Figure 48. (B) Communication with LMP8358 in Serial Mode

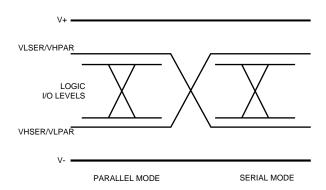

### **Communication Mode Selection**

The interface mode is determined by the two interface level pins VLSER/VHPAR and VHSER/VLPAR.

VLSER/VHPAR < VHSER/VLPAR Serial Interface. VLSER= Logic low level, VHSER = Logic high level.

VLSER/VHPAR > VHSER/VLPAR Parallel interface. VLPAR = Logic low level, VHPAR = Logic high level.

The levels applied to the VLSER/VHPAR and VHSER/VLPAR pins should be between the  $V^+$  and  $V^-$  levels as shown in Figure 49.

Figure 49. Communication Mode Selection.

## PARALLEL CONTROL INTERFACE MODE

The LMP8358 is put into Parallel Mode by setting VLSER/VHPAR > VHSER/VLPAR. The register in the LMP8358 does not control the settings of the LMP8358 in this mode. Gain and shutdown are set by placing a high or low logic level on pins 11 (SHDN), 12 (G2), 13 (G1), and 14 (G0), as shown in Table 1 and Table 2. The logic high and low levels are defined by the voltages on the VLSER/VHPAR and VHSER/VLPAR pins. See the START UP AND POWER ON RESET section for power on requirements when using the parallel mode.

Table 1. Function of Digital IO Pins, Parallel Mode

| Pin Name | Description            |  |

|----------|------------------------|--|

| G0       | Gain setting (LSB)     |  |

| G1       | Gain setting           |  |

| G2       | Gain setting (MSB)     |  |

| SHDN     | Shutdown (Active High) |  |

| VHPAR    | Positive logic level   |  |

| VLPAR    | Negative logic level   |  |

Table 2. Pin Levels for Setting Gain, Parallel Mode

| G2 | G1 | G0 | Gain Setting           | Bandwidth | Compensation Setting (Automatically Set) |

|----|----|----|------------------------|-----------|------------------------------------------|

| 0  | 0  | 0  | 10x (power-up default) | 930 kHz   | 000b                                     |

| 0  | 0  | 1  | 20x                    | 385 kHz   | 000b                                     |

| 0  | 1  | 0  | 50x                    | 460 kHz   | 001b                                     |

| 0  | 1  | 1  | 100x                   | 640 kHz   | 010b                                     |

| 1  | 0  | 0  | 200x                   | 195 kHz   | 010b                                     |

| 1  | 0  | 1  | 500x                   | 130 kHz   | 011b                                     |

| 1  | 1  | 0  | 1000x                  | 89 kHz    | 011b                                     |

| 1  | 1  | 1  | User defined           | 800 kHz   | 1xxb                                     |

# SERIAL CONTROL INTERFACE MODE

The LMP8358 is put into Serial Mode by setting VLSER/VHPAR < VHSER/VLPAR. In the Serial Mode the LMP8358 can be programmed by using pins 11 – 14 as shown in Table 3 and the SPI Timing Diagram. The LMP8358 contains a 16 bit register which controls the performance of the part. These bits can be changed using the Serial Mode of communication. The register of the LMP8358 is shown in Table 4. Immediately after power on the register should be written with the value needed for the application. See the START UP AND POWER ON RESET section.

## Table 3. Function of Digital IO Pins, Serial Mode

| Pin Name | Description          |

|----------|----------------------|

| SDO      | Serial Data Out      |

| SDI      | Serial Data In       |

| SCK      | Serial Clock         |

| CSB      | Chip Select          |

| VLSER    | Negative Logic level |

| VHSER    | Positive Logic Level |

### Table 4. LMP8358 Register Description, Serial Mode

| Bit No | Name  | Description                           |

|--------|-------|---------------------------------------|

| 0      | G0    | Gain setting (LSB)                    |

| 1      | G1    | Gain setting                          |

| 2      | G2    | Gain setting (MSB)                    |

| 3      | COMP0 | Frequency compensation setting (LSB)  |

| 4      | COMP1 | Frequency compensation setting        |

| 5      | COMP2 | Frequency compensation setting (MSB)  |

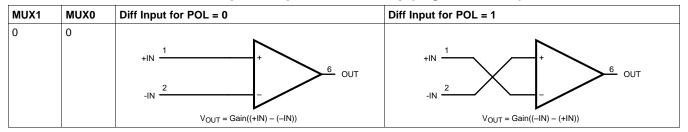

| 6      | MUX0  | Input multiplexer selection (LSB)     |

| 7      | MUX1  | Input multiplexer selection (MSB)     |

| 8      | POL   | Input polarity switch                 |

| 9      | SHDN  | Shutdown Enable                       |

| 10     | FILT  | Enable filtering using external cap   |

| 11     | PIN   | Fault detection pin selection         |

| 12     | CUR0  | Fault detection current setting (LSB) |

| 13     | CUR1  | Fault detection current setting       |

| 14     | CUR2  | Fault detection current setting (MSB) |

| 15     | N/A   | Unused, set to 0                      |

### **Serial Control Interface Operation**

The LMP8358 gain, bandwidth compensation, shutdown, input options, and fault detection are controlled by an on board programmable register. Data to be written into the control register is first loaded into the LMP8358 via the serial interface. The serial interface employs an 16-bit double-buffered register for glitch-free transitions between settings. Data is loaded through the serial data input, SDI. Data passing through the shift register is output through the serial data output, SDO. The serial clock, SCK controls the serial loading process. All sixteen data bits are required to correctly program the amplifier. The falling edge of CSB enables the shift register to receive data. The SCK signal must be high during the falling and rising edge of CSB. Each data bit is clocked into the shift register on the rising edge of SCK. Data is transferred from the shift register to the holding register on the rising edge of CSB. Operation is shown in the SPI Timing Diagram.

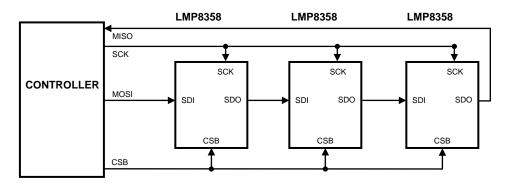

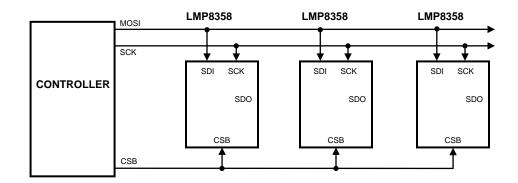

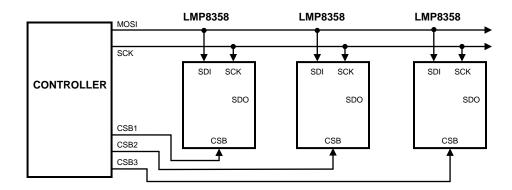

The serial control pins can be connected in one of two ways when two or more LMP8358s are used in an application.

### **Star Configuration**

The configuration shown in Figure 50 can be used if each LMP8358 will always have the same value in each register. After the microcontroller writes, all registers will have the same value. Using multiple CSB lines as shown in Figure 51 allows different values to be written into each register.

Figure 50. Star Configuration for Writing the Same Value Into Each Register

Figure 51. Star Configuration for Writing Different Values Into Each Register

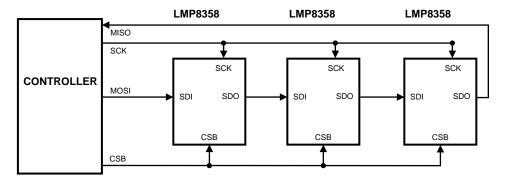

## **Daisy Chain Configuration**

This configuration can be used to program the same or different values in the register of each LMP8358. The connections are shown in Figure 52. In this configuration the SDO pin of each LMP8358 is connected to the SDI pin of the following LMP8358.

Figure 52. Daisy Chain Configuration

The following two examples show how the registers are written in the Daisy Chain Configuration.

Table 5. If all three LMP8358s need a gain of 100 with a compensation level of 010. (0000 0000 0001 0011)

|          | Register of LMP8358 #1 | Register of LMP8358 #2 | Register of LMP8358 #3 | Notes                  |

|----------|------------------------|------------------------|------------------------|------------------------|

| Power on | 0000 0000 0000 0000    | 0000 0000 0000 0000    | 0000 0000 0000 0000    | Default power on state |

# Table 5. If all three LMP8358s need a gain of 100 with a compensation level of 010. (0000 0000 0001 0011) (continued)

| After first two bytes are sent  | 0000 0000 0001 0011 | 0000 0000 0000 0000 | 0000 0000 0000 0000 | The data in the register of LMP8358 #1 is shifted into the register of LMP8358 #2, the data in the register of LMP8358 |  |

|---------------------------------|---------------------|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|--|

| After second two bytes are sent | 0000 0000 0001 0011 | 0000 0000 0001 0011 | 0000 0000 0000 0000 |                                                                                                                        |  |

| After third two bytes are sent  | 0000 0000 0001 0011 | 0000 0000 0001 0011 | 0000 0000 0001 0011 | #2 is shifted into the register of LMP8358 #3.                                                                         |  |

Table 6. If LMP8358 #1 needs a gain of 20 (0000 0000 0000 0001), LMP8358 #2 needs a gain of 1000 with a compensation level of 011 (0000 0000 0001 1110), and LMP8358 #3 needs a gain of 100 with a compensation level of 010 (0000 0000 0001 0011).

|                                 | Register of LMP8358 #1 | Register of LMP8358 #2 | Register of LMP8358 #3 | Notes                                                                |

|---------------------------------|------------------------|------------------------|------------------------|----------------------------------------------------------------------|

| Power on                        | 0000 0000 0000 0000    | 0000 0000 0000 0000    | 0000 0000 0000 0000    | Default power on state                                               |

| After first two bytes are sent  | 0000 0000 0001 0011    | 0000 0000 0000 0000    | 0000 0000 0000 0000    | The data in the register of LMP8358 #1 is shifted                    |

| After second two bytes are sent | 0000 0000 0001 1110    | 0000 0000 0001 0011    | 0000 0000 0000 0000    | into the register of LMP8358 #2, the data in the register of LMP8358 |

| After third two bytes are sent  | 0000 0000 0000 0001    | 0000 0000 0001 1110    | 0000 0000 0001 0011    | #2 is shifted into the register of LMP8358 #3                        |

#### LMP8358 SETTINGS

## Gain (Serial, Parallel)

When the LMP8358 is in Parallel Mode the gain can be set by applying a high or low level to pins 12 (G2), 13 (G1), and 14 (G0), as shown in Table 2. The Frequency Compensation bits are automatically set as shown in Table 2 to optimize the bandwidth. In Serial Mode the gain is determined by setting G[2:0] as shown in Table 7 and the bandwidth can be changed using the Frequency Compensation bits in the register.

Table 7. Gain Setting (Register bits 2:0)

| G2 | G1 | G0 | Gain Setting           |

|----|----|----|------------------------|

| 0  | 0  | 0  | 10x (power-up default) |

| 0  | 0  | 1  | 20x                    |

| 0  | 1  | 0  | 50x                    |

| 0  | 1  | 1  | 100x                   |

| 1  | 0  | 0  | 200x                   |

| 1  | 0  | 1  | 500x                   |

| 1  | 1  | 0  | 1000x                  |

| 1  | 1  | 1  | User Defined           |

When G[2:0] = 000b to 110b switch S1 is closed and switch S2 is open as shown in the Block Diagram.

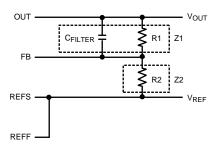

When G[2:0] = 111b in either serial or parallel mode switch S1 is open and S2 is closed and the LMP8358 gain is set by external resistors as shown in Figure 53. The gain is:

GAIN = 1 +

$$(Z1/Z2)$$

(1)

When the gain is set by external resistors and COMP[2:0] = 1xxb, a capacitor can be used to implement a noise reduction low pass filter. See the Filter and External Filter Capacitor (Serial) section. R1and  $C_{FILTER}$  are placed between the OUT and FB pins. R2 is placed between the FB and REFS pins.

Product Folder Links: LMP8358

Figure 53. External Gain Set Resistors and Filter Capacitor

# Frequency Compensation (Serial)