# High Voltage Half-Bridge Gate Driver with Adaptive Delay

Check for Samples: SM74104

### **FEATURES**

- Renewable Energy Grade

- Drives both a High Side and Low Side N-**Channel MOSFET**

- Adaptive Rising and Falling Edges with **Programmable Additional Delay**

- **Single Input Control**

- **Bootstrap Supply Voltage Range up to 118V**

- Fast Turn-Off Propagation Delay (25 ns Typical)

- Drives 1000 pF Loads with 15 ns Rise and Fall **Times**

- **Supply Rail Under-Voltage Lockout**

### TYPICAL APPLICATIONS

- **Current Fed Push-Pull Power Converters**

- **High Voltage Buck Regulators**

- **Active Clamp Forward Power Converters**

- Half and Full Bridge Converters

### DESCRIPTION

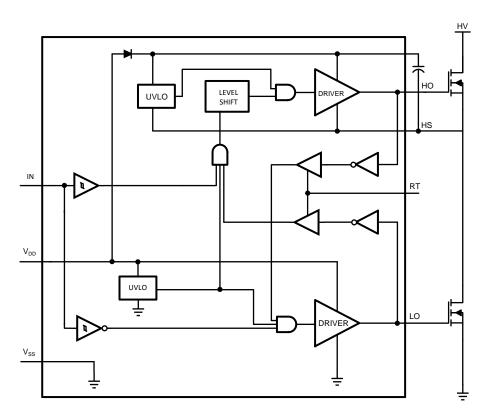

The SM74104 High Voltage Gate Driver is designed to drive both the high side and the low side N-Channel MOSFETs in a synchronous configuration. The floating high-side driver is capable of working with supply voltages up to 100V. The high side and low side gate drivers are controlled from a single input. Each change in state is controlled in an adaptive manner to prevent shoot-through issues. In addition to the adaptive transition timing, an additional delay time can be added, proportional to an external setting resistor. An integrated high voltage diode is provided to charge the high side gate drive bootstrap capacitor. A robust level shifter operates at high speed while consuming low power and providing clean level transitions from the control logic to the high side gate driver. Under-voltage lockout is provided on both the low side and the high side power rails. This device is available in the standard SOIC-8 pin and the WSON-10 pin packages.

### **PACKAGE**

- WSON-10 (4 mm x 4 mm)

- SOIC-8

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

### SIMPLIFIED BLOCK DIAGRAM

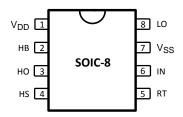

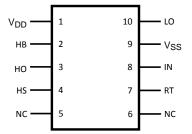

# **Connection Diagrams**

Figure 1. 8-Lead SOIC Package Number D0008A

Figure 2. 10-Lead WSON Package Number DPR0010A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings (1)(2)

| V <sub>DD</sub> to V <sub>SS</sub> | -0.3V to +18V                      |

|------------------------------------|------------------------------------|

| V <sub>HB</sub> to V <sub>HS</sub> | -0.3V to +18V                      |

| IN to V <sub>SS</sub>              | -0.3V to V <sub>DD</sub> + 0.3V    |

| LO Output                          | -0.3V to V <sub>DD</sub> + 0.3V    |

| HO Output                          | $V_{HS}$ – 0.3V to $V_{HB}$ + 0.3V |

| V <sub>HS</sub> to V <sub>SS</sub> | −1V to +100V                       |

| V <sub>HB</sub> to V <sub>SS</sub> | 118V                               |

| RT to V <sub>SS</sub>              | -0.3V to 5V                        |

| Junction Temperature               | +150°C                             |

| Storage Temperature Range          | −55°C to +150°C                    |

| ESD Rating HBM (3)                 | 2 kV                               |

|                                    |                                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) The human body model is a 100 pF capacitor discharged through a 1.5kΩ resistor into each pin. 2 kV for all pins except Pin 2, Pin 3 and Pin 4 which are rated at 500V.

# **Recommended Operating Conditions**

| $V_{DD}$             | +9V to +14V                                   |

|----------------------|-----------------------------------------------|

| HS                   | -1V to 100V                                   |

| НВ                   | V <sub>HS</sub> + 8V to V <sub>HS</sub> + 14V |

| HS Slew Rate         | <50V/ns                                       |

| Junction Temperature | -40°C to +125°C                               |

### **Electrical Characteristics**

Specifications in standard typeface are for  $T_J$  = +25°C, and those in **boldface type** apply over the full **operating junction temperature range**. Unless otherwise specified,  $V_{DD}$  =  $V_{HB}$  = 12V,  $V_{SS}$  =  $V_{HS}$  = 0V, RT = 100k $\Omega$ . No Load on LO or HO.

| Symbol            | Parameter                                | Conditions               | Min  | Тур  | Max  | Units |

|-------------------|------------------------------------------|--------------------------|------|------|------|-------|

| SUPPLY CU         | RRENTS                                   | ·                        | •    | •    | *    | •     |

| I <sub>DD</sub>   | V <sub>DD</sub> Quiescent Current        | LI = HI = 0V             |      | 0.4  | 0.6  | mA    |

| I <sub>DDO</sub>  | V <sub>DD</sub> Operating Current        | f = 500 kHz              |      | 1.9  | 3    | mA    |

| I <sub>HB</sub>   | Total HB Quiescent Current               | LI = HI = 0V             |      | 0.06 | 0.2  | mA    |

| I <sub>HBO</sub>  | Total HB Operating Current               | f = 500 kHz              |      | 1.3  | 3    | mA    |

| I <sub>HBS</sub>  | HB to V <sub>SS</sub> Current, Quiescent | $V_{HS} = V_{HB} = 100V$ |      | 0.05 | 10   | μΑ    |

| I <sub>HBSO</sub> | HB to V <sub>SS</sub> Current, Operating | f = 500 kHz              |      | 0.08 |      | mA    |

| INPUT PINS        |                                          |                          | 1    |      |      |       |

| $V_{IL}$          | Low Level Input Voltage Threshold        |                          | 0.8  | 1.8  |      | V     |

| V <sub>IH</sub>   | High Level Input Voltage Threshold       |                          |      | 1.8  | 2.2  | V     |

| R <sub>I</sub>    | Input Pulldown Resistance                |                          | 100  | 200  | 500  | kΩ    |

| TIME DELAY        | CONTROLS                                 | •                        |      | !    |      |       |

| $V_{RT}$          | Nominal Voltage at RT                    |                          | 2.7  | 3    | 3.3  | V     |

| I <sub>RT</sub>   | RT Pin Current Limit                     | RT = 0V                  | 0.75 | 1.5  | 2.25 | mA    |

| T <sub>D1</sub>   | Delay Timer, RT = 10 kΩ                  |                          | 58   | 90   | 130  | ns    |

| T <sub>D2</sub>   | Delay Timer, RT = 100 kΩ                 |                          | 140  | 200  | 270  | ns    |

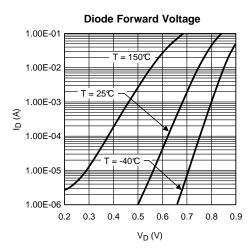

| UNDER VOL         | TAGE PROTECTION                          | •                        |      | !    |      |       |

| $V_{DDR}$         | V <sub>DD</sub> Rising Threshold         |                          | 6.0  | 6.9  | 7.4  | V     |

| $V_{DDH}$         | V <sub>DD</sub> Threshold Hysteresis     |                          |      | 0.5  |      | V     |

| $V_{HBR}$         | HB Rising Threshold                      |                          | 5.7  | 6.6  | 7.1  | V     |

# **Electrical Characteristics (continued)**

Specifications in standard typeface are for  $T_J$  = +25°C, and those in **boldface type** apply over the full **operating junction temperature range**. Unless otherwise specified,  $V_{DD}$  =  $V_{HB}$  = 12V,  $V_{SS}$  =  $V_{HS}$  = 0V, RT = 100k $\Omega$ . No Load on LO or HO.

| Symbol           | Parameter                    | Conditions                                                 | Min | Тур  | Max  | Units |

|------------------|------------------------------|------------------------------------------------------------|-----|------|------|-------|

| $V_{HBH}$        | HB Threshold Hysteresis      |                                                            |     | 0.4  |      | V     |

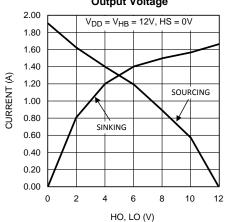

| BOOT STRA        | AP DIODE                     |                                                            |     |      |      |       |

| $V_{DL}$         | Low-Current Forward Voltage  | I <sub>VDD-HB</sub> = 100 μA                               |     | 0.60 | 0.9  | V     |

| $V_{DH}$         | High-Current Forward Voltage | I <sub>VDD-HB</sub> = 100 mA                               |     | 0.85 | 1.1  | V     |

| $R_D$            | Dynamic Resistance           | $I_{VDD-HB} = 100 \text{ mA}$                              |     | 0.8  | 1.5  | Ω     |

| LO GATE DE       | RIVER                        |                                                            |     |      |      |       |

| V <sub>OLL</sub> | Low-Level Output Voltage     | I <sub>LO</sub> = 100 mA                                   |     | 0.25 | 0.4  | V     |

| V <sub>OHL</sub> | High-Level Output Voltage    | $I_{LO} = -100 \text{ mA}$ $V_{OHL} = V_{DD} - V_{LO}$     |     | 0.35 | 0.55 | V     |

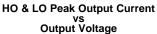

| I <sub>OHL</sub> | Peak Pullup Current          | V <sub>LO</sub> = 0V                                       |     | 1.6  |      | Α     |

| I <sub>OLL</sub> | Peak Pulldown Current        | V <sub>LO</sub> = 12V                                      |     | 1.8  |      | Α     |

| HO GATE DI       | RIVER                        |                                                            |     |      |      |       |

| V <sub>OLH</sub> | Low-Level Output Voltage     | I <sub>HO</sub> = 100 mA                                   |     | 0.25 | 0.4  | V     |

| V <sub>OHH</sub> | High-Level Output Voltage    | $I_{HO} = -100 \text{ mA},$<br>$V_{OHH} = V_{HB} - V_{HO}$ |     | 0.35 | 0.55 | V     |

| I <sub>OHH</sub> | Peak Pullup Current          | V <sub>HO</sub> = 0V                                       |     | 1.6  |      | Α     |

| I <sub>OLH</sub> | Peak Pulldown Current        | V <sub>HO</sub> = 12V                                      |     | 1.8  |      | Α     |

| THERMAL R        | RESISTANCE                   |                                                            |     | •    |      |       |

| $\theta_{JA}$    | Junction to Ambient          | SOIC-8                                                     |     | 170  |      | °C/W  |

|                  |                              | WSON-10 (1)                                                |     | 40   |      | 1     |

<sup>(1) 4</sup> layer board with Cu finished thickness 1.5/1/1/1.5 oz. Maximum die size used. 5x body length of Cu trace on PCB top. 50 x 50mm ground and power planes embedded in PCB. See Application Note AN-1187 SNOA401.

# **Switching Characteristics**

Specifications in standard typeface are for  $T_J$  = +25°C, and those in **boldface type** apply over the full **operating junction temperature range**. Unless otherwise specified,  $V_{DD} = V_{HB} = 12V$ ,  $V_{SS} = V_{HS} = 0V$ , No Load on LO or HO .

| Symbol                            | Parameter                                                   | Conditions                                      | Min | Тур | Max | Units |

|-----------------------------------|-------------------------------------------------------------|-------------------------------------------------|-----|-----|-----|-------|

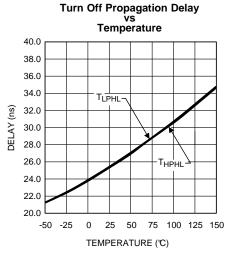

| t <sub>LPHL</sub>                 | Lower Turn-Off Propagation Delay (IN Rising to LO Falling)  |                                                 |     | 25  | 56  | ns    |

| t <sub>HPHL</sub>                 | Upper Turn-Off Propagation Delay (IN Falling to HO Falling) |                                                 |     | 25  | 56  | ns    |

| t <sub>RC</sub> , t <sub>FC</sub> | Either Output Rise/Fall Time                                | C <sub>L</sub> = 1000 pF                        |     | 15  |     | ns    |

| t <sub>R</sub> , t <sub>F</sub>   | Either Output Rise/Fall Time (3V to 9V)                     | C <sub>L</sub> = 0.1 µF                         |     | 0.6 |     | μs    |

| t <sub>BS</sub>                   | Bootstrap Diode Turn-Off Time                               | I <sub>F</sub> = 20 mA, I <sub>R</sub> = 200 mA |     | 50  |     | ns    |

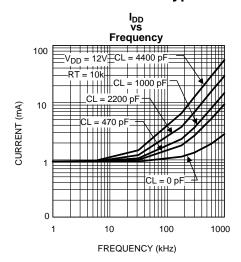

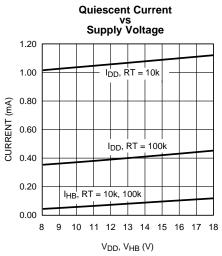

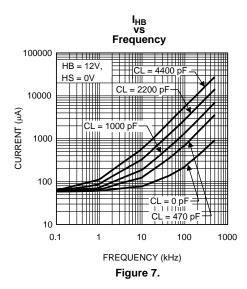

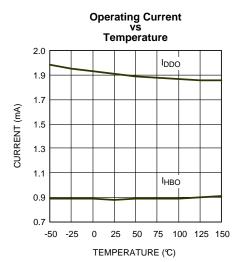

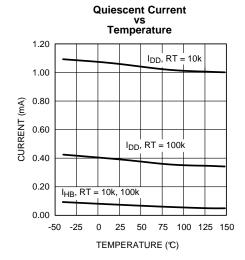

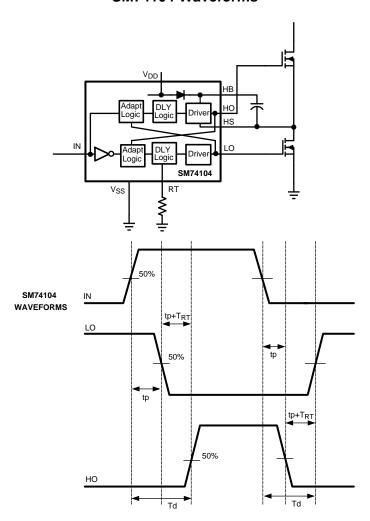

### **Typical Performance Characteristics**

Figure 3.

Figure 5.

Figure 4.

Figure 6.

Figure 8.

Copyright © 2011–2013, Texas Instruments Incorporated

Submit Documentation Feedback

# **Typical Performance Characteristics (continued)**

Figure 9.

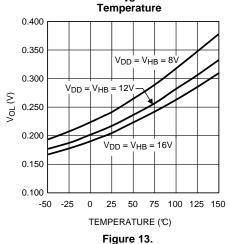

LO & HO Gate Drive—Low Level Output Voltage vs

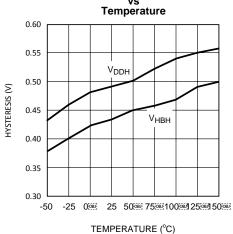

Undervoltage Threshold Hysteresis

Figure 10.

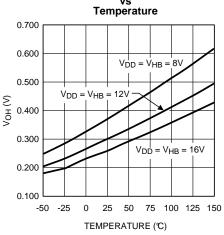

# LO & HO Gate Drive—High Level Output Voltage vs

Figure 12.

Figure 14.

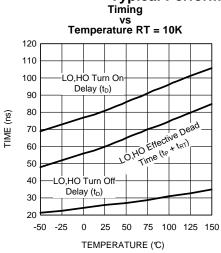

# Typical Performance Characteristics (continued) Timing

Figure 15.

Figure 16.

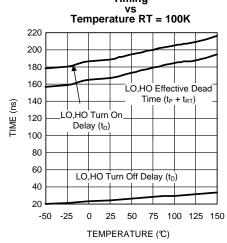

### Turn On Delay vs RT Resistor Value

Figure 17.

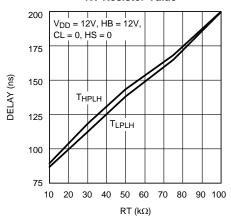

### SM74104 Waveforms

Figure 18. Application Timing Waveforms

### **OPERATIONAL DESCRIPTION**

### ADAPTIVE SHOOT-THROUGH PROTECTION

SM74104 is a high voltage, high speed dual output driver designed to drive top and bottom MOSFET's connected in synchronous buck or half-bridge configuration, from one externally provided PWM signal. SM74104 features adaptive delay to prevent shoot-through current through top and bottom MOSFETs during switching transitions. Referring to the timing diagram Figure 18, the rising edge of the PWM input (IN) turns off the bottom MOSFET (LO) after a short propagation delay ( $t_P$ ). An adaptive circuit in the SM74104 monitors the bottom gate voltage (LO) and triggers a programmable delay generator when the LO pin falls below an internally set threshold ( $\approx$  Vdd/2). The gate drive of the upper MOSFET (HO) is disabled until the deadtime expires. The upper gate is enabled after the TIMER delay ( $t_P+T_{RT}$ ), and the upper MOSFET turns-on. The additional delay of the timer prevents lower and upper MOSFETs from conducting simultaneously, thereby preventing shoot-through.

A falling transition on the PWM signal (IN) initiates the turn-off of the upper MOSFET and turn-on of the lower MOSFET. A short propagation delay ( $t_P$ ) is encountered before the upper gate voltage begins to fall. Again, the adaptive shoot-through circuitry and the programmable deadtime TIMER delays the lower gate turn-on time. The upper MOSFET gate voltage is monitored and the deadtime delay generator is triggered when the upper MOSFET gate voltage with respect to ground drops below an internally set threshold ( $\approx$  Vdd/2). The lower gate drive is momentarily disabled by the timer and turns on the lower MOSFET after the deadtime delay expires ( $t_P+T_{RT}$ ).

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

The RT pin is biased at 3V and current limited to 1mA. It is designed to accommodate a resistor between 5K and 100K, resulting in an effective dead-time proportional to RT and ranging from 90ns to 200ns. RT values below 5K will saturate the timer and are not recommended.

### Startup and UVLO

Both top and bottom drivers include under-voltage lockout (UVLO) protection circuitry which monitors the supply voltage ( $V_{DD}$ ) and bootstrap capacitor voltage ( $V_{HB} - V_{HS}$ ) independently. The UVLO circuit inhibits each driver until sufficient supply voltage is available to turn-on the external MOSFETs, and the built-in hysteresis prevents chattering during supply voltage transitions. When the supply voltage is applied to  $V_{DD}$  pin of SM74104, the top and bottom gates are held low until  $V_{DD}$  exceeds UVLO threshold, typically about 6.9V. Any UVLO condition on the bootstrap capacitor will disable only the high side output (HO).

### LAYOUT CONSIDERATIONS

The optimum performance of high and low side gate drivers cannot be achieved without taking due considerations during circuit board layout. Following points are emphasized.

- 1. A low ESR/ESL capacitor must be connected close to the IC, and between  $V_{DD}$  and  $V_{SS}$  pins and between HB and HS pins to support high peak currents being drawn from  $V_{DD}$  during turn-on of the external MOSFET.

- 2. To prevent large voltage transients at the drain of the top MOSFET, a low ESR electrolytic capacitor must be connected between MOSFET drain and ground (V<sub>SS</sub>).

- 3. In order to avoid large negative transients on the switch node (HS) pin, the parasitic inductances in the source of top MOSFET and in the drain of the bottom MOSFET (synchronous rectifier) must be minimized.

- 4. Grounding considerations:

- The first priority in designing grounding connections is to confine the high peak currents from charging and discharging the MOSFET gate in a minimal physical area. This will decrease the loop inductance and minimize noise issues on the gate terminal of the MOSFET. The MOSFETs should be placed as close as possible to the gate driver.

- The second high current path includes the bootstrap capacitor, the bootstrap diode, the local ground referenced bypass capacitor and low side MOSFET body diode. The bootstrap capacitor is recharged on the cycle-by-cycle basis through the bootstrap diode from the ground referenced V<sub>DD</sub> bypass capacitor. The recharging occurs in a short time interval and involves high peak current. Minimizing this loop length and area on the circuit board is important to ensure reliable operation.

- 5. The resistor on the RT pin must be placed very close to the IC and seperated from high current paths to avoid noise coupling to the time delay generator which could disrupt timer operation.

### POWER DISSIPATION CONSIDERATIONS

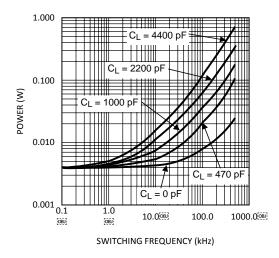

The total IC power dissipation is the sum of the gate driver losses and the bootstrap diode losses. The gate driver losses are related to the switching frequency (f), output load capacitance on LO and HO ( $C_L$ ), and supply voltage ( $V_{DD}$ ) and can be roughly calculated as:

$$P_{DGATES} = 2 \cdot f \cdot C_{L} \cdot V_{DD}^{2}$$

(1)

There are some additional losses in the gate drivers due to the internal CMOS stages used to buffer the LO and HO outputs. The following plot shows the measured gate driver power dissipation versus frequency and load capacitance. At higher frequencies and load capacitance values, the power dissipation is dominated by the power losses driving the output loads and agrees well with the above equation. This plot can be used to approximate the power losses due to the gate drivers.

Figure 19. Gate Driver Power Dissipation (LO + HO)

V<sub>CC</sub> = 12V, Neglecting Diode Losses

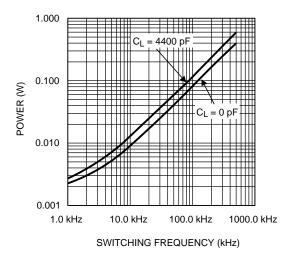

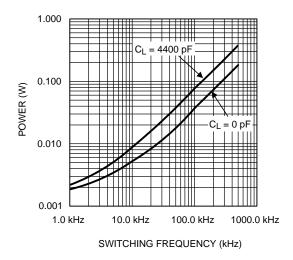

The bootstrap diode power loss is the sum of the forward bias power loss that occurs while charging the bootstrap capacitor and the reverse bias power loss that occurs during reverse recovery. Since each of these events happens once per cycle, the diode power loss is proportional to frequency. Larger capacitive loads require more current to recharge the bootstrap capacitor resulting in more losses. Higher input voltages  $(V_{IN})$  to the half bridge result in higher reverse recovery losses. The following plot was generated based on calculations and lab measurements of the diode recovery time and current under several operating conditions. This can be useful for approximating the diode power dissipation.

Figure 20. Diode Power Dissipation  $V_{IN} = 80V$

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Figure 21. Diode Power Dissipation  $V_{IN} = 40V$

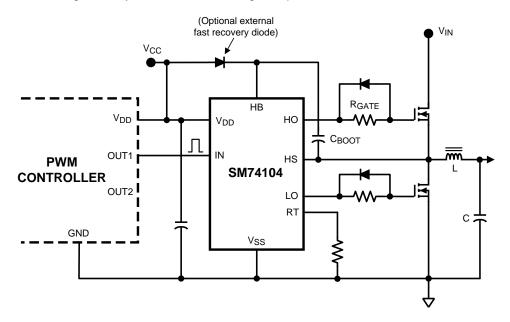

The total IC power dissipation can be estimated from the above plots by summing the gate drive losses with the bootstrap diode losses for the intended application. Because the diode losses can be significant, an external diode placed in parallel with the internal bootstrap diode (refer to Figure 22) can be helpful in removing power from the IC. For this to be effective, the external diode must be placed close to the IC to minimize series inductance and have a significantly lower forward voltage drop than the internal diode.

Figure 22. SM74104 Driving MOSFETs Connected in Synchronous Buck Configuration

### SNOSBA3C - JUNE 2011-REVISED APRIL 2013

# **REVISION HISTORY**

| Changes from Revision B (April 2013) to Revision C |                                                    | Pag |    |

|----------------------------------------------------|----------------------------------------------------|-----|----|

| •                                                  | Changed layout of National Data Sheet to TI format |     | 11 |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>