# **Lighting Management Unit with High Voltage Boost Converter**

Check for Samples: LP3958

### **FEATURES**

- High-Efficiency Boost Converter With Programmable Output Voltage

- Two Individual Drivers for Serial Display Backlight LEDs

- Three Drivers for Serial Keypad LEDs

- Automatic Dimming Controller

- Stand Alone Serial Leypad LEDs Controller

- Three General-Purpose IO Pins

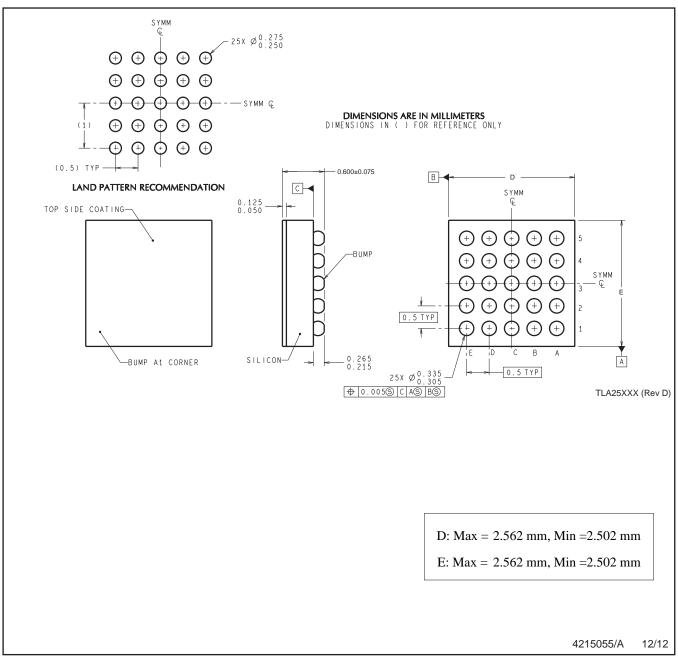

- 25-Bump DSBGA Package: 2.54mm x 2.54mm x 0.6mm

#### **APPLICATIONS**

- Cellular Phones and PDAs

- MP3 Players

- Digital Cameras

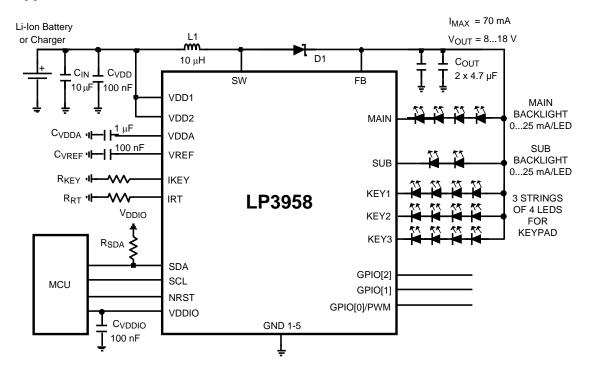

# **Typical Application**

### DESCRIPTION

LP3958 is a Lighting Management Unit for portable applications. It is used to drive display backlight and keypad LEDs. The device can drive 5 separately connected strings of LEDs with high voltage boost converter.

The keypad LED driver allows driving LEDs from high voltage boost converter or separate supply voltage. The MAIN and SUB outputs are high resolution current mode drivers. Keypad LED outputs can be used in switch mode and current mode. External PWM control can be used for any selected outputs.

The device is controlled through 2-wire low voltage I<sup>2</sup>C compatible interface that reduces the number of required connections.

LP3958 is offered in a tiny 25-bump DSBGA package.

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

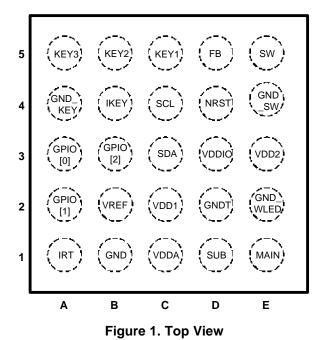

#### **CONNECTION DIAGRAMS**

25-Bump Thin DSBGA Package, Large Bump, Package Number YZR0025

Figure 2. Bottom View

## **Table 1. PIN DESCRIPTIONS**

| Pin No. | Name          | Туре               | Description                                                 |

|---------|---------------|--------------------|-------------------------------------------------------------|

| 5E      | SW            | Output             | Boost Converter Power Switch                                |

| 5D      | FB            | Input              | Boost Converter Feedback                                    |

| 5C      | KEY1          | Output             | Keypad LED Output 1 (Current Sink)                          |

| 5B      | KEY2          | Output             | Keypad LED Output 2 (Current Sink)                          |

| 5A      | KEY3          | Output             | Keypad LED Output 3 (Current Sink)                          |

| 4E      | GND_SW        | Ground             | Power Switch Ground                                         |

| 4D      | NRST          | Input              | External Reset, Active Low                                  |

| 4C      | SCL           | Logic Input        | Clock Input for I <sup>2</sup> C Compatible Interface       |

| 4B      | IKEY          | Input              | External Keypad LED Maximum Current Set Resistor            |

| 4A      | GND_KEY       | Ground             | Ground for KEY LED Currents                                 |

| 3E      | VDD2          | Power              | Supply Voltage 3.05.5 V                                     |

| 3D      | VDDIO         | Power              | Supply Voltage for Digital Input/Output Buffers and Drivers |

| 3C      | SDA           | Logic Input/Output | Data Input/Output for I <sup>2</sup> C Compatible Interface |

| 3B      | GPIO[2]       | Logic Input/Output | General Purpose Logic Input/Output                          |

| ЗА      | GPIO[0] / PWM | Logic Input/Output | General Purpose Logic Input/Output / External PWM Input     |

| 2E      | GND_WLED      | Ground             | Ground for White LED Currents (MAIN and SUB Outputs)        |

| 2D      | GNDT          | Ground             | Ground                                                      |

| 2C      | VDD1          | Power              | Supply Voltage 3.05.5 V                                     |

| 2B      | VREF          | Output             | Reference Voltage (1.23V)                                   |

| 2A      | GPIO[1]       | Logic Input/Output | General Purpose Logic Input/Output                          |

| 1E      | MAIN          | Output             | MAIN Display White LED Current Output (Current Sink)        |

| 1D      | SUB           | Output             | SUB Display White LED Current Output (Current Sink)         |

| 1C      | VDDA          | Output             | Internal LDO Output (2.80V)                                 |

| 1B      | GND           | Ground             | Ground for Core Circuitry                                   |

| 1A      | IRT           | Input              | Oscillator Frequency Set Resistor                           |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1) (2)(3)

| Aboolate maximum ratings                                         |                  |                                                |

|------------------------------------------------------------------|------------------|------------------------------------------------|

| V (SW, FB, MAIN, SUB, KEY1, KEY2, KEY3)                          |                  | -0.3V to +20V                                  |

| $V_{DD1}, V_{DD2}, V_{DDIO}, V_{DDA}$                            |                  | -0.3V to +6.0V                                 |

| Voltage on I <sub>KEY</sub> , I <sub>RT</sub> , V <sub>REF</sub> |                  | -0.3V to V <sub>DD1</sub> +0.3V with 6.0V max  |

| Voltage on Logic Pins                                            |                  | -0.3V to V <sub>DDIO</sub> +0.3V with 6.0V max |

| I (V <sub>REF</sub> )                                            |                  | 10μΑ                                           |

| I(KEY1, KEY2, KEY3)                                              |                  | 100mA                                          |

| Continuous Power Dissipation (4)                                 |                  | Internally Limited                             |

| Junction Temperature (T <sub>J-MAX</sub> )                       |                  | 125°C                                          |

| Storage Temperature Range                                        |                  | -65°C to +150°C                                |

| Maximum Lead Temperature (Soldering) (5)                         | 260°C            |                                                |

| ESD Rating <sup>(6)</sup>                                        | Human Body Model | 2kV                                            |

|                                                                  | Machine Model    | 200V                                           |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pins.

- (3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- (4) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>=150°C (typ.) and disengages at T<sub>J</sub>=130°C (typ.).

- (5) For detailed soldering specifications and information, please refer to Application Note AN1112: DSBGA Wafer Level Chip Scale Package

- (6) The Human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin. MIL-STD-883 3015.7

# Operating Ratings (1) (2)

| <u> </u>                                             |                           |

|------------------------------------------------------|---------------------------|

| V (SW, FB, MAIN, SUB)                                | 0 to +19V                 |

| V <sub>DD1,2</sub>                                   | 3.0 to 5.5V               |

| V <sub>DDIO</sub>                                    | 1.65V to V <sub>DD1</sub> |

| Recommended Load Current (KEY1, KEY2, KEY3) CC Mode  | 0mA to 15mA/driver        |

| Recommended Total Boost Converter Load Current       | 0mA to 70mA               |

| Junction Temperature (T <sub>J</sub> )               | -30°C to +125°C           |

| Ambient Temperature (T <sub>A</sub> ) <sup>(3)</sup> | -30°C to +85°C            |

|                                                      |                           |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pins.

- (3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

#### Thermal Properties

| Junction-to-Ambient Thermal Resistance(θ <sub>JA</sub> ) <sup>(1)</sup> | 60 - 100°C/W |

|-------------------------------------------------------------------------|--------------|

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

# Electrical Characteristics (1) (2)

Limits in standard typeface are for  $T_J$  = 25° C. Limits in **boldface** type apply over the operating ambient temperature range (-30°C <  $T_A$  < +85°C). Unless otherwise noted, specifications apply to the LP3958 Block Diagram with:  $V_{DD1,2}$  = 3.0 ... 5.5V,  $C_{VDD}$  =  $C_{VDDIO}$  = 100nF,  $C_{OUT}$  = 2 x 4.7 $\mu$ F,  $C_{IN}$  = 10 $\mu$ F,  $C_{VDDA}$  = 1 $\mu$ F,  $C_{VREF}$  = 100nF, L1 = 10 $\mu$ H,  $R_{KEY}$  = 8.2 $k\Omega$  and  $R_{RT}$  = 82 $k\Omega$  (3).

| Symbol           | Parameter                                                      | Test Conditions                            | Min | Тур  | Max  | Unit |

|------------------|----------------------------------------------------------------|--------------------------------------------|-----|------|------|------|

| I <sub>VDD</sub> | Standby supply current (V <sub>DD1</sub> , V <sub>DD2</sub> )  | NSTBY = L<br>Register 0DH=08H (4)          |     | 1.7  | 7    | μΑ   |

|                  | No-boost supply current (V <sub>DD1</sub> , V <sub>DD2</sub> ) | NSTBY = H,<br>EN_BOOST = L                 |     | 300  | 800  | μΑ   |

|                  | No-load supply current (V <sub>DD1</sub> , V <sub>DD2</sub> )  | NSTBY = H,<br>EN_BOOST = H<br>Autoload OFF |     | 750  | 1300 | uA   |

| $V_{DDA}$        | Output voltage of internal LDO                                 | I <sub>VDDA</sub> = 1mA                    |     | 2.80 |      | V    |

|                  |                                                                |                                            | -3  |      | +3   | %    |

| $V_{REF}$        | Reference voltage (5)                                          |                                            |     | 1.23 |      | V    |

- (1) All voltages are with respect to the potential at the GND pins.

- (2) Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

- (3) Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

- (4) Boost output voltage set to 8V (08H in register 0DH) to prevent any unneccessary current consumption.

- (5) No external loading allowed for V<sub>REF</sub> pin.

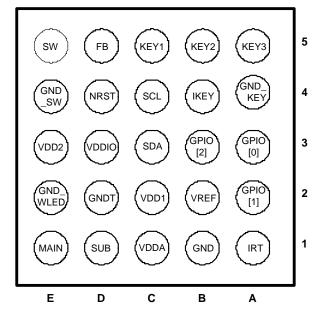

### **BLOCK DIAGRAM**

#### APPLICATION INFORMATION

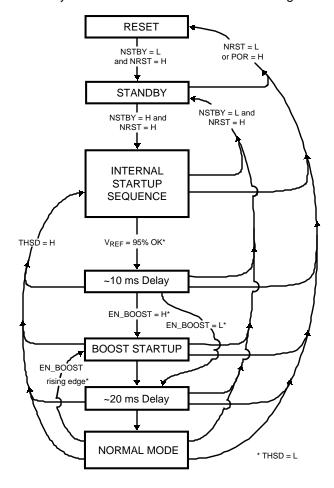

### **Modes of Operation**

- **RESET:** In the RESET mode all the internal registers are reset to the default values. Reset is entered always if input NRST is LOW or internal Power On Reset is active. Power On Reset (POR) will activate during the chip startup or when the supply voltages V<sub>DD1</sub> and V<sub>DD2</sub> fall below 1.5V. Once V<sub>DD1</sub> and V<sub>DD2</sub> rises above 1.5V, POR will inactivate and the chip will continue to the STANDBY mode. NSTBY control bit is low after POR by default.

- **STANDBY:** The STANDBY mode is entered if the register bit NSTBY is LOW and Reset is not active. This is the low power consumption mode, when all circuit functions are disabled. Registers can be written in this mode and the control bits are effective immediately after start up.

- **STARTUP:** When NSTBY bit is written high, the INTERNAL STARTUP SEQUENCE powers up all the needed internal blocks (V<sub>REF</sub>, Bias, Oscillator etc.). To ensure the correct oscillator initialization, a 10ms delay is generated by the internal state-machine. If the chip temperature rises too high, the Thermal Shutdown (THSD) disables the chip operation and STARTUP mode is entered until no thermal shutdown event is present.

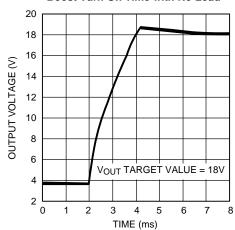

- **BOOST STARTUP:** Soft start for boost output is generated in the BOOST STARTUP mode. The boost output is raised in low current PWM mode during the 20ms delay generated by the state-machine. All LED outputs are off during the 20ms delay to ensure smooth startup. The Boost startup is entered from Internal Startup Sequence if EN\_BOOST is HIGH or from Normal mode when EN\_BOOST is written HIGH.

- **NORMAL:** During NORMAL mode the user controls the chip using the Control Registers. The registers can be written in any sequence and any number of bits can be altered in a register in one write.

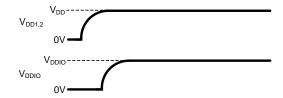

### **Power-Up Sequence**

When powering up the device,  $V_{DD1}$  and  $V_{DD2}$  should be greater than  $V_{DDIO}$  to prevent any damage to the device.

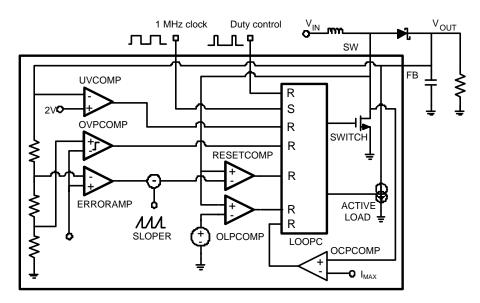

## **Magnetic Boost DC/DC Converter**

The LP3958 Boost DC/DC Converter generates an 8...18V supply voltage for the LEDs from single Li-Ion battery (3V...4.5V). The output voltage is controlled with an 8-bit register in 10 steps. The converter is a magnetic switching PWM mode DC/DC converter with a current limit. Switching frequency is 1MHz, when timing resistor RT is  $82k\Omega$ . Timing resistor defines the internal oscillator frequency and thus directly affects boost frequency and KEY timings.

EMI filter ( $R_{SW}$  and  $C_{SW}$ ) on the SW pin can be used to suppress EMI caused by fast switching. These components should be as near as possible to the SW pin to ensure reliable operation. The LP3958 Boost Converter uses pulse-skipping elimination to stabilize the noise spectrum. Even with light load or no load a minimum length current pulse is fed to the inductor. An active load is used to remove the excess charge from the output capacitor at very light loads. Active load can be disabled with the EN\_AUTOLOAD bit. Disabling active load will increase slightly the efficiency at light loads, but the downside is that pulse skipping will occur. The Boost Converter should be stopped when there is no load to minimise the current consumption.

The topology of the magnetic boost converter is called CPM control, current programmed mode, where the inductor current is measured and controlled with the feedback. The user can program the output voltage of the boost converter. The output voltage control changes the resistor divider in the feedback loop. Figure 3 shows the boost topology with the protection circuitry. Four different protection schemes are implemented:

- 1. Over voltage protection, limits the maximum output voltage

- Keeps the output below breakdown voltage.

- Prevents boost operation if battery voltage is much higher than desired output.

- 2. Over current protection, limits the maximum inductor current

- Voltage over switching NMOS is monitored; too high voltages turn the switch off.

- 3. Feedback break protection. Prevents uncontrolled operation if FB pin gets disconnected.

- 4. Duty cycle limiting, done with digital control.

Figure 3. Boost Converter Topology

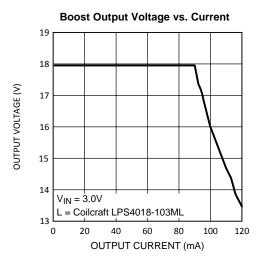

### MAGNETIC BOOST DC/DC CONVERTER ELECTRICAL CHARACTERISTICS

| Symbol               | Parameter                        | Test Conditions                                         | Min  | Тур  | Max  | Unit |

|----------------------|----------------------------------|---------------------------------------------------------|------|------|------|------|

| I <sub>LOAD</sub>    | Maximum Continuous Load Current  | $3.0V = V_{IN}$ $V_{OUT} = 18V$                         |      |      | 70   | mA   |

| V <sub>OUT</sub>     | Output Voltage Accuracy (FB Pin) | $3.0V \le V_{IN} \le 5.5V$ $V_{OUT} = 18V$              | -3.5 |      | +3.5 | %    |

| RDS <sub>ON</sub>    | Switch ON Resistance             | I <sub>SW</sub> = 0.5A                                  |      | 0.15 | 0.3  | Ω    |

| -                    | PWM Mode Switching Frequency     | RT = 82 kΩ                                              |      | 1.0  |      | MHz  |

|                      | Frequency Accuracy               | RT = 82 kΩ                                              | -7   |      | +7   | 0/   |

|                      |                                  |                                                         | -9   |      | +9   | %    |

| t <sub>PULSE</sub>   | Switch Pulse Minimum<br>Width    | no load                                                 |      | 45   |      | ns   |

| t <sub>STARTUP</sub> | Startup Time                     | Boost startup from STANDBY to $V_{OUT} = 18V$ , no load |      | 15   |      | ms   |

| I <sub>MAX</sub>     | SW Pin Current Limit             |                                                         |      | 800  | 1150 | mA   |

### **BOOST STANDBY MODE**

User can set the Boost Converter to STANDBY mode by writing the register bit EN\_BOOST low. When EN\_BOOST is written high, the converter starts for 20ms in low current PWM mode and then goes to normal PWM mode. All LED outputs are off during the 20ms delay to ensure smooth startup.

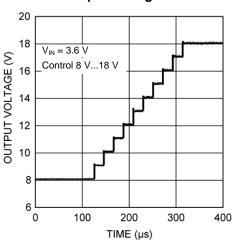

### **BOOST OUTPUT VOLTAGE CONTROL**

User can control the boost output voltage by Boost Output 8-bit register.

| Boost Ou<br>Regist | Boost Output<br>Voltage (typical) |                   |

|--------------------|-----------------------------------|-------------------|

| Bin                | Dec                               | voitage (typical) |

| 0000 1000          | 8                                 | 8.0V              |

| 0000 1001          | 9                                 | 9.0V              |

| 0000 1010          | 10                                | 10.0V             |

| 0000 1011          | 11                                | 11.0V             |

Copyright © 2006–2013, Texas Instruments Incorporated

| 0000 1100 | 12 | 12.0V |

|-----------|----|-------|

| 0000 1101 | 13 | 13.0V |

| 0000 1110 | 14 | 14.0V |

| 0000 1111 | 15 | 15.0V |

| 0001 0000 | 16 | 16.0V |

| 0001 0001 | 17 | 17.0V |

| 0001 0010 | 18 | 18.0V |

If register value is lower than 8, then value of 8 is used internally.

If register value is higher than 18, then value of 18 is used internally.

# **Boost Output Voltage Control**

Figure 4.

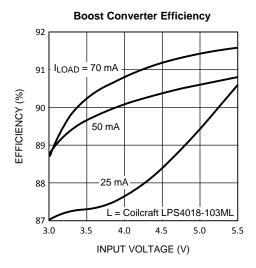

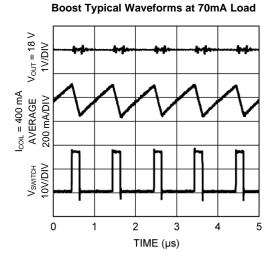

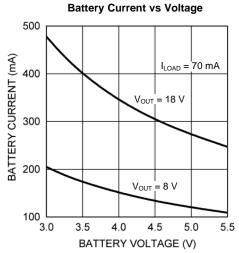

## **Boost Converter Typical Performance Characteristics**

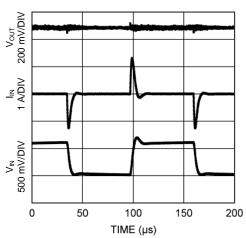

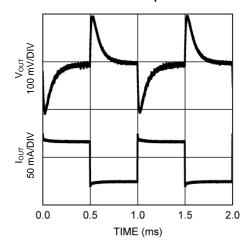

Vin = 3.6V, Vout = 18.0V if not otherwise stated

Figure 5.

Figure 6.

Vin = 3.6V, Vout = 18.0V if not otherwise stated

Figure 7.

Figure 9.

Figure 8.

Figure 10.

Vin = 3.6V, Vout = 18.0V if not otherwise stated

# Boost Load Transient Response 25mA - 70mA

Figure 11.

### Autoload Effect on Input Current, No Load

Figure 12.

Submit Documentation Feedback

Vin = 3.6V, Vout = 18.0V if not otherwise stated

### Functionality of Keypad LED Outputs (KEY1, KEY2, KEY3)

LP3958 has three individual keypad LED output pins. Output pins can be used in switch mode or constant current mode. Output mode can be selected with the control register (address 00H) bit CC\_SW. If the bit is set high, then keypad LED outputs are in switch mode, otherwise in constant current mode. These modes are described later in separate chapters.

Keypad LED output control can be done in three ways:

- 1. Defining the expected balance and brightness in Keypad register (address 01H)

- 2. Direct setting each LED ON/OFF via Keypad control register (address 00H)

- 3. External PWM control

#### **BRIGHTNESS CONTROL WITH KEYPAD REGISTER**

If the keypad LED output is used by defining the balance and brightness in the Keypad register, then one needs to set EN\_KEYP bit high and KEYP\_PWM bit high in the Control register (address 00H). K1SW, K2SW and K3SW are used to enable each LED output, enabled when written high. CC\_SW defines the LED output mode. A single register is used for defining the balance and brightness for keypad LED output:

|              | KEYPAD REGISTER (01H) |                                                                           |  |

|--------------|-----------------------|---------------------------------------------------------------------------|--|

| Name         | Bit                   | Description                                                               |  |

| BALANCE[2:0] | 6:4                   | Balance of KEY1, KEY2 and KEY3 outputs                                    |  |

| BRIGHT[2:0]  | 3:1                   | Brightness control                                                        |  |

| OVL          | 0                     | Overlapping mode selection: 0 = non-overlapping mode 1 = overlapping mode |  |

Brightness control is logarithmic and is programmed as follows:

Table 2.

| Bright[2:0] | Brightness [%] | Ratio to max brightness |

|-------------|----------------|-------------------------|

| 000         | 0              | 0                       |

| 001         | 1.56           | 1/64                    |

| 010         | 3.12           | 1/32                    |

| 011         | 6.25           | 1/16                    |

| 100         | 12.5           | 1/8                     |

| 101         | 25             | 1/4                     |

| 110         | 50             | 1/2                     |

| 111         | 100            | 1/1                     |

The LED balance can be selected as follows. This is valid only in non-overlapping mode.

Table 3.

| Balance<br>[2:0] | KEY1<br>active [%] | KEY2<br>active [%] | KEY3<br>active [%] |

|------------------|--------------------|--------------------|--------------------|

| 000              | 100                | 0                  | 0                  |

| 001              | 0                  | 100                | 0                  |

| 010              | 0                  | 0                  | 100                |

| 011              | 50                 | 50                 | 0                  |

| 100              | 0                  | 50                 | 50                 |

| 101              | 50                 | 0                  | 50                 |

| 110              | 33                 | 33                 | 33                 |

| 111              | 50                 | 25                 | 25                 |

#### **OVERLAPPING MODE**

The brightness is controlled using PWM duty cycle based control method as Figure 14 shows.

Figure 14. Overlapping Mode

Since KEY outputs are on simuneltaneously, the maximum load peak current is:

$$I_{MAX} = I(KEY1)_{MAX} + I(KEY2)_{MAX} + I(KEY3)_{MAX}$$

(1)

#### **NON-OVERLAPPING MODE**

The timing diagram shows the splitted KEY1, KEY2 and KEY3 and brightness control effect to splitted parts. Full brightness is used in the diagram. If for example ½ brightness is used, the frame is still 50µs, but all LED outputs' ON time is 50% shorter and at the last 25µs all LED outputs are OFF.

Figure 15. Non-overlapping Mode

The non-overlapping mode has 8-programmed balance ratios. Since the KEY1, KEY2 and KEY3 are split in to non-overlapping slots the output current through the keypad LED can be calculated by following equation:

$$I_{AVG} = (C_{KEY1} \times I_{KEY1} + C_{KEY2} \times I_{KEY2} + C_{KEY3} \times I_{KEY3}) \times B$$

where

- C = Balance [%] (see Table 3)

- B = Brightness [%] (see Table 2)

#### LED ON/OFF CONTROL WITH KEYPAD CONTROL REGISTER

Each LED output can be set ON by writing the corresponding bit high in the control register. K1SW controls KEY1, K2SW controls KEY2 and K3SW controls KEY3 output. Note that EN\_KEYP bit must be high and KEYP\_PWM bit low. In this mode, the KEYPAD register does not have any effect. CC\_SW bit in control register defines the LED output mode.

Submit Documentation Feedback

(2)

#### Switch Mode / Constant Current Mode

Each keypad LED output can be set to act as a switch or a constant current sink. Selection of mode is done with the CC\_SW bit in the Control Register. If bit is set high, then the switch mode is selected. Default is switch mode.

#### 1. SWITCH MODE

In switch mode, the keypad LED outputs are low ohmic switches to ground. Resistance is typically  $3.5\Omega$ . External ballast resistors must be used to limit the current through the LED.

#### 2. CONSTANT CURRENT MODE

In constant current mode, the maximum output current is defined with a single external resistor ( $R_{KEY}$ ) and the maximum current control register (address 02H).

|                      | KEYPAD MAX CURRENT REGISTER (02H) |                      |  |  |  |

|----------------------|-----------------------------------|----------------------|--|--|--|

| Name Bit Description |                                   |                      |  |  |  |

| IK1[1:0]             | 5:4                               | KEY1 maximum current |  |  |  |

| IK2[1:0]             | 3:2                               | KEY2 maximum current |  |  |  |

| IK3[1:0]             | 1:0                               | KEY3 maximum current |  |  |  |

Maximum current for each LED output is adjusted with the Keypad max current register in following way:

| IK1[1:0], IK2[1:0], IK3[1:0] | Maximum current / output |

|------------------------------|--------------------------|

| 00                           | 0.25 x I <sub>MAX</sub>  |

| 01                           | 0.50 x I <sub>MAX</sub>  |

| 10                           | 0.75 x I <sub>MAX</sub>  |

| 11                           | 1.00 x I <sub>MAX</sub>  |

External ballast resistors are not needed in this mode. The maximum current for all keypad LED drivers is set with  $R_{\text{KEY}}$ . The equation for calculating the maximum current is:

$$I_{MAX} = 100 \times 1.23 \text{V} / (R_{KEY} + 50 \Omega)$$

#### where

- I<sub>MAX</sub> = maximum KEY current in any KEY output (during constant current mode)

- 1.23V = reference voltage

- 100 = internal current mirror multiplier

- R<sub>KEY</sub> = resistor value in Ohms

- 50  $\Omega$  = Internal resistor in the I<sub>KEY</sub> input

Table with example resistance values and corresponding output currents:

| KEY resistor R <sub>KEY</sub> (kΩ) | Maximum current / output I <sub>MAX</sub> (mA) |

|------------------------------------|------------------------------------------------|

| 8.2                                | 14.9                                           |

| 9.1                                | 13.4                                           |

| 10                                 | 12.2                                           |

| 12                                 | 10.2                                           |

| 15                                 | 8.2                                            |

| 18                                 | 6.8                                            |

| 24                                 | 5.1                                            |

Product Folder Links: LP3958

(3)

Note that the LED output requires a minimum saturation voltage in order to act as a true constant current sink. The saturation voltage minimum is typically 100mV. If the LED output voltage drops below 100mV, then the current will decrease significantly.

#### **External PWM Control**

The GPIO[0]/PWM pin can be used to control the KEY output. PWM function for the pin is selected by writing EN\_PWM\_PIN high in GPIO control register (address 06H). Note, that EN\_KEYP bit must be set high. Each LED output can be enabled with K1SW, K2SW and K3SW bits. EN\_EXT\_K1\_PWM, EN\_EXT\_K2\_PWM and EN\_EXT\_K3\_PWM bits are used to select, which LED outputs are controlled with the external PWM input. Note that polarity of external PWM control is active high i.e. when high, then LED output is enabled. If KEYP\_PWM is set low, then each selected LED output is controlled directly with external PWM input. If KEYP\_PWM is set high, then internal PWM control is modulated by the external PWM input. In latter case, internal PWM control is passed to LED when external PWM input is high.

### **Keypad LEDs Driver Performance Characteristics**

| Symbol                | Parameter                                       | Test Conditions                                    | Min | Тур   | Max | Unit |

|-----------------------|-------------------------------------------------|----------------------------------------------------|-----|-------|-----|------|

| I <sub>LEAKAGE</sub>  | KEY1, KEY2, KEY3 pin leakage current            |                                                    |     |       | 1   | μΑ   |

| I <sub>MAX(KEY)</sub> | Maximum recommended sink current <sup>(1)</sup> | CC mode                                            |     |       | 15  | mA   |

|                       |                                                 | SW mode                                            |     |       | 60  | mA   |

|                       | Accuracy at 15mA                                | CC mode                                            |     | 5     |     | %    |

|                       | Current mirror ratio                            | CC mode                                            |     | 1:100 |     |      |

|                       | KEY current matching error                      | I <sub>KEY</sub> set to 15mA, CC mode              |     | 3     |     | %    |

| R <sub>SW</sub>       | Switch resistance                               | SW mode                                            |     | 3.5   |     | Ω    |

| $f_{KEY}$             | KEY internal PMW switching frequency            | Accuracy same as internal clock frequency accuracy |     | 20    |     | kHz  |

| V <sub>SAT</sub>      | Saturation voltage (current drop 10%)           | I <sub>KEY</sub> set to 15mA                       |     | 100   | 500 | mV   |

<sup>(1)</sup> KEY current should be limited as follows: constant current mode – limited by external R<sub>KEY</sub> resistor switch mode – limited by external ballast resistors

### **Backlight Drivers**

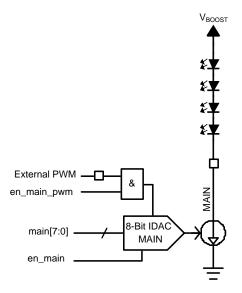

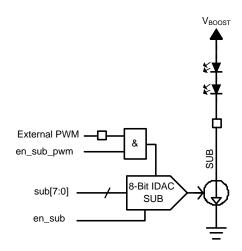

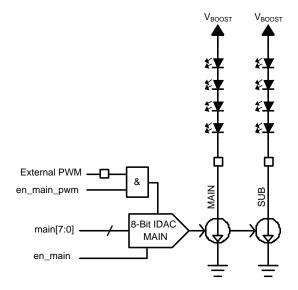

LP3958 has 2 independent backlight drivers. Both drivers are regulated constant current sinks. LED current for both LED strings are controlled by the 8-bit current mode DACs with 0.1 mA step. MAIN and SUB LEDs can be also controlled with one DAC (MAIN) for better matching allowing the use of larger displays having up to 8 white LEDs by setting DISPL bit to 1.

Figure 16. MAIN output for 4 LEDs (DISPL = 0)

Figure 17. SUB output for 2 LEDs (DISPL = 0)

Figure 18. MAIN and SUB outputs for 8 LEDs (DISPL = 1)

#### **PWM CONTROL**

External PWM control is enabled by writing 1 to EN\_MAIN\_PWM and/or EN\_SUB\_PWM bits in register address 2BH. GPIO[0] pin is used as external PWM input when EN\_PWM\_PIN is set high. PWM input is active high, i.e. LED is activated when in high state.

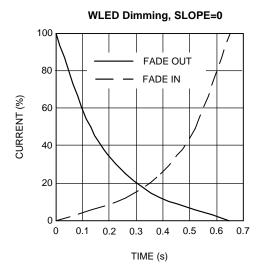

#### **FADE IN / FADE OUT**

LP3958 has an automatic fade in and out for main and sub backlight. The fade function is enabled with EN\_FADE bit. The slope of the fade curve is set by the SLOPE bit. Fade control for main and sub display is set by FADE\_SEL bit.

Recommended fading sequence:

- 1. ASSUMPTION: Current WLED value in register

- 2. Set SLOPE

- 3. Set FADE SEL

- 4. Set EN\_FADE = 1

- 5. Set target WLED value

### 6. Fading will be done either within 0.65s or 1.3s based on SLOPE selection

Fading times apply to full scale change i.e. from 0 to 100% or vice versa. If the current change does not correspond to full scale change, the time will be respectively shorter. See WLED Dimming diagrams for typical fade times.

|          | WLED CONTROL REGISTER (03H) |                                                                                             |  |  |  |

|----------|-----------------------------|---------------------------------------------------------------------------------------------|--|--|--|

| Name     | Bit                         | Description <sup>(1)</sup>                                                                  |  |  |  |

| SLOPE    | 5                           | FADE execution time: 0 = 1.3s (full scale) 1 = 0.65s (full scale)                           |  |  |  |

| FADE_SEL | 4                           | FADE selection: 0 = FADE controls MAIN 1 = FADE controls SUB                                |  |  |  |

| EN_FADE  | 3                           | FADE enable 0 = FADE disabled 1 = FADE enabled                                              |  |  |  |

| DISPL    | 2                           | Display mode: 0 = MAIN and SUB individual control 1 = MAIN and SUB controlled with MAIN DAC |  |  |  |

| EN_MAIN  | 1                           | MAIN enable: 0 = disable 1 = enable                                                         |  |  |  |

| EN_SUB   | 0                           | SUB enable: 0 = disable 1 = enable                                                          |  |  |  |

<sup>(1)</sup> If DISPL=1 and FADE\_SEL=0 then FADE effects MAIN and SUB

Adjustment is made with 04H (main current) and with 05H (sub current) registers:

| MAIN CURRENT [7:0]<br>SUB CURRENT [7:0] | Driver current,<br>mA (typical) |

|-----------------------------------------|---------------------------------|

| 0000 0000                               | 0                               |

| 0000 0001                               | 0.1                             |

| 0000 0010                               | 0.2                             |

| 0000 0011                               | 0.3                             |

|                                         |                                 |

|                                         |                                 |

| 1111 1101                               | 25.3                            |

| 1111 1110                               | 25.4                            |

| 1111 1111                               | 25.5                            |

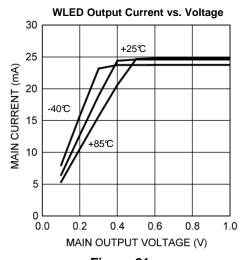

# **Backlight Driver Electrical Characteristics**

| Symbol                                | Parameter                                       | Test Conditions                                            | Min  | Тур  | Max               | Unit |

|---------------------------------------|-------------------------------------------------|------------------------------------------------------------|------|------|-------------------|------|

| I <sub>MAX</sub>                      | Maximum Sink Current                            |                                                            |      | 25.5 | 30                | mA   |

| I <sub>LEAKAGE</sub>                  | Leakage Current                                 | V <sub>SUB, MAIN</sub> =18V                                |      | 0.03 | 1                 | μΑ   |

| I <sub>MAIN</sub><br>I <sub>SUB</sub> | MAIN Current tolerance<br>SUB Current tolerance | I <sub>MAIN</sub> and I <sub>SUB</sub> set to 12.8mA (80H) | 11.1 | 12.8 | 14.1              | mA   |

| Match <sub>MAIN</sub> -               | Sink Current Matching Error <sup>(1)</sup>      | I <sub>SINK</sub> =12.8mA, DISPL=1                         |      | 0.2  |                   | %    |

| Match <sub>MAIN</sub> -<br>sub        | Sink Current Matching Error                     | I <sub>SINK</sub> =12.8mA, DISPL=0                         |      | 5    |                   | %    |

| V <sub>SAT</sub>                      | 95% Saturation Voltage                          | I <sub>SINK</sub> =25mA                                    |      | 400  | 600<br><b>800</b> | mV   |

(1) Matching is the maximum difference from the average.

WLED Dimming, SLOPE=1 100 **FADE OUT** 80 FADE IN CURRENT (%) 60 40 20 0 0.2 0.4 0.6 8.0 0.1 1.2 1.4 TIME (s)

Figure 19.

Figure 20.

Figure 21.

# **General Purpose I/O Functionality**

LP3958 has three general purpose I/O pins: GPIO[0]/PWM, GPIO[1] and GPIO[2]. GPIO[0]/PWM can also be used as a PWM input for the external LED PWM controlling. GPIO bi-directional drivers are operating from the  $V_{DDIO}$  supply domain.

Registers for GPIO are as follows:

| GPIO CONTROL (06H)   |     |                                         |  |  |  |  |  |

|----------------------|-----|-----------------------------------------|--|--|--|--|--|

| Name Bit Description |     |                                         |  |  |  |  |  |

| EN_PWM_PIN           | 4   | Enable PWM pin 0 = disable 1 = enable   |  |  |  |  |  |

| OEN[2:0]             | 2:0 | GPIO pin direction 0 = input 1 = output |  |  |  |  |  |

Copyright © 2006–2013, Texas Instruments Incorporated

| GPIO DATA (07H)      |     |           |  |  |  |  |

|----------------------|-----|-----------|--|--|--|--|

| Name Bit Description |     |           |  |  |  |  |

| DATA[2:0]            | 2:0 | Data bits |  |  |  |  |

GPIO control register is used to set the direction of each GPIO pin. For example, by setting OEN0 bit high the GPIO[0]/PWM pin acts as a logic output pin with data defined DATA0 in GPIO data register. Note, that the EN\_PWM\_PIN bit overrides OEN0 state by forcing GPIO[0]/PWM to act as PWM input. GPIO[1] and GPIO[2] pins can be selected to be inputs or outputs, defined by OEN1 and OEN2 bit status. PWM functionality is valid only for GPIO[0]/PWM pin. GPIO data register contains the data of GPIO pins. When output direction is selected to GPIO pin, then GPIO data register defines the output pin state. When GPIO data register is read, it contains the state of the pin despite of the pin direction.

Table 4. Logic Interface Characteristics(V<sub>DDIO</sub> = 1.65V...V<sub>DD1.2</sub> unless otherwise noted)

| Symbol            | Parameter               | Test Conditions           | Min                     | Тур                     | Max                   | Unit |

|-------------------|-------------------------|---------------------------|-------------------------|-------------------------|-----------------------|------|

| LOGIC IN          | PUT SCL, SDA, GPIO[0:2] | '                         |                         | u.                      |                       |      |

| V <sub>IL</sub>   | Input Low Level         |                           |                         |                         | 0.2×V <sub>DDIO</sub> | ٧    |

| V <sub>IH</sub>   | Input High Level        |                           | 0.8×V <sub>DDIO</sub>   |                         |                       | V    |

| l <sub>l</sub>    | Logic Input Current     |                           | -1.0                    |                         | 1.0                   | μA   |

| f <sub>SCL</sub>  | Clock Frequency         |                           |                         |                         | 400                   | kHz  |

| LOGIC IN          | PUT NRST                |                           | ·                       |                         |                       |      |

| V <sub>IL</sub>   | Input Low Level         |                           |                         |                         | 0.5                   | V    |

| V <sub>IH</sub>   | Input High Level        |                           | 1.2                     |                         |                       | V    |

| I <sub>I</sub>    | Input Current           |                           | -1.0                    |                         | 1.0                   | μΑ   |

| t <sub>NRST</sub> | Reset Pulse Width       |                           | 10                      |                         |                       | μs   |

| LOGIC O           | UTPUT SDA               |                           |                         |                         |                       |      |

| V <sub>OL</sub>   | Output Low Level        | $I_{SDA} = 3mA$           |                         | 0.3                     | 0.5                   | V    |

| V <sub>OH</sub>   | Output High Level       | $I_{SDA} = -3mA$          | V <sub>DDIO</sub> - 0.5 | V <sub>DDIO</sub> - 0.3 |                       |      |

| IL                | Output Leakage Current  | V <sub>SDA</sub> = 2.8V   |                         |                         | 1.0                   | μΑ   |

| LOGIC O           | UTPUT GPIO[0:2]         |                           |                         |                         |                       |      |

| V <sub>OL</sub>   | Output Low Level        | I <sub>GPIO</sub> = 3 mA  |                         | 0.3                     | 0.5                   | V    |

| V <sub>OH</sub>   | Output High Level       | I <sub>GPIO</sub> = −3 mA | V <sub>DDIO</sub> - 0.5 | V <sub>DDIO</sub> - 0.3 |                       | V    |

| IL                | Output Leakage Current  | V <sub>GPIO</sub> = 2.8V  |                         |                         | 1.0                   | μA   |

## I<sup>2</sup>C Compatible Interface

#### I<sup>2</sup>C SIGNALS

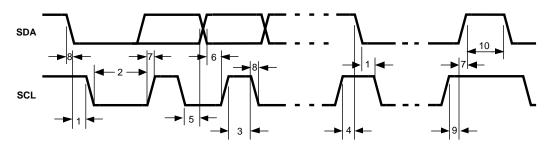

The SCL pin is used for the I<sup>2</sup>C clock and the SDA pin is used for bidirectional data transfer. Both these signals need a pull-up resistor according to I<sup>2</sup>C specification.

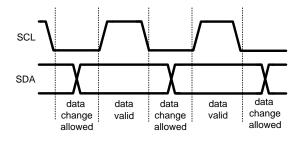

#### I<sup>2</sup>C DATA VALIDITY

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

Figure 22. I<sup>2</sup>C Signals: Data Validity

20

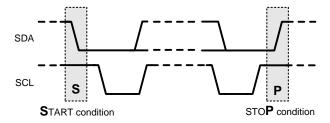

#### I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 23. I<sup>2</sup>C Start and Stop Conditions

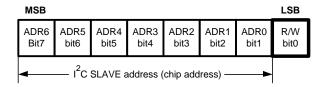

#### TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9<sup>th</sup> clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

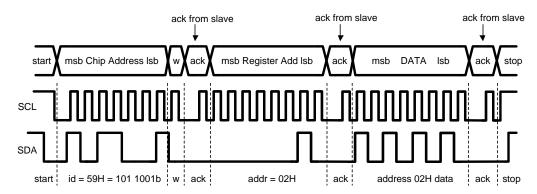

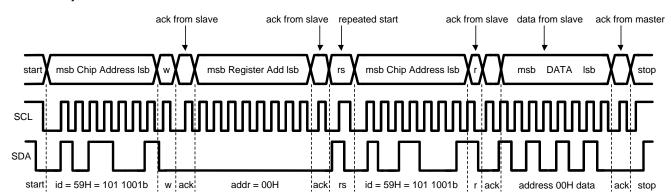

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LP3958 address is 59H (101 1001b). For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. This means that the first byte is B2H for WRITE and B3H for READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Figure 24. I<sup>2</sup>C Chip Address

Register changes take an effect at the SCL rising edge during the last ACK from slave.

w = write (SDA = "0")

r = read (SDA = "1")

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = 7-bit chip address, 59H (101 1001b) for LP3958.

Figure 25. I<sup>2</sup>C Write Cycle

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in the Read Cycle waveform.

Figure 26. I<sup>2</sup>C Read Cycle

Figure 27. I<sup>2</sup>C Timing Diagram

# $I^2C$ TIMING PARAMETERS ( $V_{DD1.2} = 3.0$ to 4.5V, $V_{DDIO} = 1.8$ V to $V_{DD1.2}$ )

|  | Symbol Parameter - | Lim                                  | Unit |     |       |

|--|--------------------|--------------------------------------|------|-----|-------|

|  |                    | Falanetei                            | Min  | Max | Offic |

|  | 1                  | Hold Time (repeated) START Condition | 0.6  |     | μs    |

(1) Data guaranteed by design

www.ti.com

| Symbol         | Parameter                                                    | Lim                  | it <sup>(1)</sup> | Unit |

|----------------|--------------------------------------------------------------|----------------------|-------------------|------|

| Symbol         | Faranteter                                                   |                      | Max               | Unit |

| 2              | Clock Low Time                                               | 1.3                  |                   | μs   |

| 3              | Clock High Time                                              | 600                  |                   | ns   |

| 4              | Setup Time for a Repeated START Condition                    | 600                  |                   | ns   |

| 5              | Data Hold Time (Output direction, delay generated by LP3958) | 300                  | 900               | ns   |

| 5              | Data Hold Time (Input direction, delay generated by Master)  | 0                    | 900               | ns   |

| 6              | Data Setup Time                                              | 100                  |                   | ns   |

| 7              | Rise Time of SDA and SCL                                     | 20+0.1C <sub>b</sub> | 300               | ns   |

| 8              | Fall Time of SDA and SCL                                     | 15+0.1C <sub>b</sub> | 300               | ns   |

| 9              | Set-up Time for STOP condition                               | 600                  |                   | ns   |

| 10             | Bus Free Time between a STOP and a START Condition           | 1.3                  |                   | μs   |

| C <sub>b</sub> | Capacitive Load for Each Bus Line                            | 10                   | 200               | pF   |

#### **Recommended External Components**

#### **OUTPUT CAPACITOR, COUT**

The output capacitor  $C_{OUT}$  directly affects the magnitude of the output ripple voltage. In general, the higher the value of  $C_{OUT}$ , the lower the output ripple magnitude. Multilayer ceramic capacitors with low ESR are the best choice. At the lighter loads, the low ESR ceramics offer a much lower  $V_{OUT}$  ripple that the higher ESR tantalums of the same value. At the higher loads, the ceramics offer a slightly lower  $V_{OUT}$  ripple magnitude than the tantalums of the same value. However, the dv/dt of the  $V_{OUT}$  ripple with the ceramics is much lower that the tantalums under all load conditions. Capacitor voltage rating must be sufficient, 25V or greater is recommended. Examples of suitable capacitors are: TDK C3216X5R1E475K, Panasonic ECJ3YB1E475K, ECJMFB1E475K and ECJ4YB1E475K.

Some ceramic capacitors, especially those in small packages, exhibit a strong capacitance reduction with the increased applied voltage (DC bias effect). The capacitance value can fall below half of the nominal capacitance. Too low output capacitance can make the boost converter unstable. Output capacitors DC bias effect should be better than -50% at 18V.

### INPUT CAPACITOR, CIN

The input capacitor  $C_{IN}$  directly affects the magnitude of the input ripple voltage and to a lesser degree the  $V_{OUT}$  ripple. A higher value  $C_{IN}$  will give a lower  $V_{IN}$  ripple. Capacitor voltage rating must be sufficient, 10V or greater is recommended.

### OUTPUT DIODE, D<sub>1</sub>

A schottky diode should be used for the output diode. Peak repetitive current should be greater than inductor peak current (800mA) to ensure reliable operation. Schottky diodes with a low forward drop and fast switching speeds are ideal for increasing efficiency in portable applications. Choose a reverse breakdown voltage of the schottky diode significantly larger (~30V) than the output voltage. Do not use ordinary rectifier diodes, since slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer. Example of suitable diode is: Central Semiconductor CMMSH1-40.

#### EMI FILTER COMPONENTS Csw, Rsw

EMI filter (R<sub>SW</sub> and C<sub>SW</sub>) on the SW pin can be used to suppress EMI caused by fast switching. These components should be as near as possible to the SW pin to ensure reliable operation. 50V or greater voltage rating is recommended for capacitor.

#### INDUCTOR, L1

A 10uH shielded inductor is suggested for LP3958 boost converter. The inductor should have a saturation current rating higher than the rms current it will experience during circuit operation (600mA). Less than  $300m\Omega$  ESR is suggested for high efficiency and sufficient output current. Open core inductors cause flux linkage with circuit components and interfere with the normal operation of the circuit. This should be avoided. For high efficiency, choose an inductor with a high frequency core material such as ferrite to reduce the core losses. To minimize radiated noise, use a toroid, pot core or shielded core inductor. The inductor should be connected to the SW pin as close to the IC as possible. Examples of suitable inductors are: TDK VLF4012AT-100MR79, VLF4018BT-100MR90, VLF5014AT-100MR92, Coilcraft LPS4018-103ML.

#### LIST OF RECOMMENDED EXTERNAL COMPONENTS

| Symbol             | Symbol Explanation                 | Value                | Unit         | Туре                               |  |  |

|--------------------|------------------------------------|----------------------|--------------|------------------------------------|--|--|

| $C_{VDD}$          | C between VDD1,2 and GND           | 100                  | nF           | Ceramic, X7R / X5R                 |  |  |

| C <sub>VDDIO</sub> | C between VDDIO and GND            | 100                  | nF           | Ceramic, X7R / X5R                 |  |  |

| C <sub>VDDA</sub>  | C between VDDA and GND             | 1                    | μF           | Ceramic, X7R / X5R                 |  |  |

| C <sub>OUT</sub>   | C between FB and GND               | 2 x 4.7 or 1 x<br>10 | μF           | Ceramic, X7R / X5R, tolerance ±10% |  |  |

|                    | Maximum DC bias effect @ 18V       | -50                  | %            | ±10%                               |  |  |

| $C_{IN}$           | C between battery voltage and GND  | 10                   | μF           | Ceramic, X7R / X5R                 |  |  |

|                    | L between SW and V <sub>BAT</sub>  | 10                   | μΗ           | Chielded industry law ECD          |  |  |

| L <sub>1</sub>     | Saturation current                 | 600                  | mA           | Shielded inductor, low ESR         |  |  |

| C <sub>VREF</sub>  | C between V <sub>REF</sub> and GND | 100                  | nF           | Ceramic, X7R / X5R                 |  |  |

| R <sub>KEY</sub>   | R between I <sub>KEY</sub> and GND | 8.2                  | kΩ           | ±1%                                |  |  |

| $R_{RT}$           | R between I <sub>RT</sub> and GND  | 82                   | kΩ           | ±1%                                |  |  |

|                    | Rectifying diode (Vf @ maxload)    | 0.3-0.5              | V            |                                    |  |  |

| $D_1$              | Reverse voltage                    | 30                   | V            | Schottky diode                     |  |  |

|                    | Repetitive peak current            | 800                  | mA           |                                    |  |  |

| C <sub>SW</sub>    | C in EMI filter                    | 100                  | pF           | Ceramic, X7R / X5R, 50V            |  |  |

| R <sub>SW</sub>    | R in EMI filter                    | 390                  | Ω            | ±1%                                |  |  |

| LEDs               |                                    |                      | User Defined |                                    |  |  |

Note: See Application Note AN-1436 "Design and Programming Examples for Lighting Management Unit LP3958" for more information on how to design with LP3958

# Table 5. LP3958 Control Register Names and Default Values

| ADDR<br>(HEX) | REGISTER           | D7       | D6        | D5           | D4                | D3                | D2                | D1              | D0         |  |

|---------------|--------------------|----------|-----------|--------------|-------------------|-------------------|-------------------|-----------------|------------|--|

| 00            | Control Register   | KEYP_PWM | EN_KEYP   | CC_SW        |                   | K1SW              | K2SW              | K3SW            |            |  |

|               |                    | 0        | 0         | 1            |                   | 0                 | 0                 | 0               |            |  |

| 01            | Keypad             |          |           | BALANCE[2:0] |                   |                   | BRIGHT[2:0]       |                 | OVL        |  |

|               |                    |          | 0         | 0            | 0                 | 0                 | 0                 | 0               | 0          |  |

| 02            | Keypad Max Current |          |           | IK1          | [1:0]             | IK2               | [1:0]             | IK3             | [1:0]      |  |

|               |                    |          |           | 0            | 0                 | 0                 | 0                 | 0               | 0          |  |

| 03            | WLED Control       |          |           | SLOPE        | FADE_SEL          | EN_FADE           | DISPL             | EN_MAIN         | EN_SUB     |  |

|               |                    |          |           | 0            | 0                 | 0                 | 0                 | 0               | 0          |  |

| 04            | MAIN Current       |          | MAIN[7:0] |              |                   |                   |                   |                 |            |  |

|               |                    | 0        | 0         | 0            | 0                 | 0                 | 0                 | 0               | 0          |  |

| 05            | SUB Current        | SUB[7:0] |           |              |                   |                   |                   |                 | 1          |  |

|               |                    | 0        | 0         | 0            | 0                 | 0                 | 0                 | 0               | 0          |  |

| 06            | GPIO Control       |          |           |              | EN_PWM_PIN        |                   |                   | OEN[2:0]        |            |  |

|               |                    |          |           |              | 0                 |                   | 0                 | 0               | 0          |  |

| 07            | GPIO Data          |          |           |              |                   |                   |                   | DATA[2:0]       |            |  |

|               |                    |          |           |              |                   |                   | 0                 | 0               | 0          |  |

| 0B            | Enables            |          | NSTBY     | EN_BOOST     |                   |                   | EN_AUTOLOA<br>D   |                 |            |  |

|               |                    |          | 0         | 0            |                   |                   | 1                 |                 |            |  |

| 0D            | Boost Output       |          |           |              | B008              | ST[7:0]           | •                 |                 | •          |  |

|               |                    | 0        | 0         | 0            | 0                 | 1                 | 0                 | 0               | 0          |  |

| 2B            | PWM Enable         |          |           |              | EN_EXT_K1_P<br>WM | EN_EXT_K2_P<br>WM | EN_EXT_K3_P<br>WM | EN_MAIN_PW<br>M | EN_SUB_PWM |  |

|               |                    |          |           |              | 0                 | 0                 | 0                 | 0               | 0          |  |

## LP3958 Register Bit Explanations

Each register is shown with a key indicating the accessibility of the each individual bit, and the initial condition:

Table 6. Register Bit Accessibility and Initial Condition

| Key   | Bit Accessibility   |

|-------|---------------------|

| RW    | Read/write          |

| R     | Read only           |

| -0,-1 | Condition after POR |

## CONTROL REGISTER (00H) - KEYPAD LEDS CONTROL REGISTER

| D7       | D6      | D5     | D4    | D3     | D2     | D1     | D0    |

|----------|---------|--------|-------|--------|--------|--------|-------|

| KEYP_PWM | EN_KEYP | cc_sw  |       | K1SW   | K2SW   | K3SW   |       |

| RW - 0   | RW - 0  | RW - 1 | R - 0 | RW - 0 | RW - 0 | RW - 0 | R - 0 |

| KEYP_PWM | Bit 7 | 0 - Internal KEYPAD PWM control disabled 1 - Internal KEYPAD PWM control enabled |

|----------|-------|----------------------------------------------------------------------------------|

| EN_KEYP  | Bit 6 | 0 – KEYPAD outputs disabled<br>1 – KEYPAD outputs enabled                        |

| cc_sw    | Bit 5 | 0 – Constant current sink mode<br>1 – Switch mode                                |

| K1SW     | Bit 3 | 0 – KEYPAD1 disabled<br>1 – KEYPAD1 enabled                                      |

| K2SW     | Bit 2 | 0 – KEYPAD2 disabled<br>1 – KEYPAD2 enabled                                      |

| кзѕw     | Bit 1 | 0 – KEYPAD3 disabled<br>1 – KEYPAD3 enabled                                      |

# KEYPAD (01H) - KEYPAD BALANCE AND BRIGHTNESS CONTROL REGISTER

| D7    | D6           | D5     | D4     | D3          | D2     | D1     | D0     |

|-------|--------------|--------|--------|-------------|--------|--------|--------|

|       | BALANCE[2:0] |        |        | BRIGHT[2:0] |        |        | OVL    |

| R - 0 | RW - 0       | RW - 0 | RW - 0 | RW - 0      | RW - 0 | RW - 0 | RW - 0 |

| BALANCE[2:0] | Bits 6-4 | PWM balance for KEYPAD outputs                                |

|--------------|----------|---------------------------------------------------------------|

| BRIGHT[2:0]  | Bits 3-1 | PWM brightness control for KEYPAD outputs                     |

| OVL          |          | 0 – Overlapping mode disabled<br>1 – Overlapping mode enabled |

# KEYPAD MAX CURRENT (02H) - MAXIMUM KEYPAD CURRENT CONTROL REGISTER

| D7    | D6       | D5     | D4       | D3     | D2       | D1     | D0     |

|-------|----------|--------|----------|--------|----------|--------|--------|

|       | IK1[1:0] |        | IK2[1:0] |        | IK3[1:0] |        |        |

| R - 0 | R - 0    | RW - 0 | RW - 0   | RW - 0 | RW - 0   | RW - 0 | RW - 0 |

| Maximum current for KEY1,2,3 driver |                         |  |  |  |  |  |  |

|-------------------------------------|-------------------------|--|--|--|--|--|--|

| IK1,2,3[1:0] Maximum output current |                         |  |  |  |  |  |  |

| 00                                  | 0.25 × I <sub>MAX</sub> |  |  |  |  |  |  |

| 01                                  | 0.50 × I <sub>MAX</sub> |  |  |  |  |  |  |

| 10                                  | 0.75 × I <sub>MAX</sub> |  |  |  |  |  |  |

| 11                                  | 1.00 × I <sub>MAX</sub> |  |  |  |  |  |  |

# WLED CONTROL (03H) - WLED CONTROL REGISTER

| D7    | D6    | D5     | D4       | D3      | D2     | D1      | D0     |

|-------|-------|--------|----------|---------|--------|---------|--------|

|       |       | SLOPE  | FADE_SEL | EN_FADE | DISPL  | EN_MAIN | EN_SUB |

| R - 0 | R - 0 | RW - 0 | RW - 0   | RW - 0  | RW - 0 | RW - 0  | RW - 0 |

| SLOPE    | Bit 5 | 0 – fade execution time 0.65 sec (full scale) 1 – fade execution time 1.3 sec (full scale) |

|----------|-------|--------------------------------------------------------------------------------------------|

| FADE_SEL | Bit 4 | 0 – fade control for MAIN<br>1 – fade control for SUB                                      |

| EN_FADE  | Bit 3 | 0 – automatic fade disabled<br>1 – automatic fade enabled                                  |

| DISPL    | Bit 2 | 0 - MAIN and SUB individual control 1 - MAIN and SUB controlled with MAIN DAC              |

| EN_MAIN  | Bit 1 | 0 – MAIN output disabled<br>1 – MAIN output enabled                                        |

| EN_SUB   | Bit 0 | 0 – SUB output disabled<br>1 – SUB output enabled                                          |

# MAIN CURRENT (04H) - MAIN CURRENT CONTROL REGISTER

| D7     | D6        | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

|--------|-----------|----|----|----|----|----|----|--|--|--|--|

|        | MAIN[7:0] |    |    |    |    |    |    |  |  |  |  |

| RW - 0 |           |    |    |    |    |    |    |  |  |  |  |

# SUB CURRENT (05H) – SUB CURRENT CONTROL REGISTER

| D7       | D6     | D5     | D4     | D3     | D2     | D1     | D0     |  |  |  |

|----------|--------|--------|--------|--------|--------|--------|--------|--|--|--|

| SUB[7:0] |        |        |        |        |        |        |        |  |  |  |

| RW - 0   | RW - 0 | RW - 0 | RW - 0 | RW - 0 | RW - 0 | RW - 0 | RW - 0 |  |  |  |

| MAIN, SUB current adjustment |                             |  |  |  |  |

|------------------------------|-----------------------------|--|--|--|--|

| MAIN[7:0], SUB[7:0]          | Typical driver current (mA) |  |  |  |  |

| 0000 0000                    | 0                           |  |  |  |  |

| 0000 0001                    | 0.1                         |  |  |  |  |

| 0000 0010                    | 0.2                         |  |  |  |  |

| 0000 0011                    | 0.3                         |  |  |  |  |

| 0000 0100                    | 0.4                         |  |  |  |  |

|                              |                             |  |  |  |  |

| 1111 1101                    | 25.3                        |  |  |  |  |

| 1111 1110                    | 25.4                        |  |  |  |  |

| 1111 1111                    | 25.5                        |  |  |  |  |

# **GPIO CONTROL (06H) – GPIO CONTROL REGISTER**

| D7    | D6    | D5    | D4         | D3    | D2     | D1       | D0     |

|-------|-------|-------|------------|-------|--------|----------|--------|

|       |       |       | EN_PWM_PIN |       |        | OEN[2:0] |        |

| R - 0 | R - 0 | R - 0 | RW - 0     | R - 0 | RW - 0 | RW - 0   | RW - 0 |

| EN_PWM_PIN | Bit 4    | 0 – External PWM pin disabled<br>1 – External PWM pin enabled |

|------------|----------|---------------------------------------------------------------|

| OEN[2:0]   | Bits 2-0 | 0 – GPIO pin set as a input<br>1 – GPIO pin set as a output   |

## **GPIO DATA (07H) - GPIO DATA REGISTER**

| D7    | D6    | D5    | D4    | D3    | D2     | D1        | D0     |

|-------|-------|-------|-------|-------|--------|-----------|--------|

|       |       |       |       |       |        | DATA[2:0] |        |

| R - 0 | R - 0 | R - 0 | R - 0 | R - 0 | RW - 0 | RW - 0    | RW - 0 |

| DATA[2:0] | Bits 2-0 | GPIO data register bits  |

|-----------|----------|--------------------------|

| שרות[ב.0] | DII3 2 0 | Of 10 data register bits |

## **ENABLES (0BH) – ENABLES REGISTER**

| D7    | D6     | D5       | D4    | D3    | D2              | D1    | D0    |

|-------|--------|----------|-------|-------|-----------------|-------|-------|

|       | NSTBY  | EN_BOOST |       |       | EN_AUTOLOA<br>D |       |       |

| R - 0 | RW - 0 | RW - 0   | R - 0 | R - 0 | RW - 1          | R - 0 | R - 0 |

| NSTBY       | Bit 6 | 0 – LP3958 standby mode<br>1 – LP3958 active mode               |

|-------------|-------|-----------------------------------------------------------------|

| EN_BOOST    | Bit 5 | 0 – Boost converter disabled<br>1 – Boost converter enabled     |

| EN_AUTOLOAD | Bit 2 | 0 – Boost active load disabled<br>1 – Boost active load enabled |

# **BOOST OUTPUT (0DH) - BOOST OUTPUT VOLTAGE CONTROL REGISTER**

| D7     | D6         | D5     | D5 D4  |        | D2     | D1     | D0     |  |

|--------|------------|--------|--------|--------|--------|--------|--------|--|

|        | BOOST[7:0] |        |        |        |        |        |        |  |

| RW - 0 | RW - 0     | RW - 0 | RW - 0 | RW - 1 | RW - 0 | RW - 0 | RW - 0 |  |

| BOOST output voltage adjustment |                                  |  |  |  |  |

|---------------------------------|----------------------------------|--|--|--|--|

| BOOST[7:0]                      | Typical boost output voltage (V) |  |  |  |  |

| 0000 1000                       | 8.00                             |  |  |  |  |

| 0000 1001                       | 9.00                             |  |  |  |  |

| 0000 1010                       | 10.00                            |  |  |  |  |

| 0000 1011                       | 11.00                            |  |  |  |  |

| 0000 1100                       | 12.00                            |  |  |  |  |

| 0000 1101                       | 13.00                            |  |  |  |  |

| 0000 1110                       | 14.00                            |  |  |  |  |

| 0000 1111                       | 15.00                            |  |  |  |  |

| 0001 0000                       | 16.00                            |  |  |  |  |

| 0001 0001                       | 17.00                            |  |  |  |  |

| 0001 0010                       | 18.00                            |  |  |  |  |

# PWM ENABLE (2BH) – EXTERNAL PWM CONTROL REGISTER

| D7    | D6    | D5    | D4                | D3                | D2                | D1              | D0         |

|-------|-------|-------|-------------------|-------------------|-------------------|-----------------|------------|

|       |       |       | EN_EXT_K1_P<br>WM | EN_EXT_K2_P<br>WM | EN_EXT_K3_P<br>WM | EN_MAIN_PW<br>M | EN_SUB_PWM |

| R - 0 | R - 0 | R - 0 | RW - 0            | RW - 0            | RW - 0            | RW - 0          | RW - 0     |

| EN_EXT_K1_PWM | Bit 4 | 0 – External PWM control for KEY1 disabled<br>1 – External PWM control for KEY1 enabled |

|---------------|-------|-----------------------------------------------------------------------------------------|

| EN_EXT_K2_PWM | Bit 3 | 0 – External PWM control for KEY2 disabled<br>1 – External PWM control for KEY2 enabled |

| EN_EXT_K3_PWM | Bit 2 | 0 – External PWM control for KEY3 disabled<br>1 – External PWM control for KEY3 enabled |

www.ti.com

| EN_EXT_MAIN_PWM | Rit 1  | 0 – External PWM control for MAIN disabled<br>1 – External PWM control for MAIN enabled |

|-----------------|--------|-----------------------------------------------------------------------------------------|

| EN_EXT_SUB_PWM  | Rit () | 0 – External PWM control for SUB disabled<br>1 – External PWM control for SUB enabled   |

## SNVS423C - JANUARY 2006-REVISED MARCH 2013

# **REVISION HISTORY**

| Changes from Revision B (March 2013) to Revision C |                                                    |  |    |  |  |  |  |  |

|----------------------------------------------------|----------------------------------------------------|--|----|--|--|--|--|--|

| •                                                  | Changed layout of National Data Sheet to TI format |  | 28 |  |  |  |  |  |

# PACKAGE OPTION ADDENDUM

11-Apr-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

| LP3958TL/NOPB    | ACTIVE | DSBGA        | YZR                | 25   | 250            | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -30 to 85    | SJHB              | Samples |

| LP3958TLX/NOPB   | ACTIVE | DSBGA        | YZR                | 25   | 3000           | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -30 to 85    | SJHB              | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

# PACKAGE MATERIALS INFORMATION

www.ti.com 21-Mar-2013

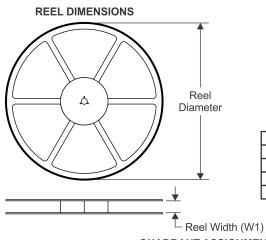

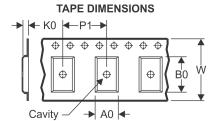

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

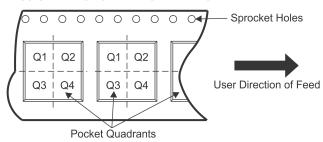

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LP3958TL/NOPB  | DSBGA           | YZR                | 25 | 250  | 178.0                    | 8.4                      | 2.69       | 2.69       | 0.76       | 4.0        | 8.0       | Q1               |

| LP3958TLX/NOPB | DSBGA           | YZR                | 25 | 3000 | 178.0                    | 8.4                      | 2.69       | 2.69       | 0.76       | 4.0        | 8.0       | Q1               |

www.ti.com 21-Mar-2013

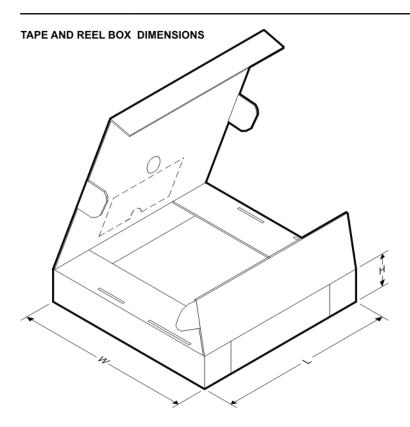

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| LP3958TL/NOPB  | DSBGA        | YZR             | 25   | 250  | 210.0       | 185.0      | 35.0        |  |

| LP3958TLX/NOPB | DSBGA        | YZR             | 25   | 3000 | 210.0       | 185.0      | 35.0        |  |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.