# LM3549 High Power Sequential LED Driver

Check for Samples: LM3549

## **FEATURES**

- Over-Current Protection

- Over-Temperature Protection

- I<sup>2</sup>C Compatible Interface

- Under-Voltage Lockout

- LED Open and Short Protection and Detection

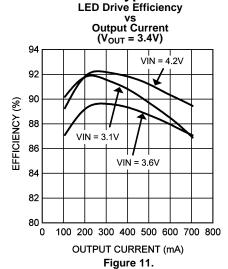

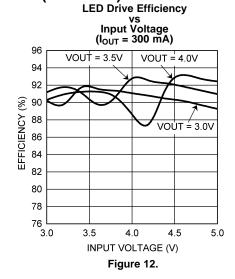

- 95% Peak Efficiency Buck-Boost Converter

- NVM Memory for Calibration Data and Standalone Usage without I<sup>2</sup>C Control

- Soft Start

## **APPLICATIONS**

- Portable Video Projectors

- High Power LED Driving

### **KEY SPECIFICATIONS**

- Integrated buck-boost Converter

- Programmable LED Drivers

- 700 mA Maximum Drive Current

- ±6% Current Accuracy Over Temperature

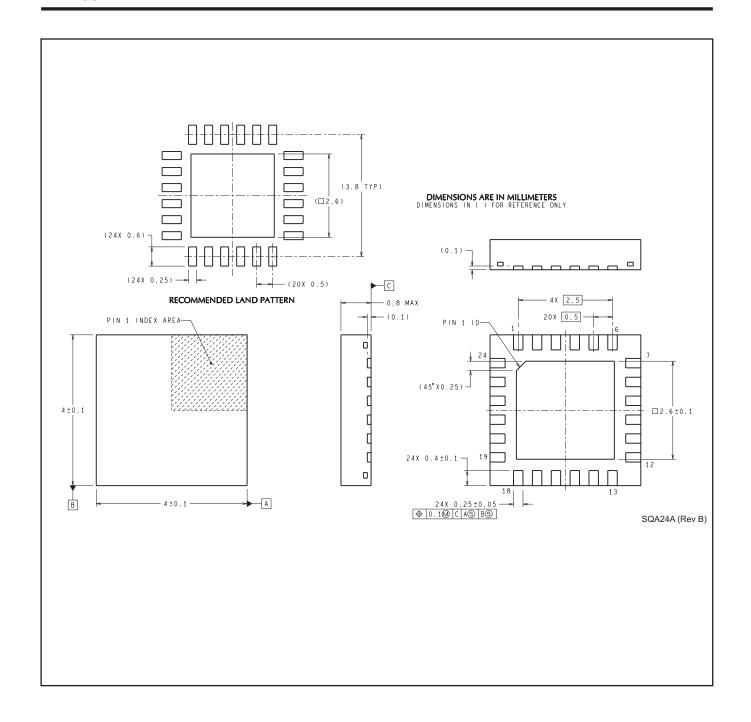

- 24-pin WQFN Package

## **DESCRIPTION**

The LM3549 is a high power LED driver with up to 700mA output current. It has three constant current LED drivers and a buck boost SMPS for driving RGB LEDs with high efficiency. LED drivers are designed for sequential drive so only one driver can be enabled at a time.

LED driver output current settings can be stored to integrated non-volatile memory which allows standalone operation without I<sup>2</sup>C interface. Non-volatile memory is rewritable so current setting can be changed if needed.

The LM3549 has a fault detection feature that can detect several different fault conditions. In case of a fault error flags are set and FAULT output sends interrupt to control logic. Error flags can be read through I<sup>2</sup>C interface.

Total brightness can be controlled with PWM input or with master fader register if I<sup>2</sup>C interface is used.

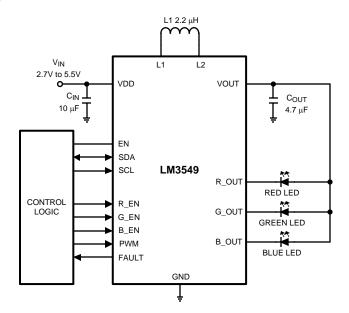

Figure 1. Typical Application Circuit

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

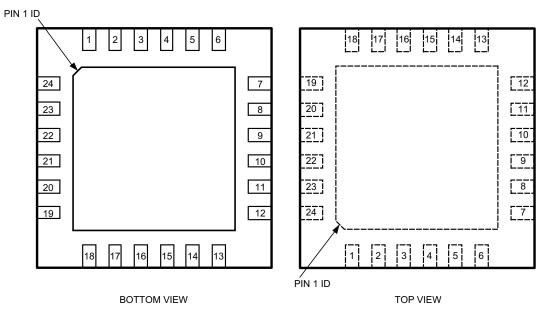

Figure 2. 24-Pin WQFN Package, No Pullback See package number RTW0024A

## **Pin Descriptions**

|        | Fin Descriptions |      |                                                                  |  |  |  |  |  |  |

|--------|------------------|------|------------------------------------------------------------------|--|--|--|--|--|--|

| Name   | Pin No.          | Туре | Description                                                      |  |  |  |  |  |  |

| NC     | 1                |      |                                                                  |  |  |  |  |  |  |

| L1     | 2                | Α    | Inductor positive terminal 1                                     |  |  |  |  |  |  |

| L1     | 3                | Α    | Inductor positive terminal 2                                     |  |  |  |  |  |  |

| GND_SW | 4                | G    | SMPS ground                                                      |  |  |  |  |  |  |

| L2     | 5                | Α    | Inductor negative terminal 1                                     |  |  |  |  |  |  |

| L2     | 6                | Α    | Inductor negative terminal 2                                     |  |  |  |  |  |  |

| VOUT   | 7                | Α    | Buck boost output terminal 1                                     |  |  |  |  |  |  |

| NC     | 8                |      |                                                                  |  |  |  |  |  |  |

| VOUT   | 9                | Α    | Buck boost output terminal 2                                     |  |  |  |  |  |  |

| R_EN   | 10               | DI   | Red output enable                                                |  |  |  |  |  |  |

| VDDS   | 11               | Р    | Supply voltage                                                   |  |  |  |  |  |  |

| G_EN   | 12               | DI   | Green output enable                                              |  |  |  |  |  |  |

| B_EN   | 13               | DI   | Blue output enable                                               |  |  |  |  |  |  |

| PWM    | 14               | DI   | Master fader input                                               |  |  |  |  |  |  |

| GND    | 15               | G    | Ground                                                           |  |  |  |  |  |  |

| R_OUT  | 16               | Α    | R output                                                         |  |  |  |  |  |  |

| G_OUT  | 17               | Α    | G output                                                         |  |  |  |  |  |  |

| B_OUT  | 18               | Α    | B output                                                         |  |  |  |  |  |  |

| FAULT  | 19               | DO   | Fault detection interrupts output. Active LOW open drain output. |  |  |  |  |  |  |

| SDA    | 20               | DI/O | I2C Data                                                         |  |  |  |  |  |  |

| SCL    | 21               | DI   | I2C Clock                                                        |  |  |  |  |  |  |

| EN     | 22               | DI   | Enable and IO reference level                                    |  |  |  |  |  |  |

| VDDP   | 23               | Р    | SMPS supply voltage                                              |  |  |  |  |  |  |

| NC     | 24               |      |                                                                  |  |  |  |  |  |  |

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **Absolute Maximum Ratings** (1) (2)(3)

| 7 Doorato maximum rtatingo                 |                                             |

|--------------------------------------------|---------------------------------------------|

| VDD and VOUT pins                          | -0.3V to 6.0V                               |

| Voltage on all other pins                  | -0.3V (V <sub>IN</sub> +0.3V)<br>w/6.0V max |

| Continuous Power Dissipation (4)           | Internally Limited                          |

| Junction Temperature (T <sub>J-MAX</sub> ) | +150°C                                      |

| Storage Temperature Range                  | -65°C to +150°C                             |

| Maximum Lead Temperature (Soldering)       | (5)                                         |

| ESD Rating <sup>(6)</sup>                  |                                             |

| Human Body Model                           | 2.0kV                                       |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is specified. Operating Ratings do not imply performance limits. For performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pin.

- (3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- (4) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>=+150°C (typ.) and disengages at T<sub>J</sub>=+140°C (typ.).

- (5) For detailed soldering specifications and information, please refer to Application Note AN-1187: Leadless Leadframe Package (LLP).(SNOA401)

- (6) The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. (MIL-STD-883 3015.7)

## Operating Ratings (1) (2)

| Input Voltage Range                                        | 2.7V to 5.5V    |

|------------------------------------------------------------|-----------------|

| Junction Temperature (T <sub>J</sub> ) Range               | −30°C to +125°C |

| Ambient Temperature (T <sub>A</sub> ) Range <sup>(3)</sup> | −30°C to +85°C  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is specified. Operating Ratings do not imply performance limits. For performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pin.

- (3) In applications where high-power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = +125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

#### **Thermal Properties**

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), WQFN-24 Package $^{(1)}$ | 35 - 50°C/W |

|------------------------------------------------------------------------------------|-------------|

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

## Electrical Characteristics (1) (2)

Limits in standard type face are for  $T_A$  = 25°C. Limits in **boldface type** apply over the full operating ambient temperature range (-30°C  $\leq T_A \leq +85$ °C). Unless otherwise noted, specifications apply to Figure 1 with:  $V_{IN}$  = 3.6V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F and L1 = 2.2  $\mu$ H. (3)

|                         | Parameter                  | Test Conditions                      | Min | Тур | Max | Units |

|-------------------------|----------------------------|--------------------------------------|-----|-----|-----|-------|

| V <sub>IN</sub>         | Supply voltage             | Minimum voltage for startup          | 2.7 |     |     | V     |

|                         |                            | Full output power                    | 3.1 |     | 5.5 |       |

| I <sub>IN</sub>         | Shutdown supply current    | EN low                               |     |     | 1   | μA    |

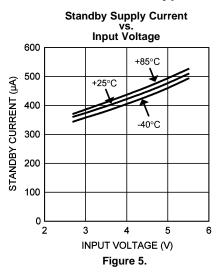

| (IVDDP + IVDDS)         | Standby supply current     | EN High, x_EN low                    |     | 0.4 | 1   | mA    |

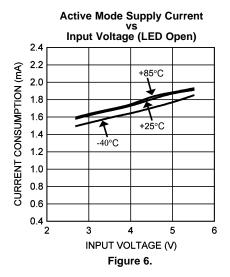

| I <sub>IN</sub> (IVDDS) | Active mode supply current | EN High, x_EN high, RGB outputs open |     | 1.6 | 3   | mA    |

- (1) All voltages are with respect to the potential at the GND pin.

- (2) Min and Max limits are specified by design, test, or statistical analysis. Typical (Typ) numbers represent the most likely norm.

- (3) C<sub>IN</sub>, C<sub>OUT</sub>: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

# Electrical Characteristics(1) (2) (continued)

Limits in standard type face are for  $T_A$  = 25°C. Limits in **boldface type** apply over the full operating ambient temperature range (-30°C  $\le T_A \le +85$ °C). Unless otherwise noted, specifications apply to Figure 1 with:  $V_{IN}$  = 3.6V,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F and L1 = 2.2  $\mu$ H.  $^{(3)}$

|                       | Parameter                              | Test Conditions                      | Min      | Тур  | Max      | Units |

|-----------------------|----------------------------------------|--------------------------------------|----------|------|----------|-------|

| Drivers (R_OL         | UT, G_OUT, B_OUT)                      |                                      |          |      |          |       |

| I <sub>OUT MIN</sub>  | Minimum output current                 |                                      | 97       | 107  | 118      | mA    |

| I <sub>OUT MAX</sub>  | Maximum output current                 |                                      | 690      | 705  | 720      | mA    |

| I <sub>LIM</sub>      | Current limit                          |                                      |          |      | 15       | %     |

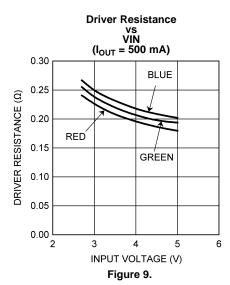

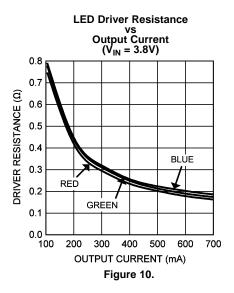

| R <sub>OUT</sub>      | Driver on resistance                   | I <sub>OUT</sub> = 500 mA            |          | 0.2  |          | Ω     |

| Driver System         | n Characteristics                      |                                      |          |      |          |       |

| I <sub>OUT</sub>      | Current accuracy                       | After settling, 500 mA (ISET = 276h) | -6       | ±1   | +6       | %     |

| t <sub>r</sub>        | Current rise time                      |                                      |          |      | 50       | μs    |

| t <sub>f</sub>        | Current fall time                      |                                      |          |      | 50       | μs    |

| I <sub>STEP</sub>     | Current step                           |                                      |          | 0.64 |          | mA    |

| Buck or Boos          | t Converter                            |                                      |          |      |          |       |

|                       | Positive current limit range           | Programmable                         | 500      |      | 2000     | mA    |

|                       | Positive current limit accuracy        | Set to 1000 mA                       | -20      |      | +20      | %     |

|                       | Negative current limit range           | Programmable                         | 550      |      | 2200     | mA    |

|                       | Negative current limit accuracy        | Set to 550 mA                        | -20      |      | +20      | %     |

| V <sub>OUT MAX</sub>  | Maximum output voltage                 |                                      |          |      | 4.6      | V     |

| f <sub>SW</sub>       | Switching frequency                    |                                      | 2.25     | 2.4  | 2.55     | MHz   |

| r <sub>DSON P1S</sub> | P1 on resistance in buck mode (small)  |                                      |          | 100  |          | mΩ    |

| r <sub>DSON P1L</sub> | P1 on resistance in boost mode (large) |                                      |          | 55   |          | mΩ    |

| r <sub>DSON N1</sub>  | N1 on resistance                       |                                      |          | 160  |          | mΩ    |

| r <sub>DSON N3</sub>  | N3 on resistance in buck mode          | VOUT = 0.8V                          |          | 70   |          | mΩ    |

| r <sub>DSON P2</sub>  | P2 on resistance in boost mode         | VOUT = 3.6V                          |          | 65   |          | mΩ    |

| r <sub>DSON N2</sub>  | N2 on resistance                       |                                      |          | 150  |          | mΩ    |

| PWM Input (G          | Blobal brightness control)             | -                                    |          |      |          |       |

| f <sub>PWM</sub>      | PWM frequency                          | 7-bit resolution                     | 4        |      | 20       | kHz   |

|                       |                                        | 8-bit resolution                     | 4        |      | 10       |       |

|                       |                                        | 9-bit resolution                     | 4        |      | 5        |       |

| t <sub>TO</sub>       | Timeout                                | For PWM zero                         | 260      | 300  | 340      | μs    |

| t <sub>ON</sub>       | Minimum on time                        |                                      |          | 1    |          | μs    |

| t <sub>OFF</sub>      | Minimum off time                       |                                      |          | 1    |          | μs    |

| Logic Input El        | N                                      |                                      |          |      |          |       |

| VIL                   | Logic input low level                  |                                      |          |      | 0.5      | V     |

| VIH                   | Logic input high level                 |                                      | 1.2      |      |          | V     |

|                       | SDA, SCL, R_EN, G_EN, B_EN, PV         | VM                                   |          |      |          |       |

| VIL                   | Logic input low level                  | VEN = 1.65 to VDD                    |          |      | 0.2* VEN | V     |

| VIH                   | Logic input high level                 | VEN = 1.65 to VDD                    | 0.8* VEN |      |          | V     |

| Logic Outputs         | s SDA, FAULT                           |                                      |          |      |          |       |

| VOL                   | Output low level                       | I <sub>OUT</sub> = 3 mA              |          |      | 0.5      | V     |

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

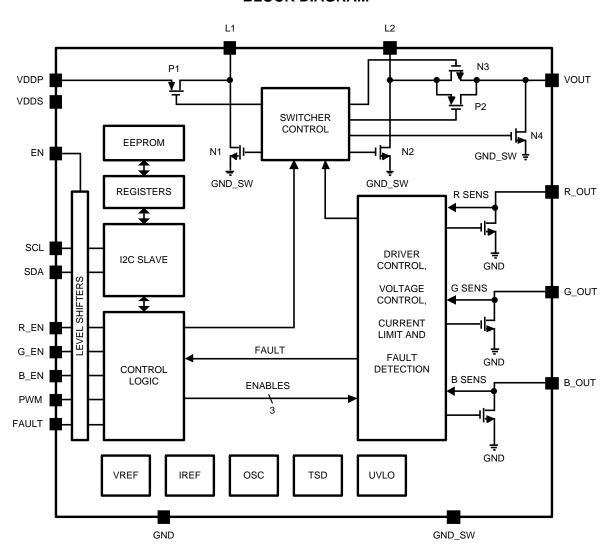

## **BLOCK DIAGRAM**

Figure 3. LM3549 Block Diagram

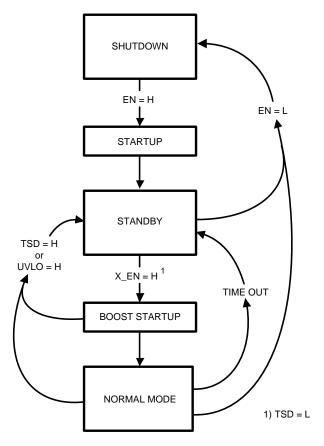

### **Modes of Operation**

Figure 4. Modes of Operation

- **SHUTDOWN:** Shutdown mode is entered always if EN is low or internal Power On Reset (POR) is active. Power on reset will activate during the chip startup or when the supply voltage VDD falls below 1.5V. This is the low power consumption mode, when all circuit functions are disabled.

- **STARTUP:** When EN input is pulled high, the internal startup sequence powers up all the needed internal blocks (VREF, Oscillator, etc.). EEPROM values are also read to registers during Startup.

- **STANDBY:** After Startup device enters Standby mode. In standby mode all support blocks are active but buckboost converter and the drivers are disabled. Control registers can be written in this mode and the control bits are effective immediately. EEPROM writing is allowed only in standby mode.

- **BOOST STARTUP:** Soft start for boost output is generated in the boost startup mode. The boost output is raised in a low current mode. Soft start time can be set with registers. The boost startup is entered from Standby if any of the X\_EN inputs is pulled high.

- **NORMAL:** During normal mode user controls the chip using the X\_EN inputs. In normal mode buck-boost converter and drivers are active. Device returns to standby mode if all X\_EN inputs are low for time period set by Time out register. If EN input is pulled low device goes to shutdown mode.

- **TSD:** If the chip temperature rises too high, the thermal shutdown (TSD) disables the chip operation and Standby mode is entered until no thermal shutdown event is present.

Submit Documentation Feedback

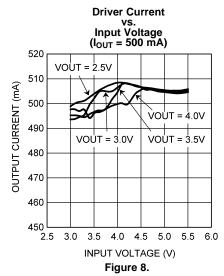

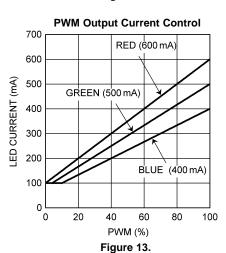

## **Typical Performance Characteristics**

**NSTRUMENTS**

## **Typical Performance Characteristics (continued)**

#### OPERATION DESCRIPTION

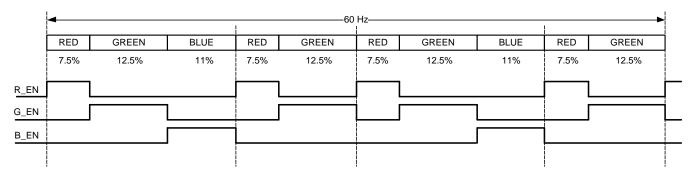

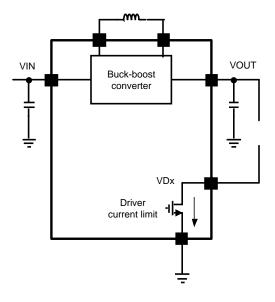

LM3549 is a sequential LED driver for portable video projectors. It has three high current low side drivers and a buck-boost DC-DC converter. Only single LED can be enabled at any given time. DC-DC converter quickly adjusts the output voltage to a suitable level based on each LED's forward voltage. This minimizes the power dissipation at the drivers and maximizes the system efficiency.

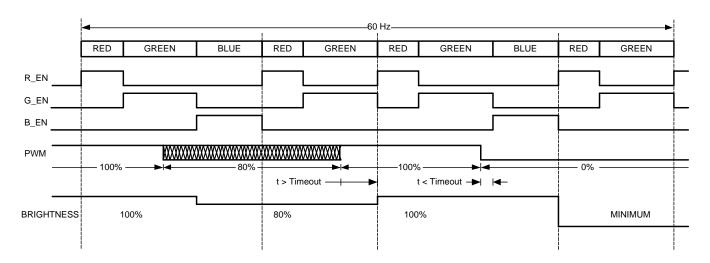

Figure 15 shows a typical timing of a portable video projector light source. Each frame is divided into 10 individual color sequences. White balance is achieved by adjusting the driver currents.

Timing of LM3549 depends solely on the R\_EN, G\_EN and B\_EN inputs. Each driver's current is set with I<sup>2</sup>C registers and current levels can be stored to internal EEPROM. After correct current values are stored to EEPROM LM3549 can be used in application without I<sup>2</sup>C interface.

| Full frame | 1/60Hz             | 16.66 ms |

|------------|--------------------|----------|

| Red        | Full frame x 7.5%  | 1.25 ms  |

| Green      | Full frame x 11%   | 1.822 ms |

| Blue       | Full frame x 12.5% | 2.08 ms  |

Figure 15. Timing Chart

## **CONTROL INTERFACE**

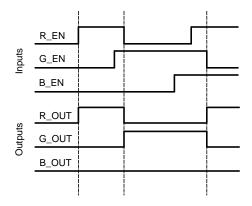

Even though each driver has its own control input only one driver can be enabled at any given time. If second control is pulled high while previous color is active second output won't be enabled until the first input is pulled low. This can be seen on Figure 16. G EN is pulled high while R\_EN is still high. G\_OUT is not activated until R EN is pulled low. Next B EN and R EN are both pulled high while G EN is high. When G EN is pulled low R OUT is enabled because R EN has higher priority (Priority order: RGB).

Figure 16. Control Signals

Copyright © 2010-2013, Texas Instruments Incorporated

#### **CONTROL REGISTERS**

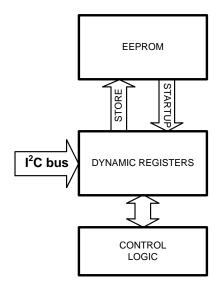

Figure 17 shows the structure of the control registers. Control registers consists of volatile dynamic registers and non volatile EEPROM.

Figure 17. Register Structure

All I<sup>2</sup>C register read write commands are done to volatile dynamic registers. Dynamic registers are also used to set the device parameters. All registers except FAULT and EEPROM CONTROL register can be stored to EEPROM. EEPROM values are automatically read to dynamic registers during startup. This makes device use very versatile. After calibration device can be used even without I<sup>2</sup>C control. If system has I<sup>2</sup>C bus, control registers can be written to adjust parameters on the fly. If registers need to be set back to default values this can be done by first writing 04h to register 40h (EE init bit to "1") followed by 01h to register 40h (EE read bit to "1").

#### **EEPROM PROGRAMMING**

EEPROM values can be rewritten if device needs recalibration. This can be done for example if white point changes due to aging effect of the LEDs. To store current register values to EEPROM user needs to first write 04h to register 40h (EE init bit to "1") followed by 02h to register 40h (EE prog bit to "1"). LM3549 Internal charge pump generates the high voltage required for programming the EEPROM. To be able to generate this high voltage Vin needs to be set to 5V during EEPROM programming. EEPROM programming should be completed within approximately 200 ms. Once EEPROM programming is completed LM3549 sets EE\_ready bit to 1. After this Vin voltage can be set back to normal operating level. EEPROM programming should always be done in standby mode.

### **CURRENT SETTING**

There are three 10 bit current settings for each driver. 10 bits are divided into two eight bit registers. First register holds the eight least significant bits (LSB) and the second register holds the two most significant bits (MSB). These settings are grouped into three banks. IR0, IG0 and IB0 form a bank0; IR1, IG1 and IB1 form a bank1 and IR2, IG2 and IB2 form a bank2. For example IR0\_MSB holds the two MSB for red on bank0 and IR0\_LSB the eight LSB for red on bank0. Bank is selected with BANK\_SEL register (00 = bank0, 01 = bank1 and 10 or 11 = bank2).

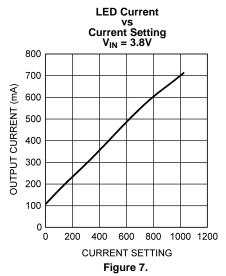

Current setting is linear up to 550mA output current (see figure LED Current vs Current Setting in Typical Performance Characteristics). 550mA current is achieved with current setting  $I_{SET} = 710$ . After this the current step decreases slightly. For currents up to 550 mA current setting can be calculated using formula:

$I_{SET}$  = (target current in mA - 100 mA)/(650mA/1024)

Fot currents between 550mA and 700mA current setting can be calculated using formula:

$I_{SFT}$  = (target current in mA - 550 mA)/0.479 mA + 710

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

#### **BRIGHTNESS CONTROL**

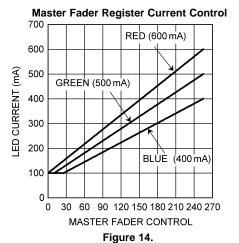

Output current of all drivers can be adjusted using PWM input or FADER register. This can be used to easilly adjust the total brightness of the LEDs. Brightness control function can be enabled from the CTRL register as seen in table below. In case of PWM input brightness control (BRC) is the positive duty cycle of the input signal. In case of FADER register brightness is MASTER FADER[7:0]/255.

| MFE | PWM | Brightness Control    |

|-----|-----|-----------------------|

| 0   | 0   | No brightness control |

| 0   | 1   | PWM input             |

| 1   | 0   | FADER register        |

| 1   | 1   | PWM input             |

The maximum currents of the drivers are set in the current setting registers. Brightness control keeps the ratio of the driver currents constant and adjusts the output currents based on the highest current setting. Driver currents can be adjusted between 100 mA to the maximum current set in the registers (see figures PWM Output Current Control and Master Fader Register Current Control in Typical Performance Characteristics).

I<sub>SET1</sub> =highest current setting

I<sub>SET2</sub> =current setting 2

**I**<sub>SET3</sub> =current setting 3

R1 =  $(I_{SET2}/I_{SET1})$ , ratio of current 2 and the highest current

**R2** = $(I_{SET3}/I_{SET1})$ , ratio of current 3 and the highest current

BRC =brightness control

$I1 = I_{SFT1} \times BRC$

$12 = 11 \times R1$

13 = 11x R2

### **PWM TIMING**

Figure 18 shows example of PWM brightness control. PWM input can be change at any given time but control takes effect when next enable is pulled high. To ensure that control takes effect for the next color time from PWM change to next enable needs to be greater than timeout time (300 µs typical).

At the beginning of the example frame PWM input is changed from 100% to 80% while green driver is enabled. Brightness level is not changed in the middle of the green frame but at the beginning of the next color which in this example is blue. During next green PWM is set back to 100%. This is done at least 300  $\mu$ s before next enable is pulled high and control takes effect then. During next green PWM is changed to 0%. Time from PWM change to next enable (blue) is less than 300  $\mu$ s and control don't take effect when blue starts but one color later, what in this example is red.

Figure 18. PWM Timing

## **FAULT DETECTION**

LM3549 can detect several different fault conditions. These are LED open, LED short, thermal shutdown (TSD), under voltage lockout (UVLO) and buck-boost converter over current protection (OCP). If any of the fault conditions occur corresponding fault bit is set in the fault register. If fault mask bit is not set also Fault output is pulled low. Reading Fault register resets its value to zero and sets Fault output to high impedance state.

## **LED OPEN FAULT**

Open fault is generated when at the end of color VOUT is at maximum and no current is flowing through driver (VDx = 0V). Also OCP fault needs to be low. Open fault can be generated by broken LED or a soldering defect.

Figure 19. LED Open Fault

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

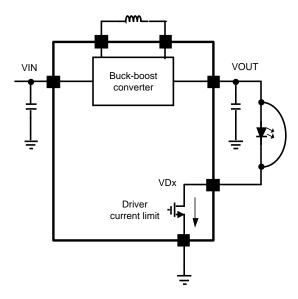

#### **LED SHORT FAULT**

Short fault is detected when VOUT < 1.0V at the end of a color. Short fault is generated when VOUT is shorted to driver by soldering defect or faulty LED. Driver current limit limits the maximum current. Depending on output current and positive limit settings, LED short can also generate OCP fault to fault register.

Figure 20. LED Short Fault

### **TSD FAULT**

Thermal shutdown (TSD) fault is generated if junction temperature rises above TSD level. TSD engages at  $T_J$ = 150°C (typ) and disengages at  $T_J$  = 140°C (typ). TSD sets device to standby mode. Occasionally a false TSD fault is generated to Fault register when device goes from shutdown mode to standby mode. It is good practice to reset the fault register by reading it every time after device is set from shutdown mode to standby mode.

### **UVLO FAULT**

Under voltage lock out (UVLO) fault is generated if VIN drops below UVLO level (~2.5V). UVLO sets device to standby mode. When VIN rises back above the 2.5V device exits UVLO. If control register values were changed from EEPROM defaults they need to be rewritten to registers because UVLO condition can generate EEPROM read sequence.

### **OVER CURRENT PROTECTION FAULT**

Over current protection (OCP) fault is generated when positive current limit is active at the end of a color. It is important to notice that OCP fault is not always set when positive current limit is activated. Positive current limit can activate during normal operation when buck-boost is adjusting the output voltage to a higher level. OCP can be caused by short from VOUT to GND, short from driver to GND or if too low positive current limit value is set for desired output current.

## I<sup>2</sup>C Compatible Interface

#### I<sup>2</sup>C ADDRESS

LM3549 I<sup>2</sup>C address is 36 hex (7 bits).

## **PC SIGNALS**

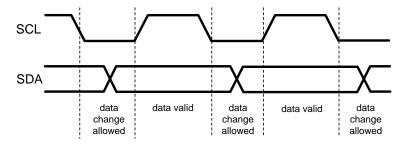

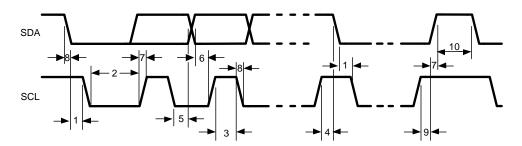

The SCL pin is used for the  $I^2C$  clock and the SDA pin is used for bidirectional data transfer. Both these signals need a pull-up resistor according to  $I^2C$  specification. The values of the pull-up resistors are determined by the capacitance of the bus (typ. ~1.8k). Signal timing specifications are shown in Table 1.

Copyright © 2010–2013, Texas Instruments Incorporated

Submit Documentation Feedback

#### **PC VALIDITY**

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

Figure 21. I<sup>2</sup>C Signals: Data Validity

### **PC START AND STOP CONDITIONS**

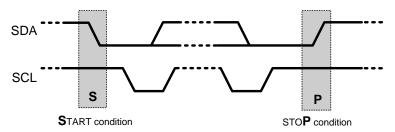

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I2C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 22. Start and Stop Conditions

#### TRANSFERRING DATA

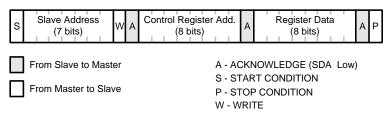

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the ninth clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

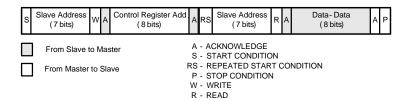

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3549 address is 36 hex. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Figure 23. I<sup>2</sup>C Write Cycle

Submit Documentation Feedback

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in Figure 24

Figure 24. I<sup>2</sup>C Read Cycle

Figure 25. I<sup>2</sup>C Timing Diagram

Table 1. I<sup>2</sup>C Timing Parameters

| Cumbal | Parameter                                          | Limit      | Unito |       |

|--------|----------------------------------------------------|------------|-------|-------|

| Symbol | Parameter                                          | Min        | Max   | Units |

| 1      | Hold Time (repeated) START Condition               | 0.6        |       | μs    |

| 2      | Clock Low Time                                     | 1.3        |       | μs    |

| 3      | Clock High Time                                    | 600        |       | ns    |

| 4      | Setup Time for a Repeated START Condition          | 600        |       | ns    |

| 5      | Data Hold                                          | 300        | 900   | ns    |

| 5      | Data Hold Time (input direction)                   | 0          | 900   | ns    |

| 6      | Data Setup Time                                    | 100        |       | ns    |

| 7      | Rise Time of SDA and SCL                           | 20 + 0.1Cb | 300   | ns    |

| 8      | Fall Time of SDA and SCL                           | 15 + 0.1Cb | 300   | ns    |

| 9      | Set-up Time for STOP condition                     | 600        |       | ns    |

| 10     | Bus Free Time between a STOP and a START Condition | 1.3        |       | μs    |

| Cb     | Capacitive Load for Each Bus Line                  | 10         | 200   | pF    |

## **Register Map**

| ADDR | NAME     | D7 | D6              | D5 | D4  | D3 | D2      | D1     | D0       | DEFAULT | NOTE   |

|------|----------|----|-----------------|----|-----|----|---------|--------|----------|---------|--------|

| 00H  | BANK_SEL |    |                 |    |     |    | *       | Bank_s | sel[1:0] | 00H     | EEPROM |

| 01H  | IR0_LSB  |    | Red 0 [7:0]     |    |     |    |         |        | 81H      | EEPROM  |        |

| 02H  | IR0_MSB  |    | N/A Red 0 [9:8] |    |     |    |         |        | 01H      | EEPROM  |        |

| 03H  | IG0_LSB  |    | Green 0 [7:0]   |    |     |    |         | 81H    | EEPROM   |         |        |

| 04H  | IG0_MSB  |    | N/A             |    |     |    |         | Green  | 0 [9:8]  | 01H     | EEPROM |

| 05H  | IB0_LSB  |    | Blue 0 [7:0]    |    |     |    |         |        | 81H      | EEPROM  |        |

| 06H  | IB0_MSB  |    | N/A Blue 0 [9   |    |     |    | 0 [9:8] | 01H    | EEPROM   |         |        |

| 07H  | IR1_LSB  |    | Red 1 [7:0]     |    |     |    |         | E7H    | EEPROM   |         |        |

| 08H  | IR1_MSB  |    |                 | ١  | N/A |    |         | Red 1  | [9:8]    | 00H     | EEPROM |

| ADDR | NAME              | D7          | D6                  | D5      | D4                     | D3         | D2      | D1      | D0       | DEFAULT | NOTE      |

|------|-------------------|-------------|---------------------|---------|------------------------|------------|---------|---------|----------|---------|-----------|

| 09H  | IG1_LSB           |             | Green 1 [7:0]       |         |                        |            |         |         |          |         | EEPROM    |

| 0AH  | IG1_MSB           |             |                     | 1       | N/A                    |            |         | Green   | 1 [9:8]  | 00H     | EEPROM    |

| 0BH  | IB1_LSB           |             |                     |         | Blu                    | e 1 [7:0]  |         |         |          | E7H     | EEPROM    |

| 0CH  | IB1_MSB           |             |                     | 1       | N/A                    |            |         | Blue '  | 1 [9:8]  | 00H     | EEPROM    |

| 0DH  | IR2_LSB           |             |                     |         | Red                    | d 2 [7:0]  |         |         |          | 4DH     | EEPROM    |

| 0EH  | IR2_MSB           |             |                     | 1       | N/A                    |            |         | Red 2   | 2 [9:8]  | 00H     | EEPROM    |

| 0FH  | IG2_LSB           |             |                     |         | Gree                   | en 2 [7:0] |         |         |          | 4DH     | EEPROM    |

| 10H  | IG2_MSB           |             |                     | 1       | N/A                    |            |         | Green   | 2 [9:8]  | 00H     | EEPROM    |

| 11H  | IB2_LSB           |             |                     |         | Blu                    | e 2 [7:0]  |         |         |          | 4DH     | EEPROM    |

| 12H  | IB2_MSB           |             |                     | 1       | N/A                    |            |         | Blue 2  | 2 [9:8]  | 00H     | EEPROM    |

| 13H  | FADER             |             |                     |         | MASTER                 | FADER [7   | :0]     |         |          | FFH     | EEPROM    |

| 14H  | CTRL              | N           | /A                  |         | OFT<br>RT[1:0]         | TIME O     | UT[1:0] | MFE     | PWM      | 00H     | EEPROM    |

| 15H  | ILIMIT            | N           | /A                  | POS_L   | MIT[1:0]               | N/         | Ά       | NEG_LI  | MIT[1:0] | 11H     | EEPROM    |

| 16H  | F_MASK            |             | N/A                 |         | SHORT                  | OPEN       | UVLO    | TSD     | OCP      | 00H     | EEPROM    |

| 17H  | FAULT             | N/A         | SHOF                | RT[1:0] | RT[1:0] OPEN[1:0] UVLO |            |         | TSD     | OCP      | 00H     | Read Only |

| 19H  | USR1              |             | User Register1[7:0] |         |                        |            |         |         |          | 00H     | EEPROM    |

| 1AH  | USR2              |             | User Register2[7:0] |         |                        |            |         |         |          | 00H     | EEPROM    |

| 40H  | EEPROM<br>CONTROL | EE<br>ready |                     |         |                        |            | EE init | EE prog | EE read  | 00H     | R/W       |

## I<sup>2</sup>C Register Details

## 00h BANK\_SEL[1:0]

Bank selection register. Selects one of the three current setting banks.

| I | ВІТ | BANK SELECTION |

|---|-----|----------------|

| 0 | 0   | Bank 0         |

| 0 | 1   | Bank 1         |

| 1 | 0   | Bank 2         |

| 1 | 1   | Bank 2         |

## 01h IR0\_LSB and 02h IR0\_MSB

Red LED current setting for Bank 0. IR0\_LSB holds the eight least significant bits and IR0\_MSB the two most significant bits.

## 03h IG0\_LSB and 04h IG0\_MSB

Green LED current setting for Bank 0. IG0\_LSB holds the eight least significant bits and IG0\_MSB the two most significant bits.

## 05h IB0\_LSB and 06h IB0\_MSB

Blue LED current setting for Bank 0. IB0\_LSB holds the eight least significant bits and IB0\_MSB the two most significant bits.

### 07h IR1\_LSB and 08h IR1\_MSB

Red LED current setting for Bank 1. IR1\_LSB holds the eight least significant bits and IR1\_MSB the two most significant bits.

### 09h IG1 LSB and 0Ah IG1 MSB

Green LED current setting for Bank 1. IG1\_LSB holds the eight least significant bits and IG1\_MSB the two most significant bits.

### 0Bh IB1 LSB and 0Ch IB1 MSB

Blue LED current setting for Bank 1. IB1\_LSB holds the eight least significant bits and IB1\_MSB the two most significant bits.

### 0Dh IR2 LSB and 0Eh IR2 MSB

Red LED current setting for Bank 2. IR2\_LSB holds the eight least significant bits and IR2\_MSB the two most significant bits.

### 0Fh IG2\_LSB and 10h IG2\_MSB

Green LED current setting for Bank 2. IG2\_LSB holds the eight least significant bits and IG2\_MSB the two most significant bits.

### 11h IB2\_LSB and 12h IB2\_MSB

Blue LED current setting for Bank 2. IB2\_LSB holds the eight least significant bits and IB2\_MSB the two most significant bits.

#### 13h FADER

Master fader control register. Can be used to control the total brightness of the LEDs if MFE is enabled.

#### 14h CTRL

Control register. Controls many of the LM3549 features.

## BIT[1:0] PWM and MFE

Control register bits [1:0] can be used to enable master control or PWM brightness control.

| MFE | PWM | BRIGHTNESS CONTROL    |  |  |  |  |  |  |  |

|-----|-----|-----------------------|--|--|--|--|--|--|--|

| 0   | 0   | No brightness control |  |  |  |  |  |  |  |

| 0   | 1   | input                 |  |  |  |  |  |  |  |

| 1   | 0   | Master input          |  |  |  |  |  |  |  |

| 1   | 1   | PWM input             |  |  |  |  |  |  |  |

## **BIT[3:2] TIME OUT[1:0]**

Selects how long device stays in active mode after all x\_EN controls have been set low

| В | IT | TIME OUT |

|---|----|----------|

| 0 | 0  | 125 ms   |

| 0 | 1  | 250 ms   |

| 1 | 0  | 500 ms   |

| 1 | 1  | 1s       |

### BIT[5:4] SOFT START[1:0]

Enables soft start feature and selects soft start time.

| В | IT | SOFT START TIME |

|---|----|-----------------|

| 0 | 0  | disabled        |

| 0 | 1  | 0.5s            |

| 1 | 0  | 1s              |

| 1 | 1  | 2s              |

#### 15h ILIMIT

ILIMIT register sets the buck-boost converters current limit values.

## BIT[1:0] NEG\_LIMIT[1:0]

Selects buck-boost converters negative current limit.

| E | BIT | NEGATIVE CURRENT LIMIT |

|---|-----|------------------------|

| 0 | 0   | 550 mA                 |

| 0 | 1   | 1100 mA                |

| 1 | 0   | 1650 mA                |

| 1 | 1   | 2200 mA                |

## BIT[5:4] POS\_LIMIT[1:0]

Selects buck-boost converters positive current limit.

| В | IT | POSITIVE CURRENT LIMIT |

|---|----|------------------------|

| 0 | 0  | 500 mA                 |

| 0 | 1  | 1000 mA                |

| 1 | 0  | 1500 mA                |

| 1 | 1  | 2000 mA                |

## 16h F\_MASK

Fault output mask register. Can be used to disable fault output from desired faults.

### 17h FAULT

Fault register. If fault occurs corresponding fault bits are set in fault register. Reading Fault register resets it. Read only register.

## BIT[0] OCP

Over current protection. Buck-boost converters current limit has been reached.

### BIT[1] TSD

Thermal shutdown fault. Junction temperature has risen abowe TSD level.

### BIT[2] UVLO

Under voltage lock-out. Input voltage has fallen below UVLO threshold level.

## BIT[4:3] OPEN[1:0]

LED open fault.

| E | BIT | FAULT      |

|---|-----|------------|

| 0 | 0   | No fault   |

| 0 | 1   | Red open   |

| 1 | 0   | Green open |

| 1 | 1   | Blue open  |

Copyright © 2010–2013, Texas Instruments Incorporated Product Folder Links: *LM3549*

## BIT[6:5] SHORT[1:0]

LED short fault.

| В | IT | FAULT       |

|---|----|-------------|

| 0 | 0  | No fault    |

| 0 | 1  | Red short   |

| 1 | 0  | Green short |

| 1 | 1  | Blue short  |

## 19h and 1AH USR1 and USR2

User registers 1 and 2. Can be used to store any user data. No affect on the device.

## **40h EEPROM CONTROL**

EEPROM Control register. This register is used to program EEPROM. EEPROM programming is described in the EEPROM Programming chapter.

**Table 2. Recommended External Components**

| Symbol | Symbol Explanation | Value            | Туре | Example               |

|--------|--------------------|------------------|------|-----------------------|

| CIN    | Input Capacitor    | 10 μF,6.3V/10V   | X7R  |                       |

| COUT   | Output Capacitor   | 4.7 μF, 6.3V/10V | X7R  |                       |

| L1     | Switcher Inductor  | 2.2 µH, 1900 mA  |      | TDK VLF4014ST-2R2M1R9 |

## **REVISION HISTORY**

| Changes from Original (May 2013) to Revision A |                                                    | Pag | j€ |

|------------------------------------------------|----------------------------------------------------|-----|----|

| •                                              | Changed layout of National Data Sheet to TI format | 1   | ξ  |

20

## PACKAGE OPTION ADDENDUM

2-May-2013

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | •       | Pins | •    |                            | Lead/Ball Finish | •                  | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        |                  | (3)                |              | (4)               |         |

| LM3549SQ/NOPB    | ACTIVE | WQFN         | RTW     | 24   | 1000 | Green (RoHS & no Sb/Br)    | CU SN            | Level-1-260C-UNLIM |              | L3549SQ           | Samples |

| LM3549SQE/NOPB   | ACTIVE | WQFN         | RTW     | 24   | 250  | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |              | L3549SQ           | Samples |

| LM3549SQX/NOPB   | ACTIVE | WQFN         | RTW     | 24   | 4500 | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM |              | L3549SQ           | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): Tl's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, Tl Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 8-May-2013

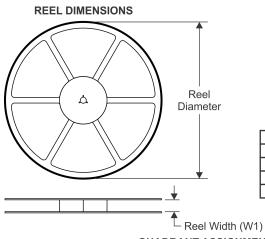

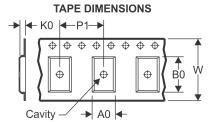

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

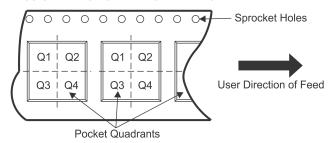

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device Device  | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3549SQ/NOPB  | WQFN            | RTW                | 24 | 1000 | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3549SQE/NOPB | WQFN            | RTW                | 24 | 250  | 178.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM3549SQX/NOPB | WQFN            | RTW                | 24 | 4500 | 330.0                    | 12.4                     | 4.3        | 4.3        | 1.3        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 8-May-2013

\*All dimensions are nominal

| 7 till difficienciale di c momina |              |                 |      |      |             |            |             |

|-----------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LM3549SQ/NOPB                     | WQFN         | RTW             | 24   | 1000 | 203.0       | 190.0      | 41.0        |

| LM3549SQE/NOPB                    | WQFN         | RTW             | 24   | 250  | 203.0       | 190.0      | 41.0        |

| LM3549SQX/NOPB                    | WQFN         | RTW             | 24   | 4500 | 367.0       | 367.0      | 35.0        |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>