SPNS085C - JULY 2003 - REVISED JANUARY 2006

- High-Performance Static CMOS Technology

- TMS470R1x 16/32-Bit RISC Core (ARM7TDMI™)

- 24-MHz System Clock (48-MHz Pipeline Mode)

- Independent 16/32-Bit Instruction Set

- Open Architecture With Third-Party Support

- Built-In Debug Module

- Utilizes Big-Endian Format

- Integrated Memory

- 256K-Byte Program ROM

- ROM Pipeline Wrapper (RPW)

- 10K-Byte Static RAM (SRAM) (VC3x8)

- 12K-Byte Static RAM (SRAM) (VC3x82)

- Operating Features

- Core Supply Voltage (V<sub>CC</sub>): 1.81 V 2.06 V

- Core Supply Voltage (V<sub>CC</sub>): 1.70 V 2.06 V

When Used from -40 to 85C

- I/O Supply Voltage (V<sub>CCIO</sub>): 3.0 V 3.6 V

- Low-Power Modes: STANDBY and HALT

- Industrial and Automotive Temperature Ranges

- 470+ System Module

- 32-Bit Address Space Decoding

- Bus Supervision for Memory and Peripherals

- Analog Watchdog (AWD) Timer

- Real-Time Interrupt (RTI)

- System Integrity and Failure Detection

- Zero-Pin Phase-Locked Loop (ZPLL)-Based Clock Module With Prescaler

- Multiply-by-4 or -8 Internal ZPLL Option

- ZPLL Bypass Mode

- Six Communication Interfaces:

- Two Serial Peripheral Interfaces (SPIs)

- 255 Programmable Baud Rates

- Two Serial Communications Interfaces (SCIs)

- 2<sup>24</sup> Selectable Baud Rates

- Asynchronous/Isosynchronous Modes

- Standard CAN Controller (SCC)

- 16-Mailbox Capacity

- Fully Compliant With CAN Protocol, Version 2.0B

- Class II Serial Interface (C2SIb)

- Two Selectable Data Rates

- Normal Mode 10.4 Kbps and 4X Mode 41.6 Kbps

- High-End Timer (HET)

- 27 Programmable I/O Channels (VC338x):

- 23 High-Resolution Pins

- 4 Standard-Resolution Pins

- 16 Programmable I/O Channels (VC348x):

- 14 High-Resolution Pins

- 2 Standard-Resolution Pins

- High-Resolution Share Feature (XOR)

- High-End Timer RAM

- 64-Instruction Capacity

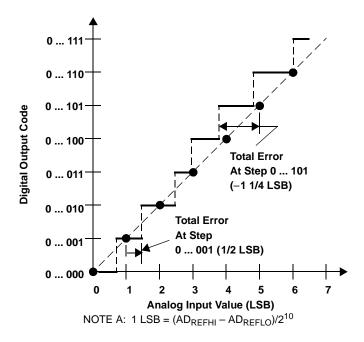

- 10-Bit Multi-Buffered ADC (MibADC)

12-Channel (VC338x)

- 16-Channel (VC348x)

- 64-Word FIFO Buffer

- Single- or Continuous-Conversion Modes

- 1.55  $\mu$ s Minimum Sample and Conversion Time

- Calibration Mode and Self-Test Features

- Eight External Interrupts

- Flexible Interrupt Handling

- 5 Dedicated General-Purpose I/O (GIO) Pins,

1 Input-Only GIO Pin, and 48 Additional Peripheral I/Os (VC338x)

- 11 Dedicated GIO Pins,1 Input-Only GIO Pin, and 38 Additional Peripheral I/Os (VC348x)

- External Clock Prescale (ECP) Module

- Programmable Low-Frequency External Clock (CLK)

- Compatible ROM Device

- On-Chip Scan-Base Emulation Logic,

IEEE Standard 1149.1<sup>†</sup> (JTAG) Test-Access Port

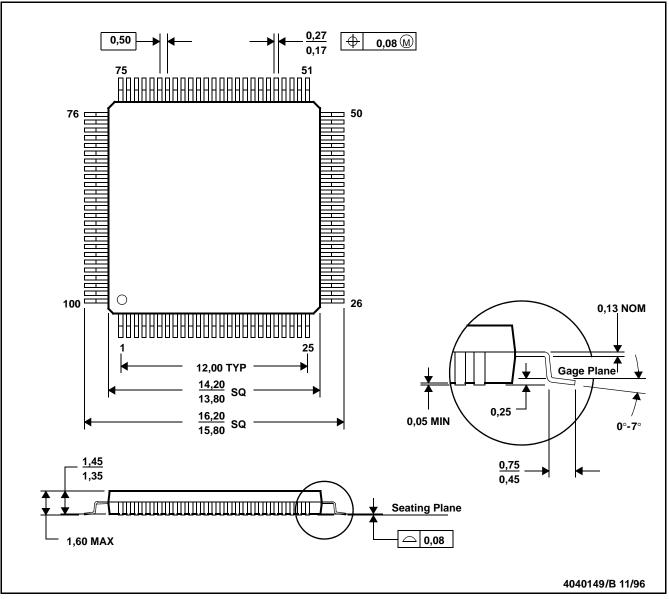

- 100-Pin Plastic Low-Profile Quad Flatpack (PZ Suffix)

- Development System Support Tools Available

- Code Composer Studio<sup>™</sup> Integrated Development Environment (IDE)

- HET Assembler and Simulator

- Real-Time In-Circuit Emulation

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Code Composer Studio is a trademark of Texas Instruments.

ARM7TDMI is a trademark of Advanced RISC Machines Limited (ARM).

All trademarks are property of their respective owners.

† The test-access port is compatible with the IEEE Standard 1149.1-1990, IEEE Standard Test-Access Port and Boundary Scan Architecture specification. Boundary scan is not supported on this device.

SPNS085C - JULY 2003 - REVISED JANUARY 2006

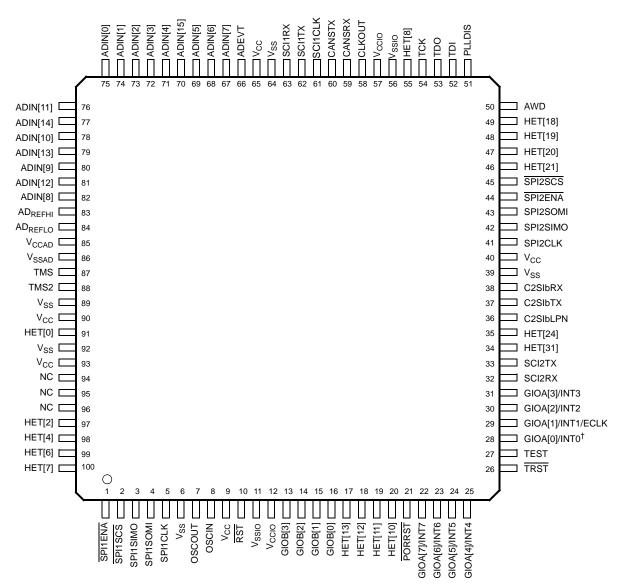

#### TMS470R1VC338x 100-PIN PZ PACKAGE (TOP VIEW) □SCI1CLK CANSTX CANSRX □CLKOUT □SCI1RX ☐ADIN[4] □ADIN[5] □SCI1TX ☐ ADIN[6] ☐ HET[9] ssio/ ☐ HET[8 □ TDO <u></u> AWD ADIN[11] □ 50 ADIN[10] 77 49 ☐ HET[18] ADIN[9] □ 78 ☐ HET[19] ADIN[8] 79 $AD_{REFHI}$ 80 ☐ HET[21] $\mathsf{AD}_\mathsf{REFLO}$ 81 ☐ HET[22] V<sub>CCAD</sub> 82 ☐ SPI2SOMI V<sub>SSAD</sub> [ 83 ☐ SPI2SIMO TMS [ 84 TMS2 ☐ SPI2CLK V<sub>SS</sub> [ 86 □ V<sub>CC</sub> V<sub>CC</sub> □ 87 HET[0] □ ☐ C2SIbRX HET[1] □ ☐ C2SIbTX ☐ C2SIbLPN V<sub>SS</sub> 90 V<sub>CC</sub> □ ☐ HET[24] 91 NC 🗆 ☐ HET[31] NC 🗆 93 ☐ HET[30] 33 NC $\square$ ☐ HET[29] 94 HET[2] ☐ SCI2TX HET[3] ☐ SCI2RX 96 HET[4] ☐ GIOA[1]/INT[1]/ECLK 97 HET[5] □ ☐ GIOA[0]/INT0<sup>†</sup> 98 99 ☐ TEST HET[7] 100 26 TRST 12 13 14 15 16 17 18 19 20 21 22 23 24 25 HET[15] HET[11] HET[10] **SPI1CLK** HET[16] HET[14] HET[13] HET[12] OSCOUT Vssio Vccio HET[17] GIOA[7]/INT7 GIOA[6]/INT6 GIOA[5]/INT5 SP11SOMI GIOA[4]/INT4

†GIOA[0]/INT0 (pin 28) is an input-only GIO pin.

#### TMS470R1VC348x 100-PIN PZ PACKAGE (TOP VIEW)

†GIOA[0]/INT0 (pin 28) is an input-only GIO pin.

SPNS085C - JULY 2003 - REVISED JANUARY 2006

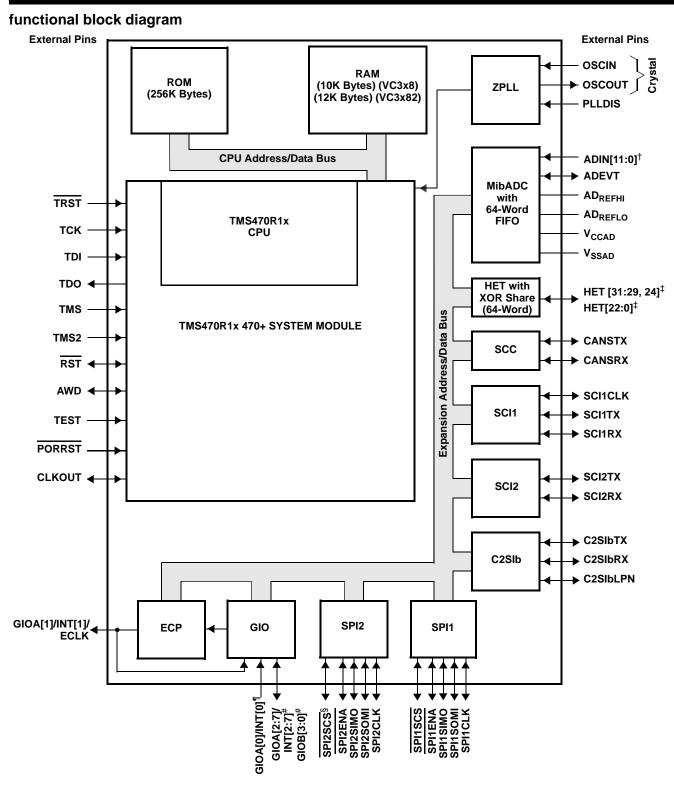

### description

The TMS470R1VC338, TMS470R1VC348, TMS470R1VC3382, and TMS470R1VC3482<sup>†</sup> devices are members of the Texas Instruments TMS470R1x family of general-purpose16/32-bit reduced instruction set computer (RISC) microcontrollers. The VC3x8x microcontroller offers high performance utilizing the high-speed ARM7TDMI 16/32-bit RISC central processing unit (CPU), resulting in a high instruction throughput while maintaining greater code efficiency. The ARM7TDMI 16/32-bit RISC CPU views memory as a linear collection of bytes numbered upwards from zero. The TMS470R1VC3x8x utilizes the big-endian format where the most significant byte of a word is stored at the lowest numbered byte and the least significant byte at the highest numbered byte.

High-end embedded control applications demand more performance from their controllers while maintaining low costs. The VC3x8x RISC core architecture offers solutions to these performance and cost demands while maintaining low power consumption.

The VC338/VC348/VC3382/VC3482 device contains the following:

- ARM7TDMI 16/32-Bit RISC CPU

- TMS470R1x system module (SYS) with 470+ enhancements

- 256K-byte ROM

- 10K-byte SRAM (VC3x8)

- 12K-byte SRAM (VC3x82)

- Zero-pin phase-locked loop (ZPLL) clock module

- Analog watchdog (AWD) timer

- Real-time interrupt (RTI) module

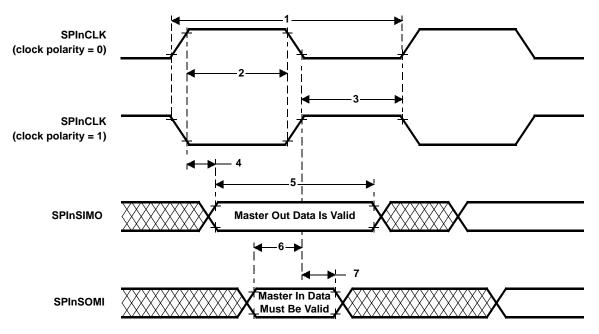

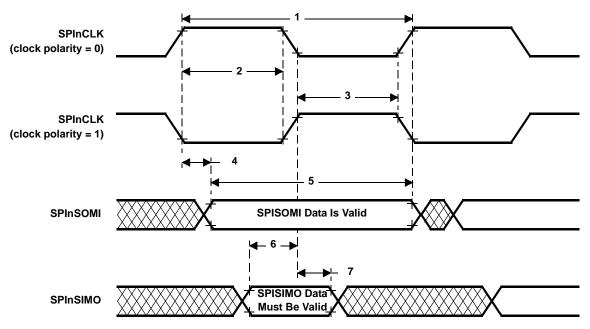

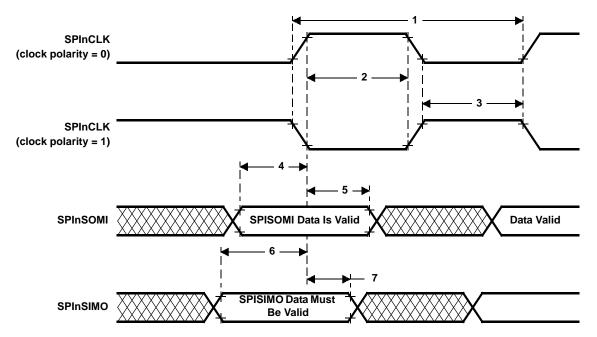

- Two serial peripheral interface (SPI) modules

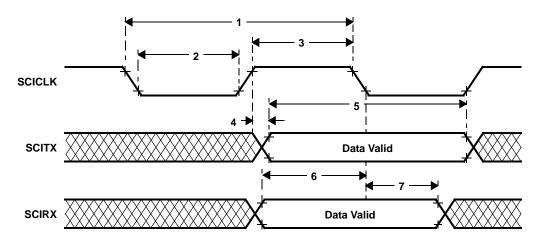

- Two serial communications interface (SCI) modules

- Standard CAN controller (SCC)

- Class II serial interface (C2SIb)

- 10-bit multi-buffered analog-to-digital converter (MibADC), 12-input channels (VC338x), 16-input channels (VC348x)

- High-end timer (HET) controlling 27 I/Os (VC338x), controlling 16 I/Os (VC348x)

- External Clock Prescale (ECP)

- Up to 53 I/O pins and 1 input-only pin (VC338x), up to 49 I/O pins and 1 input-only pin (VC348x)

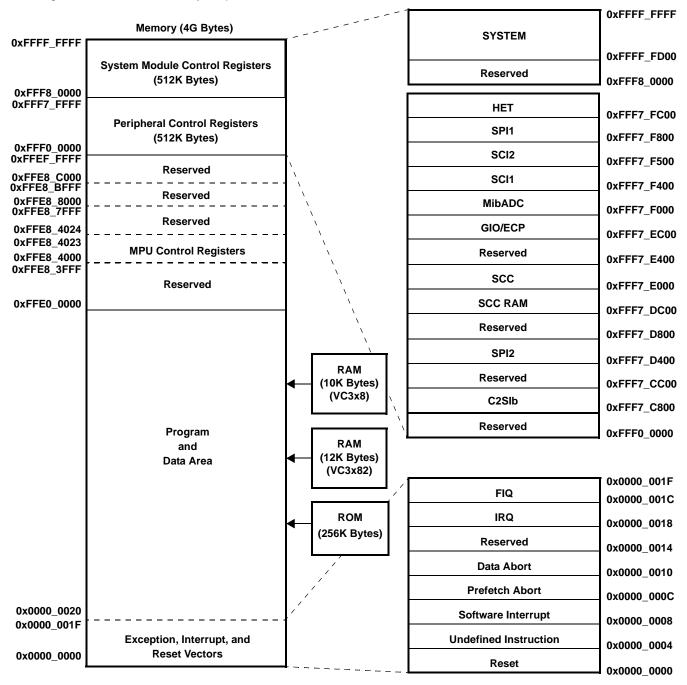

The functions performed by the 470+ system module (SYS) include: address decoding; memory protection; memory and peripherals bus supervision; reset and abort exception management; prioritization for all internal interrupt sources; device clock control; and parallel signature analysis (PSA). This data sheet includes device-specific information such as memory and peripheral select assignment, interrupt priority, and a device memory map. For a more detailed functional description of the SYS module, see the *TMS470R1x System Module Reference Guide* (literature number SPNU189).

The VC3x8x memory includes general-purpose SRAM supporting single-cycle read/write accesses in byte, half-word, and word modes.

The ROM memory on this device is programmable read-only memory that is masked at the time of device fabrication. The ROM operates with a system clock frequency of up to 24 MHz. In pipeline mode, the ROM operates with a system clock frequency of up to 48MHz. For more detailed information on the ROM Pipeline Wrapper, see the *TMS470R1x ROM Pipeline Wrapper (RPW) Reference Guide* (literature number SPNU009).

<sup>†</sup> Throughout the remainder of this document, the TMS470R1VC338, TMSVC348, TMS470R1VC3382 and TMS470R1VC3482 device names, where generic, shall be referred to as TMS470R1VC3x8x or VC3x8x; where applicable to only the 10K SRAM devices, VC3x8; where applicable to only the 12K SRAM devices, VC3x82; where applicable to only VC338 and VC3382 as VC338x; where applicable to only VC348 and VC3482 as VC348x; and, where unique, shall be referred to as either their full device name or VC338 or VC348 or VC3382 or VC3482.

SPNS085C - JULY 2003 - REVISED JANUARY 2006

### description (continued)

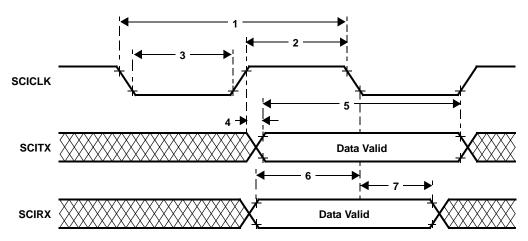

The VC3x8x device has six communication interfaces: two SPIs, two SCIs, an SCC, and a C2SIb. The SPI provides a convenient method of serial interaction for high-speed communications between similar shift-register type devices. The SCI is a full-duplex, serial I/O interface intended for asynchronous communication between the CPU and other peripherals using the standard Non-Return-to-Zero (NRZ) format. The SCC uses a serial, multimaster communication protocol that efficiently supports distributed real-time control with robust communication rates of up to 1 megabit per second (Mbps). The SCC is ideal for applications operating in noisy and harsh environments (e.g., automotive and industrial fields) that require reliable serial communication or multiplexed wiring. The C2SIb allows the VC3x8x to transmit and receive messages on a class II network following an SAE J1850<sup>†</sup> standard. For more detailed functional information on the SPI, SCI, and SCC peripherals, see the specific reference guides (literature numbers SPNU195, SPNU196, and SPNU197, respectively). For more detailed functional information on the C2SIb peripheral, see the TMS470R1x Class II Serial Interface B (C2SIb) Reference Guide (literature number SPNU214).

The HET is an advanced intelligent timer that provides sophisticated timing functions for real-time applications. The timer is software-controlled, using a reduced instruction set, with a specialized timer micromachine and an attached I/O port. The HET can be used for compare, capture, or general-purpose I/O. It is especially well suited for applications requiring multiple sensor information and drive actuators with complex and accurate time pulses. For more detailed functional information on the HET, see the *TMS470R1x High-End Timer (HET) Reference Guide* (literature number SPNU199). The VC3x8x HET peripheral contains the XOR-share feature. This feature allows two adjacent HET high-resolution channels to be XORed together, making it possible to output smaller pulses than a standard HET. For more detailed information on the HET XOR-share feature, see the *TMS470R1x High-End Timer (HET) Reference Guide* (literature number SPNU199).

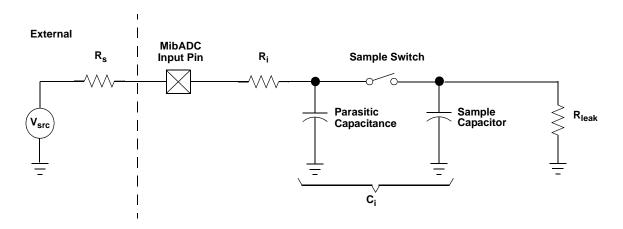

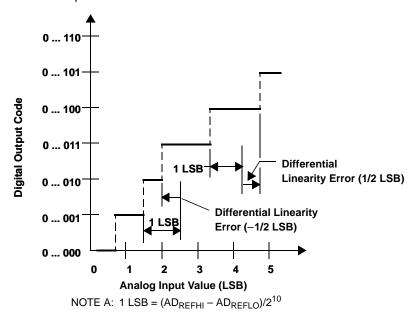

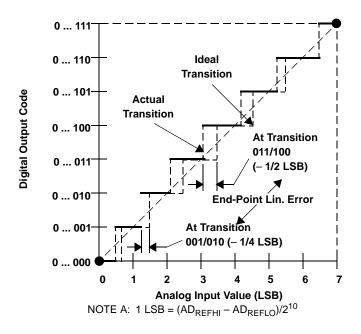

The VC3x8x device has a 10-bit-resolution sample-and-hold MibADC. The MibADC channels can be converted individually or can be grouped by software for sequential conversion sequences. There are three separate groupings, two of which are triggerable by an external event. Each sequence can be converted once when triggered or configured for continuous conversion mode. For more detailed functional information on the MibADC, see the *TMS470R1x Multi-Buffered Analog-to-Digital Converter (MibADC) Reference Guide* (literature number SPNU206).

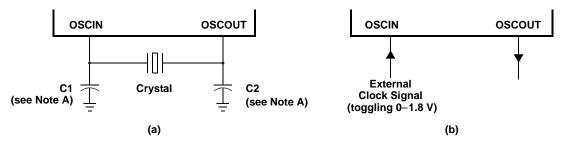

The zero-pin phase-locked loop (ZPLL) clock module contains a phase-locked loop, a clock-monitor circuit, a clock-enable circuit, and a prescaler (with prescale values of 1–8). The function of the ZPLL is to multiply the external frequency reference to a higher frequency for internal use. The ZPLL provides ACLK<sup>‡</sup> to the system (SYS) module. The SYS module subsequently provides system clock (SYSCLK), real-time interrupt clock (RTICLK), CPU clock (MCLK), and peripheral interface clock (ICLK) to all other VC3x8x device modules. For more detailed functional information on the ZPLL, see the *TMS470R1x Zero-Pin Phase Locked Loop (ZPLL) Clock Module Reference Guide* (literature number SPNU212).

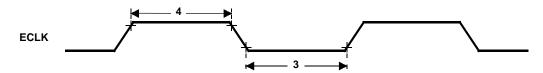

The VC3x8x device also has an external clock prescaler (ECP) module that when enabled, outputs a continuous external clock (ECLK) on a specified GIO pin. The ECLK frequency is a user-programmable ratio of the peripheral interface clock (ICLK) frequency. For more detailed functional information on the ECP, see the TMS470R1x External Clock Prescaler (ECP) Reference Guide (literature number SPNU202).

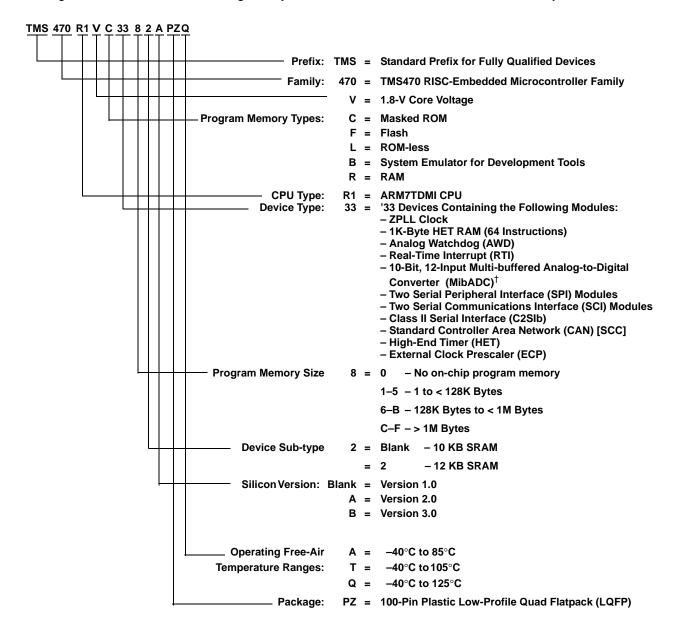

#### device characteristics

The TMS470R1VC3x8x device is a derivative of the F05 system emulation device SE470R1VB8AD. Table 1 identifies all the characteristics of the TMS470R1VC3x8x device except the SYSTEM and CPU, which are generic. The COMMENTS column aids the user in software-programming and references device-specific information.

<sup>‡</sup> ACLK should not be confused with the MibADC internal clock, ADCLK. ACLK is the continuous system clock from an external resonator/crystal reference.

<sup>†</sup> SAE Standard J1850 Class B Data Communication Network Interface

SPNS085C - JULY 2003 - REVISED JANUARY 2006

### device characteristics (continued)

**Table 1. Device Characteristics**

| CHARACTERIS-<br>TICS           | DEVICE DESCRIPTION<br>TMS470R1VC338/<br>VC3382               | DEVICE DESCRIPTION<br>TMS470R1VC348/<br>VC3482  | COMMENTS FOR VC3X8X                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                                              | MEMORY                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| For the number of mer          | mory selects on this device, s                               | see the Memory Selection As                     | ssignment table (Table 2).                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                | 256K-Byte ROM                                                | 256K-Byte ROM                                   | ROM is pipeline-capable                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INTERNAL<br>MEMORY             | 10K-Byte SRAM (VC338)<br>12K-Byte SRAM (VC3382)              | 10K-Byte SRAM (VC348)<br>12K-Byte SRAM (VC3482) | The VC3x8 RAM is implemented in one 10K array selected by two memory-select signals. The VC3x82 RAM is implemented in one 12K array selected by two memory-select signals. (See the Memory Selection Assignment table, Table 2).                                                                                                                                                                                                                    |

|                                |                                                              | PERIPHERALS                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                | interrupt priority configuration, see the Peripherals and Sy |                                                 | table (Table 4). And for the 1K peripheral address ranges and es table (Table 3).                                                                                                                                                                                                                                                                                                                                                                   |

| CLOCK                          | ZPLL                                                         | ZPLL                                            | Zero-pin PLL has no external loop filter pins.                                                                                                                                                                                                                                                                                                                                                                                                      |

| GENERAL-<br>PURPOSE<br>I/Os    | 5 I/O<br>1 Input only                                        | 11 I/O<br>1 Input only                          | Port A has six (6) external pins (VC338/VC3382 – GIOA[2]/INT2 and GIOA[3]/INT3 are not available.) Port A has eight (8) external pins and Port B has four (4) external pins (VC348)                                                                                                                                                                                                                                                                 |

| ECP                            | YES                                                          | YES                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C2Slb                          | 1                                                            | 1                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SCI                            | 1 (3-pin)<br>1 (2-pin)                                       | 1 (3-pin)<br>1 (2-pin)                          | SCI2 has no external clock pin, only transmit/receive pins (SCI2TX and SCI2RX)                                                                                                                                                                                                                                                                                                                                                                      |

| CAN<br>(HECC and/or SCC)       | 1 SCC                                                        | 1 SCC                                           | Standard CAN controller                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SPI<br>(5-pin, 4-pin or 3-pin) | 1 (5-pin)<br>1 (4-pin)                                       | 2 (5-pin)                                       | VC338/VC3382 SPI1 (5-pin), SPI2 (4-pin)<br>SPI2 has no chip select pin                                                                                                                                                                                                                                                                                                                                                                              |

|                                |                                                              |                                                 | The VC3x8x devices have both the logic and registers for a full 32-I/O HET implemented, even though not all 32 pins are available externally.                                                                                                                                                                                                                                                                                                       |

| HET with<br>XOR Share          | 27 I/O                                                       | 16 I/O                                          | The high-resolution (HR) SHARE feature allows even HR pins to share the next higher odd HR pin structures. This HR sharing is independent of whether or not the odd pin is available externally. If an odd pin is available externally and <i>shared</i> , then the odd pin can only be used as a general-purpose I/O. For more information on HR SHARE, see the <i>TMS470R1x High-End Timer (HET) Reference Guide</i> (literature number SPNU199). |

| HET RAM                        | 64-Instruction Capacity                                      | 64-Instruction Capacity                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MibADC                         | 10-bit, 12-channel<br>64-word FIFO                           | 10-bit, 16-channel<br>64-word FIFO              | 12-channel MibADC (VC338x), 16-channel MibADC (VC348x). Both the logic and registers for a full 16-channel MibADC are present. Capable of being "event triggered" from a user-selectable event source.                                                                                                                                                                                                                                              |

| CORE VOLTAGE                   | 1.81 - 2.06 V<br>1.70 - 2.06 V (-40 to 85C)                  | 1.81 - 2.06 V<br>1.70 - 2.06 V (-40 to 85C)     | The 1.70 - 2.06 V range applies when operating between -40 and 85C.                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O VOLTAGE                    | 3.0 - 3.6 V                                                  | 3.0 - 3.6 V                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PINS                           | 100                                                          | 100                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PACKAGE                        | PZ                                                           | PZ                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

<sup>†</sup> ADIN[11:0] for VC338x and ADIN[15:0] for VC348x.

<sup>#</sup>GIOA[2]/INT[2], GIOA[3]/INT[3], and GIOB[3:0] pins are not applicable to the VC338x device.

<sup>#</sup>HET[31:29, 24] and HET[22:0] for VC338x, HET[31, 24] and HET[21:18, 13:10, 8, 7, 6, 4, 2, 0] for VC348x.

<sup>§</sup> The SPI2 chip select pin (SPI2SCS) is only applicable to the VC348x device.

<sup>¶</sup> GIOA[0]/INT[0] is an input-only GIO pin.

SPNS085C - JULY 2003 - REVISED JANUARY 2006

#### **Terminal Functions**

| Т        | ERMINAL |        |                    | INTERNAL    |                                                                                                                                                                                                                             |  |  |

|----------|---------|--------|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | VC338X  | VC348X | TYPE <sup>†‡</sup> | PULLUP/     | DESCRIPTION                                                                                                                                                                                                                 |  |  |

|          |         |        |                    | PULLDOWN§   | TIMED (UET)                                                                                                                                                                                                                 |  |  |

| HET[0]   | 88      | 91     |                    | HIGH-END    | TIMER (HET)                                                                                                                                                                                                                 |  |  |

| HET[1]   | 89      |        |                    |             |                                                                                                                                                                                                                             |  |  |

| HET[2]   | 95      | 97     | -                  |             |                                                                                                                                                                                                                             |  |  |

| HET[3]   | 96      |        |                    |             |                                                                                                                                                                                                                             |  |  |

| HET[4]   | 97      | 98     |                    |             |                                                                                                                                                                                                                             |  |  |

| HET[5]   | 98      |        |                    |             | These devices have both the logic and registers for a full 32-I/O HET implemented, even though not all 32 pins are available externally                                                                                     |  |  |

| HET[6]   | 99      | 99     |                    |             | Implemented, even though not all 32 pins are available externally                                                                                                                                                           |  |  |

| HET[7]   | 100     | 100    |                    |             | Timer input capture or output compare. The HET[31:0] applicable pins                                                                                                                                                        |  |  |

| HET[8]   | 55      | 55     |                    |             | can be programmed as general-purpose input/output (GIO) pins.                                                                                                                                                               |  |  |

| HET[9]   | 56      | _      | 1                  |             | HET[22:0] are high-resolution pins and HET[31:29, 24] are standard-resolution pins for VC338x.                                                                                                                              |  |  |

| HET[10]  | 20      | 20     | 1                  |             | HET[21:18, 13:10, 8, 7, 6, 4, 2, 0] are high-resolution pins and HET[31,                                                                                                                                                    |  |  |

| HET[11]  | 19      | 19     | 1                  |             | 24] are standard-resolution pins for VC348x.                                                                                                                                                                                |  |  |

| HET[12]  | 18      | 18     | 1                  |             | The high-resolution (HR) SHARE feature allows even HR pins to share the next higher odd HR pin structures. This HR sharing is independent of whether or not the odd pin is available externally. If an odd pin is available |  |  |

| HET[13]  | 17      | 17     |                    | I/O IPD     |                                                                                                                                                                                                                             |  |  |

| HET[14]  | 16      | _      | 3.3-V I/O          |             |                                                                                                                                                                                                                             |  |  |

| HET[15]  | 15      | _      |                    |             | externally and shared, then the odd pin can only be used as a general-                                                                                                                                                      |  |  |

| HET[16]  | 14      | _      | 1                  |             | purpose I/O. For more information on HR SHARE, see the <i>TMS470R1x</i>                                                                                                                                                     |  |  |

| HET[17]  | 13      | _      |                    |             | High-End Timer (HET) Reference Guide (literature number SPNU199)                                                                                                                                                            |  |  |

| HET[18]  | 49      | 49     |                    |             | The HET[19] or HET[18] pins can also be used as a user-selectable event                                                                                                                                                     |  |  |

| HET[19]  | 48      | 48     |                    |             | source to "event trigger" the MibADC event group or group1 providing the                                                                                                                                                    |  |  |

| HET[20]  | 47      | 47     | 1                  |             | associated register source bits are properly configured and defined. For<br>the internal device connections, see the MibADC section of this data                                                                            |  |  |

| HET[21]  | 46      | 46     |                    |             | sheet. And for more detailed functional information on the MibADC, see                                                                                                                                                      |  |  |

| HET[22]  | 45      | -      | 1                  |             | the TMS470R1x Multi-Buffered Analog-to-Digital Converter (MibADC)                                                                                                                                                           |  |  |

| HET[24]  | 35      | 35     |                    |             | Reference Guide (literature number SPNU206).                                                                                                                                                                                |  |  |

| HET[28]  | _¶      | _¶     |                    |             |                                                                                                                                                                                                                             |  |  |

| HET[29]  | 32      | _      | 1                  |             |                                                                                                                                                                                                                             |  |  |

| HET[30]  | 33      | _      | 1                  |             |                                                                                                                                                                                                                             |  |  |

| HET[31]  | 34      | 34     | ]                  |             |                                                                                                                                                                                                                             |  |  |

|          |         |        | S                  | TANDARD CAN | CONTROLLER (SCC)                                                                                                                                                                                                            |  |  |

| CANSRX   | 60      | 59     | 3.3-V I/O          |             | SCC receive pin or GIO pin                                                                                                                                                                                                  |  |  |

| CANSTX   | 61      | 60     | 3.3-V I/O          | IPU         | SCC transmit pin or GIO pin                                                                                                                                                                                                 |  |  |

|          |         |        |                    |             | INTERFACE (C2SIb)                                                                                                                                                                                                           |  |  |

| C2SIbLPN | 36      | 36     | 3.3-V I/O          | IPD         | C2SIb module loopback enable pin or GIO pin                                                                                                                                                                                 |  |  |

| C2SlbRX  | 38      | 38     | 3.3-V I/O          |             | C2SIb module receive data input pin or GIO pin                                                                                                                                                                              |  |  |

| C2SIbTX  | 37      | 37     | 3.3-V I/O          | IPD         | C2SIb module transmit data output pin or GIO pin                                                                                                                                                                            |  |  |

<sup>†</sup> I = input, O = output, PWR = power, GND = ground, REF = reference voltage, NC = no connect

<sup>‡</sup> All I/O pins, except RST, are configured as inputs while PORRST is low and immediately after PORRST goes high.

<sup>§</sup> IPD = internal pulldown, IPU = internal pullup (all internal pullups and pulldowns are active on input pins, independent of the PORRST state.)

<sup>¶</sup> N/A on the VC348 device. For the VC338 device only, the HET[28] signal is only connected to the pad not to a package pin.

SPNS085C - JULY 2003 - REVISED JANUARY 2006

**Terminal Functions (Continued)**

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TE                  | RMINAL |         | 10.                | INTERNAL     |                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|---------|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Company   Company   Company   Company   Company   Company                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |        | V00 40V | TYPE <sup>†‡</sup> |              | DESCRIPTION                                                                                                                                                                                                          |

| GIOA[0]NINT10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NAME                | VC338X | VC348X  |                    | PULLDOWN§    |                                                                                                                                                                                                                      |

| General-purpose input/output pins, GIOA[0]/INT[0] is an input-only pin. GIOA[0]/INT |                     |        |         |                    | GENERAL-PU   | JRPOSE I/O (GIO)                                                                                                                                                                                                     |

| CILK   29   29   29   30   30   30   30   30   30   30   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | 28     | 28      | 3.3-V I            |              |                                                                                                                                                                                                                      |

| GIOA[3]/INT3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     | 29     | 29      |                    |              |                                                                                                                                                                                                                      |

| Signological   1971   25   25   25   25   25   25   25   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GIOA[2]/INT2        | -      | 30      | 1                  |              |                                                                                                                                                                                                                      |

| GIOA[g/INT4   25   25   25   25   25   25   25   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GIOA[3]/INT3        | _      | 31      | 0.0.1.10           | IPD          |                                                                                                                                                                                                                      |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GIOA[4]/INT4        | 25     | 25      | 3.3-1/0            |              | Tunction of the external clock prescale (ECF) module.                                                                                                                                                                |

| GIOA[7]/INT7   22   22   22   23   24   25   26   25   26   25   26   25   26   25   26   25   25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GIOA[5]/INT5        | 24     | 24      |                    |              | GIOA[2]/INT[2] and GIOA[3]/INT[3] pins are not applicable on the VC338x                                                                                                                                              |

| GIOB[0]   -   16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GIOA[6]/INT6        | 23     | 23      |                    |              | device.                                                                                                                                                                                                              |

| GIOB[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GIOA[7]/INT7        | 22     | 22      |                    |              |                                                                                                                                                                                                                      |

| Signature   Sign |                     | -      | 16      |                    |              |                                                                                                                                                                                                                      |

| GIOB[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GIOB[1]             |        | 15      | 3 3-1/ 1/0         | IDU          | General-nurnose input/outnut nins (\/C348v only)                                                                                                                                                                     |

| ADEVT   67   66   3.3-V   / O   IPD   IP | GIOB[2]             | _      | 14      | 3.3-V I/O          | יו ט         |                                                                                                                                                                                                                      |

| ADEVT   67   66   3.3-V   / O   IPD   MibADC event input. ADEVT can be programmed as a GIO pin.The ADEVT pin can also be used as a user-selectable event source to "even trigger" the MibADC event for pour providing the associated register source bits are properly configured and defined. For the internal device connections, see the MibADC section of this data sheet.    ADIN[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GIOB[3]             | -      |         |                    |              |                                                                                                                                                                                                                      |

| ADEVT   67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |        | MUL     | ΓI-BUFFEF          | RED ANALOG-T | O-DIGITAL CONVERTER (MibADC)                                                                                                                                                                                         |

| ADIN[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADEVT               | 67     | 66      | 3.3-V I/O          | IPD          | ADEVT pin can also be used as a user-selectable event source to "event trigger" the MibADC event group or group1 providing the associated register source bits are properly configured and defined. For the internal |

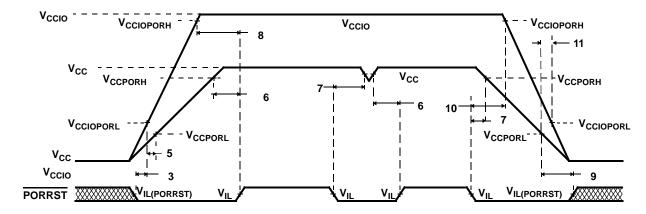

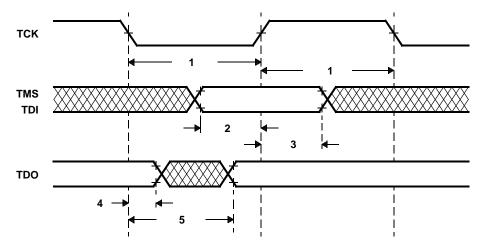

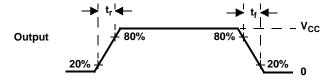

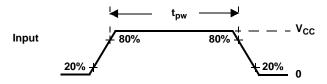

| ADIN[2]   73   73   73   ADIN[3]   72   72   ADIN[4]   71   71   71   ADIN[5]   70   69   68   ADIN[6]   69   68   67   ADIN[8]   79   82   ADIN[9]   78   80   ADIN[10]   77   78   ADIN[10]   77   78   ADIN[11]   76   76   ADIN[12]   - 81   ADIN[13]   - 79   ADIN[13]   - 70   ADIN[15]   - 81   ADIN[15]   - 80   ADIN[15]   - 80   ADIN[15]   - 80   ADIN[15]   - 70   ADIN[15]   - 80   ADI | ADIN[0]             | 75     | 75      |                    |              |                                                                                                                                                                                                                      |